JP2007294911A - Nonvolatile semiconductor memory device - Google Patents

Nonvolatile semiconductor memory device Download PDFInfo

- Publication number

- JP2007294911A JP2007294911A JP2007073790A JP2007073790A JP2007294911A JP 2007294911 A JP2007294911 A JP 2007294911A JP 2007073790 A JP2007073790 A JP 2007073790A JP 2007073790 A JP2007073790 A JP 2007073790A JP 2007294911 A JP2007294911 A JP 2007294911A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gate electrode

- insulating layer

- floating gate

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 284

- 239000000758 substrate Substances 0.000 claims abstract description 242

- 239000012535 impurity Substances 0.000 claims abstract description 228

- 230000015572 biosynthetic process Effects 0.000 claims abstract description 129

- 239000000463 material Substances 0.000 claims abstract description 73

- 239000000956 alloy Substances 0.000 claims abstract description 35

- 150000002736 metal compounds Chemical class 0.000 claims abstract description 18

- 239000007769 metal material Substances 0.000 claims abstract description 13

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 77

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 77

- 229910052710 silicon Inorganic materials 0.000 claims description 68

- 239000010703 silicon Substances 0.000 claims description 68

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 64

- 238000009832 plasma treatment Methods 0.000 claims description 64

- 229910052732 germanium Inorganic materials 0.000 claims description 47

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 47

- 230000004888 barrier function Effects 0.000 claims description 36

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 28

- 239000010936 titanium Substances 0.000 claims description 26

- 229910052721 tungsten Inorganic materials 0.000 claims description 23

- 239000010937 tungsten Substances 0.000 claims description 23

- 150000002291 germanium compounds Chemical class 0.000 claims description 20

- -1 tungsten nitride Chemical class 0.000 claims description 19

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 17

- 238000005121 nitriding Methods 0.000 claims description 17

- 229910052719 titanium Inorganic materials 0.000 claims description 17

- 239000011651 chromium Substances 0.000 claims description 16

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 claims description 15

- 229910052750 molybdenum Inorganic materials 0.000 claims description 15

- 239000011733 molybdenum Substances 0.000 claims description 15

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 15

- 229910052715 tantalum Inorganic materials 0.000 claims description 13

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 13

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 12

- 229910052759 nickel Inorganic materials 0.000 claims description 11

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 claims description 10

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 claims description 9

- 229910052804 chromium Inorganic materials 0.000 claims description 9

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 9

- 230000001590 oxidative effect Effects 0.000 claims description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 5

- 229910000476 molybdenum oxide Inorganic materials 0.000 claims description 5

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 claims description 5

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 claims description 5

- 229910001936 tantalum oxide Inorganic materials 0.000 claims description 5

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 5

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 claims description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 claims description 2

- 238000005536 corrosion prevention Methods 0.000 claims 4

- BIXHRBFZLLFBFL-UHFFFAOYSA-N germanium nitride Chemical compound N#[Ge]N([Ge]#N)[Ge]#N BIXHRBFZLLFBFL-UHFFFAOYSA-N 0.000 claims 1

- 239000010410 layer Substances 0.000 description 481

- 239000010408 film Substances 0.000 description 338

- 230000015654 memory Effects 0.000 description 198

- 238000000034 method Methods 0.000 description 59

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 57

- 239000007789 gas Substances 0.000 description 36

- 238000004519 manufacturing process Methods 0.000 description 32

- 230000003647 oxidation Effects 0.000 description 32

- 238000007254 oxidation reaction Methods 0.000 description 32

- 239000001301 oxygen Substances 0.000 description 32

- 229910052760 oxygen Inorganic materials 0.000 description 32

- 229910052581 Si3N4 Inorganic materials 0.000 description 31

- 239000000969 carrier Substances 0.000 description 31

- 230000006870 function Effects 0.000 description 31

- 229910052751 metal Inorganic materials 0.000 description 31

- 239000002184 metal Substances 0.000 description 31

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 31

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 29

- 229910052782 aluminium Inorganic materials 0.000 description 27

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 27

- 229910052757 nitrogen Inorganic materials 0.000 description 27

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 26

- 229910052698 phosphorus Inorganic materials 0.000 description 26

- 239000011574 phosphorus Substances 0.000 description 26

- 150000004767 nitrides Chemical class 0.000 description 24

- 239000002356 single layer Substances 0.000 description 20

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 19

- 239000012298 atmosphere Substances 0.000 description 19

- 229910052796 boron Inorganic materials 0.000 description 19

- 229910052785 arsenic Inorganic materials 0.000 description 17

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 17

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 16

- 229910052786 argon Inorganic materials 0.000 description 15

- 239000001257 hydrogen Substances 0.000 description 15

- 229910052739 hydrogen Inorganic materials 0.000 description 15

- 230000014759 maintenance of location Effects 0.000 description 15

- 229910045601 alloy Inorganic materials 0.000 description 14

- 230000001747 exhibiting effect Effects 0.000 description 14

- 239000010955 niobium Substances 0.000 description 14

- 239000003870 refractory metal Substances 0.000 description 14

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 13

- 238000010586 diagram Methods 0.000 description 13

- 229910052733 gallium Inorganic materials 0.000 description 13

- 238000004544 sputter deposition Methods 0.000 description 13

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 11

- 230000000694 effects Effects 0.000 description 11

- 230000008569 process Effects 0.000 description 11

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 10

- 229910052799 carbon Inorganic materials 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 238000010438 heat treatment Methods 0.000 description 10

- 229910004286 SiNxOy Inorganic materials 0.000 description 9

- 229910020286 SiOxNy Inorganic materials 0.000 description 9

- 238000002347 injection Methods 0.000 description 9

- 239000007924 injection Substances 0.000 description 9

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 238000012545 processing Methods 0.000 description 8

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 7

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 229910052743 krypton Inorganic materials 0.000 description 7

- 229910044991 metal oxide Inorganic materials 0.000 description 7

- 150000004706 metal oxides Chemical class 0.000 description 7

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 7

- 229910052758 niobium Inorganic materials 0.000 description 7

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 7

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 7

- 230000005684 electric field Effects 0.000 description 6

- 238000005530 etching Methods 0.000 description 6

- 239000012299 nitrogen atmosphere Substances 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 239000007790 solid phase Substances 0.000 description 6

- 125000001424 substituent group Chemical group 0.000 description 6

- 238000010924 continuous production Methods 0.000 description 5

- 229910052734 helium Inorganic materials 0.000 description 5

- 229910052754 neon Inorganic materials 0.000 description 5

- 229910052724 xenon Inorganic materials 0.000 description 5

- ZSLUVFAKFWKJRC-IGMARMGPSA-N 232Th Chemical compound [232Th] ZSLUVFAKFWKJRC-IGMARMGPSA-N 0.000 description 4

- 229910052684 Cerium Inorganic materials 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- 229910052776 Thorium Inorganic materials 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 125000001153 fluoro group Chemical group F* 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- 150000002431 hydrogen Chemical class 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- 239000011572 manganese Substances 0.000 description 4

- 229960001730 nitrous oxide Drugs 0.000 description 4

- 235000013842 nitrous oxide Nutrition 0.000 description 4

- 125000000962 organic group Chemical group 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 4

- 150000003376 silicon Chemical class 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 3

- 229920001665 Poly-4-vinylphenol Polymers 0.000 description 3

- 239000004952 Polyamide Substances 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 239000002784 hot electron Substances 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 239000011147 inorganic material Substances 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 229920002647 polyamide Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 150000003254 radicals Chemical class 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 101100481702 Arabidopsis thaliana TMK1 gene Proteins 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910002808 Si–O–Si Inorganic materials 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 238000000227 grinding Methods 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 150000002831 nitrogen free-radicals Chemical class 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910016909 AlxOy Inorganic materials 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000005984 hydrogenation reaction Methods 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000003746 solid phase reaction Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 230000002195 synergetic effect Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

Description

本発明は、電気的に書き込み、読み出し及び消去が可能な不揮発性半導体記憶装置並びにその作製方法に関する。特に当該不揮発性半導体記憶装置における浮遊ゲートの構成に関する。 The present invention relates to a nonvolatile semiconductor memory device which can be electrically written, read and erased, and a manufacturing method thereof. In particular, the present invention relates to a structure of a floating gate in the nonvolatile semiconductor memory device.

データを電気的に書き換え可能であり、電源を切ってもデータを記憶しておくことのできる不揮発性メモリの市場が拡大している。不揮発性メモリは、MOSFET(Metal Oxide Semiconductor Field effect transistor)と類似の構造を有し、電荷を長期間蓄積することのできる領域がチャネル形成領域上に設けられているところに特徴がある。この電荷蓄積領域は絶縁層上に形成され、周囲と絶縁分離されていることから浮遊ゲートとも呼ばれている。浮遊ゲートは絶縁物で囲まれて周囲とは電気的に絶縁されているので、浮遊ゲートに電荷が注入されるとその電荷を保持し続けるという特性を持っている。浮遊ゲート上には、さらに絶縁層を介して制御ゲートと呼ばれるゲート電極を備えている。制御ゲートは、データの書き込みや読み出しの時に所定の電圧が印加されることから浮遊ゲートとは区別されている。 The market for nonvolatile memories that can electrically rewrite data and store data even when the power is turned off is expanding. The nonvolatile memory has a structure similar to that of a MOSFET (Metal Oxide Semiconductor Field Effect Transistor) and is characterized in that a region capable of accumulating charges for a long period is provided on the channel formation region. This charge storage region is formed on an insulating layer and is also called a floating gate because it is isolated from the surroundings. Since the floating gate is surrounded by an insulator and is electrically insulated from the surroundings, the floating gate has a characteristic of continuing to hold the charge when the charge is injected into the floating gate. On the floating gate, a gate electrode called a control gate is further provided via an insulating layer. The control gate is distinguished from the floating gate because a predetermined voltage is applied when data is written or read.

このような構造を有する所謂浮遊ゲート型の不揮発性メモリは、浮遊ゲートへの電荷の注入と、浮遊ゲートからの電荷の放出を電気的に制御してデータを記憶する仕組みとなっている。具体的に、浮遊ゲートへの電荷注入及び浮遊ゲートからの電荷放出は、チャネル形成領域が形成される半導体層と、制御ゲートの間に高電圧を印加して行われている。このときチャネル形成領域上の絶縁層には、ファウラー−ノルドハイム(Fowler−Nordheim)型(F−N型)トンネル電流(NAND型)又は熱電子(NOR型)が流れると言われている。このことより当該絶縁層はトンネル絶縁層とも呼ばれている。 A so-called floating gate type nonvolatile memory having such a structure has a mechanism for storing data by electrically controlling charge injection into the floating gate and discharge of the charge from the floating gate. Specifically, charge injection into the floating gate and charge discharge from the floating gate are performed by applying a high voltage between the semiconductor layer in which the channel formation region is formed and the control gate. At this time, it is said that Fowler-Nordheim type (FN type) tunnel current (NAND type) or thermal electrons (NOR type) flow in the insulating layer on the channel formation region. Thus, the insulating layer is also called a tunnel insulating layer.

浮遊ゲート型の不揮発性メモリは、信頼性を保証するために、浮遊ゲートに貯えた電荷を10年以上保持できる特性が要求されている。そのためトンネル絶縁層には、トンネル電流が流れる厚さで形成しつつ、電荷が漏れてしまわないように、高い絶縁性が求められている。 Floating gate type non-volatile memories are required to have characteristics capable of retaining the charge stored in the floating gate for more than 10 years in order to guarantee reliability. For this reason, the tunnel insulating layer is required to have high insulating properties so as to prevent charges from leaking while being formed with a thickness through which a tunnel current flows.

また、トンネル絶縁層上に形成される浮遊ゲートは、チャネル形成領域が形成される半導体と同じ半導体材料であるシリコンで形成されてる。例えば、浮遊ゲートを多結晶シリコンで形成する方法が普及しており、例えば400nmの厚さにポリシリコン膜を堆積して形成したものが知られている(特許文献1参照)。

不揮発性メモリの浮遊ゲートは多結晶シリコンで形成されているので、半導体基板のチャネル形成領域の伝導帯の底のエネルギーレベルが同じとなる。むしろ浮遊ゲートの多結晶シリコンの厚さを薄膜化しようとすると、伝導帯の底のエネルギーレベルがチャネル形成領域を形成する半導体よりも高くなってしまう。このような状態が形成されると、半導体基板から浮遊ゲートに電子が注入されにくくなってしまい、書き込み電圧を高くする必要がある。書き込み電圧を少しでも下げるためには、浮遊ゲートを多結晶シリコンで形成する不揮発性メモリは、当該浮遊ゲートにリン、ヒ素などのn型不純物を添加してフェルミ準位を伝導帯側にシフトさせる必要がある。 Since the floating gate of the nonvolatile memory is formed of polycrystalline silicon, the energy level at the bottom of the conduction band in the channel formation region of the semiconductor substrate is the same. Rather, if the thickness of the polycrystalline silicon of the floating gate is reduced, the energy level at the bottom of the conduction band becomes higher than that of the semiconductor forming the channel formation region. When such a state is formed, it becomes difficult for electrons to be injected from the semiconductor substrate to the floating gate, and it is necessary to increase the writing voltage. In order to lower the write voltage as much as possible, in a nonvolatile memory in which the floating gate is formed of polycrystalline silicon, an n-type impurity such as phosphorus or arsenic is added to the floating gate to shift the Fermi level to the conduction band side. There is a need.

また、浮遊ゲートと半導体基板の間に設けるゲート絶縁層に関しては、低電圧で浮遊ゲートに電荷を注入するためには当該トンネル絶縁層の厚さを薄くする必要があり、一方、電荷を長期間安定的に保持させるためには、電荷(キャリア)の漏洩や不純物の侵入を防ぐために膜厚を厚くする必要がある。 In addition, regarding the gate insulating layer provided between the floating gate and the semiconductor substrate, in order to inject charges into the floating gate at a low voltage, it is necessary to reduce the thickness of the tunnel insulating layer. In order to stably hold the film, it is necessary to increase the film thickness in order to prevent leakage of charges (carriers) and intrusion of impurities.

結局、従来の不揮発性メモリは、高い書き込み電圧が必要とされている。また、電荷保持特性の繰り返しの書き換えによる劣化に対しては、冗長メモリセルを設けたりコントローラを工夫して、エラー検出/エラー訂正を行うなどの対処をして信頼性を確保している。 After all, the conventional nonvolatile memory requires a high write voltage. In addition, with respect to deterioration due to repeated rewriting of the charge retention characteristic, reliability is ensured by taking measures such as providing a redundant memory cell or devising a controller and performing error detection / error correction.

そこで本発明は、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置を提供することを目的とする。 Therefore, an object of the present invention is to provide a nonvolatile semiconductor memory device that is excellent in writing characteristics and charge retention characteristics.

本発明は、互いに離間して形成された一対の不純物領域の間にチャネル形成領域を形成する半導体基板と、半導体基板の上層部であってチャネル形成領域と略重なる位置に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を有する不揮発性半導体記憶装置である。本発明において、浮遊ゲート電極は半導体材料で形成される第1の層と、金属材料若しくはその合金材料又は金属化合物材料で形成される第2の層を少なくとも含んで形成される。すなわち、本発明に係る不揮発性半導体記憶装置の浮遊ゲート電極は、半導体層と、該半導体層の第2の絶縁層側に設けられる層であって、該半導体層の腐食を防止するバリア性の金属層、合金層若しくは金属化合物層により構成される。浮遊ゲート電極を形成する半導体材料は、チャネル形成領域を形成する半導体材料との関係において複数種の中から選択することができる。 The present invention provides a semiconductor substrate in which a channel formation region is formed between a pair of impurity regions formed apart from each other, and a first insulating layer at a position that is an upper layer portion of the semiconductor substrate and substantially overlaps the channel formation region , A non-volatile semiconductor memory device having a floating gate electrode, a second insulating layer, and a control gate electrode. In the present invention, the floating gate electrode is formed including at least a first layer formed of a semiconductor material and a second layer formed of a metal material, an alloy material thereof, or a metal compound material. That is, the floating gate electrode of the nonvolatile semiconductor memory device according to the present invention is a layer provided on the semiconductor layer and the second insulating layer side of the semiconductor layer, and has a barrier property to prevent corrosion of the semiconductor layer. It is comprised by a metal layer, an alloy layer, or a metal compound layer. The semiconductor material for forming the floating gate electrode can be selected from a plurality of types in relation to the semiconductor material for forming the channel formation region.

浮遊ゲート電極を形成する半導体材料として、次に示す一又は複数の条件を満たすものを選択することができる。浮遊ゲート電極を形成する半導体材料のバンドギャップ(「バンドギャップ」ともいう)は、半導体基板のチャネル形成領域のバンドギャップより小さいことが好ましい。例えば、浮遊ゲート電極を形成する半導体材料のバンドギャップと、半導体基板のチャネル形成領域のバンドギャップは、0.1eV以上の差があって、前者の方が小さいことが好ましい。 As a semiconductor material for forming the floating gate electrode, a material that satisfies one or more of the following conditions can be selected. The band gap (also referred to as “band gap”) of the semiconductor material forming the floating gate electrode is preferably smaller than the band gap of the channel formation region of the semiconductor substrate. For example, the band gap of the semiconductor material forming the floating gate electrode and the band gap of the channel formation region of the semiconductor substrate have a difference of 0.1 eV or more, and the former is preferably smaller.

また、浮遊ゲート電極を形成する半導体材料は、半導体基板を形成する材料よりも抵抗率が小さい材料で形成されていることが好ましい。抵抗率は40Ω・cm乃至100Ω・cmであることが好ましい。 The semiconductor material for forming the floating gate electrode is preferably formed of a material having a lower resistivity than the material for forming the semiconductor substrate. The resistivity is preferably 40 Ω · cm to 100 Ω · cm.

浮遊ゲート電極を形成する半導体材料として、代表的にはゲルマニウム若しくはゲルマニウム化合物であることが好ましい。 As a semiconductor material for forming the floating gate electrode, germanium or a germanium compound is typically preferable.

浮遊ゲート電極は電荷(キャリア)を蓄積する目的で、本発明に係る不揮発性半導体記憶装置に適用されるが、同様の機能を備えるものであれば、すなわち、電荷(キャリア)を蓄積する層として機能するものであれば、ゲルマニウム若しくはゲルマニウム化合物に限定されず、当該ゲルマニウム若しくはゲルマニウム化合物の酸化物若しくは窒化物、又は当該ゲルマニウム若しくはゲルマニウム化合物を含む酸化物層若しくは窒化物層で置き換えることもできる。 The floating gate electrode is applied to the nonvolatile semiconductor memory device according to the present invention for the purpose of accumulating charges (carriers). However, the floating gate electrode has a similar function, that is, as a layer for accumulating charges (carriers). It is not limited to germanium or a germanium compound as long as it functions, and can be replaced with an oxide or nitride of the germanium or germanium compound, or an oxide layer or nitride layer containing the germanium or germanium compound.

また、ゲルマニウム若しくはゲルマニウム化合物で形成される浮遊ゲート電極の第1の層に接する第2の層として、金属若しくはその合金又は金属化合物で形成される層を適用することが好ましい。金属としては、タングステン(W)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、ニッケル(Ni)などの高融点金属を用いることが好ましい。当該高融点金属の複数種を用いる合金を用いても良い。また、合金を形成する材料として、上記高融点金属に、ニオブ(Nb)、ジルコニウム(Zr)、セリウム(Ce)、トリウム(Th)、ハフニウム(Hf)を用いても良い。また、当該高融点金属の酸化物若しくは窒化物を用いることもできる。金属窒化物としては、窒化タンタル、窒化タングステン、窒化モリブデン、窒化チタンなどを用いることができる。金属酸化物としては、酸化タンタル、酸化チタン、酸化モリブデンなどを用いることができる。 In addition, it is preferable to apply a layer formed of a metal, an alloy thereof, or a metal compound as the second layer in contact with the first layer of the floating gate electrode formed of germanium or a germanium compound. As the metal, it is preferable to use a refractory metal such as tungsten (W), tantalum (Ta), titanium (Ti), molybdenum (Mo), chromium (Cr), nickel (Ni). An alloy using a plurality of types of the refractory metals may be used. In addition, niobium (Nb), zirconium (Zr), cerium (Ce), thorium (Th), or hafnium (Hf) may be used as the material for forming the alloy as the refractory metal. Alternatively, an oxide or nitride of the refractory metal can be used. As the metal nitride, tantalum nitride, tungsten nitride, molybdenum nitride, titanium nitride, or the like can be used. As the metal oxide, tantalum oxide, titanium oxide, molybdenum oxide, or the like can be used.

半導体基板上にトンネル絶縁層として機能する第1の絶縁層を介して浮遊ゲート電極を形成する場合に、少なくともゲルマニウムを含む半導体材料で浮遊ゲート電極を形成することにより、半導体基板のチャネル形成領域から浮遊ゲート電極への電荷(キャリア)を注入しやすくし、浮遊ゲート電極における電荷保持特性を向上させることができる。さらに、浮遊ゲート電極を形成する半導体材料に接して金属若しくはその合金、又は金属化合物で形成される層を適用することにより、この層は当該浮遊ゲート電極の耐水性を向上させ腐食を防止するバリア層として機能させることができる。それにより、浮遊ゲート電極の劣化を抑制することができる。 In the case where the floating gate electrode is formed on the semiconductor substrate through the first insulating layer functioning as the tunnel insulating layer, the floating gate electrode is formed from a semiconductor material containing at least germanium, so that the channel formation region of the semiconductor substrate is removed. Charges (carriers) can be easily injected into the floating gate electrode, and the charge retention characteristics of the floating gate electrode can be improved. Furthermore, by applying a layer formed of a metal, an alloy thereof, or a metal compound in contact with the semiconductor material forming the floating gate electrode, this layer improves the water resistance of the floating gate electrode and prevents corrosion. Can function as a layer. Thereby, deterioration of the floating gate electrode can be suppressed.

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。 Embodiments of the present invention will be described below with reference to the drawings. However, the present invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details can be variously changed without departing from the spirit and scope of the present invention. Therefore, the present invention should not be construed as being limited to the description of the embodiments below. Note that in the structures of the present invention described below, the same reference numerals may be used in common in different drawings.

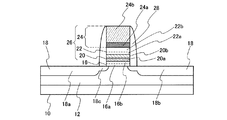

図1は本発明に係る不揮発性半導体記憶装置の主要な構成を説明するための断面図である。図1は、特に不揮発性メモリ素子の要部を示している。この不揮発性メモリ素子は、半導体基板10を用いて作製されている。半導体基板10としては単結晶シリコン基板(シリコンウエハー)を用いることが好ましい。また、SOI(Si−On−Insulator)基板を用いることもできる。SOI基板として、鏡面研磨ウェハーに酸素イオンを注入した後、高温アニールすることにより、表面から一定の深さに酸化膜層を形成させるとともに、表面層に生じた欠陥を消滅させて作られた所謂SIMOX(Separation by IMplanted Oxygen)基板を用いても良い。

FIG. 1 is a cross-sectional view for explaining a main configuration of a nonvolatile semiconductor memory device according to the present invention. FIG. 1 particularly shows the main part of the nonvolatile memory element. This nonvolatile memory element is manufactured using a

半導体基板10がn型で有る場合にはp型不純物が注入されたpウエル12が形成されている。p型不純物として、例えばホウ素が用いられ、5×1015atoms/cm3乃至1×1016atoms/cm3程度の濃度で添加されている。pウエル12を形成することにより、この領域にnチャネル型のトランジスタを形成することができる。また、pウエル12に添加するp型不純物は、トランジスタのしきい値電圧を制御する作用もある。半導体基板10に形成されるチャネル形成領域14は、後述するゲート26と略一致する領域に形成されるものであり、半導体基板10に形成される一対の不純物領域18の間に位置するものである。

When the

一対の不純物領域18は不揮発性メモリ素子においてソース及びドレインとして機能する領域である。一対の不純物領域18はn型不純物であるリン若しくはヒ素を1×10atoms/cm3乃至1021atoms/cm3程度の濃度で添加することで形成される。

The pair of

ゲート26の側壁にはスペーサ28が形成され、その端部においてリーク電流(例えば、浮遊ゲート電極20と制御ゲート電極24の間に流れてしまう電流)を防ぐ効果がある。また、このスペーサ28を利用して、ゲート26のチャネル長方向の両端に低濃度不純物領域18cを形成することができる。この低濃度不純物領域18cは低濃度ドレイン(LDD)として機能する。低濃度不純物領域18cは必須の構成とはならないが、この領域を設けることにより、ドレイン端の電界を緩和して、書き込み及び消去の繰り返しによる劣化を抑制することができる。

A

半導体基板10上には第1の絶縁層16、浮遊ゲート電極20、第2の絶縁層22、制御ゲート電極24が形成されるが、本明細書では、浮遊ゲート電極20から制御ゲート電極24までの積層構造をゲート26と呼ぶことがある。

A first insulating

第1の絶縁層16は酸化シリコン若しくは酸化シリコンと窒化シリコンの積層構造で形成する。第1の絶縁層16は、熱酸化により半導体基板10の表面を酸化して形成しても良いが、好ましくはプラズマ処理による固相酸化若しくは固相窒化で形成すると良い。半導体基板10の表面を、プラズマ処理により酸化又は窒化することにより形成した絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。第1の絶縁層16は、浮遊ゲート電極20に電荷(キャリア)を注入するためのトンネル絶縁層として用いるので、このように丈夫であるものが好ましい。この第1の絶縁層16は1nm以上20nm以下、好ましくは3nm以上6nm以下の厚さに形成することが好ましい。例えば、ゲート長を600nmとする場合、第1の絶縁層16は3nm以上6nm以下の厚さに形成することができる。

The first insulating

プラズマ処理による固相酸化処理若しくは固相窒化処理として、マイクロ波(代表的には2.45GHz)で励起され、電子密度が1×1011cm−3以上1×1013cm−3以下、且つ電子温度が0.5eV以上1.5eV以下のプラズマを利用することが好ましい。固相酸化処理若しくは固相窒化処理において、500℃以下の温度において、緻密な絶縁層を形成すると共に実用的な反応速度を得るためである。 As solid-phase oxidation treatment or solid-phase nitridation treatment by plasma treatment, the electron density is 1 × 10 11 cm −3 or more and 1 × 10 13 cm −3 or less when excited by microwaves (typically 2.45 GHz), and It is preferable to use plasma having an electron temperature of 0.5 eV to 1.5 eV. This is because in the solid phase oxidation treatment or solid phase nitridation treatment, a dense insulating layer is formed at a temperature of 500 ° C. or lower and a practical reaction rate is obtained.

このプラズマ処理により半導体基板10の表面を酸化する場合には、酸素雰囲気下(例えば、酸素(O2)又は一酸化二窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、若しくは酸素又は一酸化二窒素と水素(H2)と希ガス雰囲気下)で行う。また、プラズマ処理により窒化をする場合には、窒素雰囲気下(例えば、窒素(N2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、窒素と水素と希ガス雰囲気下、若しくはNH3と希ガス雰囲気下)でプラズマ処理を行う。希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。

When the surface of the

図15にプラズマ処理を行うための装置の構成例を示す。このプラズマ処理装置は、半導体基板10を配置するための支持台80と、ガスを導入するためのガス供給部76、ガスを排気するために真空ポンプに接続する排気口78、アンテナ72、誘電体板74、プラズマ発生用のマイクロ波を供給するマイクロ波供給部84を有している。また、支持台80に温度制御部82を設けることによって、半導体基板10の温度を制御することも可能である。

FIG. 15 shows a configuration example of an apparatus for performing plasma processing. This plasma processing apparatus includes a

以下に、プラズマ処理について説明する。なお、プラズマ処理とは、半導体基板、絶縁層、導電層に対する酸化処理、窒化処理、酸窒化処理、水素化処理、表面改質処理を含んでいる。これらの処理は、その目的に応じて、ガス供給部76から供給するガスを選択すれば良い。

Hereinafter, the plasma treatment will be described. Note that the plasma treatment includes oxidation treatment, nitridation treatment, oxynitridation treatment, hydrogenation treatment, and surface modification treatment for a semiconductor substrate, an insulating layer, and a conductive layer. For these processes, a gas supplied from the

酸化処理若しくは窒化処理を行うには以下のようにすれば良い。まず、処理室内を真空にし、ガス供給部76から酸素又は窒素を含むプラズマ処理用ガスを導入する。半導体基板10は室温若しくは温度制御部82により100℃乃至550℃に加熱する。なお、半導体基板10と誘電体板74との間隔は、20mm乃至80mm(好ましくは20mm乃至60mm)程度である。次に、マイクロ波供給部84からアンテナ72にマイクロ波を供給する。そしてマイクロ波をアンテナ72から誘電体板74を通して処理室内に導入することによって、プラズマ86を生成する。マイクロ波の導入によりプラズマの励起を行うと、低電子温度(3eV以下、好ましくは1.5eV以下)で高電子密度(1×1011cm−3以上)のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)及び/又は窒素ラジカル(NHラジカルを含む場合もある)によって、半導体基板の表面を酸化及び/又は窒化することができる。プラズマ処理用ガスにアルゴンなどの希ガスを混合させると、希ガスの励起種により酸素ラジカルや窒素ラジカルを効率良く生成することができる。この方法は、プラズマで励起した活性なラジカルを有効に使うことにより、500℃以下の低温で固相反応による酸化、窒化、酸化窒化又は酸化した層を窒化することができる。

The oxidation treatment or nitridation treatment may be performed as follows. First, the processing chamber is evacuated, and a plasma processing gas containing oxygen or nitrogen is introduced from the

図1において、プラズマ処理により形成される好適な第1の絶縁層16の一例は、酸素雰囲気下のプラズマ処理により半導体基板10の表面を3nm以上6nm以下の厚さで酸化シリコン層16aを形成し、その後窒素雰囲気下でその酸化シリコン層の表面を窒化プラズマで処理した窒素プラズマ処理層16bを形成する。具体的には、まず、酸素雰囲気下でのプラズマ処理により半導体基板10上に3nm以上6nm以下の厚さで酸化シリコン層16aを形成する。その後、続けて窒素雰囲気下でプラズマ処理を行うことにより酸化シリコン層の表面又は表面近傍に窒素濃度の高い窒素プラズマ処理層16bを設ける。なお、表面近傍とは、酸化シリコン層の表面から概略0.5nm乃至1.5nmの深さをいう。例えば、窒素雰囲気下でプラズマ処理を行うことによって、酸化シリコン層16aの表面から概略1nmの深さに窒素を20原子%乃至50原子%の割合で含有させた構造とする。

In FIG. 1, an example of a suitable first insulating

浮遊ゲート電極20は第1の絶縁層16上に形成される。この浮遊ゲート電極20は、第1の浮遊ゲート電極20aと第2の浮遊ゲート電極20bにより形成されている。勿論、この二層構造に限定されず、複数の層を積層して設ければ良い。しかしながら、第1の絶縁層16に接して形成される第1の浮遊ゲート電極20aは半導体材料で形成することが好ましく、次に示す一又は複数の条件を満たすものを選択することができる。

The floating

第1の浮遊ゲート電極20aを形成する半導体材料のバンドギャップが、半導体基板10(本例ではチャネル形成領域)のバンドギャップより小さいことが好ましい。例えば、第1の浮遊ゲート電極20aを形成する半導体材料のバンドギャップと、半導体基板10のチャネル形成領域におけるバンドギャップは、0.1eV以上の差があって、前者の方が小さいことが好ましい。半導体基板10のチャネル形成領域の伝導帯の底のエネルギーレベルより、浮遊ゲート電極20の伝導帯の底のエネルギーレベルを低くすることにより、キャリア(電子)の注入性を向上させ、電荷保持特性を向上させるためである。

The band gap of the semiconductor material forming the first floating

第1の浮遊ゲート電極20aを形成する半導体材料は、半導体基板10(本例ではチャネル形成領域)を形成する材料よりも抵抗率が小さい材料で形成されていることが好ましい。第1の浮遊ゲート電極20aを抵抗率の小さい半導体材料で形成することにより、制御ゲート電極と半導体基板(本例ではチャネル形成領域)の間に電圧を印加したとき、電界が浮遊ゲート電極で印加電圧が分圧されずにすみ、電界を半導体基板(本例ではチャネル形成領域)に有効に作用させることができる。例えば、ゲルマニウムは40Ω・cm乃至70Ω・cmの固有抵抗を有するので好ましい。また、抵抗率を下げる目的で第1の浮遊ゲート電極20aにn型不純物を添加しても良い。このように、半導体基板10(本例ではチャネル形成領域)と比較して、第1の浮遊ゲート電極20aをバンドギャップが小さく抵抗率が低い材料で形成することで、書き込み特性を向上させることができる。

The semiconductor material forming the first floating

第1の浮遊ゲート電極20aを形成する半導体材料は、第1の絶縁層16により形成される半導体基板10のチャネル形成領域における電子に対する障壁エネルギーに対し、第1の絶縁層16により形成される第1の浮遊ゲート電極20aの電子に対する障壁エネルギーが高くなるものであることが好ましい。半導体基板10の特にチャネル形成領域から第1の浮遊ゲート電極20aへのキャリア(電子)を注入しやすくし、第1の浮遊ゲート電極20aから電荷(キャリア)が消失することを防ぐためである。

The semiconductor material forming the first floating

このような条件を満たすものとして、代表的にはゲルマニウム若しくはゲルマニウム化合物を選択することができる。ゲルマニウム化合物の代表例としては、シリコンゲルマニウムであり、この場合シリコンに対してゲルマニウムが10原子%以上含まれていることが好ましい。ゲルマニウムの濃度が10原子%未満であると、構成元素としての効果が薄れ、バンドギャップが有効に小さくならないためである。 Typically, germanium or a germanium compound can be selected as satisfying such conditions. A typical example of the germanium compound is silicon germanium. In this case, it is preferable that germanium is contained at 10 atomic% or more with respect to silicon. This is because if the concentration of germanium is less than 10 atomic%, the effect as a constituent element is reduced, and the band gap is not effectively reduced.

勿論、第1の浮遊ゲート電極20aを形成するものとして同様な効果を発現するものであれば、他の材料を適用することもできる。例えば、ゲルマニウムを含む三元系の半導体材料を適用することができる。また、当該半導体材料が水素化されていても良い。また、不揮発性メモリ素子の電荷(キャリア)を蓄積する層としての機能を持つものとして、当該ゲルマニウム若しくはゲルマニウム化合物の酸化物若しくは窒化物、又は当該ゲルマニウム若しくはゲルマニウム化合物を含む酸化物若しくは窒化物の層で置き換えることもできる。

Of course, other materials can be applied as long as the same effect can be obtained as the first floating

第1の浮遊ゲート電極20aに接して、第2の絶縁層22側に設ける第2の浮遊ゲート電極20bは、金属若しくはその合金、又は金属化合物で形成される層を適用することが好ましい。金属としては、タングステン(W)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、ニッケル(Ni)などの高融点金属を用いることが好ましい。当該高融点金属の複数種を用いる合金を用いても良い。また、合金を形成する材料として、上記高融点金属に、ニオブ(Nb)、ジルコニウム(Zr)、セリウム(Ce)、トリウム(Th)、ハフニウム(Hf)を用いても良い。また、当該高融点金属の酸化物若しくは窒化物を用いることもできる。金属窒化物としては、窒化タンタル、窒化タングステン、窒化モリブデン、窒化チタンなどを用いることができる。金属酸化物としては、酸化タンタル、酸化チタン、酸化モリブデンなどを用いることができる。

As the second floating

このように第2の浮遊ゲート電極20bを、金属等で形成することにより、第1の浮遊ゲート電極20aの安定化を図ることができる。すなわち、第2の浮遊ゲート電極20bは、、ゲルマニウム若しくはゲルマニウム化合物で形成される第1の浮遊ゲート電極20aの上層側に設けることにより、製造工程においては、耐水性や耐薬品性を目的としたバリア層として用いることができる。それにより、フォトリソ工程、エッチング工程、洗浄工程における基板の扱いが容易となり、生産性を向上させることができる。すなわち、浮遊ゲート電極の加工を容易なものとすることができる。

In this manner, the first floating

第2の絶縁層22は、酸化シリコン、酸化窒化シリコン(SiOxNy、(x>y))、窒化シリコン(SiNx)又は窒化酸化シリコン(SiNxOy、(x>y))、酸化アルミニウム(AlxOy)などの一層若しくは複数層を、減圧CVD法やプラズマCVD法などで形成する。第2の絶縁層22の厚さは1nm以上20nm以下、好ましくは5nm以上10nm以下で形成する。例えば、窒化シリコン層22aを3nmの厚さに堆積し、酸化シリコン層22bの厚さを5nmの厚さに堆積したものを用いることができる。また、酸化窒化シリコン(SiOxNy、(x>y))をプラズマCVD法で成膜後、前述のプラズマ処理により窒化処理を行った絶縁層を第2の絶縁層22に適用しても良い。窒化酸化シリコン(SiNxOy、(x>y))プラズマCVD法で成膜後、前述のプラズマ処理により酸化処理を行った絶縁層を第2の絶縁層22に適用しても良い。このように、プラズマCVD法などで堆積した絶縁層に窒化又は酸化処理を目的としたプラズマ処理を行うことで、絶縁耐圧を向上させることができる。このような絶縁層を第2の絶縁層22とすることで、浮遊ゲート電極20に蓄積する電荷が制御ゲート電極24側にリークしてしまうことを防ぐことができる。

The second insulating

制御ゲート電極24はタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、ニオブ(Nb)等から選択された金属、又はこれらの金属を主成分とする合金材料若しくは化合物材料で形成することが好ましい。また、リン等の不純物元素を添加した多結晶シリコンを用いることができる。また、一層又は複数層の金属窒化物層24aと上記の金属層24bの積層構造で制御ゲート電極24を形成しても良い。金属窒化物としては、窒化タングステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物層24aを設けることにより、金属層24bの密着性を向上させることができ、剥離を防止することができる。また、窒化タンタルなどの金属窒化物は仕事関数が高いので、第2の絶縁層22との相乗効果により、第1の絶縁層16の厚さを厚くすることができる。

The

図1に示す不揮発性メモリ素子の動作メカニズムを、エネルギーバンド図を参照して説明する。以下に示すエネルギーバンド図において、図1と同じ要素には同じ符号を付している。 An operation mechanism of the nonvolatile memory element shown in FIG. 1 will be described with reference to an energy band diagram. In the energy band diagram shown below, the same elements as those in FIG.

図2は半導体基板10のチャネル形成領域、第1の絶縁層16、浮遊ゲート電極20、第2の絶縁層22、制御ゲート電極24が積層された状態を示している。図2は制御ゲート電極24に電圧を印加していない場合であって、半導体基板10のチャネル形成領域のフェルミ準位Efと制御ゲート電極24のフェルミ準位Efmが等しい場合を示している。

FIG. 2 shows a state in which the channel formation region of the

第1の絶縁層16を挟んで、半導体基板10と第1の浮遊ゲート電極20aは異なる材料で形成している。半導体基板10のチャネル形成領域のバンドギャップEg1(伝導帯の下端Ecと価電子帯の上端Evのエネルギー差)と第1の浮遊ゲート電極20aのバンドギャップEg2は異なるものとし、後者のバンドギャップは小さくなるように組み合わせている。例えば、半導体基板10のチャネル形成領域としてシリコン(1.12eV)、第1の浮遊ゲート電極20aとしてゲルマニウム(0.72eV)又はシリコンゲルマニウム(0.73eV乃至1.0eV)を組み合わせることができる。ゲルマニウム又はシリコンゲルマニウムは水素化されていても良い。このときゲルマニウム又はシリコンゲルマニウムに対する水素の含有量は、1原子%乃至30原子%であれば良い。

The

第2の浮遊ゲート電極20bとして金属層を用いる場合、その金属材料の仕事関数は、第1の浮遊ゲート電極20aの仕事関数と比較して小さいものを用いることができる。第2の浮遊ゲート電極20bに注入されたキャリア(電子)に対してバリアが形成されないためである。それにより、半導体基板10のチャネル形成領域から第2の浮遊ゲート電極20bにキャリア(電子)がより注入されやすくなる。例えば、第1の浮遊ゲート電極20aとして用いることのできるゲルマニウムの仕事関数は5.0eVであるのに対し、タングステン(仕事関数:4.55eV)、タンタル(4.25eV)、チタン(4.33eV)、モリブデン(4.6eV)、クロム(4.5eV)を適用することができる。

When a metal layer is used as the second floating

なお、第1の絶縁層16は酸化シリコン層16a(約8eV)と、当該酸化シリコンをプラズマ処理により窒化した窒化処理した窒素プラズマ処理層16b(約5eV)で示している。また、第2の絶縁層22も、浮遊ゲート電極20側から、窒化シリコン層22aと酸化シリコン層22bが積層した状態を示している。

The first insulating

第1の絶縁層16を挟んで、半導体基板10のチャネル形成領域と第1の浮遊ゲート電極20aは異なる材料で形成している。この場合、半導体基板10のチャネル形成領域のバンドギャップと第1の浮遊ゲート電極20aのバンドギャップは異なるものであり、後者のバンドギャップは小さくなるように組み合わせている。例えば、半導体基板10のチャネル形成領域をシリコン(1.12eV)として、第1の浮遊ゲート電極20aをゲルマニウム(0.72eV)又はシリコンゲルマニウム(0.73eV乃至1.1eV)とすることができる。すなわち、半導体基板10のチャネル形成領域としてシリコンのバンドギャップEg1と、第1の浮遊ゲート電極20aとしてゲルマニウムのバンドギャップEg2は、Eg1>Eg2の関係を満たしている。半導体基板10のチャネル形成領域と第1の浮遊ゲート電極20aのそれぞれについて、第1の絶縁層16による電子に対するエネルギー障壁、すなわち第1障壁Be1と第2障壁Be2は異なる値となり、Be2>Be1の関係を持たせることができる。このような状況においては、半導体基板10のチャネル形成領域と浮遊ゲート電極20の伝導帯底のエネルギーレベルのエネルギー差ΔEが発生する。後述するように、このエネルギー差ΔEは、半導体基板10のチャネル形成領域から浮遊ゲート電極20に電子を注入するとき、電子を加速する方向に作用するので、書き込み電圧を低下させるのに寄与する。

The channel formation region of the

比較のために、半導体基板のチャネル形成領域と浮遊ゲート電極を同じ半導体材料で形成した場合のエネルギーバンド図を図16に示す。このエネルギーバンド図は、半導体基板01のチャネル形成領域、第1の絶縁層02、浮遊ゲート電極03、第2の絶縁層04、制御ゲート電極05が順次積層された状態を示している。

For comparison, FIG. 16 shows an energy band diagram when the channel formation region of the semiconductor substrate and the floating gate electrode are formed of the same semiconductor material. This energy band diagram shows a state in which the channel formation region of the

浮遊ゲート電極03の厚さはチャネル長と同程度、若しくはさらに薄くすることが本来好ましい。サブミクロンのレベルでのファインパターンを形成するためである。膜厚が厚くなるとゲート長に対してファインパターンを形成することが出来なくなるからである。しかし、浮遊ゲート電極03がより薄くなると、半導体基板のチャネル形成領域と浮遊ゲート電極03を同じシリコン半導体で形成した場合、浮遊ゲート電極03のバンドギャップは結果として大きくなってしまう。すなわち、浮遊ゲート電極03の伝導帯の底のエネルギーレベルは、半導体基板のチャネル形成領域における伝導帯の底のエネルギーレベルよりも高くなってしまう。

It is originally preferable that the thickness of the floating

図16はこの状態を示している。半導体基板01におけるチャネル形成領域のバンドギャップをEg11、浮遊ゲート電極03のバンドギャップをEg12で示している。シリコンでは薄膜化すると、バンドギャップがバルクの1.12eVから1.4eV程度まで増大すると言われている。それにより、半導体基板01のチャネル形成領域と浮遊ゲート電極03の間には、電子の注入をさせにくくする方向にΔEのエネルギー差が生じてしまう。このような状況では、半導体基板01のチャネル形成領域から浮遊ゲート電極03に電子を注入するために高電圧が必要になってしまう。すなわち、書き込み電圧を下げるために、浮遊ゲート電極03にn型不純物としてリンやヒ素を高濃度にドーピングする必要がある。このことは、従来の不揮発性メモリにおける欠点である。

FIG. 16 shows this state. The band gap of the channel formation region in the

しかし、図2で示すように、浮遊ゲート電極20としてゲルマニウムを用いた場合には、シリコンよりそもそもバンドギャップが0.72eVと小さい。薄膜化によりゲルマニウムのバンドギャップが拡大したとしても、せいぜい1eV程度であるので、半導体基板10のチャネル形成領域におけるバンドギャップよりは小さい状態が保たれる。それにより、チャネル形成領域から注入される電子に対して、伝導帯下端のエネルギー差により生じる自己バイアスは、浮遊ゲート電極20に電子を注入させやすくする方向に働く。ゲルマニウムにn型不純物であるリンやヒ素を添加すると、その作用をさらに増長させることができる。

However, as shown in FIG. 2, when germanium is used as the floating

結果として、浮遊ゲート電極20としてゲルマニウム若しくはゲルマニウム化合物を用いる場合には、その膜厚を薄くすることが出来、より微細な構造を作り込むことができる。特に不揮発性メモリ素子のチャネル長が100nm以下、好ましくは20nm以上50nm以下において、ゲルマニウム若しくはゲルマニウム化合物、又はそれらにn型不純物が添加された浮遊ゲート電極については、厚さを薄くすることが出来、超高集積化する上で好ましい。

As a result, when germanium or a germanium compound is used as the floating

また、浮遊ゲート電極に対しn型不純物を高濃度に添加すると、チャネル形成領域との間に耐圧を下げる傾向があり、あまり高濃度にすることも好ましくない。結果として、n型又はp型不純物を意図的に添加しない、又はn型不純物が1×1018乃至2×1020cm−3の濃度で添加した導電性のゲルマニウム若しくはゲルマニウム化合物が好ましいものとなる。そのために、ゲルマニウム若しくはゲルマニウム化合物で形成される浮遊ゲート電極中の、絶縁化しやすい不純物である炭素(C)、窒素(N)、酸素(O)は、いずれも5×1019cm−3以下、好ましくは2×1019cm−3以下とすることが好ましい。 Further, when an n-type impurity is added at a high concentration to the floating gate electrode, the breakdown voltage tends to be lowered between the floating gate electrode and the channel formation region, and it is not preferable to make the concentration too high. As a result, conductive germanium or a germanium compound in which n-type or p-type impurities are not intentionally added or n-type impurities are added at a concentration of 1 × 10 18 to 2 × 10 20 cm −3 is preferable. . Therefore, carbon (C), nitrogen (N), and oxygen (O), which are impurities that are easily insulated, in the floating gate electrode formed of germanium or a germanium compound are all 5 × 10 19 cm −3 or less, Preferably it is 2 * 10 < 19 > cm <-3> or less.

ところで、浮遊ゲート電極20に電子を注入するには、熱電子を利用する方法と、F−N型トンネル電流を利用する方法がある。熱電子を利用する場合には、正の電圧を制御ゲート電極24印加して、ドレインに高電圧を印加して熱電子を発生させる。それにより、熱電子を浮遊ゲート電極20に注入することができる。F−N型トンネル電流を利用する場合には、正の電圧を制御ゲート電極24に印加して半導体基板10のチャネル形成領域からF−N型トンネル電流により浮遊ゲート電極20に注入する。

By the way, in order to inject electrons into the floating

図6(A)はF−N型トンネル電流により浮遊ゲート電極20に注入するときの印加電圧を示している。半導体基板10のpウエル12を接地して、制御ゲート電極24に正の高電圧(10V乃至20V)を印加すると共に、ソース領域18aとドレイン領域18bは0Vとしておく。このときのエネルギーバンド図は図3に示すようになる。高電界により半導体基板10のチャネル形成領域の電子は第1の絶縁層16に注入され、F−N型トンネル電流が流れる。図2で説明したように、半導体基板10におけるチャネル形成領域のバンドギャップEg1と、浮遊ゲート電極20のバンドギャップEg2の関係は、Eg1>Eg2である。この差が自己バイアスとして、チャネル形成領域より注入された電子を浮遊ゲート電極の方に加速するように作用する。それにより、電子の注入性を向上させることができる。

FIG. 6A shows an applied voltage when injecting into the floating

浮遊ゲート電極20の伝導帯の底のエネルギーレベルは、半導体基板10のチャネル形成領域の伝導帯の底のエネルギーレベルに対して電子エネルギー的にΔEだけ低い準位にある。そのため電子が浮遊ゲート電極20に注入されるに当たっては、このエネルギー差に起因する内部電界が作用する。これは、上記したような半導体基板10のチャネル形成領域と浮遊ゲート電極20の組み合わせによって実現する。すなわち、半導体基板10のチャネル形成領域から浮遊ゲート電極20へ電子を注入しやすくなり、不揮発性メモリ素子における書き込み特性を向上させることができる。この作用は、熱電子を利用して浮遊ゲート電極20に電子を注入する場合にも同様である。

The energy level of the bottom of the conduction band of the floating

浮遊ゲート電極20に電子が保持されている間は、不揮発性メモリ素子のしきい値電圧は正の方向にシフトする。この状態を、データ”0”が書き込まれた状態とすることができる。図4は、電荷保持状態のエネルギーバンド図を示している。浮遊ゲート電極20の電子は、第1の絶縁層16と第2の絶縁層22に挟まれていることにより、エネルギー的に閉じこめられた状態にある。第1の浮遊ゲート電極20aに蓄積するキャリア(電子)によりポテンシャルは上がるが、障壁エネルギーを超えるエネルギーが電子に付与されない限り第1の浮遊ゲート電極20aから電子は放出されないことになる。すなわち、消去動作において、浮遊ゲート電極に注入されたキャリアが残留して消去不良になってしまうのを防ぐことができる。尤も、第2の浮遊ゲート電極20bも浮遊ゲート電極としてキャリアを蓄積する能力があるので、第1の浮遊ゲート電極20aを補って浮遊ゲート電極として機能することができる。すなわち、150℃の恒温放置による信頼性試験においても浮遊ゲート電極に蓄積したキャリアを保持することができる。

While electrons are held in the floating

いずれにしても、この場合、障壁エネルギーを超えるエネルギーが電子に付与されない限り浮遊ゲート電極20から電子は放出されないことになる。また、浮遊ゲート電極20の伝導帯の底のエネルギーレベルは、半導体基板10のチャネル形成領域の伝導帯の底のエネルギーレベルに対して電子エネルギー的にΔEだけ低い準位にあり、電子に対してエネルギー的な障壁が形成される。この障壁により、トンネル電流によって半導体基板10に電子が流出してしまうのを防ぐことができる。

In any case, in this case, electrons are not emitted from the floating

データ”0”が書き込まれた状態を検出するには、中間電位Vreadを制御ゲート電極24に印加したときに、トランジスタがオンにならないことを回路によって判別すれば良い。中間電位とは、データ”1”におけるしきい値電圧Vth1と、データ”0”におけるしきい値電圧Vth2の中間の電位である(この場合、Vth1<Vread<Vth2)。又は、図6(B)に示すようにソース領域18aとドレイン領域18b間にバイアスを印加して、制御ゲート電極24を0V若しくはデータ”0”と”1”のしきい値の中間の電位Vreadとしたときに不揮発性メモリ素子が導通するか否かで判断することができる。

In order to detect the state in which the data “0” is written, it may be determined by a circuit that the transistor is not turned on when the intermediate potential Vread is applied to the

図7(A)は浮遊ゲート電極20から電荷(キャリア)を放出させ、不揮発性メモリ素子からデータを消去する状態を示している。この場合、制御ゲート電極24を接地して、半導体基板10のpウエル12に負のバイアスを印加して、半導体基板10のチャネル形成領域と浮遊ゲート電極20の間にF−N型トンネル電流を流すことにより行う。或いは、図7(B)に示すように、制御ゲート電極24に負のバイアスを印加し、ソース領域18aに正の高電圧を印加することにより、F−N型トンネル電流を発生させ、ソース領域18a側に電子を引き抜いても良い。

FIG. 7A shows a state in which charges (carriers) are released from the floating

図5は、この消去状態のエネルギーバンド図を示している。消去動作では、第1の絶縁層16を薄くすることができるので、F−N型トンネル電流により浮遊ゲート電極20の電子を半導体基板10側に放出させることができる。また、半導体基板10のチャネル形成領域から正孔を浮遊ゲート電極20に注入することにより、実質的な消去動作をすることができる。また、半導体基板10のチャネル形成領域から正孔がより注入されやすく、浮遊ゲート電極20に注入することにより、実質的な消去動作をすることができる。

FIG. 5 shows an energy band diagram in this erased state. In the erasing operation, the first insulating

浮遊ゲート電極20をゲルマニウム若しくはゲルマニウム化合物で形成することにより、第1の絶縁層16の厚さを薄くすることができる。それにより、トンネル電流によって第1の絶縁層16を介して電子を浮遊ゲート電極20に注入することが容易となり、低電圧動作が可能となる。さらに、低エネルギーレベルで電荷(キャリア)を保存することが可能になり、電荷を安定した状態で保存できるという有意な効果を奏することができる。

By forming the floating

本発明に係る不揮発性メモリ素子では、図2、図3で示すように、半導体基板10のチャネル形成領域と浮遊ゲート電極20の間でEg1>Eg2として自己バイアスが生じるように構成している。この関係は極めて重要であり、半導体基板のチャネル形成領域から浮遊ゲート電極にキャリアを注入するときに、注入しやすくするように作用する。すなわち、書き込み電圧の低電圧化を図ることができる。逆に浮遊ゲート電極からキャリアを放出させにくくしている。このことは、不揮発性メモリ素子の記憶保持特性を向上させるように作用する。また、浮遊ゲート電極としてのゲルマニウム層にn型不純物をドーピングすることにより、伝導帯の底のエネルギーレベルをさらに下げることが出来、よりキャリアを浮遊ゲート電極に注入しやすくするように自己バイアスを作用させることができる。すなわち、書き込み電圧を下げ、不揮発性メモリ素子の記憶保持特性を向上させることができる。

In the nonvolatile memory element according to the present invention, as shown in FIGS. 2 and 3, a self-bias is generated between the channel formation region of the

以上説明したように、本発明に係る不揮発性メモリ素子は、半導体基板から浮遊ゲート電極へ電荷(キャリア)を注入しやすくすることができ、浮遊ゲート電極から電荷(キャリア)が消失することを防ぐことができる。つまり、メモリとして動作する場合に、低電圧で高効率な書き込みをすることが出来、且つ電荷保持特性を向上させることが可能となる。 As described above, the nonvolatile memory element according to the present invention can easily inject electric charges (carriers) from the semiconductor substrate to the floating gate electrode, and prevents the electric charges (carriers) from disappearing from the floating gate electrode. be able to. That is, when operating as a memory, high-efficiency writing can be performed at a low voltage, and charge retention characteristics can be improved.

このような不揮発性メモリ素子を用いて、様々な態様の不揮発性半導体記憶装置を得ることができる。図8に不揮発性メモリセルアレイの等価回路の一例を示す。1ビットの情報を記憶するメモリセルMS01は、選択トランジスタS01と不揮発性メモリ素子M01で構成されている。選択トランジスタS01は、ビット線BL0と不揮発性メモリ素子M01の間に直列に挿入され、ゲートがワード線WL1に接続されている。不揮発性メモリ素子M01のゲートはワード線WL11に接続されている。不揮発性メモリ素子M01にデータの書き込むときは、ワード線WL1とビット線BL0をHレベル、BL1をLレベルとして、ワード線WL11に高電圧を印加すると、前述のように浮遊ゲート電極に電荷(キャリア)が蓄積される。データを消去する場合には、ワード線WL1とビット線BL0をHレベルとし、ワード線WL11に負の高電圧を印加すれば良い。 Various nonvolatile semiconductor memory devices can be obtained using such a nonvolatile memory element. FIG. 8 shows an example of an equivalent circuit of a nonvolatile memory cell array. The memory cell MS01 that stores 1-bit information includes a selection transistor S01 and a nonvolatile memory element M01. The selection transistor S01 is inserted in series between the bit line BL0 and the nonvolatile memory element M01, and the gate is connected to the word line WL1. The gate of the nonvolatile memory element M01 is connected to the word line WL11. When writing data to the nonvolatile memory element M01, when the word line WL1 and the bit line BL0 are set to the H level, the BL1 is set to the L level, and a high voltage is applied to the word line WL11, the floating gate electrode is charged (carrier) as described above. ) Is accumulated. When erasing data, the word line WL1 and the bit line BL0 are set to H level, and a negative high voltage is applied to the word line WL11.

図9は、ビット線に不揮発性メモリ素子を直接接続したNOR型の等価回路を示している。このメモリセルアレイは、ワード線WLとビット線BLが互いに交差して配設し、各交差部に不揮発性メモリ素子を配置している。NOR型は、個々の不揮発性メモリ素子のドレインをビット線BLに接続する。ソース線SLには不揮発性メモリ素子のソースが共通接続される。 FIG. 9 shows a NOR-type equivalent circuit in which a nonvolatile memory element is directly connected to a bit line. In this memory cell array, word lines WL and bit lines BL are arranged so as to intersect with each other, and nonvolatile memory elements are arranged at each intersection. In the NOR type, the drain of each nonvolatile memory element is connected to the bit line BL. The sources of the nonvolatile memory elements are commonly connected to the source line SL.

NOR型の動作は、例えば、次の通りである。データ書き込みは、ソース線SLを0Vとし、データを書込むために選択されたワード線WLに高電圧を与え、ビット線BLにはデータ”0”と”1”に応じた電位を与える。例えば、”0”と”1”に対してそれぞれHレベル、Lレベルの電位をビット線BLに付与する。”0”データを書き込むべく、Hレベルが与えられた不揮発性メモリ素子ではドレイン近傍でホットエレクトロンが発生し、これが浮遊ゲート電極に注入される。”1”データの場合この様な電子注入は生じない。 The NOR type operation is, for example, as follows. In data writing, the source line SL is set to 0 V, a high voltage is applied to the word line WL selected for writing data, and a potential corresponding to data “0” and “1” is applied to the bit line BL. For example, H level and L level potentials are applied to the bit line BL for “0” and “1”, respectively. In order to write “0” data, in the nonvolatile memory element to which the H level is given, hot electrons are generated near the drain and injected into the floating gate electrode. In the case of “1” data, such electron injection does not occur.

“0”データが与えられたメモリセルでは、ドレインとソースとの間の強い横方向電界により、ドレインの近傍でホットエレクトロンが生成され、これが浮遊ゲート電極に注入される。これにより、浮遊ゲート電極に電子が注入されてしきい値電圧が高くなった状態が”0”である。”1”データの場合はホットエレクトロンが生成されず、浮遊ゲート電極に電子が注入されずしきい値電圧の低い状態、すなわち消去状態が保持される。 In the memory cell to which “0” data is given, hot electrons are generated in the vicinity of the drain due to a strong lateral electric field between the drain and the source, and this is injected into the floating gate electrode. As a result, the state in which the threshold voltage is increased by the injection of electrons into the floating gate electrode is “0”. In the case of “1” data, hot electrons are not generated, electrons are not injected into the floating gate electrode, and a low threshold voltage state, that is, an erased state is maintained.

データを消去するときは、ソース線SLに10V程度の正の電圧を印加し、ビット線BLは浮遊状態としておく。そしてワード線WLに負の高電圧を印加して(制御ゲートに負の高電圧を印加して)、浮遊ゲート電極から電子を引き抜く。これにより、データ”1”の消去状態になる。 When erasing data, a positive voltage of about 10 V is applied to the source line SL, and the bit line BL is left floating. Then, a negative high voltage is applied to the word line WL (a negative high voltage is applied to the control gate), and electrons are extracted from the floating gate electrode. As a result, the data “1” is erased.

データ読み出しは、ソース線SLを0Vにすると共にビット線BLを0.8V程度とし、選択されたワード線WLに、データ”0”と”1”のしきい値の中間値に設定された読み出し電圧を与え、不揮発性メモリ素子の電流引き込みの有無を、ビット線BLに接続されるセンスアンプで判定することにより行う。 For data reading, the source line SL is set to 0V and the bit line BL is set to about 0.8V, and the selected word line WL is set to an intermediate value between the threshold values of data “0” and “1”. A voltage is applied, and the presence / absence of current draw in the nonvolatile memory element is determined by a sense amplifier connected to the bit line BL.

図10は、NAND型メモリセルアレイの等価回路を示す。ビット線BLには、複数の不揮発性メモリ素子を直列に接続したNANDセルNS1が接続されている。複数のNANDセルが集まってブロックBLKを構成している。図10で示すブロックBLK1のワード線は32本である(ワード線WL0乃至WL31)。ブロックBLK1の同一行に位置する不揮発性メモリ素子には、この行に対応するワード線が共通接続されている。 FIG. 10 shows an equivalent circuit of the NAND memory cell array. A NAND cell NS1 in which a plurality of nonvolatile memory elements are connected in series is connected to the bit line BL. A plurality of NAND cells gather to constitute a block BLK. The block BLK1 shown in FIG. 10 has 32 word lines (word lines WL0 to WL31). The nonvolatile memory elements located in the same row of the block BLK1 are commonly connected to word lines corresponding to this row.

書込み動作では、NANDセルNS1が消去状態、つまりNANDセルNS1の各不揮発性メモリ素子のしきい値が負電圧の状態にしてから実行される。書込みは、ソース線SL側の不揮発性メモリ素子M0から順に行う。不揮発性メモリ素子M0への書込みを例として説明すると概略以下のようになる。 The write operation is executed after the NAND cell NS1 is in the erased state, that is, the threshold value of each nonvolatile memory element of the NAND cell NS1 is in a negative voltage state. Writing is performed in order from the nonvolatile memory element M0 on the source line SL side. An example of writing to the non-volatile memory element M0 is as follows.

書込みは、NANDセルが消去状態、つまりNANDセルの各メモリセルのしきい値が負電圧の状態にしてから実行される。図11(A)は、”0”書込みをする場合、選択ゲート線SG2に例えばVcc(電源電圧)を印加して選択トランジスタS2をオンにすると共にビット線BLを0V(接地電圧)にする。選択ゲート線SG1は0Vとして、選択トランジスタS1はオフとする。次に、不揮発性メモリ素子M0のワード線WL0を高電圧Vpgm(20V程度)とし、これ以外のワード線を中間電圧Vpass(10V程度)にする。ビット線BL0の電圧は0Vなので、選択された不揮発性メモリ素子M0のチャネル形成領域の電位は0Vとなる。ワード線WL0とチャネル形成領域との間の電位差が大きいため、不揮発性メモリ素子M0の浮遊ゲート電極には前述のようにF−Nトンネル電流により電子が注入される。これにより、不揮発性メモリ素子M0のしきい値電圧が正の状態(”0”が書込まれた状態)となる。 Writing is executed after the NAND cell is in the erased state, that is, the threshold value of each memory cell of the NAND cell is in a negative voltage state. In FIG. 11A, when “0” is written, for example, Vcc (power supply voltage) is applied to the selection gate line SG2 to turn on the selection transistor S2 and to set the bit line BL to 0 V (ground voltage). The selection gate line SG1 is set to 0V, and the selection transistor S1 is turned off. Next, the word line WL0 of the nonvolatile memory element M0 is set to the high voltage Vpgm (about 20V), and the other word lines are set to the intermediate voltage Vpass (about 10V). Since the voltage of the bit line BL0 is 0V, the potential of the channel formation region of the selected nonvolatile memory element M0 is 0V. Since the potential difference between the word line WL0 and the channel formation region is large, electrons are injected into the floating gate electrode of the nonvolatile memory element M0 by the FN tunnel current as described above. As a result, the threshold voltage of the nonvolatile memory element M0 becomes positive (a state in which “0” is written).

一方”1”書込みをする場合は、図11(B)に示すように、ビット線BLを例えばVcc(電源電圧)にする。選択ゲート線SG2の電圧がVccであるため、選択トランジスタS2のしきい値電圧Vthに対して、VccマイナスVth(Vcc−Vth)になると、選択トランジスタS2がカットオフする。従って、不揮発性メモリ素子M0のチャネル形成領域はフローティング状態となる。次に、ワード線WL0に高電圧Vpgm(20V)、それ以外のワード線に中間電圧Vpass(10V)の電圧を印加すると、各ワード線とチャネル形成領域との容量カップリングにより、チャネル形成領域の電圧がVcc−Vthから上昇し例えば8V程度となる。チャネル形成領域の電圧が高電圧に昇圧されるため、”0”の書込みの場合と異なり、ワード線WL0とチャネル形成領域の間の電位差が小さい。したがって、不揮発性メモリ素子M0の浮遊ゲート電極には、F−Nトンネル電流による電子注入が起こらない。よって、不揮発性メモリ素子M0のしきい値は、負の状態(”1”が書込まれた状態)に保たれる。 On the other hand, when "1" is written, the bit line BL is set to Vcc (power supply voltage), for example, as shown in FIG. Since the voltage of the selection gate line SG2 is Vcc, the selection transistor S2 is cut off when Vcc minus Vth (Vcc−Vth) with respect to the threshold voltage Vth of the selection transistor S2. Accordingly, the channel formation region of the nonvolatile memory element M0 is in a floating state. Next, when the high voltage Vpgm (20 V) is applied to the word line WL0 and the intermediate voltage Vpass (10 V) is applied to the other word lines, the capacitive coupling between each word line and the channel formation region causes the channel formation region. The voltage rises from Vcc-Vth and becomes about 8V, for example. Since the voltage of the channel formation region is boosted to a high voltage, the potential difference between the word line WL0 and the channel formation region is small unlike the case of writing “0”. Therefore, electron injection due to the FN tunnel current does not occur in the floating gate electrode of the nonvolatile memory element M0. Therefore, the threshold value of the nonvolatile memory element M0 is kept in a negative state (a state where “1” is written).

消去動作をする場合は、図12(A)に示すように、選択されたブロック内の全てのワード線を0Vとして、pウエルに負の高電圧(Vers)を印加する。ビット線BL、ソース線SLはフローティング状態とする。これにより、ブロックの全てのメモリセルにおいて浮遊ゲート電極中の電子がトンネル電流により半導体基板に放出される。この結果、これらのメモリセルのしきい値電圧が負方向にシフトする。 When performing the erase operation, as shown in FIG. 12A, all the word lines in the selected block are set to 0 V, and a negative high voltage (Vers) is applied to the p-well. The bit line BL and the source line SL are in a floating state. Thereby, electrons in the floating gate electrode are emitted to the semiconductor substrate by the tunnel current in all the memory cells of the block. As a result, the threshold voltages of these memory cells shift in the negative direction.

図12(B)に示す読み出し動作では、読出しの選択がされた不揮発性メモリ素子M0のワード線WL0を電圧Vr(例えば0V)とし、非選択のメモリセルのワード線WL1乃至WL31及び選択ゲート線SG1、SG2を電源電圧より少し高い読出し用中間電圧Vreadとする。すなわち、図13に示すように、選択メモリ素子以外のメモリ素子はトランスファートランジスタとして働く。これにより、読出しの選択がされた不揮発性メモリ素子M0に電流が流れるか否かを検出する。つまり、不揮発性メモリ素子M0に記憶されたデータが”0”の場合、不揮発性メモリ素子M0はオフなので、ビット線BLは放電しない。一方、”1”の場合、不揮発性メモリ素子M0はオンするので、ビット線BLが放電する。 In the reading operation shown in FIG. 12B, the word line WL0 of the nonvolatile memory element M0 selected for reading is set to the voltage Vr (for example, 0 V), and the word lines WL1 to WL31 and the selection gate lines of the unselected memory cells. SG1 and SG2 are read intermediate voltages Vread that are slightly higher than the power supply voltage. That is, as shown in FIG. 13, the memory elements other than the selected memory element function as transfer transistors. Thus, it is detected whether or not a current flows through the nonvolatile memory element M0 selected for reading. That is, when the data stored in the nonvolatile memory element M0 is “0”, the nonvolatile memory element M0 is off, and the bit line BL is not discharged. On the other hand, in the case of “1”, since the nonvolatile memory element M0 is turned on, the bit line BL is discharged.

図14は、不揮発性半導体記憶装置の回路ブロック図の一例を示している。不揮発性半導体記憶装置は、メモリセルアレイ52と周辺回路54が同一の基板上に形成されている。メモリセルアレイ52は、図8、図9、図10で示すような構成を有している。周辺回路54の構成は以下の通りである。

FIG. 14 shows an example of a circuit block diagram of a nonvolatile semiconductor memory device. In the nonvolatile semiconductor memory device, the

ワード線選択のためにロウデコーダ62と、ビット線選択のためにカラムデコーダ64が、メモリセルアレイ52の周囲に設けられている。アドレスは、アドレスバッファ56を介してコントロール回路58に送られ、内部ロウアドレス信号及び内部カラムアドレス信号がそれぞれロウデコーダ62及びカラムデコーダ64に転送される。

A

データ書き込み及び消去には、電源電位を昇圧した電位が用いられる。このため、コントロール回路58により動作モードに応じて制御される昇圧回路60が設けられている。昇圧回路60の出力はロウデコーダ62やカラムデコーダ64を介して、ワード線WLやビット線BLに供給される。センスアンプ66はカラムデコーダ64から出力されたデータが入力される。センスアンプ66により読み出されたデータは、データバッファ68に保持され、コントロール回路58からの制御により、データがランダムアクセスされ、データ入出力バッファ70を介して出力されるようになっている。書き込みデータは、データ入出力バッファ70を介してデータバッファ68に一旦保持され、コントロール回路58の制御によりカラムデコーダ64に転送される。

For writing and erasing data, a potential obtained by boosting the power supply potential is used. Therefore, a

次いで、上記した不揮発性半導体記憶装置について、実施例により詳細に説明する。以下に説明する本発明の構成において、同じ要素を指す符号は異なる図面で共通して用い、その場合における繰り返しの説明は省略する場合がある。 Next, the above-described nonvolatile semiconductor memory device will be described in detail with reference to examples. In the structure of the present invention described below, reference numerals indicating the same elements are used in common in different drawings, and repetitive description in that case may be omitted.

本実施例では、不揮発性半導体記憶装置の一例に関して図面を参照して説明する。以下の説明では、不揮発性半導体記憶装置において、メモリ部を構成する不揮発性メモリ素子と、当該メモリ部と同一の基板上に設けられメモリ部の制御等を行うロジック部を構成するトランジスタ等の素子とを同時に形成する場合を示す。 In this embodiment, an example of a nonvolatile semiconductor memory device will be described with reference to the drawings. In the following description, in a nonvolatile semiconductor memory device, a non-volatile memory element that forms a memory unit, and an element such as a transistor that forms a logic unit that is provided on the same substrate as the memory unit and controls the memory unit. Are shown simultaneously.

まず、不揮発性半導体記憶装置におけるメモリ部の模式図を図8に示す。 First, FIG. 8 shows a schematic diagram of a memory portion in a nonvolatile semiconductor memory device.

本実施例で示すメモリ部は、選択トランジスタと不揮発性メモリ素子を有するメモリセルが複数設けられている。図8では、選択トランジスタS01と不揮発性メモリ素子M01により一つのメモリセルが形成されている。また、同様に、選択トランジスタS02と不揮発性メモリ素子M02、選択トランジスタS03と不揮発性メモリ素子M03、選択トランジスタS11と不揮発性メモリ素子M11、選択トランジスタS12と不揮発性メモリ素子M12、選択トランジスタS13と不揮発性メモリ素子M13とによりメモリセルが形成されている。 In the memory portion shown in this embodiment, a plurality of memory cells each including a selection transistor and a nonvolatile memory element are provided. In FIG. 8, one memory cell is formed by the select transistor S01 and the nonvolatile memory element M01. Similarly, the selection transistor S02 and the nonvolatile memory element M02, the selection transistor S03 and the nonvolatile memory element M03, the selection transistor S11 and the nonvolatile memory element M11, the selection transistor S12 and the nonvolatile memory element M12, and the selection transistor S13 and the nonvolatile transistor A memory cell is formed by the volatile memory element M13.

選択トランジスタS01のゲート電極はワード線WL1に接続され、ソース又はドレインの一方はビット線BL0に接続され、他方は不揮発性メモリ素子M01のソース又はドレインに接続されている。また、不揮発性メモリ素子M01のゲート電極はワード線WL11に接続され、ソース又はドレインの一方は選択トランジスタS01のソース又はドレインに接続され、他方はソース線SL0に接続されている。 The gate electrode of the selection transistor S01 is connected to the word line WL1, one of the source and the drain is connected to the bit line BL0, and the other is connected to the source or the drain of the nonvolatile memory element M01. The gate electrode of the nonvolatile memory element M01 is connected to the word line WL11, one of the source and the drain is connected to the source or the drain of the selection transistor S01, and the other is connected to the source line SL0.

なお、メモリ部に設けられる選択トランジスタは、ロジック部に設けられるトランジスタと比較して駆動電圧が高いため、メモリ部に設けるトランジスタとロジック部に設けるトランジスタのゲート絶縁膜等を異なる厚さで形成することが好ましい。例えば、駆動電圧が小さくしきい値電圧のばらつきを小さくしたい場合にはゲート絶縁膜が薄いトランジスタを設けることが好ましく、駆動電圧が大きくゲート絶縁膜の耐圧性が求められる場合にはゲート絶縁膜が厚いトランジスタを設けることが好ましい。 Note that since the selection transistor provided in the memory portion has a higher driving voltage than the transistor provided in the logic portion, the gate insulating film of the transistor provided in the memory portion and the transistor provided in the logic portion are formed with different thicknesses. It is preferable. For example, it is preferable to provide a transistor with a thin gate insulating film when the driving voltage is small and it is desired to reduce the variation in threshold voltage. When the driving voltage is large and the gate insulating film is required to have a withstand voltage, the gate insulating film is It is preferable to provide a thick transistor.

従って、本実施例では、駆動電圧が小さくしきい値電圧のばらつきを小さくしたいロジック部のトランジスタに対しては膜厚が小さい絶縁層を形成し、駆動電圧が大きくゲート絶縁膜の耐圧性が求められるメモリ部のトランジスタに対しては膜厚が大きい絶縁層を形成する場合に関して以下に図面を参照して説明する。なお、図17乃至図20において、A−B間及びC−D間はロジック部に設けられるトランジスタを示し、E−F間はメモリ部に設けられる不揮発性メモリ素子を示し、G−H間はメモリ部に設けられるトランジスタを示している。また、本実施例では、A−B間に設けられるトランジスタをpチャネル型、C−D間、G−H間に設けるトランジスタをnチャネル型、E−F間に設けられる不揮発性メモリ素子のキャリアの移動を電子で行う場合に関して説明するが、本発明の不揮発性半導体装置はこれに限られるものでない。 Therefore, in this embodiment, an insulating layer with a small film thickness is formed for a transistor in the logic portion where the driving voltage is small and the threshold voltage variation is to be small, and the withstand voltage of the gate insulating film is required to be large. A case where an insulating layer having a large film thickness is formed for a transistor in a memory portion will be described below with reference to the drawings. Note that in FIGS. 17 to 20, between AB and CD are transistors provided in the logic portion, between EF are nonvolatile memory elements provided in the memory portion, and between GH are A transistor provided in the memory portion is shown. In this embodiment, a transistor provided between A and B is a p-channel type, a transistor provided between C and D, a transistor provided between GH is an n channel type, and a carrier of a nonvolatile memory element provided between EF However, the nonvolatile semiconductor device of the present invention is not limited to this.

まず、基板100に素子を分離した領域104、106、108、110を形成し、当該領域104、106、108、110の表面に第1の絶縁層112、114、116、118を形成する。そして、当該第1の絶縁層112、114、116、118を覆うように後に完成する不揮発性メモリ素子において浮遊ゲート電極を形成する第1導電層120及び第2導電層123を積層して形成する(図17(A)参照)。基板100に設けられた領域104、106、108、110は、それぞれ絶縁層102(フィールド酸化膜ともいう)によって分離されている。また、本例では、基板100としてn型の導電型を有する単結晶シリコン基板を用い、基板100の領域106、108、110にpウェル107を設けた例を示している。

First,

また、基板100は、半導体基板であれば特に限定されず用いることができる。例えば、n型又はp型の導電型を有する単結晶シリコン基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板等)、貼り合わせ法またはSIMOX(Separation by IMplanted OXygen)法を用いて作製されたSOI(Silicon on Insulator)基板等を用いることができる。

The

素子が分離された領域104、106、108、110は、選択酸化法(LOCOS(Local Oxidation of Silicon)法)又はトレンチ分離法等を適宜用いることができる。

For the

また、基板100の領域106、108、110に形成されたpウェルは、基板100にp型の導電型を有する不純物元素を選択的に導入することによって形成することができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。

The p well formed in the

なお、本実施例では、基板100としてn型の導電型を有する半導体基板を用いているため、領域104には不純物元素の導入を行っていないが、n型を示す不純物元素を導入することにより領域104にnウェルを形成してもよい。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。一方、p型の導電型を有する半導体基板を用いる場合には、領域104にn型を示す不純物元素を導入してnウェルを形成し、領域106、108、110には不純物元素の導入を行わない構成としてもよい。

Note that in this embodiment, since a semiconductor substrate having n-type conductivity is used as the

第1の絶縁層112、114、116、118は、熱処理を行い基板100に設けられた領域104、106、108、110の表面を酸化させることにより酸化シリコン膜で形成することができる。また、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸素と窒素を含有したシリコン膜(酸化窒化シリコン膜)との積層構造で形成することができる。

The first insulating

他にも、プラズマ処理を用いて第1の絶縁層112、114、116、118を形成してもよい。例えば、基板100に設けられた領域104、106、108、110の表面に高密度プラズマ処理により酸化処理又は窒化処理を行うことにより、第1の絶縁層112、114、116、118として酸化シリコン(SiOx)膜又は窒化シリコン(SiNx)膜を形成することができる。また、高密度プラズマ処理により領域104、106、108、110の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、領域104、106、108、110の表面に接して酸化シリコン膜が形成され、当該酸化シリコン膜上に酸化窒化シリコン膜が形成され、第1の絶縁層112、114、116、118は酸化シリコン膜と酸化窒化シリコン膜とが積層された膜となる。また、熱酸化法により領域104、106、108、110の表面に酸化シリコン膜を形成した後に高密度プラズマ処理により酸化処理又は窒化処理を行ってもよい。

In addition, the first insulating

本例では、第1の絶縁層112、114、116、118を1nm以上10nm以下、好ましくは1nm以上5nm以下で形成する。例えば、熱処理により領域104、106、108、110に酸化処理を行い当該領域104、106、108、110の表面に概略5nmの酸化シリコン膜を形成した後、高密度プラズマ処理により窒化処理を行い酸化シリコン膜の表面又は表面の近傍に窒素プラズマ処理層を形成する。具体的には、まず、酸素雰囲気下のプラズマ処理により領域104、106、108、110上に3nm以上6nm以下の厚さで酸化シリコン層を形成する。その後、続けて窒素雰囲気下でプラズマ処理を行うことにより酸化シリコン層の表面又は表面近傍に窒素濃度の高い窒素プラズマ処理層を設ける。本例では、窒素雰囲気下でプラズマ処理を行うことによって、酸化シリコン層の表面から概略1nmの深さに窒素を20原子%乃至50原子%の割合で含有させた構造とする。窒素プラズマ処理層には、酸素と窒素を含有したシリコン(酸化窒化シリコン)が形成されている。また、このとき、熱処理と高密度プラズマ処理による窒化処理は大気に一度も曝されることなく連続して行うことが好ましい。熱処理と高密度プラズマ処理を連続して行うことによって、汚染物の混入の防止や生産効率の向上を実現することができる。

In this example, the first insulating

なお、高密度プラズマ処理により被処理物(本例では基板100)を酸化する場合には、酸素を含む雰囲気下(例えば、酸素(O2)又は一酸化二窒素(N2O)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、若しくは酸素又は一酸化二窒素と水素(H2)と希ガス雰囲気下)で行う。一方、高密度プラズマ処理により被処理物を窒化する場合には、窒素を含む雰囲気下(例えば、窒素(N2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下、窒素と水素と希ガス雰囲気下、若しくはNH3と希ガス雰囲気下)でプラズマ処理を行う。

Note that when an object to be processed (the

希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。高密度プラズマ処理を希ガス雰囲気中で行った場合、第1の絶縁層112、114、116、118は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる場合があり、Arを用いた場合には第1の絶縁層112、114、116、118にArが含まれている場合がある。

As the rare gas, for example, Ar can be used. A gas in which Ar and Kr are mixed may be used. When the high-density plasma treatment is performed in a rare gas atmosphere, the first insulating

また、高密度プラズマ処理は、上記ガスの雰囲気中において、電子密度が1×1011cm−3以上であり、プラズマの電子温度が1.5eV以下で行う。より詳しくは、電子密度が1×1011cm−3以上1×1013cm−3以下で、プラズマの電子温度が0.5eV以上1.5eV以下で行う。プラズマの電子密度が高密度であり、基板100上に形成された被処理物(本例では、基板100)付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化または窒化することよって形成される酸化物または窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、且つ緻密な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で酸化または窒化処理を行うことができる。プラズマを形成するための周波数としては、マイクロ波(例えば、2.45GHz)等の高周波を用いることができる。

The high-density plasma treatment is performed in an atmosphere of the above gas at an electron density of 1 × 10 11 cm −3 or more and an electron temperature of plasma of 1.5 eV or less. More specifically, the electron density is 1 × 10 11

本実施例では、高密度プラズマ処理により被処理物の酸化処理を行う場合、酸素(O2)、水素(H2)とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、酸素を0.1sccm乃至100sccm、水素を0.1sccm乃至100sccm、アルゴンを100sccm乃至5000sccmとして導入すればよい。なお、酸素:水素:アルゴン=1:1:100の比率で混合ガスを導入することが好ましい。例えば、酸素を5sccm、水素を5sccm、アルゴンを500sccmとして導入すればよい。 In this embodiment, when an object to be processed is oxidized by high-density plasma treatment, a mixed gas of oxygen (O 2 ), hydrogen (H 2 ), and argon (Ar) is introduced. The mixed gas used here may be introduced with oxygen at 0.1 sccm to 100 sccm, hydrogen at 0.1 sccm to 100 sccm, and argon at 100 sccm to 5000 sccm. Note that the mixed gas is preferably introduced at a ratio of oxygen: hydrogen: argon = 1: 1: 100. For example, oxygen may be introduced at 5 sccm, hydrogen at 5 sccm, and argon at 500 sccm.

また、高密度プラズマ処理により窒化処理を行う場合、窒素(N2)とアルゴン(Ar)との混合ガスを導入する。ここで用いる混合ガスは、窒素を20sccm乃至2000sccm、アルゴンを100sccm乃至10000sccmとして導入すればよい。例えば、窒素を200sccm、アルゴンを1000sccmとして導入すればよい。 In addition, when performing nitriding treatment by high-density plasma treatment, a mixed gas of nitrogen (N 2 ) and argon (Ar) is introduced. The mixed gas used here may be introduced at 20 sccm to 2000 sccm for nitrogen and 100 sccm to 10000 sccm for argon. For example, nitrogen may be introduced at 200 sccm and argon at 1000 sccm.

本実施例では、基板100において、メモリ部に設けられた領域108上に形成される第1の絶縁層116は、後に完成する不揮発性メモリ素子において、トンネル絶縁膜として機能する。従って、第1の絶縁層116の膜厚が薄いほど、トンネル電流が流れやすく、メモリとして高速動作が可能となる。また、第1の絶縁層116の膜厚が薄いほど、後に形成される浮遊ゲート電極に低電圧で電荷(キャリア)を蓄積させることが可能となるため、不揮発性半導体記憶装置の消費電力を低減することができる。そのため、第1の絶縁層112、114、116、118は、膜厚を薄く形成することが好ましい。

In this embodiment, in the

第1導電層120は、ゲルマニウム(Ge)又はシリコンゲルマニウム合金等のゲルマニウムを含む膜で形成する。本例では、第1導電層120として、ゲルマニウム元素を含む雰囲気中(例えば、GeH4)でプラズマCVD法を行うことにより、ゲルマニウムを主成分とする膜を1nm以上20nm以下、好ましくは1nm以上10nm以下で形成する。具体的には、水素で5%乃至10%に希釈されたゲルマン(GeH4)ガスを用い、基板100の加熱温度を200℃乃至350℃として、13.56MHz乃至60MHz(例えば、27MHz)の高周波電力を印加することで、ゲルマニウム層を形成することができる。

The first

第2導電層123は、金属若しくはその合金、又は金属化合物で形成する。例えば、タンタル膜を1nm以上20nm以下、好ましくは1nm以上10nm以下で形成する。その他にも、タングステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、ニッケル(Ni)などの高融点金属を用いることができる。また、合金を形成する材料として、上記高融点金属に、ニオブ(Nb)、ジルコニウム(Zr)、セリウム(Ce)、トリウム(Th)、ハフニウム(Hf)を用いても良い。また、当該高融点金属の酸化物若しくは窒化物を用いることもできる。金属窒化物としては、窒化タンタル、窒化タングステン、窒化モリブデン、窒化チタンなどを用いることができる。金属酸化物としては、酸化タンタル、酸化チタン、酸化モリブデンなどを用いることができる。第2導電層123はスパッタリング法、電子ビーム蒸着法などで形成することができる。第2導電層123をスパッタリング法で形成する場合には、対象となる金属のターゲトを用いれば良い。また、金属酸化物又は金属窒化物を形成する場合には、反応性スパッタリング若しくは当該金属酸化物又は金属窒化物のターゲットを用いて成膜すれば良い。このように、後に第2の浮遊ゲート電極層125となる第2導電層123を金属等で形成することにより、第1導電層120から形成される第1の浮遊ゲート電極層121の安定化を図ることができる。

The second

また、基板100として単結晶シリコン基板を用い、当該シリコン基板のある領域上にトンネル絶縁膜として機能する第1の絶縁層を介してシリコンよりエネルギーギャップの小さいゲルマニウムを含む膜を浮遊ゲート電極を形成する第1導電層120として設けた場合、シリコン基板のある領域の電荷(キャリア)に対する絶縁層により形成される第1の障壁に対して浮遊ゲート電極の電荷(キャリア)に対する絶縁層により形成される第2の障壁がエネルギー的に高くなる。その結果、シリコン基板のある領域から浮遊ゲート電極へ電荷(キャリア)を注入しやすくすることができ、浮遊ゲート電極から電荷(キャリア)が消失することを防ぐことができる。つまり、メモリとして動作する場合に、低電圧で高効率な書き込みをすることが出来、且つ電荷保持特性を向上させることができる。また、基板100において、メモリ部に設けられた領域108上に形成される第1導電層120及び第2導電層123を含む積層構造は、後に完成する不揮発性メモリ素子において、浮遊ゲート電極として機能する。

In addition, a single crystal silicon substrate is used as the

次に、基板100の領域104、106、110上に形成された、第1の絶縁層112、114、118と第1導電層120、第2導電層123を含む積層構造を選択的に除去し、領域108上に形成された、第1の絶縁層116と第1導電層120及び第2導電層123を含む積層構造を残存させる。本例では、基板100において、メモリ部に設けられた領域108、第1の絶縁層116、第1導電層120及び第2導電層123を含む積層構造を選択的にレジストで覆い、領域104、106、110上に形成された、第1の絶縁層112、114、118と第1導電層120及び第2導電層123を含む積層構造をエッチングすることによって選択的に除去する(図17(B)参照)。

Next, the stacked structure including the first insulating

次に、基板100の領域104、106、110と、領域108の上方に形成された第1導電層120及び第2導電層123を含む積層構造の一部を選択的に覆うようにレジスト122を形成し、当該レジスト122に覆われていない第1導電層120及び第2導電層123をエッチングして選択的に除去することによって、第1導電層120及び第2導電層123を含む積層構造の一部を残存させ、第1の浮遊ゲート電極層121及び第2の浮遊ゲート電極層125を含む積層構造を形成する(図17(C)参照)。

Next, a resist 122 is applied so as to selectively cover a part of the stacked structure including the

次に、基板100の領域110の特定の領域に不純物領域を形成する。本例では、レジスト122を除去後、領域104、106、108と、領域110の一部を選択的に覆うようにレジスト124を形成し、当該レジスト124に覆われていない領域110に不純物元素を導入することによって、不純物領域126を形成する(図18(A)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。本例では、不純物元素として、リン(P)を領域110に導入する。

Next, an impurity region is formed in a specific region of the

次に、基板100の領域104、106、110と、領域108の上方に形成された第1の絶縁層116と第1の浮遊ゲート電極層121及び第2の浮遊ゲート電極層125を含む積層構造を覆うように第2の絶縁層128を形成する(図18(B)参照)。

Next, a stacked structure including the

第2の絶縁層128は、CVD法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiOxNy、(x>y>0))、窒化酸化シリコン(SiNxOy、(x>y>0))等の絶縁材料を用いて単層又は積層して形成する。例えば、第2の絶縁層128を単層で設ける場合には、CVD法により酸化窒化シリコン膜又は窒化酸化シリコン膜を5nm以上50nm以下の膜厚で形成する。また、第2の絶縁層128を3層構造で設ける場合には、第1層目の絶縁層として酸化窒化シリコン膜を形成し、第2層目の絶縁層として窒化シリコン膜を形成し、第3層目の絶縁層として酸化窒化シリコン膜を形成する。また、他にも第2の絶縁層128として、ゲルマニウムの酸化物又は窒化物を用いてもよい。

The second

なお、領域108の上方に形成された第2の絶縁層128は、後に完成する不揮発性メモリ素子においてコントロール絶縁層として機能し、領域110の上方に形成された第2の絶縁層128は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。

Note that the second insulating

次に、領域108、110の上方に形成された第2の絶縁層128を覆うようにレジスト130を選択的に形成し、領域104、106上に形成された第2の絶縁層128を選択的に除去する(図18(C)参照)。

Next, a resist 130 is selectively formed so as to cover the second insulating

次に、領域104、106を覆うように第3の絶縁層132、134をそれぞれ形成する(図19(A)参照)。

Next, third insulating

第3の絶縁層132、134は、上記第1の絶縁層112、114、116、118の形成方法で示したいずれかの方法を用いて形成する。例えば、熱処理を行い基板100に設けられた領域104、106の表面を酸化させることにより酸化シリコン膜で第3の絶縁層132、134を形成することができる。また、熱酸化法により酸化シリコン膜を形成した後に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸素と窒素を含有したシリコン膜(酸化窒化シリコン膜)との積層構造で形成してもよい。

The third insulating

他にも、上述したように、プラズマ処理を用いて第3の絶縁層132、134を形成してもよい。例えば、基板100に設けられた領域104、106の表面に高密度プラズマ処理により酸化処理又は窒化処理を行うことにより、第3の絶縁層132、134として酸化シリコン(SiOx)膜又は窒化シリコン(SiNx)膜で形成することができる。また、高密度プラズマ処理により領域104、106の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、領域104、106の表面に接して酸化シリコン膜が形成され、当該酸化シリコン膜上に酸化窒化シリコン膜が形成され、第3の絶縁層132、134は酸化シリコン膜と酸化窒化シリコン膜とが積層された膜となる。また、熱酸化法により領域104、106の表面に酸化シリコン膜を形成した後に高密度プラズマ処理により酸化処理又は窒化処理を行ってもよい。

In addition, as described above, the third insulating

なお、第3の絶縁層132、134を熱酸化法や高密度プラズマ処理で形成する際に、基板100の領域108、110の上方に形成された第2の絶縁層128の表面にも、酸化膜又は酸窒化膜が形成される場合がある。また、基板100の領域104、106に形成された第3の絶縁層132、134は、後に完成するトランジスタにおいてゲート絶縁膜として機能する。

Note that when the third insulating

次に、領域104、106の上方に形成された第3の絶縁層132、134、領域108、110の上方に形成された第2の絶縁層128を覆うように導電膜を形成する(図19(B)参照)。本例では、導電膜として、導電膜136と導電膜138を順に積層して形成した例を示している。もちろん、導電膜は、単層又は3層以上の積層構造で形成してもよい。