JP2007199708A - 表示装置及びその作製方法 - Google Patents

表示装置及びその作製方法 Download PDFInfo

- Publication number

- JP2007199708A JP2007199708A JP2006351955A JP2006351955A JP2007199708A JP 2007199708 A JP2007199708 A JP 2007199708A JP 2006351955 A JP2006351955 A JP 2006351955A JP 2006351955 A JP2006351955 A JP 2006351955A JP 2007199708 A JP2007199708 A JP 2007199708A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- film

- conductive film

- transistor

- reflective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 34

- 239000004973 liquid crystal related substance Substances 0.000 claims abstract description 66

- 239000000758 substrate Substances 0.000 claims description 68

- 239000003990 capacitor Substances 0.000 claims description 65

- 238000000034 method Methods 0.000 claims description 56

- 238000003860 storage Methods 0.000 claims description 51

- 238000005530 etching Methods 0.000 claims description 17

- 239000010408 film Substances 0.000 description 386

- 239000004065 semiconductor Substances 0.000 description 113

- 239000010410 layer Substances 0.000 description 83

- 239000000463 material Substances 0.000 description 25

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 17

- 229910052710 silicon Inorganic materials 0.000 description 17

- 229910045601 alloy Inorganic materials 0.000 description 15

- 239000000956 alloy Substances 0.000 description 15

- 230000005540 biological transmission Effects 0.000 description 15

- 229910052804 chromium Inorganic materials 0.000 description 15

- 238000001312 dry etching Methods 0.000 description 14

- 229910052715 tantalum Inorganic materials 0.000 description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 13

- 229910052750 molybdenum Inorganic materials 0.000 description 13

- 229910052719 titanium Inorganic materials 0.000 description 13

- 239000011521 glass Substances 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 11

- 230000002093 peripheral effect Effects 0.000 description 11

- 239000010703 silicon Substances 0.000 description 11

- 229910052721 tungsten Inorganic materials 0.000 description 11

- 229910052779 Neodymium Inorganic materials 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 9

- 239000013078 crystal Substances 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- 238000004544 sputter deposition Methods 0.000 description 9

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 9

- 229910001887 tin oxide Inorganic materials 0.000 description 9

- 238000002425 crystallisation Methods 0.000 description 8

- 239000011159 matrix material Substances 0.000 description 8

- 230000010355 oscillation Effects 0.000 description 8

- 238000001039 wet etching Methods 0.000 description 8

- 239000000919 ceramic Substances 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 7

- 239000011787 zinc oxide Substances 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- 238000000149 argon plasma sintering Methods 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 230000008025 crystallization Effects 0.000 description 6

- 229910052737 gold Inorganic materials 0.000 description 6

- 239000010931 gold Substances 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 6

- 239000002245 particle Substances 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- 229910052758 niobium Inorganic materials 0.000 description 5

- 239000010955 niobium Substances 0.000 description 5

- 229910052697 platinum Inorganic materials 0.000 description 5

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 5

- 229910052709 silver Inorganic materials 0.000 description 5

- 239000010944 silver (metal) Substances 0.000 description 5

- 230000005236 sound signal Effects 0.000 description 5

- 229910052725 zinc Inorganic materials 0.000 description 5

- 239000011701 zinc Substances 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- 230000001678 irradiating effect Effects 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 229910052769 Ytterbium Inorganic materials 0.000 description 3

- ZCLBLRDCYNGAGV-UHFFFAOYSA-N [Si]=O.[Sn].[In] Chemical compound [Si]=O.[Sn].[In] ZCLBLRDCYNGAGV-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 150000002739 metals Chemical class 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 229910052691 Erbium Inorganic materials 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 229910004283 SiO 4 Inorganic materials 0.000 description 2

- 229910052775 Thulium Inorganic materials 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 239000002041 carbon nanotube Substances 0.000 description 2

- 229910021393 carbon nanotube Inorganic materials 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910052839 forsterite Inorganic materials 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- HCWCAKKEBCNQJP-UHFFFAOYSA-N magnesium orthosilicate Chemical compound [Mg+2].[Mg+2].[O-][Si]([O-])([O-])[O-] HCWCAKKEBCNQJP-UHFFFAOYSA-N 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 238000007493 shaping process Methods 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- BSYNRYMUTXBXSQ-UHFFFAOYSA-N Aspirin Chemical compound CC(=O)OC1=CC=CC=C1C(O)=O BSYNRYMUTXBXSQ-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910019974 CrSi Inorganic materials 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000010893 electron trap Methods 0.000 description 1

- -1 etc. Inorganic materials 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 239000010979 ruby Substances 0.000 description 1

- 229910001750 ruby Inorganic materials 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

【解決手段】画素電極となる透明電極と反射電極を積層させる。反射電極上に半透部を有する露光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパターンを形成する。レジストパターンを用いて反射電極と透明電極とを形成する。以上により、1つのレジストマスクを用いて、反射電極と透明電極を形成することが可能となる。

【選択図】図2

Description

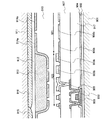

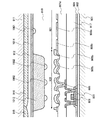

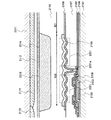

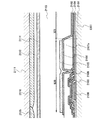

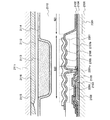

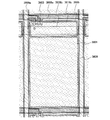

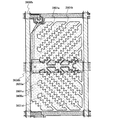

図1〜図2に、反射電極と透明電極とを形成する製造方法について述べる。

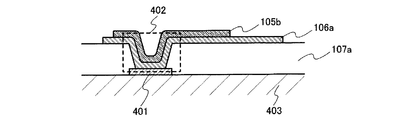

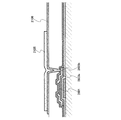

実施の形態1では、絶縁膜107の上に画素電極が形成される場合について述べた。しかし、実際には、画素電極は別の配線やトランジスタや保持容量などに接続されることになる。そのため、必要であれば、絶縁膜107にコンタクトホールを形成して、配線などと接続する必要がある。

次に、トランジスタを配置した場合の具体例について述べる。ただし、トランジスタは必ずしも必要ではなく、いわゆるパッシブマトリックス型に適用してもよい。

液晶層910には、様々な方式の液晶分子を配置することが出来る。

次に、非晶質シリコンを用いたトランジスタの場合について述べる。なお、本実施の形態で説明するTFTを構成する基板の種類、各層の形成方法及び材料等は実施の形態1〜実施の形態4を参照できる。

これまでは、主に断面図を用いて述べてきたが、本実施の形態では、上面図を述べる。

本実施の形態では、実施の形態1〜6で用いた露光マスクについて図20を用いて説明する。図20(A)〜(C)は、図1、図3、図7、図8で示した露光マスクの遮光部101a及び半透部101bの上面図を示す。露光マスクの遮光部101aの幅はt1と示し、半透部101bの幅はt2と示している。

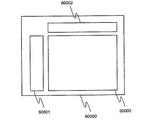

本発明の画素回路について述べる。図45に画素配列50000には、画素50001がマトリックス状に配置されている。画素50001には、ビデオ信号が入力されるソース信号線50002、ゲート信号が入力されるゲート信号線50003が接続されている。それらの信号を用いてトランジスタ50004を制御して、液晶CLC、保持容量Csにビデオ信号を入力する。保持容量Csは、保持容量線50005と接続されている。そして、ビデオ信号に応じて、液晶CLCの光透過率が変化し、画像を表示する。

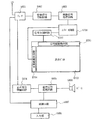

本発明の表示装置を表示部に有する携帯電話の構成例について図40を用いて説明する。

図42は表示パネル5701と、回路基板5702を組み合わせた液晶モジュールを示している。表示パネル5701は画素部5703、走査線駆動回路5704及び信号線駆動回路5705を有している。回路基板5702には、例えば、コントロール回路5706や信号分割回路5707などが形成されている。表示パネル5701と回路基板5702は接続配線5708によって接続されている。接続配線にはFPC等を用いることができる。

本発明は様々な電子機器に適用することができる。具体的には電子機器の表示部に適用することができる。そのような電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうる表示装置を備えた装置)などが挙げられる。

Claims (9)

- トランジスタと、

前記トランジスタに電気的に接続する透明電極と、

前記透明電極に電気的に接続する反射電極と

前記トランジスタに電気的に接続する保持容量と、を有し、

前記反射電極の下に、前記保持容量の少なくとも一部が形成され、

前記反射電極の下面全体が前記透明電極の上面に接していることを特徴とする表示装置。 - トランジスタと、

前記トランジスタに電気的に接続する透明電極と、

前記透明電極に電気的に接続する反射電極と、を有し、

前記透明電極もしくは前記反射電極の少なくとも1つは、スリットを有し、

前記反射電極の下面全体が前記透明電極の上面に接していることを特徴とする表示装置。 - トランジスタと、

前記トランジスタに電気的に接続する透明電極と、

前記透明電極に電気的に接続する反射電極と、

前記トランジスタに電気的に接続する保持容量と、を有し、

前記透明電極もしくは前記反射電極の少なくとも1つは、スリットを有し、

前記反射電極の下に、前記保持容量の少なくとも一部が形成され、

前記反射電極の下面全体が前記透明電極の上面に接していることを特徴とする表示装置。 - トランジスタと、

前記トランジスタに電気的に接続する透明電極と、

前記透明電極に電気的に接続する反射電極と

前記トランジスタに電気的に接続する保持容量と、を有し、

前記反射電極の下に、前記保持容量の少なくとも一部が形成され、

前記反射電極の下に、前記トランジスタの少なくとも一部が形成され、

前記反射電極の下面全体が前記透明電極の上面に接していることを特徴とする表示装置。 - トランジスタと、

前記トランジスタに電気的に接続する画素電極と、を有し、

前記画素電極は、透明電極と反射電極とを有し、

前記反射電極の下面全体が前記透明電極の上面に接しており、

前記反射電極と接する領域での前記透明電極の膜厚は、前記反射電極と接しない領域での前記透明電極の膜厚よりも厚いことを特徴とする表示装置。 - 請求項1乃至請求項5のいずれか1項において、

前記反射電極と、対向電極との間に液晶層が配置されていることを特徴とする表示装置。 - 請求項6に記載の表示装置を具備することを特徴とする電子機器。

- 基板上にトランジスタを形成し、

前記トランジスタの上に絶縁膜を形成し、

前記絶縁膜の上に透明導電膜を形成し、

前記透明導電膜の上に反射導電膜を形成し、

前記反射導電膜の上に半透部を有する露光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚の薄い領域とを有するレジストパターンを形成し、

前記レジストパターンを用いて、前記透明導電膜でなる透明電極と、前記反射導電膜でなる反射電極とを形成することを特徴とする表示装置の作製方法。 - 基板上にトランジスタを形成し、

前記トランジスタの上に絶縁膜を形成し、

前記絶縁膜の上に透明導電膜を形成し、

前記透明導電膜の上に反射導電膜を形成し、

前記反射導電膜の上に半透部を有する露光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚の薄い領域とを有するレジストパターンを形成し、

前記レジストパターンを用いて、前記反射導電膜と前記透明導電膜とをエッチングし、

前記レジストパターンの一部を除去し、

前記一部が除去されたレジストパターンを用いて、前記反射導電膜をエッチングすることを特徴とする表示装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006351955A JP2007199708A (ja) | 2005-12-28 | 2006-12-27 | 表示装置及びその作製方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005378778 | 2005-12-28 | ||

| JP2006351955A JP2007199708A (ja) | 2005-12-28 | 2006-12-27 | 表示装置及びその作製方法 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010046764A Division JP5025743B2 (ja) | 2005-12-28 | 2010-03-03 | 液晶表示装置、表示モジュール、電子機器 |

| JP2011241768A Division JP5063807B2 (ja) | 2005-12-28 | 2011-11-03 | 表示装置、表示モジュール、電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007199708A true JP2007199708A (ja) | 2007-08-09 |

| JP2007199708A5 JP2007199708A5 (ja) | 2009-12-03 |

Family

ID=38454333

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006351955A Withdrawn JP2007199708A (ja) | 2005-12-28 | 2006-12-27 | 表示装置及びその作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007199708A (ja) |

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009008892A (ja) * | 2007-06-28 | 2009-01-15 | Sumitomo Metal Mining Co Ltd | 半透過・半反射電極基板とその製造方法および半透過・半反射電極基板が用いられた半透過半反射型液晶表示装置 |

| JP2009251174A (ja) * | 2008-04-03 | 2009-10-29 | Mitsubishi Electric Corp | Tft基板及びそれを用いた液晶表示装置並びにそれらの製造方法 |

| JP2010107570A (ja) * | 2008-10-28 | 2010-05-13 | Kobe Steel Ltd | 表示装置の製造方法 |

| JP2010262007A (ja) * | 2009-04-30 | 2010-11-18 | Sony Corp | 表示装置および表示装置の製造方法 |

| JP2011022232A (ja) * | 2009-07-14 | 2011-02-03 | Sony Corp | 液晶表示装置、液晶表示装置の製造方法および電子機器 |

| JP2011186079A (ja) * | 2010-03-05 | 2011-09-22 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2012003256A (ja) * | 2010-05-20 | 2012-01-05 | Semiconductor Energy Lab Co Ltd | 液晶表示装置および液晶表示装置の作製方法 |

| KR20120031365A (ko) * | 2010-09-24 | 2012-04-03 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| JP2012137771A (ja) * | 2006-11-14 | 2012-07-19 | Mitsubishi Electric Corp | 多層薄膜パターン及び表示装置の製造方法 |

| JP2015146053A (ja) * | 2005-12-28 | 2015-08-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US9257082B2 (en) | 2009-09-04 | 2016-02-09 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US9397255B2 (en) | 2008-05-16 | 2016-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| JP2018032021A (ja) * | 2016-08-17 | 2018-03-01 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2018513413A (ja) * | 2015-06-24 | 2018-05-24 | 深▲せん▼市華星光電技術有限公司Shenzhen China Star Optoelectronics Technology Co., Ltd. | 薄膜トランジスタ配列基板及其製作方法 |

| JP2019074684A (ja) * | 2017-10-18 | 2019-05-16 | シャープ株式会社 | 表示パネル用基板の製造方法 |

| JP2020129132A (ja) * | 2020-04-28 | 2020-08-27 | 株式会社ジャパンディスプレイ | 半導体装置 |

| JP2020129113A (ja) * | 2015-08-28 | 2020-08-27 | 群創光電股▲ふん▼有限公司Innolux Corporation | 表示装置 |

| JP2021185423A (ja) * | 2013-07-10 | 2021-12-09 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2023155310A (ja) * | 2010-02-26 | 2023-10-20 | 株式会社半導体エネルギー研究所 | 表示装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002094064A (ja) * | 2000-09-11 | 2002-03-29 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ、薄膜トランジスタの製造方法、液晶表示装置およびエレクトロルミネッセンス表示装置 |

| JP2002134756A (ja) * | 2000-10-26 | 2002-05-10 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2003207774A (ja) * | 2001-10-30 | 2003-07-25 | Nec Corp | 半透過型液晶表示装置およびその製造方法 |

| JP2005258410A (ja) * | 2004-03-08 | 2005-09-22 | Samsung Electronics Co Ltd | 液晶表示装置及びその製造方法 |

| JP2005275213A (ja) * | 2004-03-26 | 2005-10-06 | Sharp Corp | 液晶表示装置 |

-

2006

- 2006-12-27 JP JP2006351955A patent/JP2007199708A/ja not_active Withdrawn

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002094064A (ja) * | 2000-09-11 | 2002-03-29 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ、薄膜トランジスタの製造方法、液晶表示装置およびエレクトロルミネッセンス表示装置 |

| JP2002134756A (ja) * | 2000-10-26 | 2002-05-10 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2003207774A (ja) * | 2001-10-30 | 2003-07-25 | Nec Corp | 半透過型液晶表示装置およびその製造方法 |

| JP2005258410A (ja) * | 2004-03-08 | 2005-09-22 | Samsung Electronics Co Ltd | 液晶表示装置及びその製造方法 |

| JP2005275213A (ja) * | 2004-03-26 | 2005-10-06 | Sharp Corp | 液晶表示装置 |

Cited By (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12189232B2 (en) | 2005-12-28 | 2025-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| US10739637B2 (en) | 2005-12-28 | 2020-08-11 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| US9703140B2 (en) | 2005-12-28 | 2017-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| US11269214B2 (en) | 2005-12-28 | 2022-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2015146053A (ja) * | 2005-12-28 | 2015-08-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US10444564B1 (en) | 2005-12-28 | 2019-10-15 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2012137771A (ja) * | 2006-11-14 | 2012-07-19 | Mitsubishi Electric Corp | 多層薄膜パターン及び表示装置の製造方法 |

| JP2009008892A (ja) * | 2007-06-28 | 2009-01-15 | Sumitomo Metal Mining Co Ltd | 半透過・半反射電極基板とその製造方法および半透過・半反射電極基板が用いられた半透過半反射型液晶表示装置 |

| JP2009251174A (ja) * | 2008-04-03 | 2009-10-29 | Mitsubishi Electric Corp | Tft基板及びそれを用いた液晶表示装置並びにそれらの製造方法 |

| US11646322B2 (en) | 2008-05-16 | 2023-05-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having conductive oxide electrode layers in direct contact with oxide semiconductor layer |

| US12300702B2 (en) | 2008-05-16 | 2025-05-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including storage capacitor having pixel electrode, directly stacked conductive layer, and insulating layer interposed between them, wherein the stacked conductive layers extending towards the gate and source wirings/lines |

| US9397255B2 (en) | 2008-05-16 | 2016-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US11133332B2 (en) | 2008-05-16 | 2021-09-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US10580797B2 (en) | 2008-05-16 | 2020-03-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| JP2010107570A (ja) * | 2008-10-28 | 2010-05-13 | Kobe Steel Ltd | 表示装置の製造方法 |

| JP2010262007A (ja) * | 2009-04-30 | 2010-11-18 | Sony Corp | 表示装置および表示装置の製造方法 |

| US8553194B2 (en) | 2009-07-14 | 2013-10-08 | Japan Display West Inc. | Liquid crystal display device, liquid crystal display device manufacturing method, and electronic device |

| JP2011022232A (ja) * | 2009-07-14 | 2011-02-03 | Sony Corp | 液晶表示装置、液晶表示装置の製造方法および電子機器 |

| US9257082B2 (en) | 2009-09-04 | 2016-02-09 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US11069817B2 (en) | 2009-09-04 | 2021-07-20 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US12557344B2 (en) | 2009-09-04 | 2026-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US10134912B2 (en) | 2009-09-04 | 2018-11-20 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US11652174B2 (en) | 2009-09-04 | 2023-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US11430899B2 (en) | 2009-09-04 | 2022-08-30 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US10700215B2 (en) | 2009-09-04 | 2020-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US12206025B2 (en) | 2009-09-04 | 2025-01-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US11935965B2 (en) | 2009-09-04 | 2024-03-19 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| JP2023155310A (ja) * | 2010-02-26 | 2023-10-20 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2011186079A (ja) * | 2010-03-05 | 2011-09-22 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2017146630A (ja) * | 2010-05-20 | 2017-08-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置および液晶表示装置の作製方法 |

| US9337218B2 (en) | 2010-05-20 | 2016-05-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and manufacturing method thereof |

| JP2012003256A (ja) * | 2010-05-20 | 2012-01-05 | Semiconductor Energy Lab Co Ltd | 液晶表示装置および液晶表示装置の作製方法 |

| KR101954981B1 (ko) * | 2010-09-24 | 2019-03-08 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR20120031365A (ko) * | 2010-09-24 | 2012-04-03 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| JP2021185423A (ja) * | 2013-07-10 | 2021-12-09 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US11869453B2 (en) | 2013-07-10 | 2024-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Display device comprising semiconductor layer having LDD regions |

| JP2018513413A (ja) * | 2015-06-24 | 2018-05-24 | 深▲せん▼市華星光電技術有限公司Shenzhen China Star Optoelectronics Technology Co., Ltd. | 薄膜トランジスタ配列基板及其製作方法 |

| US11686987B2 (en) | 2015-08-28 | 2023-06-27 | Innolux Corporation | Display device |

| JP2020129113A (ja) * | 2015-08-28 | 2020-08-27 | 群創光電股▲ふん▼有限公司Innolux Corporation | 表示装置 |

| JP7049784B2 (ja) | 2016-08-17 | 2022-04-07 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2018032021A (ja) * | 2016-08-17 | 2018-03-01 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US10620468B2 (en) | 2017-10-18 | 2020-04-14 | Sharp Kabushiki Kaisha | Method of manufacturing display panel substrate |

| JP2019074684A (ja) * | 2017-10-18 | 2019-05-16 | シャープ株式会社 | 表示パネル用基板の製造方法 |

| JP7065147B2 (ja) | 2020-04-28 | 2022-05-11 | 株式会社ジャパンディスプレイ | 半導体装置 |

| JP2020129132A (ja) * | 2020-04-28 | 2020-08-27 | 株式会社ジャパンディスプレイ | 半導体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6605050B2 (ja) | 表示装置の作製方法 | |

| JP6603425B2 (ja) | アクティブマトリクス型表示装置、携帯電話機 | |

| JP2007199708A (ja) | 表示装置及びその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091016 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091016 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111020 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111107 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120417 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120622 |