JP2006068252A - 遊技機 - Google Patents

遊技機 Download PDFInfo

- Publication number

- JP2006068252A JP2006068252A JP2004254912A JP2004254912A JP2006068252A JP 2006068252 A JP2006068252 A JP 2006068252A JP 2004254912 A JP2004254912 A JP 2004254912A JP 2004254912 A JP2004254912 A JP 2004254912A JP 2006068252 A JP2006068252 A JP 2006068252A

- Authority

- JP

- Japan

- Prior art keywords

- integrated circuit

- input

- output

- main control

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【解決手段】 基板120の基板面120aには、制御用構成要素130と入出力用構成要素140が平行に配置されている。制御用構成要素130と入出力用構成要素140は、基板に最も近い面が最も大きい面積を有する面とならないように配置されている。また、入出力用構成要素140と制御用構成要素130は、制御用構成要素130の、入出力用構成要素140に対抗する側の面に表示されている識別情報の視認が可能となるように離して配置されている。入出力用構成要素140は、セレクタ端子の組を介して入力されたセレクト信号に基づいて、データバス端子と複数のデータ端子との間のデータの入出力を行う。

【選択図】 図2

Description

主制御装置を構成する構成要素、例えば、主制御回路、記憶回路(ROMやRAM)、主制御回路と外部機器を接続するためのソケット等は、主制御基板に配置されている。各構成要素は、主制御基板に印刷されている配線パターン等の接続線によって接続されている。通常、主制御回路は、制御プログラム等を記憶している記憶回路(例えば、ROM)等とともに樹脂によってモールドされ、パッケージ化された主制御用集積回路(「ワンチップマイコン」という)として形成されている。各構成要素が配置された主制御基板は、内部が視認可能な透明性を有するケースに収納され、封印されている。

ところで、近年、遊技方法や遊技内容の複雑化や多様化に伴って、主制御回路とデータの入出力を行う外部機器(主制御基板に配置されている他の電気回路を含む)の数が増加し、また、主制御回路と外部機器との接続状態が変更されることが多くなっている。

外部機器の数が増加すると、既存の制御用集積回路に設けられているデータ端子(例えば、8個の端子によって構成される8ビットのデータ端子)の数が不足する場合がある。このような場合には、データ端子の数が多い主制御用集積回路を用いる必要がある。

また、主制御回路と外部機器との接続状態を変更する場合には、主制御用集積回路周辺の配線パターンを変更する必要がある。ここで、主制御回路は、遊技機全体の制御を行うため、多くの外部機器との間でデータの入出力を行っている。このため、主制御用集積回路周辺には多くの配線パターンが配設されており、主制御用集積回路周辺の配線パターンを変更するのは非常に困難である。

そこで、主制御用集積回路の汎用性を高め、外部機器の数の増加や主制御回路と外部機器との接続状態の変更に安価に対応できる技術の開発が要望されている。

ここで、主制御用集積回路の汎用性を高める方法として、入出力機能を拡張することができる入出力用集積回路(拡張I/Oポート機能を有する集積回路)を、主制御用集積回路と外部機器との間に設ける方法が考えられる。

この場合、主制御基板への入出力用集積回路の配置によって、他の電気回路の配置スペースが狭くなるため、主制御基板の実装効率を高める必要がある。

例えば、主制御用集積回路を不正な制御用集積回路(例えば、不正な制御プログラムを記憶しているROMを内蔵する制御用集積回路)に交換する不正が行われることがある。さらに、外観を正規の主制御用集積回路の外観に巧妙に似せた不正な制御用集積回路を用いる不正が行われることもある。この場合、このような不正を発見するのが困難である。

特に、主制御用集積回路としてDIP(Dual In-line Package)型(「横型」という)の集積回路を用いている場合、主制御基板(主制御基板の基板面)に対向する面(裏面)の面積が大きく、また、裏面と主制御基板との間の間隔が狭い。このため、主制御用集積回路が主制御基板に配置された状態では、ケースの外部から主制御用集積回路の裏面の状態を確認することができず、主制御用集積回路が不正な制御用集積回路に交換されたことや、主制御用集積回路と主制御基板との間に不正回路(例えば、不正な始動信号や入賞信号を出力する不正回路)が設けられていることを発見するのが困難である。

そこで、制御用集積回路としてZIP(Zig-zag In-line Package)型(「縦型」という)のROM内蔵の集積回路を用いた遊技機が提案されている。(特許文献1参)

縦型に形成された制御用集積回路は、制御用集積回路の面積が大きい表面及び裏面が基板の基板面から立ち上がる方向に配置されるため、ケースの外部から制御用集積回路の表面及び裏面の状態を容易に確認することができる。このため、制御用集積回路が不正な制御用集積回路に交換されたことや、制御用集積回路と基板の基板面との間に不正回路が設けられていることを容易に発見することができる。

また、縦型の形成された制御用集積回路は、基板に対向する面の面積が小さいため、基板の実装効率を高めることができる。

そこで、前記した、主制御用集積回路及び入出力用集積回路として、縦型の集積回路を用いることが考えられる。

また、主制御用集積回路と入出力用集積回路としてZIP型(縦型)の制御用集積回路を用いることにより、主制御用集積回路に対する不正を防止することができるとともに、主制御基板の実装効率を高めることができる。

したがって、主制御用集積回路及び入出力用集積回路としてZIP型(縦型)の制御用集積回路を用いた場合にも、一般的には、主制御用集積回路と入出力用集積回路は、主制御用集積回路と入出力用集積回路の間の距離が短くなるように近づけて主制御基板に配置される。

ここで、主制御用集積回路には、識別情報を表示することが義務付けられている。このため、例えば、主制御用集積回路あるいは主制御用集積回路に内蔵されている主制御回路の型番を示す文字等が印刷されたラベルが主制御用集積回路に貼付されている。

ZIP型(縦型)の主制御用集積回路と入出力用集積回路が近づけて主制御基板に配置され、また、主制御用集積回路の、入出力用集積回路に対向する側の面にラベルが貼付されている場合には、入出力用集積回路の存在によって、主制御用集積回路に貼付されているラベルに印刷されている文字等をケースの外部から視認するのが困難となる。

この場合、主制御用集積回路が、外観は正規の主制御用集積回路の外観に巧妙に似せているが、正規のシールが貼付されていない不正な制御用集積回路に交換されたことを判別するのが困難となる。

そこで、本発明が解決しようとする課題は、不正防止効果を高めながら、制御用集積回路の汎用性を高めることができる遊技機を提供することである。

請求項1に記載の遊技機では、制御用構成要素と入出力用構成要素は、基板に最も近い面が最も大きい面積を有する面とならないように基板に配置されているとともに、制御用構成要素の、入出力用構成要素に対向する側の面に表示されている識別情報の視認が可能となるように離して平行に配置されている。

「基板に最も近い面が最も大きい面積を有する面とならないように基板に配置されている」という記載は、制御用構成要素及び入出力用構成要素が基板に配置された時に、基板に最も近い面(例えば、面の中心と基板面との間の距離が最も小さい面)の面積より大きい他の面が存在する配置態様を表している。この典型的な配置態様は、制御用構成要素及び入出力用構成要素としてZIP型等の縦型の制御用集積回路を用い、制御用構成要素が基板の基板面に配置された時に、制御用構成要素の最も面積が大きい面が、基板面から略直角に立ち上がるように配置される態様である。

「制御用構成要素に表示されている識別情報」は、例えば、制御用構成要素に印刷されているあるいは制御用構成要素に貼付されているラベルに印刷されている、当該制御用構成要素あるいは当該制御用構成要素に内蔵されている制御回路の型番を示す文字等の情報を含む。

「制御用構成要素と入出力用構成要素が平行に配置される」という記載は、制御用構成要素の端子列の配列方向と入出力用構成要素の端子列の配列方向が平行になるように、制御用構成要素と入出力用構成要素が配置される構成を意味する。なお、「平行に配置される」構成には、略平行に配置される構成も含まれる。

「制御用構成要素と入出力用構成要素が、制御用構成要素の、入出力用構成要素に対向する面に表示されている識別情報の視認が可能となるように離して平行に配置されている」構成としては、制御用構成要素に表示されている識別情報全体を視認可能な距離以上離して制御用構成要素と入出力用構成要素が平行に配置されている構成や、制御用構成要素に表示されている識別情報の一部を視認可能であり、且つ、視認した識別情報の一部に基づいて識別情報全体を推定可能な距離以上離して制御用構成要素と入出力用構成要素が平行に配置されている構成を用いることができる。すなわち、必ずしも、識別情報の全体を視認可能でなくてもよい。

また、制御用構成要素及び入出力用構成要素を、基板に最も近い面が最も大きい面積を有する面とならないように基板に配置しているため、基板の実装効率を高めることができるとともに、制御用構成要素や入出力用構成要素と基板の基板面との間に不正回路が設けられていることを容易に発見することができる。

さらに、制御用構成要素に表示されている識別情報の視認が可能となるように制御用構成要素と入出力用構成要素を離して基板に平行に配置しているため、不正な制御用構成要素(例えば、外観は正規の制御用構成要素に似せているが、正規の表示情報が表示されていない不正な制御用構成要素)が設けられていることを容易に発見することができ、不正防止効果を高めることができる。

ここで、制御用構成要素と入出力用構成要素を離して配置することにより、制御用構成要素と入出力用構成要素を接続する接続線の長さが長くなるが、制御用構成要素と入出力用構成要素を平行に配置しているため、接続線の長さが長くなる量を最小限に抑えることができる。

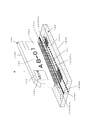

本発明の一実施の形態の遊技機に設けられる主制御基板の概略構成を示す図1に示す。また、図1のII線矢視図(矢印II方向から見た平面図)を図2に示し、図1の要部の斜視図を図3に示す。なお、図2に示されている構成要素(電気回路)の一部(例えば、発振器122)は、図1には示していない。また、図1及び図2には、主制御基板に配置される構成要素(電気回路)の全てを示していない。

本実施の形態では、パチンコ機に用いられている、主制御回路とROM等の記憶回路を内蔵する主制御用集積回路、入出力処理回路を内蔵する入出力用集積回路等が配置された主制御基板について説明する。

主制御用集積回路130、入出力用集積回路140、ソケット121、発振器122等の構成要素(電気回路)が配置された主制御基板120は、ベースとカバーからなるケース110内に収納され、封印具や封印シール等によって封印される。ケース110は、通常、ケース110が遊技機に取り付けられた状態で、係員等が、ケース外部からケース内部の状態(例えば、主制御基板120に配置されている構成要素の配置状態、構成要素の外形形状や構成要素に表示されている識別情報等)を視認可能な透明性を有する樹脂によって形成されている。

本実施の形態では、主制御用集積回路130として、ZIP型(縦型)に形成された制御用集積回路を用いている。主制御用集積回路130は、側面130a(入出力用集積回路140に対向する側の面)及び側面130b(入出力用集積回路140に対向する側と反対側の面)、底面(基板面120aに対向する面)130cを有している(図10参照)。側面130aあるいは130bが、面積が最も大きい面である。

長方形に形成されている底面130cには、長辺方向(図10では、紙面に垂直な方向)に端子131がジグザグ状に交互に配列されている。これにより、端子131の先端部によって、底面の長辺方向に平行な2列の直線状の端子列131a、131bが形成されている。

本実施の形態では、入出力用集積回路140は、主制御用集積回路130と同様に、ZIP型(縦型)に形成された入出力用集積回路を用いており、側面140a及び140b、底面140c(図示省略)を有している。

長方形に形成されている底面140cには、長辺方向に端子141がジグザグ状に交互に配列されている。これにより、端子141の先端部によって、底面の長辺方向に平行な2列の直線状の端子列141a、141bが形成されている。

本実施の形態では、主制御用集積回路130及び入出力用集積回路140として、外形形状が同じであり、端子131と141の数及び配置形状が同じである集積回路を用いている。

主制御用挿入部120CPUは、主制御用集積回路130の2列の端子列131a及び131bに対応させて配列された、平行な2列の主制御用挿入部列(主制御用接続端子列)120CPUa及び120CPUbを有している。

また、入出力用挿入部120IOは、入出力用集積回路140の2列の端子列141a及び141bに対応させて配列された、平行な2列の入出力用挿入部列(入出力用接続端子列)120IOa及び120IObを有している。

(主制御用挿入部列120CPUa及び120CPUbを形成)が本発明の「制御用接続部」に対応し、入出力用集積回路140の端子141(端子列141a及び141bを形成)が本発明の「入出力用集積回路の端子」に対応し、入出力用挿入部120IO(入出力用挿入部列120IOa及び120IObを形成)が本発明の「入出力用接続部」に対応する。

そこで、本実施の形態では、制御用挿入部120CPUの制御用挿入部列120CPUa及び120CPUbの配列方向と入出力用挿入部120IOの入出力用挿入部列120IOa及び120IObの配列方向が平行となるように、制御用挿入部120CPU及び入出力用挿入部120IOを基板120に配置することによって(すなわち、主制御用集積回路130の端子131の端子列131a及び131bの配列方向と入出力用集積回路140の端子列141a及び141bの配列方向を平行とすることによって)、制御用挿入部120と入出力用挿入部120IOの間(すなわち、主制御用集積回路130の端子131と入出力用集積回路140の端子141との間)に配設されるデータバスの長さを短くしている。本実施の形態では、このような配置状態を、「主制御用集積回路130と入出力用集積回路140が平行に制御基板120に配置されている」という。

本実施の形態では、主制御用集積回路130と入出力用集積回路140は、平行方向の配置位置が一致(略一致を含む)している、すなわち、平行方向にずれていない状態(ほとんどずれでいない状態を含む)で平行に配置されている。

そこで、本実施の形態では、主制御基板120の実装効率を高めるために、入出力用挿入部120IOの入出力用挿入部列120IOa及び120IObの配列方向(したがって、入出力用挿入部列120IOa及び120IObと平行な主制御用挿入部列120CPUa及び120CPUbの配列方向)が、主制御基板120の、長方形に形成されている基板面120aの長辺に平行(図2の左右方向)と平行になるように、入出力用挿入部120IO(したがって、制御用挿入部120CPU)を基板120に配置している、本実施の形態では、このような配置状態を、「主制御用集積回路130と入出力用集積回路140が基板120の基板面120aの長辺に平行に配置されている」という。

そこで、本実施の形態では、図1及び図2に示すように、入出力用挿入部120IO(入出力用挿入部列120IOa及び120IOb)を、主制御用挿入部120CPU(主制御用挿入部列120CPUa及び120CPUb)よりも主制御基板120の基板面120aの中央部側に配置することによって、入出力用集積回路140と他の電気回路との間に配設される接続線の長さを短くしている。

さらに、ソケット121の接続端子の配列方向と入出力用挿入部列120OIa及び120IObの配列方向が平行となるように、ソケット121を制御基板120に取り付けているこのような配置状態を、「ソケット(接続部)を入出力用集積回路140と平行に配置する」という。

なお、本明細書では、「平行」という記載は、2つの構成要素が概略平行である構成をも含むものとして用いている。また、「中央部」という記載は、中央の位置の近傍を含むものとして用いている。

主制御用集積回路130には、端子131によって2列の端子列131a(端子番号1〜32)及び131b(端子番号33〜64)が形成されている。また、入出力用集積回路140には、端子141によって2列の端子列141a(端子番号1〜32)及び141b(端子番号33〜64)が形成されている。

本実施の形態では、図4に示すように、主制御用集積回路130では、入出力用集積回路140側に配置されている端子列131aに、データを入出力するデータバス端子DBc(端子番号10〜17の端子の組)を設けている。また、入出力用集積回路140と反対側に配置されている端子列131bに、セレクトデータを出力するセレクト端子Sc(端子番号37〜44の端子の組)を設けている。

一方、入出力用集積回路140では、主制御用集積回路130側に配置される端子列141bに、データを入出力するデータバス端子DBi(端子番号42〜49の端子の組)を設けている。また、主制御用集積回路130と反対側に配置されている端子列141aに、セレクトデータを入力するセレクト端子Si(端子番号1〜8の端子の組)と、主制御基板120に配置されている他の電気回路との間でデータを入出力する複数のデータ端子D1(端子番号9〜16の端子の組)及びD2(端子番号17〜24の端子の組)を設けている。

なお、図4では、2つのデータ端子D1とD2のみを示したが、データ端子の数は主制御回路との間でデータを入出力する外部機器(主制御基板120に配置されている他の電気回路を含む)の数に応じて適宜変更される。

また、セレクト端子Sc及びSiを構成する端子の数は、セレクト信号の形態に応じて適宜設定される。例えば、セレクト端子を構成する各端子によってデータ端子を選択する場合(例えば、端子37から「H」レベルの信号を出力することによってデータ端子D1を選択する場合)には、セレクト端子は、入出力用集積回路140に設けられているデータ端子の数に等しい数の端子により構成される。あるいは、複数ビットの信号によってセレクト信号を構成する場合には、セレクト端子は、ビット数に対応する数の端子により構成される。例えば、8ビットのセレクト信号を用いる場合には、セレクト端子は、8つの端子により構成される。

このように、主制御用集積回路130の、入出力用集積回路140側の端子列120CPUaに含まれている端子をデータバス端子とし、入出力用集積回路140の、主制御用集積回路130側の端子列120IObに含まれている端子をデータバス端子として用いることにより、主制御用集積回路130と入出力用集積回路140との間に配設されるデータバスの長さを短くすることができる。

さらに、本実施の形態では、主制御用集積回路130のデータバス端子DBcと入出力用集積回路140のデータバス端子DBiの配設位置を、主制御用集積回路130と入出力用集積回路140が主制御基板120の基板面120aに配置された時に、データバス端子DBcとDBiが対向するように設定されている。

すなわち、主制御用集積回路130のデータバス端子DBcが挿入(接続)される制御用挿入部120CPUと、入出力用集積回路140のデータバス端子DBiが挿入(接続)される入出力用挿入部120IOを接続するデータバスDBLが、制御用挿入部120CPUと入出力用挿入部120IOの平行方向(主制御用集積回路130と入出力用集積回路140の平行方向)に直角(略直角を含む)な直線状(略直線状を含む)に配設可能に設定されている。

これにより、主制御用集積回路130と入出力用集積回路140との間に配設されるデータバスの長さをより短くすることができる。

また、入出力用集積回路140のデータ端子D1及びD2が挿入(接続)される入出力用挿入部120IOと、他の電気回路の端子は、対応するデータ線(基板面120aに配設された配線パターン)DL1及びDL2によって接続されている。

例えば、主制御用集積回路130に内蔵されている主制御回路から、データ線DL1にデータを出力する場合には、主制御回路は、データバス端子DBcを介してデータバスDBLにデータを出力するとともに、セレクト端子Scにデータ端子D1を示すセレクト信号を出力する。入出力用集積回路140に内蔵されている入出力処理回路は、セレクト端子Siに、データ端子D1を示すセレクト信号が入力されると、データバス端子DBiとデータ端子D1を接続し、データバスDBL上のデータを、データバス端子DBi及びデータ端子D1を介してデータ線DL1に出力する。

また、データ線DL2から主制御回路にデータを入力する場合には、主制御回路は、セレクト端子Scにデータ端子D2を示すセレクト信号を出力する。入出力用集積回路140に内蔵されている入出力処理回路は、セレクト端子Siに、データ端子D2を示すセレクト信号が入力されると、データ端子D2とデータバス端子DBiを接続し、データ線DL2上のデータを、データ端子D2及びデータバス端子DBiを介してデータバスDBLに出力する。主制御回路は、データバスDBLからデータバス端子DBcに入力されたデータを読み取る。

識別情報としては、図1に示すように、主制御用集積回路130の外周面(例えば、側面)に印刷等によって表示されている識別情報(図1では、「AB−01」)132、制御用集積回路130の外周面(例えば、側面)に貼付されたシール133に印刷等によって表示されている識別情報(図1では、「abcd」)133aが用いられる。

識別情報132としては、主制御用集積回路130(あるいは、主制御用集積回路130に内蔵されている主制御回路)の製造会社名や型番等が用いられ、識別情報133aとしては、主制御用集積回路130が設けられている遊技機の製造会社や機種名や機種番号等が用いられる。

通常、図1及び図3に示すように、主制御用集積回路130の、入出力用集積回路140に対向する側の面(側面130a)に、識別情報132が印刷されるとともに、識別情報133aが印刷されたシール133が貼付される。

このため、主制御用集積回路130に表示されている識別情報(132や133a)を確認することによって、主制御用集積回路130が不正な制御用集積回路に交換されていることを発見することができる。例えば、外観は正規の主制御用集積回路の外観に似せているが、正規の識別情報が表示されていないことを視認(確認)することによって、主制御用集積回路が不正な制御用集積回路に交換されていることを発見することができる。

主制御用集積回路130の外観や制御用集積回路130に表示されている識別情報の視認(確認)は、主制御基板120がケース110に収容されている状態で、ケース110の外部から行われる。

そこで、本実施の形態では、主制御用集積回路130と入出力用集積回路140を、主制御用集積回路130と入出力用集積回路140との間に配設される接続線の抵抗による影響や接続線へのノイズの侵入による影響よりも、不正な制御用集積回路の発見の容易性(不正防止効果の向上)を優先している。

すなわち、主制御用集積回路130と入出力用集積回路140の間の距離Hを、ケース110が遊技機に取り付けられている状態で、主制御用集積回路130の、入出力用集積回路140に対向する側の面(側面130a)に表示されている識別情報(132や133a)を、ケース110の外部から視認可能となる距離に設定している。

しかしながら、接続線の抵抗による影響や接続線へのノイズの侵入による影響を軽減し、また、制御基板120の実装効率を高めるためには、主制御用集積回路130と入出力用集積回路140の間の距離は短い方がよい。また、主制御用集積回路130に表示されている識別情報は、その一部を視認することができれば識別情報全体を推定することができる。

したがって、主制御用集積回路130と入出力用集積回路140の間の距離は、係員等が、ケース110が遊技機に取り付けられている状態で、ケース110の外部から、通常の視認姿勢で、制御用集積回路130の側面130aに表示されている識別情を視認した時に識別情報の一部を視認可能であり、且つ、視認した識別情報の一部に基づいて識別情報全体を推定可能な距離以上の距離に設定するのが好ましい。

このような距離に設定することにより、接続線の長さが長くなるのをできる限り抑制しながら、不正防止効果を高めることができる。

識別情報を視認可能な距離(識別情報全体を視認可能な距離あるいは識別情報全体を推定可能な一部の識別情報を視認可能な距離)は、ケース110が遊技機に取り付けられている位置や、ケース110の配設状態等によって異なる。

すなわち、本実施の形態で用いているZIP型(縦型)の主制御用集積回路130と同じ数の端子(64ピン)を有するDIP型(横型)の主制御用集積回路を主制御基板120に配置した場合の、主制御基板120上の実装面積(具体的には、横型の主制御用集積回路に取り付けられている端子の外周を覆う面積)に等しい領域を、ZIP型(縦型)の主制御用集積回路130の周囲に確保することができるように、主制御用集積回路130と入出力用集積回路140の距離を設定する。この領域には、配線パターン以外は配置されない。

通常、横型の主制御用集積回路を、実装面積の小さい縦型の主制御用集積回路に置き換えた場合には、縦型の主制御用集積回路を用いることによる効果を最大限に利用するために(すなわち、接続線を短くするとともに実装効率を高めるために)、縦型の主制御用集積回路の周囲には、横型の主制御用集積回路を主制御基板に配置した場合の実装面積より小さい領域しか確保されない。すなわち、主制御用集積回路と隣接する回路の間の距離は、できるだけ短い値に設定される。

本実施の形態では、接続線の長さが長くなり、また、実装効率が低下するのを許容し、不正防止効果を高めることを優先するため、縦型の主制御用集積回路を用いてはいるが、縦型の主制御用集積回路の周囲には、横型の主制御用集積回路を主制御基板に配置した場合の実装面積に等しい領域を確保している。

なお、「縦型の主制御用集積回路の周囲に、横型の主制御用集積回路を主制御基板に配置した場合の実装面積に等しい領域を確保する」方法としては、例えば、横型の主制御用集積回路と入出力用集積回路を平行に主制御基板上に配置した場合に、横型の主制御用集積回路が配置される領域(実装領域)の中央部に、縦型の主制御用集積回路の端子の配列方向が横型の主制御用集積回路の端子の配列方向と同じ方向となるように、縦型の主制御用集積回路を主制御基板に配置する。

主制御用集積回路130と入出力用集積回路140の間の距離をこのように設定することにより、主制御用集積回路130の入出力用集積回路140側の面に表示されている識別情報の視認が可能となるように、制御用集積回路と入出力用集積回路を容易に配置することができる。

図5は、主制御用集積回路130に対する不正防止効果の向上を目的とした配置例であり、図6及び図7は、主制御用集積回路130及び入出力用集積回路140に対する不正防止効果の向上を目的とした配置例である。

図5では、ZIP型の主制御用集積回路130と同じ端子の数(64ピン)を有するDIPの主制御用集積回路を主制御基板120に配置した場合の実装領域(左下がりのハッチングで示す領域)の中央部に、ZIP型の主制御用集積回路130を、ZIP型の主制御用集積回路130の端子の配列方向が、DIP型の主制御用集積回路の端子の配列方向と同じ方向(図5では、長方形の実装領域の長辺方向である上下方向)となるように配置している。そして、ZIP型の主制御用集積回路130の周囲に、DIP型の主制御用集積回路の実装領域を確保した状態で、入出力用集積回路140を配置している。DIP型の主制御用集積回路の実装領域内には、配線パターン以外の構成要素は配置されていない。

これにより、主制御用集積回路130の入出力用集積回路140側の面に表示されている識別情報の視認が可能となる。また、主制御用集積回路130の周囲に不正な回路が配設されていることを容易に発見することができる。

なお、主制御用集積回路130と入出力用集積回路140の間の距離は、図5に示す距離以上であればよい。

図6では、DIP型の主制御用集積回路の実装領域及びDIP型の入出力用集積回路の実装領域内には、配線パターン以外の構成要素は配置されていない。

これにより、主制御用集積回路130の入出力用集積回路140側の面に表示されている識別情報の視認や入出力用集積回路140の主制御用集積回路130側の面に表示されている識別情報の確認が可能となる。また、主制御用集積回路130の周囲や入出力用集積回路140の周囲に不正な回路が配設されていることを容易に発見することができる。

通常、64ピン構造のDIP型の主制御用集積回路と入出力用集積回路の実装面積はほぼ等しく、また、64ピン構造の縦型の主制御用集積回路と入出力用集積回路の実装面積はほぼ等しい。このため、図6に示すように、主制御用集積回路130の、入出力用集積回路140側の周囲に確保する領域と、入出力用集積回路140の、主制御用集積回路130側の周囲に確保する領域をほぼ100%重複させることができる。この場合、主制御用集積回路130と入出力用集積回路140の間の距離を短くすることができ、主制御基板120の実装効率を高めることができ。

なお、主制御用集積回路130と入出力用集積回路140の間の距離は、図6に示す距離以上であればよい。

この場合、不正防止効果の向上に対する要求が高い主制御用集積回路130の周囲に確保する領域内には抵抗アレイを配置しない。すなわち、図7に示すように、主制御用集積回路130の領域(左下がりのハッチングで示す、横型の主制御用集積回路の実装領域)より入出力用集積回路140側に、少なくとも抵抗アレイ125を配置するのに必要な距離Wだけ重ならない状態で、入出力用集積回路140の領域(右下がりのハッチングで示す、横型の入出力用集積回路の実装領域)が確保されるように、主制御用集積回路130と入出力用集積回路140の間の距離を設定する。

なお、主制御用集積回路130と入出力用集積回路140の間の距離は、図7に示す距離以上であればよい。

また、主制御用集積回路130の領域と入出力用集積回路140の領域が、抵抗アレイ125を配置するのに必要な距離Wだけ離れた位置に配置されるように、主制御用集積回路130と入出力用集積回路140の間の距離を設定することもできる。

本実施の形態では、主制御用集積回路130と入出力用集積回路130の間の距離を、主制御用集積回路130の入出力用集積回路140側の面に表示されている識別情報を視認可能な距離に設定することにより、不正な主制御用集積回路が配設されていることを容易に発見することができるとともに、平行に配置された縦型の主制御用集積回路130と入出力用集積回路140の間に不正な回路が配設されたことも容易に発見することができる。

ここで、主制御用集積回路130と入出力用集積回路140の間に配設されているデータバスDBLには多くの入出力信号が流れるため、データバスDBLにノイズが侵入すると主制御回路や外部機器が誤動作する恐れがある。

そこで、本実施の形態では、発振器122から発生するノイズがデータバスDBLに侵入するのを防止するように発振器122を配置している。

すなわち、図2に示すように、発振器122を、主制御用集積回路130を挟んで入出力用集積回路140と反対側に配置している。また、主制御用集積回路130の、入出力用集積回路140と対抗する側と反対側の端子列131bにクロック端子CLc(端子番号56〜59の端子の組)を設けている。そして、発振器122とクロック端子CLcを、クロック線(配線パターン)CLによって接続している。

このように、発振器122とデータバスDLBを離して配置しているため、発振器122から発生するノイズがデータバスDBLに侵入するのを防止することができ、データバスDBLを流れるデータにノイズが混入するのを防止することができる。

なお、発振器122の端子とクロック端子CLcが対向するように、発振器122の配置位置あるいはクロック端子CLcの配設位置を設定するのが好ましい。これにより、クロック線CLの長さを短くすることができる。

本実施の形態では、ソケット121を、入出力用集積回路140を挟んで主制御用集積回路130と反対側に配置している。これにより、入出力用集積回路140のデータ端子とソケット121に設けられている接続端子との間のデータ線の長さを短くすることができる。

また、ソケット121の接続端子の配列方向が入出力用挿入部列120IOa及び120IObの配列方向と平行になるように、すなわち、ソケット121と入出力用集積回路140が平行に配置されるように、ソケット121が主制御基板120に配置されている。これにより、入出力用集積回路140のデータ端子が挿入(接続)される入出力挿入部120IOとソケット121の接続端子の間、したがって、入出力用集積回路140のデータ端子とソケット121の接続端子の間のデータ線の長さを短くすることができる。

なお、ソケット121と入出力用集積回路140が主制御基板120に配置された状態で、ソケット121の接続端子と、入出力用集積回路140のデータ端子が挿入(接続)される入出力挿入部120IO(入出力用挿入部列141aの入出力用挿入部)が対向するようにソケット121の配置位置あるいは入出力用集積回路140における入出力用挿入部の配設位置を設定することにより、出力用集積回路140のデータ端子とソケット121の接続端子の間のデータ線の長さをさらに短くすることができる。

このため、入出力用集積回路140とソケット121の間の距離Kを長くして、入出力用集積回路140とソケット121との間の領域に不正な入力信号を出力する不正回路が設けられていることを容易に発見できるようにするのが好ましい。本実施の形態では、入出力用集積回路140とソケット121の間の距離Kを、主制御用集積回路130と入出力用集積回路140との間の距離Hより大きい距離に設定している。

ソケット121には、入出力用集積回路140のデータ端子D1やD2に接続されているデータ線DL1やDL2が接続される接続端子が設けられている。また、ケース110の、ソケット121に対応する箇所に孔111が設けられている。孔111にプラグ(接続部材)を挿入することによって、プラグの端子がソケットの接続端子に接続される。

なお、ソケット121の接続端子がデータ端子と対向するようにソケット121の配置位置あるいはデータ端子の配設位置を設定するのが好ましい。

この場合には、不正な回路の発見の容易性を高める(不正防止効果を高める)ために入出力用集積回路140とソケット121を離して配置することにより、入出力用集積回路140のデータ端子とソケット121の接続端子の間に配設されるデータ線の長さが長くなるのを抑制することができる。

本実施の形態では、主制御用集積回路130や入出力用集積回路140から発生したノイズが外部に放出されるのを防止するために、主制御用集積回路130や入出力用集積回路140の下方の基板面に接地線を配設している。

主制御用集積回路130の下方に接地線を配設する構成を、図8〜図10を用いて説明する。なお、図9は、図8のIX線矢視図(平面図)であり、図10は、図9のX−X線断面図である。

すなわち、図10に示すように、主制御基板120には、基板面120aと120bを貫通し、主制御用集積回路130の端子131により形成される2列の端子列131a及び131bに対応する2列の主制御用挿入部列120CPUa及び120CPUbを形成する主制御用挿入部120CPUが設けられている。

そして、基板面120a及び120bには、2列の主制御用挿入部列120CPUaと120CPUbの間に、主制御用挿入部列120CPUa及び120CPUbの配列方向に沿って接地線120Gf及び120Gbが直線状に配設されている。

本実施の形態では、接地線120Gf及び120Gbとして、主制御基板120の基板面120a及び120bに配設され、主制御基板120の接地端子に接続されている配線パターンを用いている。なお、主制御用集積回路130の端子131には接地端子が含まれており、この接地端子は、接地線120Gf及び120Gbに接続される。

接地線120Gf及び120Gbの配設位置は、2列の主制御用挿入部列120CPUaと120CPUbの間の中央部が好ましいが、2列の制御用挿入部列120CPUaと120CPUbの間であればよい。また、接地線120Gf及び120Gbは直線状でなくてもよい。

本実施の形態では、入出力用集積回路140に対しても同様の接地線120Hf及び120(図示省略)を設けている。

なお、接地線は、主制御用集積回路130あるいは入出力用集積回路140のいずれか一方に対してのみ設けてもよい。また、主制御基板120の基板面120a(実装側基板面)あるいは基板面120b(半実装側基板面)の一方側のみに設けてもよい。この場合でも、回路から発生するノイズが外部に放出するのを防止することができる。

本実施の形態では、主制御基板120の基板面120aの、主制御用集積回路130の端子列131aと131bの間あるいは入出力用集積回路140の端子列141aと14bの間に接地線120Gf、120Hfが配設されている。

このため、主制御用集積回路130の端子列131aと131bの間あるいは入出力用集積回路140の端子列141aと14bの間に不正な回路が配設されるのを防止することができる。また、不正な回路が配設された場合でも、不正な回路が配設されたことを容易に発見することができる。

また、主制御用集積回路130と入出力用集積回路140として縦型(ZIP型)の集積回路を用いているため、主制御用集積回路130や入出力用集積回路140が不正な制御用集積回路や不正な入出力用集積回路に交換されたこと、主制御用集積回路や入出力用集積回路と主制御基板との間に不正な回路が設けられていることを容易に発見することができ、不正防止効果を高めることができる。同時に、主制御用集積回路130と入出力用集積回路140の主制御基板120上での実装面積を低減することができるため、主制御基板120の実装効率を高めることができる。

さらに、縦型(ZIP型)の主制御用集積回路130と入出力用集積回路140を、主制御用集積回路130の、入出力用集積回路140と対向する側の面に表示されている識別情報を、主制御基板120を収容したケース110を遊技機に取り付けた状態で、ケース110の外部から視認可能となるように離して平行に主制御基板120に配置しているため、主制御用集積回路130と入出力用集積回路140の間に配設されるデータバスの長さが長くなる量を最小限に抑えながら、外観を正規の主制御用集積回路に似せているが正規の識別情報が表示されていない不正な制御用集積回路が設けられていることを容易に発見することができる。これにより、主制御用集積回路130と入出力用集積回路との間に配設されるデータバスの抵抗による影響やデータバスへのノイズの侵入を最小限に抑えながら、不正防止効果をより高めることができる。さらに、主制御用集積回路130と入出力用集積回路140の間に不正な回路が設けられたことを容易に発見することができる。

また、入出力用集積回路140を主制御用集積回路130より、主制御基板120の基板面120aの中心部側に配置しているため、入出力用集積回路140と他の電気回路の間に配設される接続線を短くすることができる。

また、主制御用集積回路130、入出力用集積回路140、ソケット121を、主制御基板120の長方形の基板面120aの長辺方向に沿って(長辺に平行に)配置しているため、主制御基板120の実装効率を高めることができる。

また、外部機器と接続されるソケット121を、入出力用集積回路140を挟んで主制御用集積回路130と反対側に、主制御用集積回路130と入出力用集積回路140との間の距離より長い距離だけ離して入出力用集積回路140に平行に配置しているため、入出力用集積回路140とソケット121の間に不正な回路が設けられたことを容易に発見することができ、不正防止効果を高めることができる。

また、主制御回路の動作用クロック信号を出力する発振器122を、主制御用集積回路130を挟んで入出力用集積回路140と反対側に配置しているため、発振器122から発生するノイズが、主制御回路用集積回路130と入出力用集積回路140の間に配設されるデータバスに侵入するのを防止することができる。

また、主制御用集積回路130及び入出力用集積回路140の少なくとも一方の、主制御基板120に対向する面(底面130c)に対向する主制御基板120の箇所には、主制御基板120の基板面120a及び120bの少なくとも一方に接地線120Gf及び120Gbが配設されているため、主制御用集積回路130や入出力用集積回路140から発生するノイズが接地線120a及び120bに流れる。これにより、主制御用集積回路130や入出力用集積回路140から発生するノイズの外部への放出を防止することができ、外部機器(主制御基板120に配置されている他の電気回路を含む)の誤動作等を防止することができる。さらに、主制御用集積回路130の端子列の間あるいは入出力用集積回路140の端子列の間に不正な回路が設けられるのを防止することができる。

なお、本実施の形態は、主制御用集積回路130と入出力用集積回路140が、縦型の集積回路として形成され、主制御用集積回路130の、入出力用集積回路140と対向する面に表示されている識別情報をケース110の外部から視認可能に平行に離して配置されている構成を備えていればよく、他の構成要素は適宜選択可能である。勿論、他の構成要素を付加することによって、種々の効果を得ることができる。

以下に、このような場合でも、主制御用集積回路130と入出力用集積回路140との間に配設される接続線の長さを長くすることなく、不正防止効果を高めることができる第2の実施の形態を説明する。

第2の実施の形態の要部の斜視図を図11に示し、平面図を図12に示す。

本実施の形態では、図12に示すように、主制御用集積回路130及び入出力用集積回路140が主制御基板120に配置された時に、主制御用集積回路130のデータバス端子DBcと入出力用集積回路140のデータバス端子DBiが対向するように、主制御用集積回路130あるいは入出力用集積回路140の配置位置を平行方向にずらせている。すなわち、前述した実施の形態では、主制御用集積回路130入出力用集積回路140は、平行方向の配置位置が一致(略一致を含む)している(平行方向の両端部の位置が一致している)が、本実施の形態では、平行方向の配置位置がずれている(一方の集積回路の平行方向の一方の端部が、他方の集積回路の平行方向の両端部の間に配置されている)。

例えば、入出力用集積回路140の端子141が挿入(接続)される入出力用挿入部120IOを、主制御用集積回路130の端子131が挿入(接続)される主制御用挿入部120CPUに対して、図11に示す矢印の方向(平行方向)に距離Sだけずらす。平行方向にずらせる量は、データバス端子DBcの長辺方向における配設位置とデータバス端子DBiの長辺方向における配設位置とのずれ量に応じて設定される。

これにより、主制御用集積回路130のデータバス端子DBcと入出力用集積回路140のデータバス端子DBiを接続するデータバス(制御用集積回路130と入出力用集積回路140との間に配設されるデータバス)DBLの長さを短くすることができる。

この場合、主制御用集積回路130の、入出力用集積回路140と対向する側の側面130aの、入出力用集積回路140と対向しない箇所(入出力用集積回路140と重ならない箇所)に表示されている識別情報(図11では、シール133に表示されている識別情報133a)は、ZIP型(縦型)の主制御用集積回路130及び入出力用集積回路140が平行に主制御基板120に配置されていても、主制御基板120を収容したケースI10が遊技機に取り付けられている状態で、ケース110の外部から容易に視認することができる。

したがって、主制御用集積回路130と入出力用集積回路140を平行方向にずらせて配置した場合には、ずらせて配置しない場合に比べて、主制御用集積回路130の側面130aに表示されている情報識別を視認可能な、主制御用集積回路130と入出力用集積回路140との間の距離Hの最小距離を短くすることができる。すなわち、主制御用集積回路130と入出力用集積回路140との間に配設される接続線の長さをより短くすることができる。

この場合、識別情報132あるいはシール133に表示されている識別情報133aの視認結果から識別情報132あるいは133aの全体を推定可能な範囲内において、識別情報132あるいは133aの一部を入出力用集積回路140と対向しない箇所に表示してもよい。

この方法を用いると、主制御用集積回路130と入出力用集積回路140の平行方向のずれ量が変更された場合でも、ずれ量に応じて識別情報132の表示位置やシール133の貼付位置を変更することにより、主制御用集積回路130と入出力用集積回路140を平行方向にずらせて配置しない場合に比べて、主制御用集積回路130と入出力用集積回路140との間の距離を短くしながら、識別情報の視認性を確保することができる。

また、必ずしも、主制御用集積回路130と入出力用集積回路140を平行方向にずらせて配置した状態で、対向する位置にある主制御用集積回路130の端子131及び入出力用集積回路140の端子141をデータバス端子として用いる必要はない。

このような構成を用いることによっても、平行に配置された縦型の主制御用集積回路130と入出力用集積回路140を用いた場合に、主制御用集積回路130の入出力用集積回路側の面に表示されている識別情報を視認することができ、主制御用集積回路130と入出力用集積回路140との間の距離を短くしながら、識別情報の視認性を確保することができる。

このような場合、従来では、作業員は、集積回路に表示されている識別情報(例えば、製造会社名や型番等)を視認することによって、集積回路が主制御用集積回路130であるか入出力用集積回路140であるかを判別し、集積回路の配置位置を判別している。

そこで、以下に、このように同じ外径形状を有している制御用集積回路130と入出力用集積回路の配置位置を確実に判別することができる第3の実施の形態を説明する。

本実施の形態の要部の斜視図を図13に示す。

また、主制御基板120には、主制御用集積回路130の端子131が挿入され、端子列131a及び131bに対応する主制御用挿入部列120CPUa及び120CPUbを有する主制御用挿入部120が設けられているとともに、入出力用集積回路140の端子141が挿入され、端子列141a及び141bに対応する入出力用挿入部列120IOa及び120IObを有する入出力用挿入部120IOが設けられている。(図14参照)

そして、主制御用集積回路130の端子131の配置形状と入出力用集積回路140の端子141の配置形状、したがって、主制御用挿入部120CPUの配置形状と入出力用挿入部120IOの配置形状が同じになるように構成されている。

主制御用集積回路130と入出力用集積回路140に表示する色を変える方法としては、全体の色を変える方法や、所定の箇所の色を変える方法等を用いることができる。所定の箇所としては、作業員等が容易に視認することができる箇所、例えば、主制御用集積回路130や入出力用集積回路140の上面(反基板面側の面)を選択するのが好ましい。

また、主制御用集積回路130と入出力用集積回路140の全体あるいは部分の模様を変える方法を用いることができる。模様を変える態様には、一方を無地とし、他方に模様を表示する態様が含まれる。模様は色によって構成されているため、表示する模様を変える方法は、表示する色を変える概念に含まれる。

異なる色や異なる模様としては、作業員等が一瞥して判別可能な色や模様を用いるのが好ましい。

このため、作業員等は、集積回路の色を視認するのみで、集積回路が主制御用集積回路130であるか入出力用集積回路140あるかを簡単に、確実に判別することができる。したがって、端子や挿入部の数や配置状態が同じ場合でも、集積回路の配置位置を間違えることがない。

以下に、主制御用集積回路及び主制御用挿入部の近傍に表示する色と入出力用集積回路及び入出力用挿入部の近傍に表示する色を変えた第4の実施の形態を説明する。

本実施の形態の要部の斜視図を図14に示す。

また、第3の実施の形態と同様に、主制御用集積回路130及び入出力用集積回路140には、異なる色が表示されている。例えば、主制御用集積回路130及び入出力用集積回路140の全体あるいは一部に異なる色が表示されている。

さらに、主制御基板120の基板面(実装側基板面)120aに設けられている、主制御用集積回路130の端子131が挿入される主制御用挿入部120CPUの近傍に主制御用表示部(CPU用表示部)が表示されているとともに、入出力用集積回路140の端子141が挿入される入出力用挿入部120IOの近傍に入出力用表示部(IO用表示部)が表示されている。本実施の形態では、主制御用挿入部120CPU全体を覆う領域をCPU用表示部とし、入出力用挿入部120IO全体を覆う領域をIO用表示部としている。

CPU用表示部を表示する主制御用挿入部120CPUの近傍や、IO用表示部を表示する入出力用挿入部120IOの近傍は、挿入部が制御用挿入部120CPUであることあるいは入出力用挿入部120IOであることを判別可能であれば適宜設定することができる。例えば、主制御用接続部120CPUや入出力用接続部120IOから離れている位置、主制御用接続部120CPUや入出力用接続部IOの一部あるいは全部を含む領域を設定することができる。

そして、CPU用表示部には、主制御用集積回路130に表示されている色と同じ色が表示され、IO用表示部には、入出力用集積回路140に表示されている色と同じ色が表示されている。

なお、前述したように、異なる模様を表示する態様は、異なる色を表示する概念に含まれる。

したがって、集積回路の端子や端子を挿入する挿入部の数や配置状態が同じ場合でも、主制御用集積回路130と入出力用集積回路140の配置位置を間違えることがない。

例えば、主制御用集積回路130の端子131と入出力用集積回路140の端子141の数や配置状態の少なくとも一方を変える。また、端子131と141の数や配置状態を変えることに伴って、端子131が挿入される制御用挿入部120CPUと端子141が挿入される入出力用挿入部120IOの数や配置状態を端子131と141の数や配置状態に合わせる。端子の配置態様としては、例えば、台形状に配置する態様を用いることができる。

なお、以上の実施の形態で用いた技術は、同じ基板に配置される同じ外形形状を有する主制御用集積回路と入出力用集積回路の配置位置を判別するため、さらには、同じ基板に配置される同じ外形形状を有する複数の構成要素の配置位置を判別するために用いることができる。

例えば、本発明の遊技機は、前記各実施の形態で説明した各構成の全てを備える必要はなく、各実施の形態で説明した各構成の中から適宜選択した構成を備えるものであってもよい。

また、縦型の集積回路としては、基板に最も近い面(基板側に配置される面)が最も大きい面積を有する面とならないように基板に配置されるものであればよい。

また、パチンコ機について説明したが、本明細書に記載されている技術は、パチンコ機以外の種々の遊技機に適用することができる。

例えば、「(態様1)第1のセレクト端子及び第1のデータバス端子を含む端子を有し、遊技機の動作を制御する制御回路を内蔵する制御用集積回路と、前記制御用集積回路の第1のセレクタ端子及び第1のデータバス端子に接続される第2のセレクト端子及び第2のデータバス端子と複数のデータ端子を含む端子を有し、前記第2のセレクト端子に入力されたセレクト信号に基づいて、前記第2のデータバス端子と前記複数のデータ端子との接続を制御する入出力処理回路を内蔵する入出力用集積回路と、前記制御用集積回路及び前記入出力用集積回路が配置される制御基板と、前記制御用集積回路及び前記入出力用集積回路が配置された前記制御基板を収容するケースを備え、前記制御用集積回路及び前記入出力用集積回路は、縦型の集積回路として形成されているとともに、平行に前記制御基板に配置されており、前記制御用集積回路の、前記入出力用集積回路と対向する側の面には識別情報が表示されており、前記制御用集積回路と前記入出力用集積回路の距離は、前記制御用集積回路の、前記入出力用集積回路と対向する側の面に表示されている識別情報を、前記ケースの外部から視認可能な距離に設定されている、ことを特徴とする遊技機。」として構成することができる。

本態様は、第1のセレクト端子及び第1のデータバス端子を含む端子を有する制御用集積回路と、第1のセレクタ端子及び第1のデータバス端子に接続される第2のセレクト端子及び第2のデータバス端子と複数のデータ端子を含む端子を有する入出力用集積回路と、制御基板と、制御基板を収容するケースを備えている。

制御用集積回路及び入出力用集積回路は、縦型の集積回路として形成されているとともに、平行に制御基板に配置されている。

そして、制御用集積回路の、入出力用集積回路と対向する側の面には識別情報が表示されており、制御用集積回路と入出力用集積回路の距離が、制御用集積回路に表示されている識別情報を、ケースの外部から視認可能な距離に設定されている。

「縦型の集積回路」は、基板側に配置される面が最も大きい面積を有する面とならないように基板に配置される集積回路を意味する。このような集積回路は、典型的には、ZIP型等の縦型の集積回路である。

「制御用集積回路と入出力用集積回路が平行に配置される」という記載は、制御用集積回路の端子列の配列方向と入出力用集積回路の端子列の配列方向が平行になるように、制御用集積回路と入出力用集積回路が配置される構成を意味する。「制御用集積回路と入出力用集積回路を平行に配置する」態様は、制御用集積回路と入出力用集積回路が、平行方向に少なくとも一部が重なるように配置する態様を意味する。縦型の制御用集積回路と入出力用集積回路を用いる場合には、最も大きい面積を有する面が平行になるように配置される。

なお、「平行に配置される」構成には、略平行に配置される構成も含まれる。

「制御用集積回路に表示されている識別情報」は、例えば、制御用集積回路に印刷されているあるいは制御用集積回路に貼付されているラベルに印刷されている、当該制御用集積回路あるいは当該制御用集積回路に内蔵されている制御回路の型番を示す文字等の情報を含む。

「制御用構成要素と入出力用構成要素が、制御用構成要素の、入出力用構成要素に対向する面に表示されている識別情報の視認が可能となるように離して平行に配置されている」構成としては、制御用構成要素に表示されている識別情報全体を視認可能な距離以上離して制御用構成要素と入出力用構成要素が平行に配置されている構成や、制御用構成要素に表示されている識別情報の一部を視認可能であり、且つ、視認した識別情報の一部に基づいて識別情報全体を推定可能な距離以上離して制御用構成要素と入出力用構成要素が平行に配置されている構成を用いることができる。すなわち、必ずしも、識別情報の全体を視認可能でなくてもよい。

態様1の遊技機を用いれば、制御用集積回路の汎用性を高めることができる。また、制御基板の実装効率を高めることができるとともに、制御用集積回や入出力用集積回路と制御基板との間に不正回路が設けられていることを容易に発見することができる。また、制御用集積回路と入出力用集積回路を接続する接続線の長さが長くなる量を最小限に抑えながら、外観は正規の制御用構成要素に似せているが、正規の表示情報が表示されていない不正な制御用集積回路を容易に発見することができる。

態様2の遊技機は、第1のセレクト端子及び第1のデータバス端子を含む端子を有する制御用集積回路と、第1のセレクタ端子及び第1のデータバス端子に接続される第2のセレクト端子及び第2のデータバス端子と複数のデータ端子を含む端子を有する入出力用集積回路と、制御基板と、制御基板を収容するケースを備えている。

制御用集積回路及び入出力用集積回路は、縦型の集積回路として形成されているとともに、平行に制御基板に配置されている。

そして、制御用集積回路と入出力用集積回路は、平行方向にずらせて配置されている。

「制御用集積回路と入出力用集積回路を、平行に、平行方向にずらせて配置する」態様は、制御用集積回路と入出力用集積回路が、平行方向に少なくとも一部は重なるが、全部は重ならない態様を意味する。

態様2の遊技機を用いれば、態様1の遊技機と同様の効果を有する。なお、態様2の遊技機では、態様1の遊技機に比べて、制御用集積回路と入出力用集積回路を接続する接続線の長さが長くなる量をより抑えることができる。

態様3の遊技機では、制御用集積回路と入出力用集積回路が、制御用集積回路の、識別情報が表示されている面を入出力用集積回路側から見た時に、識別情報の少なくとも一部が入出力用集積回路と重ならないように、平行方向にずらせて配置されている。

「制御用集積回路の、識別情報が表示されている面を入出力用集積回路側から見た時に、識別情報の少なくとも一部が入出力用集積回路と重ならないように平行方向にずらせて配置される」構成は、入出力用集積回路側から見た時に視認可能な識別情報の少なくとも一部(全部を含む)を視認可能であり、且つ、視認した識別情報の少なくとも一部に基づいて、識別情報全体を推定可能な距離以上離して制御用構成要素と入出力用構成要素が平行に配置されている構成を意味している。

態様3の遊技機を用いれば、制御用集積回路と入出力用集積回路を接続する接続線の長さが長くなる量を最小限に抑えながら、外観は正規の制御用構成要素に似せているが、正規の表示情報が表示されていない不正な制御用集積回路をより容易に発見することができる。

態様4の遊技機では、制御用集積回路及び入出力用集積回路の端子は2列に平行に配置されているとともに、制御基板には、制御用集積回路及び入出力用集積回路の端子が接続可能な制御用接続部及び入出力用接続部が2列に平行に配置されている。

そして、入出力用集積回路側の列の制御用集積回路の端子及び制御用集積回路側の列の入出力用集積回路の端子をデータバス端子とし、制御基板の、データバス端子が接続される制御用接続部と入出力用接続部の間にデータバスを配置している。

態様4の遊技機を用いれば、直線状のデータバスを配置することができるため、データバスの長さを短くすることができる。

態様5の遊技機では、データバス端子が対向するように配置されている。

「データバス端子が対向するように配置されている」という記載は、制御用集積回路と入出力用集積回路の平行方向、すなわち、制御用接続部と入出力用接続部の平行方向に直角(略直角を含む)な位置にデータバス端子が配置されている構成を意味する。

態様5の遊技機を用いれば、データバス端子の長さをより短くすることができる。

態様6の遊技機では、制御用集積回路と入出力用集積回路の距離が、制御基板に配置された縦型の制御用集積回路の周囲に、横型の集積回路として形成された制御用集積回路を制御基板に配置した場合に必要とする実装面積と等しい領域を確保可能な距離に設定されている。

「制御基板に配置された、縦型の制御用集積回路の周囲に、横型の集積回路として形成された制御用集積回路を制御基板に配置した場合に必要とする実装面積と等しい領域を確保可能な距離」という記載は、例えば、横型の主制御用集積回路と入出力用集積回路を平行に主制御基板上に配置した場合に、横型の主制御用集積回路が配置される領域(実装領域)の中央部に、縦型の主制御用集積回路の端子の配列方向が横型の主制御用集積回路の端子の配列方向と同じ方向となるように、縦型の主制御用集積回路を主制御基板に配置する構成を意味する。

態様6の遊技機を用いれば、制御用集積回路の、入出力用集積回路側の面に表示されている識別情報を視認可能となるように、制御用集積回路と入出力用集積回路を容易に配置することができる。

態様7の遊技機では、入出力用集積回路のデータ端子の中の少なくとも1つに接続される接続端子を有する接続部を、入出力用集積回路を挟んで制御用集積回路と反対側に、入出力用集積回路と平行に配置している。

「接続部を入出力用集積回路と平行に配置する」構成は、例えば、接続部の接続端子の配列方向が入出力用集積回路の端子列の配列方向と平行になるように、接続部と入出力用集積回路を配置する構成を意味する。

接続部に接続されるデータ端子は1つでもよいし複数でもよい。

接続部の配置位置あるいは接続部の接続端子に接続される入出力用集積回路のデータ端子の配設位置は、接続部と入出力用集積回路が制御基板に配置された時に、接続部の接続端子と入出力用集積回路のデータ端子が対向するように設定されているのが好ましい。

態様7の遊技機を用いれば、入出力用集積回路と接続部との間に配設されるデータ線の長さを短くすることができる。

態様8の遊技機では、接続部と入出力用集積回路の間の距離を、制御用集積回路と入出力用集積回路の間の距離以上に設定している。

態様8の遊技機を用いれば、入出力用集積回路と接続部の間に不正な回路が設けられていることを容易に発見することができる。

態様9の遊技機では、入出力用集積回路が制御用集積回路より制御基板の中央部側に配置されている。

態様9の遊技機を用いれば、入出力用集積回路と他の回路との間に配設される接続線を短くすることができる。

態様10の遊技機では、制御用集積回路及び入出力用集積回路が、長方形に形成されている制御基板の基板面の長辺に平行に配置されている。

態様10の遊技機を用いれば、制御用集積回路に表示されている識別情報を視認可能に、制御用集積回路と入出力用集積回路の間の距離を確保しながら、制御基板の実装効率を高めることができる。

態様11の遊技機では、制御回路の動作用クロック信号を出力する発振器を、制御用集積回路を挟んで入出力用集積回路と反対側に配置している。

態様11の遊技機を用いれば、発振器から発生するノイズが、制御用集積回路と入出力用集積回路との間に配設されているデータバスに浸入するのを防止することができる。

態様12の遊技機では、制御基板の少なくとも一方側の面に、2列の制御用接続部列の間あるいは2列の入出力用接続部列の間に接地線が配置されている。

接地線の配設位置は、2列の制御用接続部列の間あるいは2列の入出力用接続部列の間であればよいが、2列の制御用接続部列の間あるいは2列の入出力用接続部列の間の中央部であるのが好ましい。

接地線は、2列の制御用接続部列の間及び2列の入出力用接続部列の間の少なくとも一方に配設されていればよい。また、少なくとも一方側の基板面に配設されていればよい。

「制御用集積回路及び入出力用集積回路が配置されていない側(反実装側)の基板面における2列の制御用接続部列の間あるいは2列の入出力用接続部列の間」は、制御用集積回路及び入出力用集積回路が配置されている側(実装側)の基板面に設けられている制御用接続部あるいは入出力用接続部を、制御用集積回路及び入出力用集積回路が配置されていない側に貫通させることによって形成される2列の制御用接続部列あるいは2列の入出力用接続部列の間を意味する。

態様12の遊技機では、制御用集積回路あるいは入出力用集積回路の下方の基板面に接地線が配設されているため、制御用集積回路あるいは入出力用集積回路から発生するノイズが外部に放出されるのを防止することができる。これにより、外部機器のノイズによる誤動作を防止することができる。また、制御用集積回路あるいは入出力用集積回路の端子列の間に不正な回路が配置されることを防止することができ、不正防止効果を高めることができる。

態様13の遊技機では、同じ外形形状を有する制御用集積回路と入出力用集積回路を判別可能に構成している。

「判別可能に構成する」方法としては、色によって判別可能に構成する方法や、接続端子の数や配設態様によって判別可能に構成する態様等を用いることができる。

態様13の遊技機では、同じ外形形状を有している制御用集積回路と入出力用集積回路を判別することができるため、作業員等が制御用集積回路と入出力用集積回路の配設位置を間違えるのを防止することができる。

態様14の遊技機では、制御用集積回路及び入出力用集積回路が、縦型の集積回路として形成されているとともに、平行に制御基板に配置されている。

態様14の遊技機を用いれば、制御基板の実装効率を高めることができる。また、制御用集積回路と入出力用集積回路との間に配設される接続線を短くすることができる。さらに、制御用集積回路及び入出力用集積回路と制御基板との間に不正回路が配設されたことを容易に発見することができる。

態様15の遊技機では、制御用集積回路及び入出力用集積回路が、少なくとも一部の色が異なるように構成されている。

制御用集積回路や入出力用集積回路の一部の色を変える方法を用いる場合には、色の表示位置を、色が異なっていることを容易に判別することができる位置、例えば、制御用集積回路や入出力用集積回路の上面(反基板面側)に設定するのが好ましい。

ここで、模様は色の組合せであるから、「制御用集積回路と入出力用集積回路の少なくとも一部の色が異なる」態様には、制御用集積回路と入出力用集積回路の少なくとも一部に異なる模様を表示する態様が含まれる。模様には、無地の模様も含まれる。

態様15の遊技機を用いれば、作業員等は、制御用集積回路と入出力用集積回路の一部あるいは全部に表示されている色(模様を含む)を視認するだけで、制御用集積回路と入出力用集積回路を簡単に、確実に判別することができる。これにより、作業員等が制御用集積回路と入出力用集積回路の配設位置を間違えるのを防止することができる。

態様16の遊技機では、制御用集積回路の端子及び制御用接続部と入出力用集積回路の端子及び入出力用接続部の数あるいは配置形状の少なくとも一方を変えている。

態様16の遊技機を用いれば、制御用集積回路の端子は制御用接続部にしか接続することができず、また、入出力用集積回路の端子は入出力用接続部にしか接続することができない。このため、同じ外形形状であっても、制御用集積回路や入出力用集積回路を正しい配置位置に確実に配置することができる。

態様17の遊技機では、制御用集積回路及び制御用接続部の近傍と入出力用集積回路及び入出力用接続部の近傍にそれぞれ異なる色を表示している。

制御用接続部や入出力用接続部の近傍としては、制御用接続部や入出力用接続部から離れている箇所、制御用接続部や入出力用接続部の一部あるいは全部を含む領域を設定することができる。

模様を表示する態様は、色を表示する態様に含まれる。

態様17の遊技機を用いれば、作業員等は、集積回路に表示されている色(模様を含む)と、制御用接続部及び入出力用接続部の近傍の色を対比するだけで、すなわち、集積回路に表示されている色と同じ色が表示されている制御用接続部あるいは入出力用接続部を選択するだけで、集積回路を正しい配置位置に配置することができる。

態様18の遊技機では、制御用集積回路及び制御用接続部の近傍と入出力用集積回路及び入出力用接続部の近傍に異なる模様を表示している。

異なる模様としては、一瞥して判別可能な模様を用いるのが好ましい。

態様18の遊技機を用いれば、作業員等は、模様の認識及び対比を行うだけでよいため、集積回路を正しい配置位置に、容易に、確実に配置することができる。

111 孔

120 基板

120a、120b 基板面

120CPU 制御用挿入部

120CPUa、120CPUb 制御用挿入部列

120IO 入出力用挿入部

120IOa、120IOb 入出力用挿入部列

120Gf、120Gb 接地パターン

121 ソケット

122 発振器

130 制御用集積回路(CPUチップ)

130a、130b 側面

130c 底面(基板と対向する面)

131、141 端子

131a、131b、141a、141b 端子列

132、133a 識別情報

133 シール

140 入出力用集積回路(IOチップ)

140a、140b 側面

Claims (1)

- 遊技機の動作を制御する制御回路を内蔵する制御用構成要素と、前記制御用構成要素に接続され、前記制御回路と他の回路との間でのデータの入出力処理を実行する入出力処理回路を内蔵する入出力用構成要素と、前記制御用構成要素及び入出力用構成要素が配置される基板とを備える遊技機であって、

前記制御用構成要素及び前記入出力用構成要素は、基板に最も近い面が最も大きい面積を有する面とならないように配置されているとともに、前記制御用構成要素の、前記入出力用構成要素に対向する側の面に表示されている識別情報の視認が可能となるように離して平行に配置されている、

ことを特徴とする遊技機。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004254912A JP2006068252A (ja) | 2004-09-01 | 2004-09-01 | 遊技機 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004254912A JP2006068252A (ja) | 2004-09-01 | 2004-09-01 | 遊技機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006068252A true JP2006068252A (ja) | 2006-03-16 |

| JP2006068252A5 JP2006068252A5 (ja) | 2009-11-05 |

Family

ID=36149470

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004254912A Pending JP2006068252A (ja) | 2004-09-01 | 2004-09-01 | 遊技機 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006068252A (ja) |

Cited By (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012055757A (ja) * | 2011-12-21 | 2012-03-22 | Sophia Co Ltd | 遊技機 |

| JP2017159075A (ja) * | 2017-04-24 | 2017-09-14 | 株式会社大都技研 | 遊技台 |

| JP2017159074A (ja) * | 2017-04-24 | 2017-09-14 | 株式会社大都技研 | 遊技台 |

| JP2017196419A (ja) * | 2017-05-26 | 2017-11-02 | 株式会社大都技研 | 遊技台 |

| JP2019000392A (ja) * | 2017-06-15 | 2019-01-10 | 株式会社大一商会 | 遊技機 |

| JP2019166134A (ja) * | 2018-03-23 | 2019-10-03 | 株式会社三共 | 遊技機 |

| JP2019187988A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187986A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187989A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187987A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019213622A (ja) * | 2018-06-11 | 2019-12-19 | 株式会社三共 | 遊技機 |

| JP2019217133A (ja) * | 2018-06-22 | 2019-12-26 | 株式会社三共 | 遊技機 |

| JP2019217132A (ja) * | 2018-06-22 | 2019-12-26 | 株式会社三共 | 遊技機 |

| JP2020081576A (ja) * | 2018-11-29 | 2020-06-04 | 株式会社三共 | 遊技機 |

| JP2020096746A (ja) * | 2018-12-19 | 2020-06-25 | 株式会社三共 | 遊技機 |

| JP2021079268A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

| JP2021079267A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

| JP2021079269A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

| JP2021087855A (ja) * | 2021-03-05 | 2021-06-10 | 株式会社三共 | 遊技機 |

| JP2021102015A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP2021102014A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP2021102016A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP2022027962A (ja) * | 2018-11-29 | 2022-02-14 | 株式会社三共 | 遊技機 |

| JP7404573B2 (ja) | 2018-06-04 | 2023-12-25 | 株式会社三共 | 遊技機 |

| JP7404570B2 (ja) | 2018-06-04 | 2023-12-25 | 株式会社三共 | 遊技機 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62183779A (ja) * | 1986-02-07 | 1987-08-12 | 株式会社三共 | 遊技機 |

| JPH02125650A (ja) * | 1988-11-04 | 1990-05-14 | Nec Corp | 半導体装置用パッケージ |

| JPH0397256A (ja) * | 1989-09-11 | 1991-04-23 | Sanyo Electric Co Ltd | 混成集積回路装置 |

| JPH03222354A (ja) * | 1990-01-26 | 1991-10-01 | Sanyo Electric Co Ltd | 混成集積回路装置 |

| JPH0619285U (ja) * | 1992-08-20 | 1994-03-11 | 日本航空電子工業株式会社 | 同軸コネクタ |

| JP2000332366A (ja) * | 1999-05-21 | 2000-11-30 | Minolta Co Ltd | 多層プリント配線基板 |

| JP2001314622A (ja) * | 2000-05-11 | 2001-11-13 | Sanyo Product Co Ltd | 遊技機 |

| JP2003164650A (ja) * | 2001-11-30 | 2003-06-10 | Taiyo Elec Co Ltd | 遊技機 |

| JP2004057292A (ja) * | 2002-07-25 | 2004-02-26 | Sankyo Kk | 遊技機 |

-

2004

- 2004-09-01 JP JP2004254912A patent/JP2006068252A/ja active Pending

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62183779A (ja) * | 1986-02-07 | 1987-08-12 | 株式会社三共 | 遊技機 |

| JPH02125650A (ja) * | 1988-11-04 | 1990-05-14 | Nec Corp | 半導体装置用パッケージ |

| JPH0397256A (ja) * | 1989-09-11 | 1991-04-23 | Sanyo Electric Co Ltd | 混成集積回路装置 |

| JPH03222354A (ja) * | 1990-01-26 | 1991-10-01 | Sanyo Electric Co Ltd | 混成集積回路装置 |

| JPH0619285U (ja) * | 1992-08-20 | 1994-03-11 | 日本航空電子工業株式会社 | 同軸コネクタ |

| JP2000332366A (ja) * | 1999-05-21 | 2000-11-30 | Minolta Co Ltd | 多層プリント配線基板 |

| JP2001314622A (ja) * | 2000-05-11 | 2001-11-13 | Sanyo Product Co Ltd | 遊技機 |

| JP2003164650A (ja) * | 2001-11-30 | 2003-06-10 | Taiyo Elec Co Ltd | 遊技機 |

| JP2004057292A (ja) * | 2002-07-25 | 2004-02-26 | Sankyo Kk | 遊技機 |

Cited By (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012055757A (ja) * | 2011-12-21 | 2012-03-22 | Sophia Co Ltd | 遊技機 |

| JP2017159075A (ja) * | 2017-04-24 | 2017-09-14 | 株式会社大都技研 | 遊技台 |

| JP2017159074A (ja) * | 2017-04-24 | 2017-09-14 | 株式会社大都技研 | 遊技台 |

| JP2017196419A (ja) * | 2017-05-26 | 2017-11-02 | 株式会社大都技研 | 遊技台 |

| JP2019000392A (ja) * | 2017-06-15 | 2019-01-10 | 株式会社大一商会 | 遊技機 |

| JP2019166134A (ja) * | 2018-03-23 | 2019-10-03 | 株式会社三共 | 遊技機 |

| JP7058061B2 (ja) | 2018-04-27 | 2022-04-21 | 株式会社三共 | 遊技機 |

| JP2019187988A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187986A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187989A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2019187987A (ja) * | 2018-04-27 | 2019-10-31 | 株式会社三共 | 遊技機 |

| JP2021098085A (ja) * | 2018-04-27 | 2021-07-01 | 株式会社三共 | 遊技機 |

| JP7404570B2 (ja) | 2018-06-04 | 2023-12-25 | 株式会社三共 | 遊技機 |

| JP7404573B2 (ja) | 2018-06-04 | 2023-12-25 | 株式会社三共 | 遊技機 |

| JP2019213622A (ja) * | 2018-06-11 | 2019-12-19 | 株式会社三共 | 遊技機 |

| JP2019217132A (ja) * | 2018-06-22 | 2019-12-26 | 株式会社三共 | 遊技機 |

| JP2019217133A (ja) * | 2018-06-22 | 2019-12-26 | 株式会社三共 | 遊技機 |

| JP2020081576A (ja) * | 2018-11-29 | 2020-06-04 | 株式会社三共 | 遊技機 |

| JP7209077B2 (ja) | 2018-11-29 | 2023-01-19 | 株式会社三共 | 遊技機 |

| JP6998290B2 (ja) | 2018-11-29 | 2022-01-18 | 株式会社三共 | 遊技機 |

| JP2022027962A (ja) * | 2018-11-29 | 2022-02-14 | 株式会社三共 | 遊技機 |

| JP2020096746A (ja) * | 2018-12-19 | 2020-06-25 | 株式会社三共 | 遊技機 |

| JP2021102016A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP2021102014A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP2021102015A (ja) * | 2019-12-26 | 2021-07-15 | 株式会社藤商事 | 遊技機 |

| JP7334113B2 (ja) | 2019-12-26 | 2023-08-28 | 株式会社藤商事 | 遊技機 |

| JP7334111B2 (ja) | 2019-12-26 | 2023-08-28 | 株式会社藤商事 | 遊技機 |

| JP7334112B2 (ja) | 2019-12-26 | 2023-08-28 | 株式会社藤商事 | 遊技機 |

| JP2021087855A (ja) * | 2021-03-05 | 2021-06-10 | 株式会社三共 | 遊技機 |

| JP7150919B2 (ja) | 2021-03-05 | 2022-10-11 | 株式会社三共 | 遊技機 |

| JP7058060B2 (ja) | 2021-03-05 | 2022-04-21 | 株式会社三共 | 遊技機 |

| JP7058058B2 (ja) | 2021-03-05 | 2022-04-21 | 株式会社三共 | 遊技機 |

| JP7058059B2 (ja) | 2021-03-05 | 2022-04-21 | 株式会社三共 | 遊技機 |

| JP2021079269A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

| JP2021079267A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

| JP2021079268A (ja) * | 2021-03-05 | 2021-05-27 | 株式会社三共 | 遊技機 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006068252A (ja) | 遊技機 | |

| JP6100748B2 (ja) | 遊技機 | |

| JP6378394B2 (ja) | 遊技機 | |

| JP6974227B2 (ja) | 遊技機 | |

| JP5938324B2 (ja) | 遊技機用の制御基板 | |

| JP6602347B2 (ja) | 遊技機 | |

| JP7019495B2 (ja) | 遊技機 | |

| JP2019166135A (ja) | 遊技機 | |

| JP2012099670A (ja) | 実装基板 | |

| JP4062542B2 (ja) | 遊技機の制御装置 | |

| JP2003093699A (ja) | 遊技機 | |

| JP7404572B2 (ja) | 遊技機 | |

| JP2016106777A (ja) | 遊技機 | |

| JP2016106778A (ja) | 遊技機 | |

| JP2002011230A (ja) | パチンコ機の不正防止構造 | |

| JP7068900B2 (ja) | 遊技機 | |

| JP6138750B2 (ja) | 遊技機 | |

| JP6974228B2 (ja) | 遊技機 | |

| JP7132261B2 (ja) | 遊技機 | |

| JP7106343B2 (ja) | 遊技機 | |

| JP7128653B2 (ja) | 遊技機 | |

| JP2006149637A (ja) | 遊技機 | |

| JP4716199B2 (ja) | 耐タンパリング構造 | |

| JP7068901B2 (ja) | 遊技機 | |

| JP7404571B2 (ja) | 遊技機 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20090318 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090911 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091007 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091207 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100610 |