JP2005295793A - 力率補正回路 - Google Patents

力率補正回路 Download PDFInfo

- Publication number

- JP2005295793A JP2005295793A JP2005101067A JP2005101067A JP2005295793A JP 2005295793 A JP2005295793 A JP 2005295793A JP 2005101067 A JP2005101067 A JP 2005101067A JP 2005101067 A JP2005101067 A JP 2005101067A JP 2005295793 A JP2005295793 A JP 2005295793A

- Authority

- JP

- Japan

- Prior art keywords

- power factor

- winding

- factor correction

- correction circuit

- primary winding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000012937 correction Methods 0.000 title claims abstract description 58

- 238000004804 winding Methods 0.000 claims abstract description 107

- 239000003990 capacitor Substances 0.000 claims abstract description 44

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical group [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 claims 3

- 238000010586 diagram Methods 0.000 description 18

- 238000013461 design Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 238000013459 approach Methods 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/42—Circuits or arrangements for compensating for or adjusting power factor in converters or inverters

- H02M1/4208—Arrangements for improving power factor of AC input

- H02M1/4258—Arrangements for improving power factor of AC input using a single converter stage both for correction of AC input power factor and generation of a regulated and galvanically isolated DC output voltage

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

- Rectifiers (AREA)

Abstract

【課題】高い力率を有する力率補正回路を提供する。

【解決手段】力率補正回路710は、直列に接続された第1の巻線、ダイオード、インダクタLおよび第1のコンデンサを含む。第1の巻線の極性は1次巻線の極性と反対である。第2のコンデンサは1次巻線に接続されて、1次巻線を制御して第1のコンデンサを通る電圧を生成する。この電圧は変圧器T1を介して第1の巻線へ伝送され、第1のコンデンサ電圧を昇圧させて力率を向上する。

【選択図】図7

【解決手段】力率補正回路710は、直列に接続された第1の巻線、ダイオード、インダクタLおよび第1のコンデンサを含む。第1の巻線の極性は1次巻線の極性と反対である。第2のコンデンサは1次巻線に接続されて、1次巻線を制御して第1のコンデンサを通る電圧を生成する。この電圧は変圧器T1を介して第1の巻線へ伝送され、第1のコンデンサ電圧を昇圧させて力率を向上する。

【選択図】図7

Description

本発明は、力率補正回路に関し、特に高調波電流規則(harmonic current rules)EN−6100−3−2で要求されているクラスAまたはクラスDに合致するフライバックトポロジー(flyback topologies)で設計されたスイッチング電源供給器の力率を向上する力率補正回路に関する。

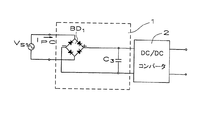

図1は一般のスイッチング電源供給器を示す回路図である。このスイッチング電源供給器はAC/DC整流器1およびDC/DCコンバータ2を備え、電解コンデンサC3はブリッジ整流器BD1のフィルタとして接続される。

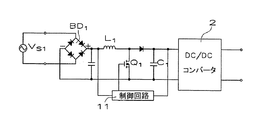

図5は回路構造を示し、図1のDC/DCコンバータ2はハーフブリッジコンバータ(half-bridge converter)である。図5に示す回路設計は、ブリッジ整流器BD1により交流電圧源VS1を整流する。そして、この整流された交流電圧源はコンデンサC3によりフィルタされ、直流電圧源VC3が生成される。このコンデンサC1およびコンデンサC2は、共通ノードに接続されて分圧器が形成される。そのため、二つのコンデンサの間に設けられた共通ノードの電圧はVC3/2である。

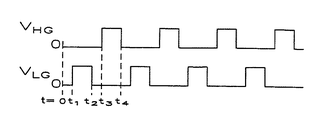

図6はPWM(pulse width modulation)信号を示すタイムチャートであり、VHGおよびVLGは、図5のスイッチQ1、Q2の駆動信号をそれぞれ示す。

0≦t≦t1において、PWM信号VHG、VLGのそれぞれは低い(低電圧)状態であり、スイッチQ1、Q2がそれぞれオフとなっているとき、出力電圧VOはコンデンサC4により提供される。

t1≦t≦t2のとき、PWM信号VLGは高く(高電圧)、PWM信号VHGは低い(低電圧)状態であるため、スイッチQ1はオフされ、スイッチQ2はオン(導電)状態である。続いて電流がコンデンサC1、1次巻線P1およびスイッチQ2を通って接地される。この状況下では、変圧器が1次巻線P1から2次巻線S1へ電力を変換し、コンデンサC4へ電力を供給して電圧VOを出力する。

t2≦t≦t3のとき、スイッチQ1、Q2のそれぞれは共に再びオフの状態となり、回路の動作状態は0≦t≦t1のときと同じ状態である。

t3≦t≦t4のとき、PWM信号VLGは低く(低電圧)、PWM信号VHGは高い(高電圧)状態であるため、スイッチQ1は導電されてスイッチQ2はオフの状態である。続いて、電流はスイッチQ1、1次巻線P1およびコンデンサC2を通って接地される。変圧器は1次巻線P1から2次巻線S2へ電力を変換し、コンデンサC4へ電力を供給して電圧VOを出力する。

上述のパワースイッチングのサイクルが繰返されることにより電力が負荷に供給され、同時に出力電圧VOはフィードバックシステム12へ伝送される。フィードバックシステム12は信号を高周波パルス信号制御回路50へフィードバックすることにより、PWM信号VHG、VLGのデューティサイクルを調整する。例えば、出力電圧が所定値よりも低いときには負荷に供給される電力は十分でなくなるため、フィードバック信号はPWM信号VHG、VLGのデューティサイクルを延ばすことにより、スイッチQ1、Q2の導電時間が増大される。その結果、変圧器T1の1次巻線から2次巻線へ電力が伝送される時間が延長される。つまり、2次巻線へ提供される電力は増大される。そして、出力電圧VOが増大されることにより必要な電圧を維持することができる。つまり、これは出力電圧が所定値よりも高いときに、負荷に提供される電力が過剰駆動されるということである。このような場合、PWM信号VHG、VLGのデューティサイクルは減少されなければならない。

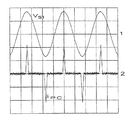

図5に示される入力電流IPCは、図2に示されるパルス電流である。入力電流の歪みは、従来のスイッチング電源供給器の力率を大幅に低減し(一般には約50%の低減)、図1に示すように、AC/DC整流器1により整流された後に100%を超える総高調波歪を発生させる。その結果、総高調波は大きく歪んで品質が低下し、貴重なエネルギーも浪費されることとなった。

そのため、多くの国では、提供される電力の効率および品質を向上させるため、製造メーカが従うべき高調波電流規則(例えば、EN−6100−3−2など)が多数公開されている。

このように、従来のスイッチング電源供給器の力率を向上させるために様々な種類の力率補正回路が開発されてきた。そして典型的な従来技術である二つの実施形態を以下に示す。

(インダクタ型力率補正回路)

図3は、ブリッジ整流器BD1と電解コンデンサC1との間に直列接続された低周波大型巻線L1を示す従来技術の回路図である。巻線L1およびコンデンサC1により形成されたローパスフィルタはDC/DCコンバータ2の入力電流を整流する。この設計は、蛍光灯の力率を修正する安定器の機能に類似している。しかし、巻線L1の体積は比較的大きかったため、力率の向上は限定されたものとなり、動作するときにも異常に高い温度が発生した。

図3は、ブリッジ整流器BD1と電解コンデンサC1との間に直列接続された低周波大型巻線L1を示す従来技術の回路図である。巻線L1およびコンデンサC1により形成されたローパスフィルタはDC/DCコンバータ2の入力電流を整流する。この設計は、蛍光灯の力率を修正する安定器の機能に類似している。しかし、巻線L1の体積は比較的大きかったため、力率の向上は限定されたものとなり、動作するときにも異常に高い温度が発生した。

(アクティブ型力率補正回路)

図4は、従来技術によるDC/DCコンバータ2を含む2段式回路を形成するAC/DC整流器を示す回路図である。また、そこには力率を向上させるために複雑な制御回路11および大きなスイッチング素子Q1が加えられている。そのため、回路設計が複雑となり製造コストも多くかかった。

図4は、従来技術によるDC/DCコンバータ2を含む2段式回路を形成するAC/DC整流器を示す回路図である。また、そこには力率を向上させるために複雑な制御回路11および大きなスイッチング素子Q1が加えられている。そのため、回路設計が複雑となり製造コストも多くかかった。

そして、多くの力率補正回路は、上述した二つの従来技術に含まれる基本概念を基に開発されているため、同様の欠点を備えていた。

上述したように、従来の力率補正回路には多くの欠点があった。例えば、図3に示す回路構造は体積が比較的大きく、図4に示す回路構造は複雑で製造コストも高かった。

本発明の第1の目的は、高い力率を有する力率補正回路を提供することにある。

本発明の第2の目的は、従来技術で存在していた問題を解決する力率補正回路を提供することにある。

本発明の第3の目的は、小型で経済的なスイッチング電源供給器を提供する力率補正回路を提供することにある。

本発明の第2の目的は、従来技術で存在していた問題を解決する力率補正回路を提供することにある。

本発明の第3の目的は、小型で経済的なスイッチング電源供給器を提供する力率補正回路を提供することにある。

上述の目的を達成するために、本発明の力率補正回路は、直列に接続された第1の巻線、ダイオード、インダクタおよび第1のコンデンサを含む。インダクタは、ダイオードからの入力電圧をフィルタするために使用される。第1の巻線は変圧器の追加の巻線である。1次巻線は、インダクタと第1のコンデンサとの間に接続される。第1の巻線の極性は1次巻線の極性と反対である。第2のコンデンサは1次巻線に接続され、1次巻線を制御して第1のコンデンサを通る電圧を生成する。この電圧は変圧器を通って第1の巻線へ伝送される。この伝送された電圧は第1のコンデンサの電圧を昇圧させて力率を向上させる。

本発明の力率補正回路構造は、様々なスイッチング電源供給器へ用いることができる。本発明の回路構造により、高い力率と、比較的小さい体積とを達成することができる。また、本発明は追加のインダクタや追加の力率補正クロックも必要ないため、回路構造のサイズや製造コストを減らすことができる。

以下、本発明の力率補正回路を好適な実施形態により示すが、これは本発明の趣旨と領域を何ら制限するものではない。また当該技術に習熟している者なら分かるように、本発明の力率補正回路構造は、様々なスイッチング電源供給器へ用いることができる。

本発明の回路構造は、力率補正回路およびスイッチング電源供給器を含む。

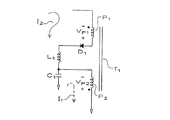

図7は、本発明の好適な一実施形態によるフライバック型スイッチング電源供給器で使用されるアクティブ型力率補正回路を示す回路図である。本発明の力率補正回路は、フォワード型(forward-type)、プッシュプル型(push-pull-type)、ハーフブリッジ型(half-bridge-type)、フルブリッジ型(full-bridge-type)、抵抗トランジスタ制御型(resistor-capacitor-control-type)などその他の種類のコンバータに使用することもできる。

図7は、本発明の好適な一実施形態によるフライバック型スイッチング電源供給器で使用されるアクティブ型力率補正回路を示す回路図である。本発明の力率補正回路は、フォワード型(forward-type)、プッシュプル型(push-pull-type)、ハーフブリッジ型(half-bridge-type)、フルブリッジ型(full-bridge-type)、抵抗トランジスタ制御型(resistor-capacitor-control-type)などその他の種類のコンバータに使用することもできる。

図7に示すように、変圧器T1は1次巻線P1、第2の巻線Sおよび追加の力率補正回路710の巻線P1を有する。力率補正回路710を使用することによりスイッチング電源供給器の力率は向上する。電圧VS1は交流入力電源であり、電流IS1は交流入力電源により生成された電流である。ブリッジ整流器BD1は交流電源を直流電源に整流する。コンデンサC3は入力端からノイズをフィルタするために使用される。高周波パルス信号制御回路712は、PWM信号を出力してスイッチングトランジスタ714を制御する。フィードバックシステム716は、出力端から伝送される出力信号VOを受信し、フィードバック信号を高周波パルス信号制御回路712へ送信する。続いて、高周波パルス信号制御回路712は出力信号VOを安定させるために、スイッチングトランジスタ714へ送信されるPWM信号のデューティサイクル(duty cycle)を調整する。

本発明の好適な実施形態によると、力率補正回路710は直列に接続された巻線P1、ダイオードD1、インダクタLおよびコンデンサC1を含む。インダクタLは、ダイオードD1からの入力電圧をフィルタするために使用される。巻線P1と1次巻線P2とは同じ鉄心中に設けられ、互いに反対の極性を有する。そのため1次巻線P2は、1次巻線P2と反対の巻線P1中の電圧を送信することができる。

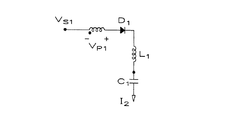

図8は、補助電源供給器が示されていない一次側回路を示す簡略回路図である。図8が示す点線は電流I1の方向を示す。高周波パルス信号制御回路によりスイッチングトランジスタ714が導電されると、オリジナル電圧VC1を有するコンデンサC1は、巻線P2を介して電流I1により放電を行う。その結果、エネルギーが巻線P2に蓄えられ、巻線P2中に電圧VP2が生成される。また、スイッチングトランジスタ714がオフされると、電力が鉄心から第2の巻線Sおよび巻線P1へ伝送される。続いて、VP2と反対の電圧VP1が巻線P1中に生成されると、電力が負荷(図示しない)および巻線P1に提供される。電圧VP1の大きさは、スイッチングトランジスタ714が導電されるデューティ時間と、1次巻線P2および巻線P1の巻線比率と関連する。巻線P1を通過する電圧VP1は次のように示される。

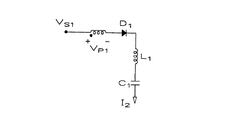

図9は、巻線P1の極性の電圧VP1を示す拡大回路図である。電圧VS1は交流電源の入力電圧である。そのため、ダイオードD1に印加される入力電圧VD1は次のように示される。

入力電圧VD1がコンデンサの電圧VC1よりも大きいとき、ダイオードD1は順バイアスであり、このときにダイオードD1は導電されて電流I2が生成される。本発明の好適な一実施形態によると、巻線P1および巻線P2は、スイッチングトランジスタが導電されたときに、入力電圧VD1が電圧VC1よりも常に大きくなるように構成されている。図8の実線は電流I2の方向を示し、電流I2はコンデンサC1を充電する。

高周波パルス信号制御回路がスイッチングトランジスタ714をオフすると、電力は鉄心から第2の巻線S1へ伝送される。続いて、電力が第2の巻線S1から負荷(図示せず)およびコンデンサC2へ提供される。このとき巻線P1の極性は逆転する。図10は、巻線P1の電圧VP1極性を示す拡大回路図である。電圧VS1は交流入力電源である。従って、ダイオードD1に印加される入力電圧VD1は以下の通りである。

本発明の好適な一実施形態によると、巻線P1および巻線P2は、スイッチングトランジスタがオフされるときに、入力電圧VD1が電圧VC1よりも常に小さくなるように構成されている。そのため、ダイオードD1は逆バイアスされ、コンデンサC1を充電するダイオードD1には電流が流れない。

一方、図7に示すように、出力電圧VOはフィードバックシステムへ伝送される。フィードバックシステムは、信号を高周波パルス信号制御回路712へフィードバックすることによりPWM信号のデューティサイクルを修正する。例えば、出力電圧が所定値よりも低いときには負荷に供給される電力が十分でないため、フィードバック信号はPWM信号のデューティサイクルを延長して、スイッチングトランジスタ714の導電時間を延ばす。その結果、変圧器T1の1次巻線から第2の巻線へ電力が伝送される時間が増える。そして、第2の巻線へ供給される電力が増大されることにより、出力電圧VOが増大されて所定値を得ることができる。しかしながら、出力電圧が所定値よりも高いときには、負荷に供給される電力が過剰となり、この場合にはPWM信号のデューティサイクルを減らす必要がある。

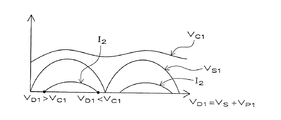

図11は、本発明の一実施形態による臨界電圧におけるVC1およびVS1と、入力電流I2との関係を示す波形図である。図8および図11に示すように、電圧VS1は交流入力電源である。電圧VC1はコンデンサC1を通る電圧である。電流I2はコンデンサC1を充電する電流である。入力電圧VD1はダイオードD1へ印加される電圧である。

従って、入力電圧VD1がコンデンサの電圧VC1よりも大きいとき、ダイオードD1は順バイアスとなり、このときにダイオードD1は導電されて電流I2が生成される。そして、電流I2がコンデンサC1を充電するため、力率補正を向上することができる。また、入力電圧VD1がコンデンサの電圧VC1よりも小さいとき、ダイオードD1は逆バイアスとなり、このときダイオードD1はオフとなるため電流I2は生成されない。そして、巻線P1と巻線P2との巻数比率が1に近づくと、力率も1に近づく。

本発明では好適な実施形態を前述の通り開示したが、これらは決して本発明を限定するものではなく、当該技術に熟知するものなら誰でも、本発明の主旨と領域を脱しない範囲内で各種の変更や修正を加えることができる。従って、本発明の保護の範囲は、特許請求の範囲で指定した内容を基準とする。

716 フィードバックシステム、712 高周波パルス信号制御回路、710 力率補正回路、714 スイッチングトランジスタ、VS1、VC1、VP1、VP2 電圧、VO 出力電圧、T1 変圧器、BD1 ブリッジ整流器、P1、P2、S 巻線、D1、D2、D3、D4 ダイオード、L、L1 インダクタ、C1、C2、C3、C4 コンデンサ、Q1、Q2 スイッチ、VHG、VLG PWM信号、IPC、IS1、I1、I2 電流

Claims (23)

- 力率補正回路と、スイッチング素子に接続された第2の巻線および1次巻線を有するコンバータと、を含むスイッチング電源供給器の力率を向上させる力率補正回路であって、

前記1次巻線と反対の極性を有する巻線と、

前記巻線に接続されたダイオードと、

前記1次巻線に接続された共通のノードを有する前記ダイオードに接続されたコンデンサと、

を備えることを特徴とする力率補正回路。 - ノイズをフィルタするインダクタをさらに備えることを特徴とする請求項1記載の力率補正回路。

- 前記巻線、前記第2の巻線および前記1次巻線は、同じ鉄心に巻かれることを特徴とする請求項1記載の力率補正回路。

- 前記コンバータは、フォワード型、プッシュプル型、ハーフブリッジ型、フルブリッジ型または抵抗トランジスタ制御型のコンバータであることを特徴とする請求項1記載の力率補正回路。

- 前記巻線と前記1次巻線との巻数比率が1に近いことを特徴とする請求項1記載の力率補正回路。

- 前記スイッチング素子は、前記コンデンサを制御して前記1次巻線を充電することを特徴とする請求項1記載の力率補正回路。

- 前記コンデンサは、前記ダイオードが順バイアスのときに充電されることを特徴とする請求項1記載の力率補正回路。

- 前記ダイオードが逆バイアスのときに、前記1次巻線を介して前記第2の巻線へ電力が伝送されることを特徴とする請求項1記載の力率補正回路。

- 力率補正回路と、スイッチング素子に接続された第2の巻線および1次巻線を有するコンバータと、を含むスイッチング電源供給器の力率を向上させる力率補正回路であって、

前記1次巻線と反対の極性を有する巻線と、

前記巻線に接続されたダイオードと、

前記ダイオードに接続されたインダクタと、

前記1次巻線に接続された共通のノードを有する前記インダクタに接続されたコンデンサと、

を備えることを特徴とする力率補正回路。 - 前記インダクタは、ノイズをフィルタすることを特徴とする請求項9記載の力率補正回路。

- 前記巻線、前記第2の巻線および前記1次巻線は、同じ鉄心に巻かれることを特徴とする請求項9記載の力率補正回路。

- 前記コンバータは、フォワード型、プッシュプル型、ハーフブリッジ型、フルブリッジ型または抵抗トランジスタ制御型のコンバータであることを特徴とする請求項9記載の力率補正回路。

- 前記巻線と前記1次巻線との巻数比率は1に近いことを特徴とする請求項9記載の力率補正回路。

- 前記スイッチング素子は、前記コンデンサを制御して前記1次巻線を充電することを特徴とする請求項9記載の力率補正回路。

- 前記コンデンサは、前記ダイオードが順バイアスのときに充電されることを特徴とする請求項9記載の力率補正回路。

- 前記ダイオードが逆バイアスのときに、前記1次巻線を介して前記第2の巻線へ電力が伝送されることを特徴とする請求項9記載の力率補正回路。

- 力率補正回路と、スイッチング素子に接続された第2の巻線および1次巻線を有するコンバータと、を含むスイッチング電源供給器の力率を向上させる力率補正回路であって、

前記1次巻線と反対の極性を有する巻線と、

前記巻線に接続されたダイオードと、

前記ダイオードに接続されたインダクタと、

前記インダクタに接続されたコンデンサと、を備え、

前記巻線、前記第2の巻線、および前記1次巻線は、同じ鉄心に巻かれ、

前記コンデンサおよび前記インダクタは、前記1次巻線に接続される共通のノードを有することを特徴とする力率補正回路。 - 前記インダクタは、ノイズをフィルタすることを特徴とする請求項17記載の力率補正回路。

- 前記コンバータは、フォワード型、プッシュプル型、ハーフブリッジ型、フルブリッジ型または抵抗トランジスタ制御型のコンバータであることを特徴とする請求項17記載の力率補正回路。

- 前記巻線と前記1次巻線との巻数比率は1に近いことを特徴とする請求項17記載の力率補正回路。

- 前記スイッチング素子は、前記コンデンサを制御して前記1次巻線を充電することを特徴とする請求項17記載の力率補正回路。

- 前記コンデンサは、前記ダイオードが順バイアスのときに充電されることを特徴とする請求項17記載の力率補正回路。

- 前記ダイオードが逆バイアスのときに、前記1次巻線を介して前記第2の巻線へ電力が伝送されることを特徴とする請求項17記載の力率補正回路。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/814,231 US7061779B2 (en) | 2004-04-01 | 2004-04-01 | Power factor correction circuit |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005295793A true JP2005295793A (ja) | 2005-10-20 |

Family

ID=35050175

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005101067A Pending JP2005295793A (ja) | 2004-04-01 | 2005-03-31 | 力率補正回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7061779B2 (ja) |

| JP (1) | JP2005295793A (ja) |

| CN (1) | CN1677812A (ja) |

| DE (1) | DE102005014734A1 (ja) |

| TW (1) | TW200534072A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009537829A (ja) * | 2006-05-22 | 2009-10-29 | ヴァリアン オーストラリア ピーティーワイ.エルティーディー. | 分光分析用の発電機 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100826246B1 (ko) * | 2004-08-27 | 2008-04-29 | 삼성전자주식회사 | 전원공급장치 및 전원공급방법 |

| US7355868B2 (en) * | 2005-03-31 | 2008-04-08 | International Rectifier Corporation | Current sense method for bridgeless boost (BLB) PFC circuit using single current transformer |

| US7218060B1 (en) * | 2006-03-07 | 2007-05-15 | System General Corp. | Flyback ballast for fluorescent lamp |

| US7903442B2 (en) * | 2006-11-30 | 2011-03-08 | Dell Products L.P. | Apparatus and methods for power conversion |

| US8093871B2 (en) * | 2007-11-16 | 2012-01-10 | Jackman John F | Power distribution system control and monitoring |

| TWI384898B (zh) * | 2008-06-18 | 2013-02-01 | 台達電子工業股份有限公司 | 可調光之發光二極體驅動電路 |

| WO2010148329A1 (en) * | 2009-06-19 | 2010-12-23 | Robertson Transformer Co. | Multimodal led power supply with wide compliance voltage and safety controlled output |

| CN102339085B (zh) * | 2011-05-27 | 2013-11-06 | 深圳和而泰智能控制股份有限公司 | 电磁功率设备的测控装置 |

| KR102065471B1 (ko) | 2012-10-23 | 2020-01-14 | 삼성디스플레이 주식회사 | 백라이트 유닛 및 그것을 포함하는 표시 장치 |

| CN103840670A (zh) * | 2013-01-04 | 2014-06-04 | 李珏莹 | 一种节能型高频开关电源 |

| US9036386B2 (en) | 2013-07-22 | 2015-05-19 | Regal Beloit America, Inc. | Interleaved two-stage power factor correction system |

| US10461654B2 (en) | 2017-05-04 | 2019-10-29 | Dell Products, Lp | Power supply light load efficiency control circuit |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6473318B1 (en) * | 2000-11-20 | 2002-10-29 | Koninklijke Philips Electronics N.V. | Leakage energy recovering system and method for flyback converter |

| US6314002B1 (en) * | 2000-11-20 | 2001-11-06 | Philips Electronics North America Corporation | Voltage clamping system and method for a DC/DC power converter |

| JP3741035B2 (ja) * | 2001-11-29 | 2006-02-01 | サンケン電気株式会社 | スイッチング電源装置 |

| US6834002B2 (en) * | 2003-01-31 | 2004-12-21 | Entrust Power Co., Ltd. | Power factor correction circuit |

-

2004

- 2004-04-01 US US10/814,231 patent/US7061779B2/en not_active Expired - Fee Related

-

2005

- 2005-03-25 TW TW094109439A patent/TW200534072A/zh unknown

- 2005-03-31 CN CNA2005100626567A patent/CN1677812A/zh active Pending

- 2005-03-31 DE DE102005014734A patent/DE102005014734A1/de not_active Ceased

- 2005-03-31 JP JP2005101067A patent/JP2005295793A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009537829A (ja) * | 2006-05-22 | 2009-10-29 | ヴァリアン オーストラリア ピーティーワイ.エルティーディー. | 分光分析用の発電機 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1677812A (zh) | 2005-10-05 |

| US7061779B2 (en) | 2006-06-13 |

| TW200534072A (en) | 2005-10-16 |

| US20050219869A1 (en) | 2005-10-06 |

| DE102005014734A1 (de) | 2005-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Kim et al. | High-efficiency LLC resonant converter with high voltage gain using an auxiliary LC resonant circuit | |

| US6834002B2 (en) | Power factor correction circuit | |

| JP7439671B2 (ja) | スイッチング電源装置および電力供給システム | |

| US9667153B2 (en) | Switching power supply apparatus for generating control signal for lowering switching frequency of switching devices | |

| JP2003518714A (ja) | 一体化磁気部品を具えた高電力電子安定器 | |

| KR20030052989A (ko) | 스위칭 전원장치 | |

| KR101769335B1 (ko) | 멀티 토플러지를 이용한 dc/dc 컨버터 | |

| JP2005295793A (ja) | 力率補正回路 | |

| JP2000295852A (ja) | 電源供給装置 | |

| JP2010124567A (ja) | スイッチング電源装置 | |

| US20120194070A1 (en) | Operating an electrodeless discharge lamp | |

| JP2001006890A (ja) | 放電灯点灯回路 | |

| JPH113789A (ja) | 放電灯の点灯回路 | |

| EP1001514A2 (en) | Switched power converter with hold-up time and harmonics reduction | |

| KR20170104434A (ko) | 공진형 dc-dc 컨버터 | |

| JPH11164552A (ja) | 電源装置 | |

| KR102030918B1 (ko) | 작은 출력전류 리플을 갖는 고효율 충전기 | |

| JP2022006847A (ja) | 昇圧型電流共振dc-dcコンバータ | |

| JP5141982B2 (ja) | 電源装置 | |

| KR101937013B1 (ko) | 역률 개선 컨버터 | |

| JP4649729B2 (ja) | 電源装置及び放電灯点灯装置 | |

| KR101005065B1 (ko) | 유전체 장벽형 무수은 평판 형광램프용 플라이백 포워드 결합 컨버터 회로 | |

| JP4415363B2 (ja) | スイッチング電源 | |

| JP7772579B2 (ja) | 直流電源装置 | |

| JP2007288855A (ja) | スイッチング電源装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070731 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20071225 |