JP2005295250A - 薄膜圧電共振器及びその製造方法 - Google Patents

薄膜圧電共振器及びその製造方法 Download PDFInfo

- Publication number

- JP2005295250A JP2005295250A JP2004108049A JP2004108049A JP2005295250A JP 2005295250 A JP2005295250 A JP 2005295250A JP 2004108049 A JP2004108049 A JP 2004108049A JP 2004108049 A JP2004108049 A JP 2004108049A JP 2005295250 A JP2005295250 A JP 2005295250A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- thin film

- piezoelectric resonator

- film piezoelectric

- silicon substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

Abstract

【課題】 スプリアス振動を起こす等の不具合を生ずることのない薄膜圧電共振器を得る。

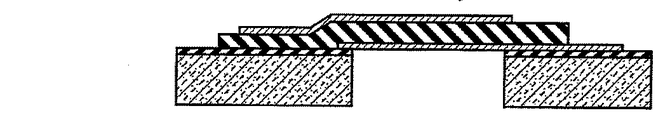

【解決手段】 第二のシリコン基板2上に貫通孔が形成された第一のシリコン基板1が接着され、その上に薄膜圧電共振器本体が形成される。

【選択図】 図1

【解決手段】 第二のシリコン基板2上に貫通孔が形成された第一のシリコン基板1が接着され、その上に薄膜圧電共振器本体が形成される。

【選択図】 図1

Description

本発明は,高周波フィルタや高周波発振器として応用が可能な、圧電体薄膜の厚み縦振動を用いた薄膜圧電共振器、及びその製造方法に関する。

近年無線通信技術はめざましい発展を遂げ、さらに情報の高速伝送を目的とした開発が続けられている。これら無線通信技術で用いられる周波数域は、PHSシステムや第3世代携帯通信、無線LANなどの導入により2GHz前後での周波数帯も市場において広く使われだし、加入者の数、端末数なども飛躍的に増大している。情報伝送量の高速化を目的に搬送波の周波数そのものはさらに高周波化をたどり、無線LANシステムにおいては5GHz帯までの商用化も開始された。

これら高周波通信機器に関して小型、軽量化の要求は強く、特にパーソナルコンピューター(PC)用途においてはPCカードでの使用ができるよう、薄く製作することが非常に重要である。PCカード等の無線機器は一般に高周波(RF)を処理する、RFフロントエンド部とディジタル信号処理を行うベースバンド(BB)部に大別される。このうちBB部は信号の変・復調をディジタル信号処理で行う部分であり、基本的にはSi基板をベースとしたLSIチップによって構成することができるため、BB部の高さは容易に1mm以下程度にまで低くすることができる。一方RF部は高周波の信号をアナログ信号として増幅や周波数変換などを行う部分であり、LSIチップだけで構成するのは難しく、発振器やフィルターなど多くの受動部品を含む複雑な構成となる。受動部品のうち、フィルターは従来、誘電体フィルターやLCフィルターが用いられていたがこれらの部品は高周波信号を空洞共振器やLC回路の通過帯域特性を用いてフィルタリングするため、本質的に小型化が難しく、数mmの高さ以下にするのが極めて困難であった。このためこれらの高周波機器の小型化、薄型化に限界があった。

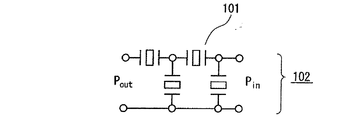

このような課題を解決するために、薄膜圧電共振器(FBAR:Film Bulk Acoustic Wave Resonator)が注目されている。薄膜圧電共振器は窒化アルミニウム(AlN)や酸化亜鉛(ZnO)からなる薄膜圧電体を2枚の電極で挟み込み、基板上に形成された空洞上に作りつけた素子である。図5にその概略構造図を示す。薄膜圧電共振子は、空気層に接した下部電極及び上部電極と圧電体膜を合わせた厚み方向に周波数の共振を得るもので、成膜で作りやすい範囲の0.5μm〜数μmの厚さが数GHzに相当し、GHz帯の高周波領域の共振に有利である。帯域通過フィルター応用に関してはこの薄膜圧電共振子2個を直列接続、1個を並列接続するラダー型で構成することができる。並列接続と直列接続の共振器の中心周波数をわずかに変え、例えば直列に接続した共振器の共振周波数と並列に接続した共振器の反共振周波数が一致するように調整することで、帯域通過フィルターを得ている。薄膜圧電共振器は半導体基板上に薄膜を主に構成するため、非常に小型化が容易で特に高さに関しては既存フィルターでは困難な1mm以下の寸法を容易に実現できる。またトランジスタやIC、LSIとの実装も容易である。

従来のFBARの構造として、図17のような構成がある。しかしながら良好な特性の薄膜圧電共振器を作製するのには次のような課題があった。

(1)基板裏面にキャビティを形成する際、基板の厚みがかなりあるため、キャビティ形成のためのエッチングを行うと、基板裏面の開口径と基板表面の開口径の大きさの違いが大きくなる(寸法変換差が大きくなる)。

(2)基板裏面のキャビティがそのまま薄膜圧電共振器を露出する構造となるため、基板裏面からの水分の浸入を防止することができない。

(1)基板裏面にキャビティを形成する際、基板の厚みがかなりあるため、キャビティ形成のためのエッチングを行うと、基板裏面の開口径と基板表面の開口径の大きさの違いが大きくなる(寸法変換差が大きくなる)。

(2)基板裏面のキャビティがそのまま薄膜圧電共振器を露出する構造となるため、基板裏面からの水分の浸入を防止することができない。

このような問題点を解決するため、特許文献1のような構造が考えられている(図18参照)。図18において、空洞部206は比較的層厚の薄い第1の半導体層209に形成されるため、上記(1)のような、寸法変換差の問題が発生しにくい。また、空洞部6は半導体基板1上に形成されるため、薄膜圧電素子が露出することはなく、上記(2)の問題も生じにくい。

特開平9−83029号公報

しかしながら、図18の構造は、以下の問題点がある。すなわち、半導体基板201上に圧電素子を形成した後、半導体基板201表面から空洞部206形成のためのエッチングを施さなければならない。そのため、空洞部206の横幅が大きくなり、第1の電極202、圧電体薄膜203、第2の電極204を支持力を大きく損なうことになり、ひいては薄膜圧電素子がスプリアス振動を起こす可能性が高くなるという問題点がある。

本発明は上記の問題点を解決すべくなされたもので、スプリアス振動を起こす等の不具合を生ずることのない薄膜圧電共振器を得ることを目的とする。

上記の課題を解決するために本発明の薄膜圧電共振器は、表面、裏面を貫く第一の貫通孔が形成される第一の基板と、前記第一の基板下に載置される第二の基板と、前記貫通孔上に形成され、かつその幅が前記貫通孔の幅より大きい下部電極と、前記下部電極上に形成される圧電膜と、前記圧電膜上に形成される上部電極と、を具備し、前記貫通孔と前記第一の基板の表面とでキャビティを構成することを特徴とする。

また、本発明の薄膜圧電共振器の製造方法は、第一の基板表面に下部電極、圧電膜、上部電極を形成する工程と、前記第一の基板裏面からの気相エッチングにより、前記下部電極に達し、前記第一の基板を貫通する貫通孔を形成する工程と、前記第一の基板裏面に第二の基板を貼り合わせる工程とを具備することを特徴とする。

本発明によれば、キャビティを第一の基板の裏面からの異方性エッチングにより形成するため、キャビティの幅を所望の大きさにすることができる。従って、上部電極、圧電膜、下部電極の支持面積を大きくすることができるため、不要なスプリアス振動が生じにくくなる。

本発明者らは裏面空洞型の薄膜圧電共振器の高性能化と実装パッケージ法について鋭意検討を行った。その結果、この目的のためには、パッケージを構成する層構造を最適化することが重要であることを見出した。ここで薄膜圧電共振器とはセラミック共振子やSAWデバイスとは異なり、薄膜の厚み方向の弾性波を用いた共振、すなわち薄膜をバルクとして膜全体の弾性波を用いた共振器のことである。以下図面を用いて詳細に説明する。

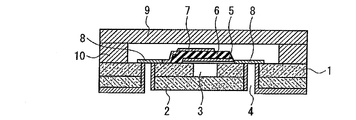

図1は本発明に係わる第1の実施例を示すものである。薄膜圧電共振器は、第一シリコン基板1上に形成され、下部電極5をAl、圧電体膜6をAlN、上部電極7をAlとする2枚の電極で挟み込み込まれた橋梁を共振させ共振特性を得るものである。下部電極5はAlNの配向性を高めるため、下層がアモルフォス構造となる二重構造となっている。AlNは配向制御することで、Q値(Quality factor:共振の鋭さを表す値)向上等の好特性を得る。スパッタで成膜した本実施例では配向性はX線のロッキングカーブで1.5゜以下に制御することができる。キャビティ3は第一シリコン基板1裏面側から反応性イオンエッチング(RIE)により基板をくり抜くことで形成される。電極パッド8は金(Au)、ビアホール4の内面もメッキによりAuで被覆されている。第二のシリコン基板2はその表面が清浄表面となっており、第二のシリコン基板2表面と第一のシリコン基板の裏面とが真空中にて直接接着による貼りあわせで形成される。上部電極7の上部にはこの薄膜圧電共振器をパッケージとした際の蓋に該当する第三のシリコン基板9が形成されており、この第三のシリコン基板9とシーリング(ガスケット)10、及び下部電極5、圧電体膜6、上部電極7からなる圧電共振器本体との間で中空が形成され、この中空と空洞3中に圧電共振器本体を配置することで、共振動作を生じさせることになる。ここで、キャビティ3の幅(図1紙面に平行な方向における幅)は、下部電極5の幅(図1紙面に平行な方向における幅)よりも小さくなっている。

シーリング10により、第一のシリコン基板1と第三のシリコン基板9とが強力に接着されるため、その後のダイシング工程で剥がれるなどの問題も起きない。第二のシリコン基板2、第三のシリコン基板9は所望の仕様の厚さを維持する目的から200μm程度とすることが適当である。これらの厚さは実装時や製造時の要求により、第一のシリコン基板1の厚さよりもフレキシブルに設定することができる。

本構造において最適化したのは第一のシリコン基板1の厚さである。通常のシリコン基板厚である400〜600μmをRIEでエッチングすると、途中でオーバーハングやノッチ(エッチングに用いるマスクからの寸法差)が出る。そればかりでなく、エッチング時間も増加し、製造上大きな問題となる。そこで、基板の厚さを200μm以下とするとこれらの問題が激減することを発明者らの鋭意研究により見出した。この根拠を以下に示す。実用的なエッチングレートとして5μm以上を維持するとオーバーハングやノッチ量として深さ方向に対して1%以下に制御するのは難しい。裏面空洞の位置ずれは寄生容量を薄膜共振素子に作りつけてしまうために3μm以下とする必要があるが、これらの関係を満たすためにはマージンを考慮して200μm以下にする必要がある。

図14に実際に基板厚を変えて行ったノッチ量に対する影響に関す実験結果を示す。この関係図に示すように200μm以下が適正なノッチ量範囲に制御するのに必須な基板厚となることがわかる。100μm以下にするとさらに制御性とスループットの上では望ましい。しかし基板が薄くなるため、取り扱いに関しては注意が必要となる。50μm前後が作製上の限界となる。

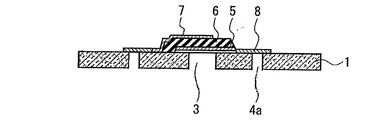

図2乃至8に本実施例の製造方法を示す。まず、図2に示すように第一のシリコン基板1上にそれぞれアルミニウム(Al)等の材料からなる下部電極5、窒化アルミニウム(AlN)等の材料からなる圧電体膜6、アルミニウム(Al)等の材料からなる上部電極7となる材料を、10-7Torr以下に維持された真空チャンバーを有するスパッタ装置により、連続スパッタ法により成膜する。そしてアルゴン(Ar)等の不活性ガスで希釈されたCl2等の塩素系ガスを用いたドライエッチングにより、下部電極5、圧電体膜6、上部電極7をそれぞれ形成する。電極パッド8もこの段階でスパッタ法、ドライエッチングによるパターニングで形成する。

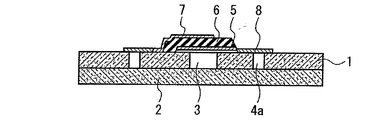

次に、図3に示すように、上部構造側をシリンダー状の冶具に、例えば電子用ワックスを用いて接着し、AlNを含むスラリーにより第一のシリコン基板1裏面を、厚さ150μmとなるよう研磨する。

そして図4に示すように、冶具につけたまま、裏面空洞を、例えばボッシュシステムと呼ばれる、SF6系のガスを用いて、エッチングと堆積とを交互に繰り返すタイプの高速反応性イオンエッチング(高速RIE)により形成する。このとき、裏面空洞の幅(図1紙面に平行な方向における幅)は、下部電極5の幅(図1紙面に平行な方向における幅)よりも小さくなるようにエッチングする。エッチングレートは約10μm/minとする。

高速RIE後、図5に示すように、底部となる第二のシリコン基板2を直接接着技術で貼りあわせる。直接接着とは清浄表面同士が真空中で原子層オーダで接触し、熱を加えることにより、原子間の結合が形成されることで接着する方法である。本実施例のような製造方法においては、例えば1kg/cm2の加重をかけ300℃の温度で行う。

その後、図6に示すように、再度高速RIEを用いてビアホール4を形成し、図7に示すようにビアホール4内面から電極パッド8の裏面部にかけてメッキにてメタライズコートする。本実施例では、例えばNi、Auの積層構造を用いる。この段階で上部構造を冶具から剥離して、高周波パラメータ測定装置により、圧電薄膜共振子の共振周波数テストを行い、仕様に合うように周波数を調整する目的でトリミングを行う。トリミングは、例えば表面あるいは裏面より電極の一部をスパッタエッチングを行う方法で実施する。

最後に、図8に示すように、感光性ポリイミドを第一のシリコン基板1上にスピンコートし、シーリング10となる部分をフォトリソグラフィ法で形成し、350℃程度でのキュアを行う。一方第三のシリコン基板9裏面にもポリイミドのスピンコートを施しておき、シーリング10との貼りあわせを行う。貼りあわせ後、再度350℃程度のキュアを行う。このキュアにより、シーリング10の成分となるポリイミドと、第三のシリコン基板10裏面にコートされたポリイミドとが強力に接着される。その後、パッケージ化された薄膜圧電共振器はダイシングして個片化されるが、この貼りあわせ方法によれば、ダイシング工程時にも第三のシリコン基板9が剥がれることはない。

本実施例では基板はすべてシリコン基板としたが、ポリイミド基板等、樹脂製の基板を用いても良い。ただし、水分の浸透や透過性に関しては十分注意をはらう必要がある。またSi基板を用いる際も基板どうしの接着やシーリングとの接着に十分注意を払う必要がある。接着部が不十分であると、水分が浸透し、信頼性に関して深刻な課題となる。

次に、本発明に係わる実施例2につき、図面を用いて説明する。図9は第2の実施例の薄膜圧電共振器の、第三のシリコン基板9を取り除いた状態での平面図、図10はA−A´における断面図(第三のシリコン基板9は接着された状態)である。本実施例の特徴は薄膜圧電共振器の空洞3の気圧と第三のシリコン基板9、シーリング10、薄膜圧電共振器本体とで取り囲まれた中空部分の気圧とが同一気圧になるように調整用の抜き穴11を、下部電極5、圧電体膜6、上部電極7を貫くように設けたことにある。その他符号が実施例1と同一の部分は同様な形状を有しているため、詳細な説明を省略する。

実施例1のように空洞3と中空部分とが分離されている場合、製造時や使用時の温度環境などにより、それぞれの圧力が異なった場合、薄膜圧電共振子がたわみ、特性劣化が生じ、最悪の場合、薄膜圧電共振器自体が破壊されることもある。本実施例のように抜き穴を設けておくと、これらの問題は生じにくい。本実施例では下部電極5、圧電体膜6、上部電極7を貫くように直接抜き穴を設けたが、下部電極5、圧電体膜6、上部電極7を貫通せず、間接的に抜き穴を設けてもよい。本実施例では実施例1と比べて製造時の歩留まりが10%向上し、動作時の突発劣化も激減した。

図11乃至13は本発明に係わる第3の実施例の製造方法を示すものである。実施例1における図3の工程までは同様である。本実施例の特徴は、図11に示すように、薄膜圧電共振器本体を冶具につけたまま、空洞3とビアホール4aを高速RIEにより同時にエッチングすることにある。空洞3の幅は実施例1と同様、下部電極5の幅よりも小さくなっている。この工程によりビアホールのエッチングの工程時間を大幅に短縮することが可能となる。

空洞3、ビアホール4aの同時エッチング後、図12に示すように、第一のシリコン基板1の裏面と第二のシリコン基板2の表面とを接着し、図13に示すように、再度RIEにより、ビアホール4aの形成位置に合わせ、ビアホール4aより開口径の大きいビアホール4bを高速RIE等の方法でエッチングする。本実施例によれば、ビアホール4aと4bとの位置合わせのマージンを大きくとることができ、もっとスループットの高いサンドブラストやレーザ加工などを併用することも可能となる。

次に、以上の実施例により作成された薄膜圧電共振器のアプリケーションについて、図15、16を用いて説明する。

薄膜圧電共振器101は、図15に示すように直列ないし並列に複数個並べて梯子型フィルタ102を形成することにより、移動体通信機のRFフィルタとして利用することができる。

また、図16に示すように、薄膜圧電共振器101、バリアブルキャパシタ104および増幅器105を組合せることで、移動体通信機の電圧制御発振器(Voltage Controlled Oscillator: VCO)103として 利用することができる。

なお上記実施例における製造工程はそれぞれ単独で用いることも可能であるが、製造工程の一部をそれぞれ別の実施例の製造工程と組み合わせて用いてもさらに大きな効果を発揮することができる。

1 … 第一のシリコン基板

2 … 第二のシリコン基板

3 … 空洞

4、4a、4b … ビアホール

5 … 下部電極

6 … 圧電体膜

7 … 上部電極

8 … 電極パッド

9 … 第三のシリコン基板

10 … シーリング

11 … 抜き穴

101 … 薄膜圧電共振器

102 … 梯子型フィルタ

103 … 電圧制御発振器(VCO)

104 … バリアブルキャパシタ

105 … 増幅器

201 … 半導体基板

202 … 第1の電極

203 … 圧電体薄膜

204 … 第2の電極

206 … 空洞部

2 … 第二のシリコン基板

3 … 空洞

4、4a、4b … ビアホール

5 … 下部電極

6 … 圧電体膜

7 … 上部電極

8 … 電極パッド

9 … 第三のシリコン基板

10 … シーリング

11 … 抜き穴

101 … 薄膜圧電共振器

102 … 梯子型フィルタ

103 … 電圧制御発振器(VCO)

104 … バリアブルキャパシタ

105 … 増幅器

201 … 半導体基板

202 … 第1の電極

203 … 圧電体薄膜

204 … 第2の電極

206 … 空洞部

Claims (7)

- 表面、裏面を貫く第一の貫通孔が形成される第一の基板と、

前記第一の基板下に載置される第二の基板と、

前記貫通孔上に形成され、かつその幅が前記貫通孔の幅より大きい下部電極と、

前記下部電極上に形成される圧電膜と、

前記圧電膜上に形成される上部電極と、

を具備し、

前記貫通孔と前記第一の基板の表面とでキャビティを構成することを特徴とする薄膜圧電共振器。 - 前記第一の基板の厚さが200μm以下であることを特徴とする請求項1に記載の薄膜圧電共振器。

- 前記第一の基板、第二の基板のいずれかがシリコンよりなることを特徴とする。請求項1、2に記載の薄膜圧電共振器。

- 前記第一の基板、第二の基板に形成され、前記下部電極下、前記上部電極下を貫通する第二の貫通孔を設けることを特徴とする請求項1乃至3に記載の薄膜圧電共振器。

- 前記下部電極、圧電膜、上部電極に、前記キャビティに接続する第三の貫通孔を設けることを特徴とする請求項1乃至4に記載の薄膜圧電共振器。

- 前記第一の基板上にシーリングを介して第三の基板が形成されることを特徴とする請求項1乃至5に記載の薄膜圧電共振器。

- 第一の基板表面に下部電極、圧電膜、上部電極を形成する工程と、

前記第一の基板裏面からの気相エッチングにより、前記下部電極に達し、前記第一の基板を貫通する貫通孔を形成する工程と、

前記第一の基板裏面に第二の基板を貼り合わせる工程と

を具備することを特徴とする薄膜圧電共振器の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108049A JP2005295250A (ja) | 2004-03-31 | 2004-03-31 | 薄膜圧電共振器及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108049A JP2005295250A (ja) | 2004-03-31 | 2004-03-31 | 薄膜圧電共振器及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005295250A true JP2005295250A (ja) | 2005-10-20 |

Family

ID=35327687

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108049A Pending JP2005295250A (ja) | 2004-03-31 | 2004-03-31 | 薄膜圧電共振器及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005295250A (ja) |

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007159116A (ja) * | 2005-12-07 | 2007-06-21 | Samsung Electronics Co Ltd | 複数の素子を相互隔離させるためのエアキャビティを備えたシステムオンチップ構造物、デュプレックサー及びその製造方法 |

| WO2007148459A1 (ja) * | 2006-06-20 | 2007-12-27 | National Institute Of Advanced Industrial Science And Technology | 誘電体構造及びその製造方法 |

| JP2008042878A (ja) * | 2006-07-07 | 2008-02-21 | Ngk Insulators Ltd | 圧電薄膜デバイス |

| JP2008118480A (ja) * | 2006-11-06 | 2008-05-22 | Fujitsu Media Device Kk | 圧電薄膜デバイスおよびその製造方法 |

| JP2009147238A (ja) * | 2007-12-17 | 2009-07-02 | National Institute Of Advanced Industrial & Technology | 誘電体構造体、誘電体構造の製造方法、圧着転写方法、及び保持構造 |

| JP2010141570A (ja) * | 2008-12-11 | 2010-06-24 | Ube Ind Ltd | 圧電薄膜音響共振器およびその製造方法 |

| JP2011138909A (ja) * | 2009-12-28 | 2011-07-14 | Clean Venture 21 Corp | 光電変換素子およびその製造方法、ならびに光電変換装置およびその製造方法 |

| WO2011111732A1 (ja) * | 2010-03-12 | 2011-09-15 | 北陸電気工業株式会社 | Pzt膜を備えたセンサ素子の製造方法 |

| US20120049976A1 (en) * | 2010-09-01 | 2012-03-01 | Samsung Electronics Co., Ltd. | Bulk acoustic wave resonator structure, a manufacturing method thereof, and a duplexer using the same |

| JP2012165132A (ja) * | 2011-02-04 | 2012-08-30 | Taiyo Yuden Co Ltd | 弾性波デバイスの製造方法 |

| JP2018129561A (ja) * | 2017-02-06 | 2018-08-16 | 新日本無線株式会社 | バルク弾性波共振器の製造方法 |

| JP2018536157A (ja) * | 2015-10-28 | 2018-12-06 | コーボ ユーエス,インコーポレイティド | バルク音波(baw)共振器と基板を貫通する流体ビアを有するセンサー装置 |

| CN108964628A (zh) * | 2017-05-18 | 2018-12-07 | 三星电机株式会社 | 体声波谐振器 |

| CN109470367A (zh) * | 2018-11-12 | 2019-03-15 | 中国科学院长春光学精密机械与物理研究所 | 一种基于fbar的宽波段非制冷红外探测器的制备方法 |

| JP2022518313A (ja) * | 2019-12-31 | 2022-03-15 | 中芯集成電路(寧波)有限公司上海分公司 | 共振器及びその形成方法 |

| CN114257193A (zh) * | 2020-09-21 | 2022-03-29 | 中芯集成电路(宁波)有限公司上海分公司 | 薄膜体声波谐振器的制造方法及滤波器 |

| JP2022137818A (ja) * | 2021-03-09 | 2022-09-22 | 太陽誘電株式会社 | 弾性波デバイスおよびその製造方法、フィルタおよびマルチプレクサ |

| JP2023071988A (ja) * | 2019-07-19 | 2023-05-23 | 中芯集成電路(寧波)有限公司上海分公司 | Baw共振器のパッケージングモジュールおよびパッケージング方法 |

| WO2025070357A1 (ja) * | 2023-09-26 | 2025-04-03 | 日東電工株式会社 | Baw共振器、bawデバイス及び電子機器 |

-

2004

- 2004-03-31 JP JP2004108049A patent/JP2005295250A/ja active Pending

Cited By (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007159116A (ja) * | 2005-12-07 | 2007-06-21 | Samsung Electronics Co Ltd | 複数の素子を相互隔離させるためのエアキャビティを備えたシステムオンチップ構造物、デュプレックサー及びその製造方法 |

| WO2007148459A1 (ja) * | 2006-06-20 | 2007-12-27 | National Institute Of Advanced Industrial Science And Technology | 誘電体構造及びその製造方法 |

| JP2008004572A (ja) * | 2006-06-20 | 2008-01-10 | National Institute Of Advanced Industrial & Technology | 誘電体構造及びその製造方法 |

| JP2008042878A (ja) * | 2006-07-07 | 2008-02-21 | Ngk Insulators Ltd | 圧電薄膜デバイス |

| JP2008118480A (ja) * | 2006-11-06 | 2008-05-22 | Fujitsu Media Device Kk | 圧電薄膜デバイスおよびその製造方法 |

| JP2009147238A (ja) * | 2007-12-17 | 2009-07-02 | National Institute Of Advanced Industrial & Technology | 誘電体構造体、誘電体構造の製造方法、圧着転写方法、及び保持構造 |

| JP2010141570A (ja) * | 2008-12-11 | 2010-06-24 | Ube Ind Ltd | 圧電薄膜音響共振器およびその製造方法 |

| JP2011138909A (ja) * | 2009-12-28 | 2011-07-14 | Clean Venture 21 Corp | 光電変換素子およびその製造方法、ならびに光電変換装置およびその製造方法 |

| WO2011111732A1 (ja) * | 2010-03-12 | 2011-09-15 | 北陸電気工業株式会社 | Pzt膜を備えたセンサ素子の製造方法 |

| KR101782447B1 (ko) | 2010-03-12 | 2017-09-28 | 호쿠리쿠 덴키 고교 가부시키가이샤 | Pzt막을 구비한 센서 소자의 제조 방법 |

| CN102792477A (zh) * | 2010-03-12 | 2012-11-21 | 北陆电气工业株式会社 | 具备pzt膜的传感器元件的制造方法 |

| JP5100915B2 (ja) * | 2010-03-12 | 2012-12-19 | 北陸電気工業株式会社 | Pzt膜を備えたセンサ素子の製造方法 |

| CN102792477B (zh) * | 2010-03-12 | 2015-05-27 | 北陆电气工业株式会社 | 具备pzt膜的传感器元件的制造方法 |

| CN104752602A (zh) * | 2010-03-12 | 2015-07-01 | 北陆电气工业株式会社 | 具备pzt膜的传感器元件的制造方法 |

| CN104752602B (zh) * | 2010-03-12 | 2017-07-28 | 北陆电气工业株式会社 | 具备pzt膜的传感器元件的制造方法 |

| US20120049976A1 (en) * | 2010-09-01 | 2012-03-01 | Samsung Electronics Co., Ltd. | Bulk acoustic wave resonator structure, a manufacturing method thereof, and a duplexer using the same |

| US8648671B2 (en) * | 2010-09-01 | 2014-02-11 | Samsung Electronics Co., Ltd. | Bulk acoustic wave resonator structure, a manufacturing method thereof, and a duplexer using the same |

| US9148107B2 (en) | 2011-02-04 | 2015-09-29 | Taiyo Yuden Co., Ltd. | Method for manufacturing acoustic wave device |

| JP2012165132A (ja) * | 2011-02-04 | 2012-08-30 | Taiyo Yuden Co Ltd | 弾性波デバイスの製造方法 |

| JP2018536157A (ja) * | 2015-10-28 | 2018-12-06 | コーボ ユーエス,インコーポレイティド | バルク音波(baw)共振器と基板を貫通する流体ビアを有するセンサー装置 |

| JP2018129561A (ja) * | 2017-02-06 | 2018-08-16 | 新日本無線株式会社 | バルク弾性波共振器の製造方法 |

| CN108964628A (zh) * | 2017-05-18 | 2018-12-07 | 三星电机株式会社 | 体声波谐振器 |

| CN109470367A (zh) * | 2018-11-12 | 2019-03-15 | 中国科学院长春光学精密机械与物理研究所 | 一种基于fbar的宽波段非制冷红外探测器的制备方法 |

| JP2023071988A (ja) * | 2019-07-19 | 2023-05-23 | 中芯集成電路(寧波)有限公司上海分公司 | Baw共振器のパッケージングモジュールおよびパッケージング方法 |

| JP7557893B2 (ja) | 2019-07-19 | 2024-09-30 | 中芯集成電路(寧波)有限公司上海分公司 | Baw共振器のパッケージングモジュールおよびパッケージング方法 |

| US12506458B2 (en) | 2019-07-19 | 2025-12-23 | Ningbo Semiconductor International Corporation (Shanghai Branch) | Packaging module and packaging method of BAW resonator |

| JP7255910B2 (ja) | 2019-12-31 | 2023-04-11 | 中芯集成電路(寧波)有限公司上海分公司 | 共振器及びその形成方法 |

| JP2022518313A (ja) * | 2019-12-31 | 2022-03-15 | 中芯集成電路(寧波)有限公司上海分公司 | 共振器及びその形成方法 |

| CN114257193A (zh) * | 2020-09-21 | 2022-03-29 | 中芯集成电路(宁波)有限公司上海分公司 | 薄膜体声波谐振器的制造方法及滤波器 |

| JP2022137818A (ja) * | 2021-03-09 | 2022-09-22 | 太陽誘電株式会社 | 弾性波デバイスおよびその製造方法、フィルタおよびマルチプレクサ |

| JP7611007B2 (ja) | 2021-03-09 | 2025-01-09 | 太陽誘電株式会社 | 弾性波デバイスおよびその製造方法、フィルタおよびマルチプレクサ |

| WO2025070357A1 (ja) * | 2023-09-26 | 2025-04-03 | 日東電工株式会社 | Baw共振器、bawデバイス及び電子機器 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005295250A (ja) | 薄膜圧電共振器及びその製造方法 | |

| US12088270B2 (en) | Transversely-excited film bulk acoustic resonator package and method | |

| KR100622955B1 (ko) | 박막 벌크 음향 공진기 및 그 제조방법 | |

| CN114553170A (zh) | 低热阻抗的横向激励薄膜体声波谐振器 | |

| US10784838B2 (en) | Air-gap type film bulk acoustic resonator and method of manufacturing the same | |

| EP1469599A2 (en) | Air gap type FBAR, duplexer using the FBAR, and fabricating methods thereof | |

| CN112039485A (zh) | 一种薄膜压电声波滤波器及其制造方法 | |

| JP2003347884A (ja) | 薄膜バルクアコースティック共振器(FBARs)素子及びその製造方法 | |

| CN109687835B (zh) | 薄膜体声波谐振器及其制作方法、滤波器 | |

| CN111130490A (zh) | 电极具有空隙层的体声波谐振器及制造方法、滤波器及电子设备 | |

| US20060202769A1 (en) | Piezoelectric thin film device and method of producing the same | |

| CN113630099B (zh) | 体声波谐振器及制造方法、组件、滤波器及电子设备 | |

| CN108566177A (zh) | 射频谐振器与滤波器 | |

| US7057477B2 (en) | Integration of FBAR filter(s) and on-chip inductors | |

| JP2005333644A (ja) | インダクタが内蔵されたフィルタ、デュプレクサおよびその製造方法 | |

| EP1471636B1 (en) | Film bulk acoustic resonator having an air gap and a method for manufacturing the same | |

| JP3952464B2 (ja) | デュプレクサ | |

| CN110544689B (zh) | 射频前端模块中有源器件和无源单晶器件及单片集成方法 | |

| US7417360B2 (en) | Piezoelectric resonator and method for producing the same | |

| JPH0964675A (ja) | 密閉空洞上の圧電共振器および製造方法 | |

| CN111327291A (zh) | 体声波谐振器及弹性波滤波器装置 | |

| JP2005117665A (ja) | エアギャップ型fbarおよびその製造方法、これを用いたフィルタおよびデュープレクサ | |

| CN1953175A (zh) | 合成射频器件和用于制造该器件的方法 | |

| JP2005110017A (ja) | 高周波フィルタモジュール及びその製造方法 | |

| KR102028719B1 (ko) | Fbar 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070220 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070803 |