JP2005293563A - 半導体装置、無線チップ、icカード、icタグ、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ及び衣類 - Google Patents

半導体装置、無線チップ、icカード、icタグ、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ及び衣類 Download PDFInfo

- Publication number

- JP2005293563A JP2005293563A JP2005063588A JP2005063588A JP2005293563A JP 2005293563 A JP2005293563 A JP 2005293563A JP 2005063588 A JP2005063588 A JP 2005063588A JP 2005063588 A JP2005063588 A JP 2005063588A JP 2005293563 A JP2005293563 A JP 2005293563A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- chip

- antenna

- memory

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

- G06K19/07309—Means for preventing undesired reading or writing from or onto record carriers

- G06K19/07372—Means for preventing undesired reading or writing from or onto record carriers by detecting tampering with the circuit

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B42—BOOKBINDING; ALBUMS; FILES; SPECIAL PRINTED MATTER

- B42D—BOOKS; BOOK COVERS; LOOSE LEAVES; PRINTED MATTER CHARACTERISED BY IDENTIFICATION OR SECURITY FEATURES; PRINTED MATTER OF SPECIAL FORMAT OR STYLE NOT OTHERWISE PROVIDED FOR; DEVICES FOR USE THEREWITH AND NOT OTHERWISE PROVIDED FOR; MOVABLE-STRIP WRITING OR READING APPARATUS

- B42D25/00—Information-bearing cards or sheet-like structures characterised by identification or security features; Manufacture thereof

- B42D25/30—Identification or security features, e.g. for preventing forgery

- B42D25/305—Associated digital information

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/077—Constructional details, e.g. mounting of circuits in the carrier

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- General Engineering & Computer Science (AREA)

- Semiconductor Memories (AREA)

- Credit Cards Or The Like (AREA)

Abstract

【解決手段】非接触型IDチップにおいて、チップ内部に不揮発性のFeRAMを有し、FeRAMに書き込みがおこなわれたかどうかを示すデータも、固有情報書き込み時に書き込みをおこない、そのデータがあるときにはIDチップ内部のFeRAMに情報が新たに書き込めないような回路構成を有する。

【選択図】図1

Description

またメモリ回路にEEPROMを用いた場合、ユーザーが自由に内容を書き換えられる反面、本来のユーザー以外の人が、認証用として書き換えられるべきでない情報を書き換えることが可能になり、偽造を行うことも可能である。従って、そのような偽造を防止するため1回のみの書き込みが可能なIDチップが求められている。

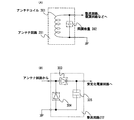

図1において、IDチップに用いる半導体装置100はアンテナ回路101、整流回路102、安定化電源回路103、変調回路104、アンプ105、論理回路106、復調回路107、アンプ108、論理回路109、FeRAMコントロール回路110、FeRAM回路111によって構成されている。また、アンテナ回路101は従来例、図3(A)に示したものと同様である。整流回路102は従来例、図3(B)に示したものと同様である。本実施形態において、アンテナ回路は半導体装置100上に構成されているが、これに限定されずアンテナ回路を半導体装置100の外部に接続しても良い。アンテナを実装した本発明のチップを無線チップとも言う。

アンテナ回路101で受信した交流信号は整流回路102によって整流され、平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源回路103で安定化され、安定化された後の電圧をアンプ105、復調回路107、アンプ108、論理回路109に供給する。

まず、メモリセル700が”1”を出力するような書き込みをする場合を考える。まず、入力端子727に高電位(例えばVDD)を与える。次にビット線デコーダー701を動作させ、ビット線選択スイッチ725をオンさせる。これによって、ビット線713には高電位が供給される。このときプレート線717の電位は中間電位(例えばVDD/2)としておく。次にワード線デコーダー702を動作させ、ワード線715をアクティブとする、それによってトランジスタ705、706はオンとなり、ビット線713と強誘電体容量素子709は短絡される。従って、強誘電体容量素子709にはVDD/2の電圧が印加される。

このようなTFTを用いて19段リングオシレータを構成した場合において、電源電圧3〜5Vにおいて、その発振周波数は1MH以上、好ましくは100MHz以上の特性を有する。電源電圧3〜5Vにおいて、インバータ1段あたりの遅延時間は26ns、好ましくは0.26ns以下を有する。

TFTなどのアクティブ素子の存在しない領域には下地絶縁材料、層間絶縁材料および配線材料が主として設けられている。TFTの活性領域以外の面積は全体の面積の60%以上であることが望ましい。

アクティブ素子の活性領域の厚さは20nm〜200nm、代表的には40〜170nmが好ましい。また、活性領域を広くとる場合は活性領域の厚さを45〜55nmとし、活性領域を狭くとる場合は活性領域の厚さを145〜155nmとすることが好適である。

IDチップ2703を実装したラベル2702と、当該ラベル2702が貼られた肉のパック2701を示す。IDチップ2703はラベル2702の表面に実装していてもよいし、ラベル2702内部に実装してもよい。また野菜等の生鮮食品の場合、生鮮食品を覆うラップにIDチップを実装してもよい。

IDチップを実装する結果、事前に生産ラインに投入される自動車の順序や同色を有する数を調整する必要がない。強いては、自動車の順序や数、それに合わせるように塗装装置を制御するプログラムを設定しなくてすむ。すなわち製造装置は、自動車に実装されたIDチップの情報に基づき、個別に動作することができる。

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

100 半導体装置、101 アンテナ回路、102 整流回路、103 安定化電源回路、104 変調回路、105 アンプ、106 論理回路、107 復調回路、108 アンプ、109 論理回路、110 FeRAMコントロール回路、111 FeRAM回路。

200 半導体装置、201 アンテナ回路、202 整流回路、203 安定化電源回路、204 変調回路、205 アンプ、206 論理回路、207 復調回路、208 アンプ、209 論理回路、210 メモリコントロール回路、211 メモリ回路。

301 アンテナ、302 同調容量、303、304 ダイオード、305 平滑容量。

401 IDチップ、402 アンテナユニット、403 質問器、404 バッグ。

500 メモリセル、501 ビット線デコーダー、502 ワード線デコーダー、503 プレート線デコーダー、504 プリチャージ回路、505〜512 n型メモリトランジスタ(トランジスタ)、513〜520 強誘電体容量素子、521〜524 ビット線、525、526 ワード線、527、528 プレート線、529、530 センスアンプ、531、532 センスアンプ選択スイッチ、533〜536 プリチャージスイッチ、537〜540 ビット線選択スイッチ、541、542 入力端子、543 出力端子。

700 メモリセル、701 ビット線デコーダー、702 ワード線デコーダー、703 プレート線デコーダー、704 プリチャージ回路、705〜708 n型メモリトランジスタ(トランジスタ)、709〜712 強誘電体容量素子、713、714 ビット線、715、716 ワード線、717、718 プレート線、719、720 センスアンプ、721、722 センスアンプ選択スイッチ、723、724 プリチャージスイッチ、725、726 ビット線選択スイッチ、727 入力端子、728 出力端子。

901 デコード回路、902 ディレイ回路、903 スイッチ、904 1ビットFeRAM回路。

1000 基板、1001 アンテナ、1002 回路、1003 基板、1004 アンテナ、1005 回路、1006 基板、1007 アンテナ、1008 回路、1009 基板、1010 アンテナ、1011 回路、1012 基板、1013 アンテナ、1014 回路、1100 上部基板、1101 アンテナ配線。

1301 デコード回路、1302 ディレイ回路、1303 スイッチ、1304 揮発性メモリ回路。

2000 ICカード、2001 回路部、2010 IDタグ、2011 回路部、2020 商品、2021 保護膜、2022 IDチップ、2030 筐体、2031 IDチップ、2040 荷札、2041 IDチップ、2050 書籍、2051 保護膜、2052 IDチップ、2060 紙幣、2061 IDチップ、2070 靴、2071 保護膜、2072 IDチップ。

2201 抵抗、2202 トランジスタ、2203 トランジスタ、2204 電流供給用抵抗、2205〜2209 トランジスタ、2210 抵抗。

2301 フレキシブル保護層(保護層)、2302 IDチップ、2303 フレキシブル保護層(保護層)、2304 アンテナ、

2501 バッグ、2502 IDチップ。

2601 パスポート、2602 IDチップ、2603 免許証、2604 IDチップ。

2701 パック、2702 ラベル、2703 IDチップ。

2801 ラベル、2802 IDチップ、2803 ビール瓶、2804 ラベル、2805 ライタ装置、2806 ベルトコンベア、2807 IDチップ。

2901 ICカード、2902 IDチップ、2903 レジスタ、2904 リーダ/ライタ、2905 キー。

Claims (14)

- 絶縁基板上に変調回路と、復調回路と、論理回路と、メモリ回路と、アンテナ回路とを有し、

前記変調回路及び前記復調回路は前記アンテナ回路に電気的に接続し、

前記復調回路は前記論理回路に接続し、

前記メモリ回路は前記論理回路の出力信号を記憶する手段を有し、

前記メモリ回路は強誘電体容量素子を有する回路であり、

前記メモリ回路は1回のみの書き込みが可能である制御回路を有することを特徴とする半導体装置。 - 絶縁基板上に変調回路と、復調回路と、論理回路と、メモリ回路と、アンテナ回路とを有し、

前記変調回路および前記復調回路は前記アンテナ回路に電気的に接続し、

前記復調回路は前記論理回路に接続し、

前記メモリ回路は前記論理回路の出力信号を記憶する手段を有し、

前記メモリ回路は強誘電体容量素子を有する回路であり、

前記論理回路は前記メモリ回路に記憶するデータによって、前記メモリ回路の書き込みの可否を制御する手段を有することを特徴とする半導体装置。 - 請求項1又は請求項2において、前記メモリ回路を構成するメモリセルは2つのトランジスタと2つの強誘電体容量素子を有することを特徴とする半導体装置。

- 請求項1又は請求項2において、前記メモリ回路を構成するメモリセルは1つのトランジスタと1つの強誘電体容量素子を有することを特徴とする半導体装置。

- 請求項1乃至請求項4に記載のいずれか一項において、前記変調回路と、前記復調回路と、前記論理回路と、前記メモリ回路とのうち、少なくとも一つは薄膜トランジスタで構成することを特徴とした半導体装置。

- 請求項1乃至請求項5に記載のいずれか一項において、前記アンテナ回路と、前記変調回路と、前記復調回路と、前記論理回路と、前記メモリ回路とは、同一の絶縁基板上に設けられることを特徴とした半導体装置。

- 請求項1乃至請求項6に記載のいずれか一項において、前記変調回路と、前記復調回路と、前記論理回路と、前記メモリ回路とは、同一の絶縁基板上に一体形成され、前記アンテナ回路は別の絶縁基板上に設けられることを特徴とした半導体装置。

- 請求項6又は請求項7において、前記絶縁基板はガラスであることを特徴とする半導体装置。

- 請求項6又は請求項7において、前記絶縁基板はプラスチックであることを特徴とする半導体装置。

- 請求項6又は請求項7において、前記絶縁基板はフィルム状の絶縁体であることを特徴とする半導体装置。

- 請求項1乃至請求項10に記載のいずれか一項において、前記アンテナ回路は、前記変調回路と、前記復調回路と、前記論理回路と、前記メモリ回路とのうち少なくとも一つの上方に設けられることを特徴とした半導体装置。

- 請求項1乃至請求項11のいずれか一項において、前記アンテナ回路に入力する信号は無線信号であることを特徴とした半導体装置。

- 請求項1乃至請求項12のいずれか一項に記載された半導体装置を有する無線チップ、ICカード、ICタグ、トランスポンダ、紙幣、有価証券、パスポート、バッグ、衣類。

- 請求項1乃至請求項12のいずれか一項に記載された半導体装置を有する電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005063588A JP4652087B2 (ja) | 2004-03-11 | 2005-03-08 | 半導体装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004068450 | 2004-03-11 | ||

| JP2005063588A JP4652087B2 (ja) | 2004-03-11 | 2005-03-08 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005293563A true JP2005293563A (ja) | 2005-10-20 |

| JP2005293563A5 JP2005293563A5 (ja) | 2008-03-27 |

| JP4652087B2 JP4652087B2 (ja) | 2011-03-16 |

Family

ID=34975788

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005063588A Expired - Fee Related JP4652087B2 (ja) | 2004-03-11 | 2005-03-08 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7675795B2 (ja) |

| JP (1) | JP4652087B2 (ja) |

| KR (1) | KR101098406B1 (ja) |

| CN (1) | CN1930580B (ja) |

| WO (1) | WO2005088532A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014146370A (ja) * | 2009-09-02 | 2014-08-14 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7699232B2 (en) * | 2004-02-06 | 2010-04-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7663473B2 (en) * | 2004-02-12 | 2010-02-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, IC card, IC tag, RFID, transponder, bills, securities, passport, electronic apparatus, bag, and clothes |

| US20060255159A1 (en) * | 2005-05-11 | 2006-11-16 | Fec Co., Ltd.., And The Government Of Malaysia | Power supply circuit in IC chip for non-contact IC card |

| US7675796B2 (en) | 2005-12-27 | 2010-03-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR100764438B1 (ko) * | 2006-07-18 | 2007-10-05 | 주식회사 하이닉스반도체 | Rfid 장치 |

| US8463332B2 (en) * | 2006-08-31 | 2013-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Wireless communication device |

| KR100909801B1 (ko) * | 2007-07-10 | 2009-07-29 | 주식회사 하이닉스반도체 | Rfid 태그 및 그의 동작 방법 |

| KR100881823B1 (ko) * | 2007-08-31 | 2009-02-03 | 주식회사 하이닉스반도체 | 불휘발성 강유전체 메모리를 포함하는 rfid 장치 |

| US20090088618A1 (en) | 2007-10-01 | 2009-04-02 | Arneson Michael R | System and Method for Manufacturing a Swallowable Sensor Device |

| JP5106031B2 (ja) * | 2007-10-12 | 2012-12-26 | パナソニック株式会社 | 半導体記憶装置及びその製造方法並びに半導体スイッチング装置 |

| JP2009163843A (ja) * | 2008-01-09 | 2009-07-23 | Panasonic Corp | 半導体記憶装置及びその製造方法 |

| KR100983700B1 (ko) * | 2008-04-18 | 2010-09-24 | 주식회사 하이닉스반도체 | Rfid 장치 |

| KR101644811B1 (ko) * | 2008-09-19 | 2016-08-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN102150268B (zh) * | 2008-09-30 | 2013-07-31 | 株式会社半导体能源研究所 | 半导体存储器件 |

| US7933138B2 (en) * | 2009-01-30 | 2011-04-26 | Texas Instruments Incorporated | F-RAM device with current mirror sense amp |

| US9024761B2 (en) * | 2009-03-17 | 2015-05-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | System and method for persistent ID flag for RFID applications |

| JP2010231828A (ja) * | 2009-03-26 | 2010-10-14 | Elpida Memory Inc | 半導体記憶装置 |

| CN102751244B (zh) * | 2011-04-20 | 2014-03-12 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件及其形成方法、射频识别芯片及其形成方法 |

| KR20230043924A (ko) | 2020-08-03 | 2023-03-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 구동 방법 |

| US12437793B2 (en) | 2020-09-22 | 2025-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of semiconductor device |

| WO2022064315A1 (ja) | 2020-09-25 | 2022-03-31 | 株式会社半導体エネルギー研究所 | 半導体装置、及び電子機器 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11297963A (ja) * | 1998-04-10 | 1999-10-29 | Toshiba Corp | 電荷蓄積容量素子及びその製造方法、半導体記憶装置及びこれを用いたidカード |

| JP2000020665A (ja) * | 1998-06-30 | 2000-01-21 | Toshiba Corp | 半導体装置 |

| JP2000035991A (ja) * | 1998-05-11 | 2000-02-02 | Sony Corp | 履歴情報記録装置及びこれを備えた製品 |

| JP2000227956A (ja) * | 1998-12-04 | 2000-08-15 | Dainippon Printing Co Ltd | 携帯可能記憶媒体及びその発行方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1994000921A1 (fr) | 1992-06-25 | 1994-01-06 | Nippondenso Co., Ltd. | Dispositif d'identification d'un objet mobile |

| JP3607032B2 (ja) * | 1996-06-03 | 2005-01-05 | 東芝マイクロエレクトロニクス株式会社 | 不揮発性強誘電体メモリ及びその駆動方法 |

| JP4042182B2 (ja) * | 1997-07-03 | 2008-02-06 | セイコーエプソン株式会社 | Icカードの製造方法及び薄膜集積回路装置の製造方法 |

| JPH1173481A (ja) * | 1997-08-28 | 1999-03-16 | Hitachi Ltd | 非接触型icカード |

| JPH11120797A (ja) * | 1997-10-15 | 1999-04-30 | Toshiba Microelectronics Corp | 強誘電体メモリ及びそのスクリーニング方法 |

| JP3614747B2 (ja) | 2000-03-07 | 2005-01-26 | Necエレクトロニクス株式会社 | 昇圧回路、それを搭載したicカード及びそれを搭載した電子機器 |

| JP2003163331A (ja) | 2001-11-28 | 2003-06-06 | Ricoh Co Ltd | 不揮発性有機半導体記憶素子及びそれを有する非接触情報管理表示装置 |

| JP3940014B2 (ja) * | 2002-03-29 | 2007-07-04 | 富士通株式会社 | 半導体集積回路、無線タグ、および非接触型icカード |

| JP2004056089A (ja) | 2002-05-31 | 2004-02-19 | Sharp Corp | Icカード |

| US7699232B2 (en) | 2004-02-06 | 2010-04-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7663473B2 (en) | 2004-02-12 | 2010-02-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, IC card, IC tag, RFID, transponder, bills, securities, passport, electronic apparatus, bag, and clothes |

-

2005

- 2005-03-08 JP JP2005063588A patent/JP4652087B2/ja not_active Expired - Fee Related

- 2005-03-09 WO PCT/JP2005/004584 patent/WO2005088532A1/en not_active Ceased

- 2005-03-09 US US10/591,275 patent/US7675795B2/en not_active Expired - Fee Related

- 2005-03-09 CN CN2005800076086A patent/CN1930580B/zh not_active Expired - Fee Related

-

2006

- 2006-09-27 KR KR1020067019997A patent/KR101098406B1/ko not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11297963A (ja) * | 1998-04-10 | 1999-10-29 | Toshiba Corp | 電荷蓄積容量素子及びその製造方法、半導体記憶装置及びこれを用いたidカード |

| JP2000035991A (ja) * | 1998-05-11 | 2000-02-02 | Sony Corp | 履歴情報記録装置及びこれを備えた製品 |

| JP2000020665A (ja) * | 1998-06-30 | 2000-01-21 | Toshiba Corp | 半導体装置 |

| JP2000227956A (ja) * | 1998-12-04 | 2000-08-15 | Dainippon Printing Co Ltd | 携帯可能記憶媒体及びその発行方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014146370A (ja) * | 2009-09-02 | 2014-08-14 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7675795B2 (en) | 2010-03-09 |

| CN1930580B (zh) | 2011-01-26 |

| KR20070008607A (ko) | 2007-01-17 |

| KR101098406B1 (ko) | 2011-12-23 |

| CN1930580A (zh) | 2007-03-14 |

| WO2005088532A1 (en) | 2005-09-22 |

| JP4652087B2 (ja) | 2011-03-16 |

| US20070171693A1 (en) | 2007-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4652087B2 (ja) | 半導体装置 | |

| US8430326B2 (en) | Semiconductor device | |

| US7909260B2 (en) | Semiconductor device | |

| JP4776941B2 (ja) | 半導体装置の製造方法、icカード、icタグ、rfid、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ及び衣類 | |

| KR101146599B1 (ko) | 반도체 장치 및 그를 갖는 제품 | |

| JP4718850B2 (ja) | 半導体装置、icカード、icタグ、rfid、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ及び衣類 | |

| JP4836466B2 (ja) | 半導体装置 | |

| JP2005252232A (ja) | 有価証券並びにチップ搭載物、及びそれらの作製方法 | |

| JP4836523B2 (ja) | 半導体装置、icカード、icタグ、rfid、トランスポンダ、紙幣、有価証券類、パスポート、電子機器、バッグ及び衣類 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080206 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101207 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101215 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4652087 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131224 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131224 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |