JP2005293300A - セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 - Google Patents

セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 Download PDFInfo

- Publication number

- JP2005293300A JP2005293300A JP2004108286A JP2004108286A JP2005293300A JP 2005293300 A JP2005293300 A JP 2005293300A JP 2004108286 A JP2004108286 A JP 2004108286A JP 2004108286 A JP2004108286 A JP 2004108286A JP 2005293300 A JP2005293300 A JP 2005293300A

- Authority

- JP

- Japan

- Prior art keywords

- cache

- way

- block

- address

- information

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

- G06F12/121—Replacement control using replacement algorithms

- G06F12/123—Replacement control using replacement algorithms with age lists, e.g. queue, most recently used [MRU] list or least recently used [LRU] list

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Abstract

【解決手段】 キャッシュシステムは、i(2)組のm(2)ウェイn(2)セットのキャッシュアレイ330、340と、キャッシュアドレス300とキャッシュ管理情報310とに基づいて、i(2)組のキャッシュアレイ330、340の全部又は1つを選択し、キャッシュアドレスに従って、選択したキャッシュメモリのうちの第jのセットを選択するセットアドレスデコーダ320と、キャッシュ管理情報310に基づいてウェイを選択し、選択されたセットの選択したウェイのキャッシュブロックのブロックアドレスとキャッシュブロックのブロックアドレスとを比較し、キャッシュヒットとミスとの別を判定すると共に置き換えブロックを選択する比較回路350と、より構成される。

【選択図】 図3

Description

・ 領域を分割した場合、キャッシュブロックをそのまま利用できないのでキャッシュミスが発生する(課題1)。

キャッシュウェイで分割するタイプ

・ ウェイ数が不足して処理単位内での競合ミスが発生することがある(課題2)。

・ 処理単位数を増減して領域を変更する場合、処理単位間の競合ミスが発生する(課題3)。

キャッシュブロック単位で分割するタイプ

・ 処理単位数の増減に関わらず、処理単位間の競合ミスが発生する(課題4)。

また、ウェイ数の指定を可能とし、タスク間のキャッシュミスを減らす技術が特許文献2に開示されている。

また、特許文献1と2とに開示されたウェイ選択・比較方法は、キャッシュ要求時のウェイの最大値を指定する手法であり、最大構成より少ないウェイ数の構成にした時に使用されないキャッシュ容量が発生し、キャッシュの使用効率が低い。

また、この発明は、セット数やウェイ数を変更しても、利用可能なキャッシュ容量が減少しないセットアソシアティブキャッシュシステムなどを提供することを目的とする。

i組のmウェイnセットのキャッシュメモリと、

キャッシュアドレスとキャッシュ管理情報に基づいて、前記i組のキャッシュメモリの全部又は1つを選択し、キャッシュアドレスに従って、選択したキャッシュメモリのうちの第jのセットを選択するセット選択手段と、

キャッシュ管理情報に基づいてウェイを選択するウェイ選択手段と、

前記セット選択手段により選択されたセットの前記ウェイ選択手段で選択したウェイのキャッシュブロックのブロックアドレスとキャッシュブロックのブロックアドレスとを比較し、キャッシュヒットとミスとの別を判定する判定手段と、

前記判定手段の判定結果に基づいて、置き換えブロックを選択する置き換え選択手段と、

を具備することを特徴とする。

i組のmウェイnセットのキャッシュメモリについて、

キャッシュアドレスとキャッシュ管理情報に基づいて、前記i組のキャッシュメモリの全部又は1つを選択し、キャッシュアドレスに従って、選択したキャッシュメモリのうちの第jのセットを選択し、

キャッシュ管理情報に基づいてウェイを選択し、

選択したセットの選択したウェイのキャッシュブロックのブロックアドレスと、キャッシュアドレス中の要求ブロックアドレスとを比較し、キャッシュヒットとミスとを判定し、

判定結果に基づいて、置き換えブロックを選択する、

ことを特徴とする。

以下、この発明の実施の形態に係るキャッシュシステムを説明する。このキャッシュシステムは、処理単位(システム、プロセス、スレッド)に応じてキャッシュ構成を変更できる可変mウェイnセットアソシアティブキャッシュである。

また、プロセッサチップ200は論理的にシステム数を複数(本実施の形態では2)に分割できる。

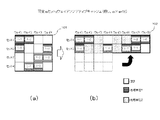

この2−4セット4−2ウェイアソシアティブキャッシュ240は、キャッシュコントローラ230からの指示により、2セット4ウェイアソシアティブ構成と4セット2ウェイアソシアティブ構成とで切り替えることができるキャッシュである。

さらに、あるスレッドがメモリを共有している場合には、そのスレッドの番号がメモリ共有情報313に設定される。

2−4セット4−2ウェイアソシアティブキャッシュの動作の説明をする。図5はキャッシュ要求でセットアドレス302とキャッシュ管理情報310とからセットとウェイとの領域を決定するセットアドレスデコーダ320とウェイ選択回路410の動作結果とを表している。アクセス1から2は、4セット2ウェイアソシアティブキャッシュ構成で、アクセス3から6は、2セット4ウェイアソシアティブキャッシュ構成となる。

アクセス5の場合、スレッド3とスレッド4とがメモリ共有されている。そのことを示す情報がメモリ共有情報310にセットされている。メモリ共有情報310は、ヒット判定回路440に入力され、結局、ウェイ1とウェイ2とがヒット判定対象キャッシュブロックとなる。

ウェイ数を増やせるので、処理単位内及び処理単位間での競合ミスを防ぐ(効果1)。

セット数とウェイ数を変更してもキャッシュアドレスが指すキャッシュブロックの位置が変わらないのでキャッシュ区分領域変更でのキャッシュミスを低減できる(効果2)。

各ウェイの領域を変更する時にLRUビットを参照することによって区分領域を決定するので処理単位間での競合ミスを低減することができる(効果3)。

例えば、図1の構成では、4ブロック(2セット×2ウェイ)のキャッシュアレイを2セット(330と340)用意し、セットの選択とウェイの選択とを制御することにより、4セット×2ウェイ(セット1、セット2、セット3、セット4、各セット1と2とについてはウェイ1とウェイ2、セット3と4とについては、ウェイ3と4)と、2セット×4ウェイ(セット1とセット3とからなる第1のセット、セット2とセット4とからなる第2のセット;第1のセットと第2のセットはそれぞれウェイ1〜ウェイ4)とを切り替えたが、構成は任意である。

Claims (9)

- i組のmウェイnセットのキャッシュメモリと、

キャッシュアドレスとキャッシュ管理情報に基づいて、前記i組のキャッシュメモリの全部又は1つを選択し、キャッシュアドレスに従って、選択したキャッシュメモリのうちの第jのセットを選択するセット選択手段と、

キャッシュ管理情報に基づいてウェイを選択するウェイ選択手段と、

前記セット選択手段により選択されたセットの前記ウェイ選択手段で選択したウェイのキャッシュブロックのブロックアドレスとキャッシュブロックのブロックアドレスとを比較し、キャッシュヒットとミスとの別を判定する判定手段と、

前記判定手段の判定結果に基づいて、置き換えブロックを選択する置き換え選択手段と、

を具備することを特徴とするセットアソシアティブキャッシュシステム。 - 前記キャッシュアドレスは、ブロックアドレスとセットアドレスとを含み、

前記キャッシュ管理情報は、処理単位に関する情報を含む、

ことを特徴とする請求項1に記載のセットアソシアティブキャッシュシステム。 - 前記処理単位に関する情報は、システムの状態を示す情報、プロセスの状態を示す情報、スレッドの状態を示す情報、メモリの共有の情報を含む、

ことを特徴とする請求項2に記載のセットアソシアティブキャッシュシステム。 - 前記ウェイ選択手段は、前記キャッシュ管理情報と共にキャッシュブロックのLRU情報に基づいて、ウェイを選択し、

前記置き換え選択手段は、前記キャッシュ管理情報と共にキャッシュブロックのLRU情報に基づいて、置き換えブロックを選択する、

ことを特徴とする請求項1、2又は3のいずれか1項に記載のセットアソシアティブキャッシュシステム。 - 前記ウェイ選択手段は、前記キャッシュ管理情報と共にキャッシュブロックのLRU情報とさらに各ウェイへの処理の割り当ての情報に基づいて、ウェイを選択し、

前記置き換え選択手段は、前記キャッシュ管理情報と共にキャッシュブロックのLRU情報とさらに各ウェイへの処理の割り当ての情報に基づいて、置き換えブロックを選択する、

ことを特徴とする請求項1、2又は3のいずれか1項に記載のセットアソシアティブキャッシュシステム。 - i・nセット、mウェイセットアソシアティブキャッシュと、nセット、i・mウェイセットアソシアティブキャッシュと、として機能することを特徴とする請求項1乃至5のいずれか1項に記載のセットアソシアティブキャッシュシステム。

- セット数とウェイ数とを変更しても、同一のキャッシュアドレスに対応するキャッシュブロックの位置が変化しない、ことを特徴とする請求項1乃至6のいずれか1項に記載のセットアソシアティブキャッシュシステム。

- セット数とウェイ数とを変更しても、利用可能なキャッシュ容量が変化しない、ことを特徴とする請求項1乃至7のいずれか1項に記載のセットアソシアティブキャッシュシステム。

- i組のmウェイnセットのキャッシュメモリについて、

キャッシュアドレスとキャッシュ管理情報に基づいて、前記i組のキャッシュメモリの全部又は1つを選択し、キャッシュアドレスに従って、選択したキャッシュメモリのうちの第jのセットを選択し、

キャッシュ管理情報に基づいてウェイを選択し、

選択したセットの選択したウェイのキャッシュブロックのブロックアドレスと、キャッシュアドレス中の要求ブロックアドレスとを比較し、キャッシュヒットとミスとを判定し、

判定結果に基づいて、置き換えブロックを選択する、

ことを特徴とするセットアソシアティブキャッシュメモリの制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108286A JP4036206B2 (ja) | 2004-03-31 | 2004-03-31 | セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 |

| US11/092,679 US7330935B2 (en) | 2004-03-31 | 2005-03-30 | Set associative cache system and control method for cache memories |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108286A JP4036206B2 (ja) | 2004-03-31 | 2004-03-31 | セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293300A true JP2005293300A (ja) | 2005-10-20 |

| JP4036206B2 JP4036206B2 (ja) | 2008-01-23 |

Family

ID=35055722

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108286A Expired - Fee Related JP4036206B2 (ja) | 2004-03-31 | 2004-03-31 | セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7330935B2 (ja) |

| JP (1) | JP4036206B2 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101056460B1 (ko) | 2009-06-05 | 2011-08-11 | 세종대학교산학협력단 | 캐쉬 제어기 및 캐쉬 블록 교체 방법 |

| JP2011164975A (ja) * | 2010-02-10 | 2011-08-25 | Fujitsu Ltd | 情報処理装置 |

| US8312221B2 (en) | 2008-07-29 | 2012-11-13 | Kabushiki Kaisha Toshiba | Cache system, cache system control method, and information processing apparatus |

| JP2017503299A (ja) * | 2014-12-14 | 2017-01-26 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | モードに応じてセットの1つ又は複数を選択的に選択するように動的に構成可能であるマルチモード・セット・アソシエイティブ・キャッシュ・メモリ |

| JP2017503298A (ja) * | 2014-12-14 | 2017-01-26 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | アドレス・タグ・ビットに基づく動的キャッシュ置換ウェイ選択 |

| JP2017507442A (ja) * | 2014-12-14 | 2017-03-16 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | モードに応じてウェイの全部又はサブセットに選択的に割り当てるように動的に構成可能であるマルチモード・セット・アソシエイティブ・キャッシュ・メモリ |

| JP2018133038A (ja) * | 2017-02-17 | 2018-08-23 | Necプラットフォームズ株式会社 | 情報処理装置、制御装置、制御方法及びプログラム |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4506292B2 (ja) * | 2004-06-10 | 2010-07-21 | 株式会社日立製作所 | キャッシュ制御方法およびデータ処理システム並びにその処理プログラム |

| US7673101B2 (en) * | 2005-05-16 | 2010-03-02 | Texas Instruments Incorporated | Re-assigning cache line ways |

| US8244980B2 (en) * | 2006-06-21 | 2012-08-14 | Intel Corporation | Shared cache performance |

| US7861041B2 (en) * | 2007-09-04 | 2010-12-28 | Advanced Micro Devices, Inc. | Second chance replacement mechanism for a highly associative cache memory of a processor |

| US8392658B2 (en) * | 2009-07-10 | 2013-03-05 | Apple Inc. | Cache implementing multiple replacement policies |

| KR101862785B1 (ko) * | 2011-10-17 | 2018-07-06 | 삼성전자주식회사 | 타일 기반 렌더링을 위한 캐쉬 메모리 시스템 및 캐슁 방법 |

| US9043554B2 (en) | 2012-12-21 | 2015-05-26 | Apple Inc. | Cache policies for uncacheable memory requests |

| EP3066572B1 (en) * | 2014-12-14 | 2020-02-19 | VIA Alliance Semiconductor Co., Ltd. | Cache memory budgeted by chunks based on memory access type |

| WO2016097807A1 (en) * | 2014-12-14 | 2016-06-23 | Via Alliance Semiconductor Co., Ltd. | Cache replacement policy that considers memory access type |

| EP3066571B1 (en) | 2014-12-14 | 2018-06-13 | VIA Alliance Semiconductor Co., Ltd. | Cache memory budgeted by ways on memory access type |

| WO2016097813A1 (en) * | 2014-12-14 | 2016-06-23 | Via Alliance Semiconductor Co., Ltd. | Set associative cache memory with heterogeneous replacement policy |

| WO2016097806A1 (en) * | 2014-12-14 | 2016-06-23 | Via Alliance Semiconductor Co., Ltd. | Fully associative cache memory budgeted by memory access type |

| US10073786B2 (en) | 2015-05-28 | 2018-09-11 | Micron Technology, Inc. | Apparatuses and methods for compute enabled cache |

| GB2547189A (en) * | 2016-02-03 | 2017-08-16 | Swarm64 As | Cache and method |

| US12346265B2 (en) | 2019-12-16 | 2025-07-01 | Advanced Micro Devices, Inc. | Cache line re-reference interval prediction using physical page address |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0520193A (ja) | 1991-07-15 | 1993-01-29 | Oki Electric Ind Co Ltd | キヤツシユ・メモリ装置 |

| JPH0962582A (ja) | 1995-08-21 | 1997-03-07 | Toshiba Corp | 疑似セットアソシアティブ方式キャッシュメモリ装置 |

| KR100373849B1 (ko) * | 2000-03-13 | 2003-02-26 | 삼성전자주식회사 | 어소시어티브 캐시 메모리 |

| JP3900025B2 (ja) | 2002-06-24 | 2007-04-04 | 日本電気株式会社 | 共有キャッシュメモリのヒット判定制御方法及び共有キャッシュメモリのヒット判定制御方式 |

| JP3931757B2 (ja) | 2002-07-26 | 2007-06-20 | 日本電気株式会社 | 共有キャッシュメモリ障害処理方式 |

-

2004

- 2004-03-31 JP JP2004108286A patent/JP4036206B2/ja not_active Expired - Fee Related

-

2005

- 2005-03-30 US US11/092,679 patent/US7330935B2/en active Active

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8312221B2 (en) | 2008-07-29 | 2012-11-13 | Kabushiki Kaisha Toshiba | Cache system, cache system control method, and information processing apparatus |

| KR101056460B1 (ko) | 2009-06-05 | 2011-08-11 | 세종대학교산학협력단 | 캐쉬 제어기 및 캐쉬 블록 교체 방법 |

| JP2011164975A (ja) * | 2010-02-10 | 2011-08-25 | Fujitsu Ltd | 情報処理装置 |

| JP2017503299A (ja) * | 2014-12-14 | 2017-01-26 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | モードに応じてセットの1つ又は複数を選択的に選択するように動的に構成可能であるマルチモード・セット・アソシエイティブ・キャッシュ・メモリ |

| JP2017503298A (ja) * | 2014-12-14 | 2017-01-26 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | アドレス・タグ・ビットに基づく動的キャッシュ置換ウェイ選択 |

| JP2017507442A (ja) * | 2014-12-14 | 2017-03-16 | ヴィア アライアンス セミコンダクター カンパニー リミテッド | モードに応じてウェイの全部又はサブセットに選択的に割り当てるように動的に構成可能であるマルチモード・セット・アソシエイティブ・キャッシュ・メモリ |

| US9798668B2 (en) | 2014-12-14 | 2017-10-24 | Via Alliance Semiconductor Co., Ltd. | Multi-mode set associative cache memory dynamically configurable to selectively select one or a plurality of its sets depending upon the mode |

| US10698827B2 (en) | 2014-12-14 | 2020-06-30 | Via Alliance Semiconductor Co., Ltd. | Dynamic cache replacement way selection based on address tag bits |

| US10719434B2 (en) | 2014-12-14 | 2020-07-21 | Via Alliance Semiconductors Co., Ltd. | Multi-mode set associative cache memory dynamically configurable to selectively allocate into all or a subset of its ways depending on the mode |

| JP2018133038A (ja) * | 2017-02-17 | 2018-08-23 | Necプラットフォームズ株式会社 | 情報処理装置、制御装置、制御方法及びプログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050223173A1 (en) | 2005-10-06 |

| JP4036206B2 (ja) | 2008-01-23 |

| US7330935B2 (en) | 2008-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4036206B2 (ja) | セットアソシアティブキャッシュシステム及びキャッシュメモリの制御方法 | |

| US8250332B2 (en) | Partitioned replacement for cache memory | |

| JP4209906B2 (ja) | 低消費電力メモリ管理方法及びその方法を用いた計算機 | |

| US6725336B2 (en) | Dynamically allocated cache memory for a multi-processor unit | |

| JP4006436B2 (ja) | 種々のキャッシュ・レベルにおける連想セットの重畳一致グループを有するマルチレベル・キャッシュ | |

| US6877067B2 (en) | Shared cache memory replacement control method and apparatus | |

| US6578065B1 (en) | Multi-threaded processing system and method for scheduling the execution of threads based on data received from a cache memory | |

| KR101639943B1 (ko) | 범용 그래픽 프로세서의 공유 메모리를 캐시로 동작시키기 위한 공유 메모리 제어 방법 및 이를 이용한 범용 그래픽 프로세서 | |

| JP2011129101A (ja) | キャッシュメモリにおけるキャッシュラインの置き換え | |

| US5860101A (en) | Scalable symmetric multiprocessor data-processing system with data allocation among private caches and segments of system memory | |

| JP2009520295A (ja) | 共有メモリバンクを有するマルチプロセッサ回路 | |

| CN102346682A (zh) | 信息处理装置及信息处理方法 | |

| JP5336423B2 (ja) | 計算機システム | |

| JP4888839B2 (ja) | キャッシュメモリを備えるベクトル計算機システム、及びその動作方法 | |

| US6038642A (en) | Method and system for assigning cache memory utilization within a symmetric multiprocessor data-processing system | |

| JP2009528612A (ja) | データ処理システム並びにデータ及び/又は命令のプリフェッチ方法 | |

| US5893163A (en) | Method and system for allocating data among cache memories within a symmetric multiprocessor data-processing system | |

| CN119487486A (zh) | 具有命令重新排序的存储器控制器 | |

| US6760743B1 (en) | Instruction memory system for multi-processor environment and disjoint tasks | |

| JP2009015509A (ja) | キャッシュメモリ装置 | |

| JP2001282617A (ja) | 共有されたキャッシュを動的に区分するための方法及びシステム | |

| KR20190013049A (ko) | 모놀리식 3차원 집적 기술 기반 캐시 메모리 및 이의 제어 방법 | |

| JPH07129464A (ja) | 情報処理装置 | |

| JP2009093559A (ja) | プロセッサ、情報処理装置、プロセッサのキャッシュ制御方法 | |

| JP7754203B2 (ja) | メモリアクセス方法およびメモリアクセス制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070709 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20070711 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070724 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070921 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071009 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071022 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4036206 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101109 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111109 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111109 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121109 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121109 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131109 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |