最も一般的なノーマリホワイトモードの液晶パネルにおいては、画素電極とドレインバスラインやゲートバスラインとの隙間から漏れ光が生じてコントラストが低下することを防止するために、ブラックマトリクスと呼ばれる遮光膜を対向基板に設けている。しかし、このような構造の液晶パネルにおいては、TFTが設けられたTFT基板と対向基板との位置合わせマージンを考慮する必要があり、ブラックマトリクスの遮光膜の面積が増えて開口率が低下してしまう。開口率は液晶パネルの表示品質を左右する重要なパラメータであり、明るい表示を実現するために開口率を向上する必要がある。

また、液晶の容量値である液晶容量も、液晶パネルの表示品質を左右する重要なパラメータであり、表示品質を向上するためには液晶容量を大きくする必要がある。

液晶容量を大きくして、しかも、開口率を向上することが、液晶パネルにおける重要な技術的課題となっている。

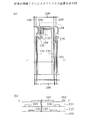

従来の薄膜トランジスタマトリクス装置を図38に示す。図38(a)はパターンレイアウトを示し、図38(b)はA−A′線断面を示す。

薄膜トランジスタマトリクス装置のパターンレイアウトを図38(a)を用いて説明する。画素電極102は、透明絶縁基板100上にマトリクス状に配置されている。各画素電極102には薄膜トランジスタ104が設けられている。薄膜トランジスタ104のゲートを共通接続するため、図38(a)の横方向に延びるゲートバスライン106が設けられている。薄膜トランジスタ104のドレインを共通接続するため、図38(a)の縦方向に延びるドレインバスライン108が設けられている。

薄膜トランジスタの構造の詳細について図38(b)を用いて説明する。透明絶縁基板100上にはゲート電極109が形成され、ゲート電極109上にゲート絶縁膜110が形成されている。ゲート絶縁膜110上には、薄膜トランジスタのチャネル層となるアモルファスシリコン層112が形成されている。アモルファスシリコン層112上には、中央のチャネル領域を保護するためにチャネル保護膜114が設けられている。アモルファスシリコン層112上であって、チャネル保護膜114の両側には、n+型アモルファスシリコン層116、118が形成され、n+型アモルファスシリコン層116上にドレイン電極120が形成され、n+型アモルファスシリコン層118上にソース電極122が形成されている。薄膜トランジスタ104全体は保護膜124により覆われている。保護膜124上には画素電極102が形成されている。画素電極102とソース電極122とは、保護膜124に形成されたコンタクトホール126を介して接続されている。

薄膜トランジスタマトリクス装置の等価回路を図39に示す。ゲートバスライン106とドレインバスライン108の交差位置に薄膜トランジスタ104が設けられている。薄膜トランジスタ104のソース電極122には液晶による容量である液晶容量Clcが接続されている。更に、画素電極102とゲートバスライン106間には寄生容量Cgsが存在する。この寄生容量Cgsは、薄膜トランジスタ104のゲート電極109とソース電極122が重なる程度に応じた容量値と、画素電極102とゲートバスライン106が隣接することによって生じる容量値との合計になる。

次に、薄膜トランジスタマトリクス装置の動作を図40を用いて説明する。

ゲートバスライン106に正パルスを印加すると、薄膜トランジスタ104がオンして、ドレイン電極120に印加されているドレイン電圧VDが画素電極102に印加される。このときのドレイン電圧VDを変化することにより、階調も含めた所望の表示を行うことができる。

しかしながら、寄生容量Cgsが存在すると画素電極102に所望のドレイン電圧VDを書き込むことができなくなる。すなわち、所望のドレイン電圧VDを印加し、ゲート電圧VGをオフ時の電圧VGoffからオン時の電圧VGonに変化すると、薄膜トランジスタ104はオンし、画素電極102にドレイン電圧VDが印加される。しかしながら、ゲート電圧VGがオン時の電圧VGonからオフ時の電圧VGoffまでΔVGだけ変化すると、寄生容量Cgsによる容量結合により、画素電極102の電位も次式に示すようにΔVだけ下がってしまう。

ΔV=Cgs/(Cgs+Clc)・ΔVG (1)

したがって、画素電極102の電位にΔVの直流雑音成分が重畳されることになり、液晶表示のちらつきであるフリッカや、コントラストの低下や、液晶・配向膜の分解等の信頼性低下や、液晶表示の焼き付き等の問題が発生する。このため、対向電極の電位であるコモン電位VcをΔVだけ下げるようにして、液晶に所望の電圧が印加するようにしている。

しかしながら、液晶容量Clcは液晶のオンオフ状態で変化する。液晶に電圧が印加されているオン状態の液晶容量Clc(on)の方が、液晶に電圧が印加されていないオフ状態の液晶容量Clc(off)よりも大きい。このため、寄生容量Cgsによる容量結合により低下する電圧ΔVが表示状態により変化することになる。

したがって、コモン電位Vcを下げるようにしても、表示状態によっては、液晶表示の焼き付き等の前述した問題が発生する。

このような問題を解決するために、液晶容量と並列に補助容量を設けた薄膜トランジスタマトリクス装置が提案されている。

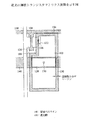

このような薄膜トランジスタマトリクス装置を図41に示す。図41(a)はパターンレイアウトを示し、図41(b)はA−A′線断面を示し、図41(c)はB−B′線断面を示す。

薄膜トランジスタマトリクス装置のパターンレイアウトを図41(a)を用いて説明する。画素電極102は、透明絶縁基板100上にマトリクス状に配置されている。各画素電極102には薄膜トランジスタ104が設けられている。薄膜トランジスタ104のゲートを共通接続するゲートバスライン106、薄膜トランジスタ104のドレインを共通接続するドレインバスライン108が設けられている。

画素電極102の下部には、補助容量Csを形成するための中間電極128が形成されている。ゲートバスライン106は、中間電極128下方に形成され、ドレインバスライン108に沿った画素電極102間の隙間に対応して形成されている。

薄膜トランジスタマトリクス装置の構造を図41(b)、図41(c)を用いて説明する。

補助容量Csの構造は、図41(c)に示すように、透明絶縁基板100上にゲートバスライン106が形成され、ゲートバスライン106上にゲート絶縁膜110を介して中間電極128が形成されている。中間電極128は保護膜124により覆われている。保護膜124上には画素電極102が形成されている。画素電極102と中間電極128とは、保護膜124に形成されたコンタクトホール130を介して接続されている。

薄膜トランジスタマトリクス装置の等価回路を図42に示し、薄膜トランジスタマトリクス装置の動作波形を図43を示す。

ゲートバスライン106とドレインバスライン108の交差位置に薄膜トランジスタ104が設けられている。薄膜トランジスタ104のソース電極122には液晶による容量である液晶容量Clcが接続されている。更に、画素電極102と隣接するゲートバスライン106との間には補助容量Csが存在する。この寄生容量Csは、ゲートバスライン106と中間電極128が重なる程度に応じた値となる。

薄膜トランジスタマトリクス装置における画素電極102の直流電圧変動ΔVは次式のようになる。

ΔV=Cgs/(Cgs+Clc+Cs)・ΔVG (2)

したがって、(Clc+Cs)>>Cgsとなるように、補助容量の容量値Csをできるだけ大きくすれば、図43に示すように、電圧変動ΔVを小さくすることができ、表示品質を大幅に改善することができる。なお、図43に示すように、補助容量Csが接続されたゲートバスライン106の書き込みパルスにより画素電極102の電圧は変動するが、非常に短期間であるので表示品質に影響を与えることはない。

このように、表示品質を向上させるためには、補助容量を設けて見かけ上の液晶容量を大きくすることが非常に有効である。このことを実現するために、ゲートバスラインの一部を絶縁膜を挟んで画素電極の一部と重なるように配置して補助容量を形成する、Cs−on−Gate構造と呼ばれる構造が提案されている。なお、前述した図41の構造もこのCs−on−Gate構造に該当している。

Cs−on−Gate構造の一例を図44に示す。図44(a)はパターンレイアウトを示し、図44(b)はC−C′線断面を示す。

この薄膜トランジスタマトリクス装置は、補助容量を形成するためのパターンが、漏れ光を遮光するブラックマトリクスをも兼ねるようにして、開口率の向上も図るものである。

画素電極102は、透明絶縁基板100上にマトリクス状に配置されている。各画素電極102には薄膜トランジスタ104が設けられている。薄膜トランジスタ104のゲートを共通接続するゲートバスライン106、薄膜トランジスタ104のドレインを共通接続するドレインバスライン108が設けられている。 画素電極102の左右両側に隣接する画素電極との間の隙間を覆う補助パターン132が設けられている。この補助パターン132は、画素電極102と縁部で重なっている。補助パターン132とゲートバスライン106とは連続して一体のパターンとなっている。

図44(b)に示すように、透明絶縁基板100上にはゲートバスライン106に連続する補助パターン132が形成され、補助パターン132上にゲート絶縁膜110が形成されている。ゲート絶縁膜110上には、ドレインバスライン108が形成され、ドレインバスライン108上には、保護膜124が形成されている。保護膜124上に画素電極102が形成されている。

画素電極102と補助パターン132は、ゲート絶縁膜110と保護膜124を挟んで、一部が互いに重なっており、これにより、画素電極102とゲートバスライン106間に補助容量Csが形成される。

なお、補助パターン132は漏れ光を遮光する遮光膜としても機能するので、対向基板に形成されるブラックマトリクス134のパターンは、図44(a)に示すように、画素電極102の上部の薄膜トランジスタ104を含む領域と、ゲートバスライン106と画素電極102との間の領域となっている。

しかしながら、図44(a)に示すCs−on−Gate構造の薄膜トランジスタマトリクス装置では、画素電極102の三辺しか囲んでいないので、残り一辺はブラックマトリクスが必要となり、その分開口率が低下する。

このため、画素電極102を取り囲むように補助パターン132を形成したCs−on−Gate構造がある。そのようなCs−on−Gate構造を図45に示す。図45(a)はパターンレイアウトを示し、図45(b)はC−C′線断面を示す。

この薄膜トランジスタマトリクス装置では、補助パターン132を更に画素電極102の上部にも延ばして、画素電極102を取り囲むリング状のパターンとしたものである。対向基板に形成されるブラックマトリクス134のパターンは、薄膜トランジスタ104だけを遮蔽できればよく、位置合わせマージンを非常に小さくすることができる。

しかしながら、図45に示す薄膜トランジスタマトリクス装置では、隣接するゲートバスライン同士がかなり長い距離にわたって近接したパターンとなるため、精度よく製造することが困難であり、製造上の歩留まりが悪化するという問題があった。

一方、寄生容量に関しては、画素電極とゲートバスライン間の寄生容量だけでなく、画素電極間の寄生容量も問題となる。画素電極間の寄生容量が大きい場合には、ある行の画素電極にデータを書き込んでも、隣接する行の画素電極にデータを書き込む際に、容量結合により画素電極の電位が変化してしまうという問題があった。

このため、たとえパターン上の余裕があったとしても、画素電極同士を例えば5μmより近づけることはできず、一定程度以上に開口率を向上することができなかった。

また、補助容量を設けて見かけ上の液晶容量を大きくする構造として、上述したCs−on−Gate構造の他に、ゲートバスラインとは独立に補助容量Cs用の容量バスラインを設け、この容量バスライン上に補助容量Csを設けた、いわゆる独立Cs方式の構造が提案されている。

図46に、独立Cs方式の構造を採用した従来の薄膜トランジスタマトリクス装置を示す。

画素電極102は透明基板上にマトリクス状に配置されている。各画素電極102には薄膜トランジスタ104が設けられている。薄膜トランジスタ104には、ゲート電極109、ドレイン電極120、ソース電極122が設けられている。薄膜トランジスタ104のゲート電極109は、図46の横方向に延びるゲートバスライン106により共通接続されている。薄膜トランジスタ104のドレイン電極120は、図46の縦方向に延びるドレインバスライン108により共通接続されている。薄膜トランジスタ104のソース電極122はコンタクトホール126を介して画素電極102に接続されている。

補助容量Csを形成するために、画素電極102の中央に中間電極128が設けられている。中間電極128はコンタクトホール130を介して画素電極102に接続されている。中間電極128下には、図46の横方向に延びる容量バスライン140が設けられている。中間電極128と容量バスライン140間に補助容量Csが形成される。

薄膜トランジスタマトリクス装置における画素電極102とゲートバスライン106、ドレインバスライン108の間の隙間を遮光するために、TFT基板に対向する対向基板側にブラックマトリクスと呼ばれる遮光膜150を形成している。

しかしながら、独立Cs方式の薄膜トランジスタマトリクス装置の場合にも、ブラックマトリクスにより隙間を遮光する方法では、TFT基板と対向基板との貼り合わせ誤差を考慮して、図46に示すように、貼り合わせ精度に応じたマージンを考慮する必要がある。このため、一定程度以上に開口率を向上することが難しかった。

したがって、開口率を向上させるためには、対向基板のブラックマトリクスを用いることなく、TFT基板側のゲートバスラインや容量バスライン等を利用して隙間を遮光することが考えられる。薄膜トランジスタマトリクス基板側のパターンにより遮光する場合には、貼り合わせ精度に比べて高い位置合せ精度が確保できるため、開口率を向上することができる。

図47に、ゲートバスラインを用いて隙間を遮光する従来の薄膜トランジスタマトリクス装置の一例を示す。図47(a)はパターンレイアウトを示し、図47(b)はI−I′線断面を示す。

図47の薄膜トランジスタマトリクス装置では、ゲートバスライン106の幅を太くすることにより、画素電極102とゲートバスライン106間の隙間を遮光するようにしている。このように、ゲートバスライン106や、容量バスライン140等のTFT基板側のパターンを用いて、隙間を遮光するようにすれば、大きな位置合せマージンを考慮する必要がないので、開口率を向上することができる。

しかしながら、図47(b)に示すように、ゲートバスライン106を用いて隙間を遮光するようにすると、画素電極102とゲートバスライン106の間に新たな容量Cgsが発生し、画素電極102の直流電圧変動ΔV、すなわち、フィールドスルー電圧ΔVは、前述した式(1)又は(2)で与えられる。これら式から明らかなように、容量Cgsが増大すると、フィールドスルー電圧ΔVが増大し、白表示時と黒表示時での実効画素電圧の差が大きくなり、表示品質を劣化を招くことになる。

また、ゲートバスラインを用いて画素電極の隙間を遮光するようにすると、ゲートバスライン近傍の液晶の配向状態に歪みが発生し、その歪みにより漏れ光が生じるという問題がある。

図48及び図49に、ゲートバスラインを用いて隙間を遮光する従来の薄膜トランジスタマトリクス装置の一例を示す。図48はパターンレイアウトを示し、図49はJ−J′線断面を示す。

この薄膜トランジスタマトリクス装置では、図48に示すように、ゲートバスライン106を2つの画素電極102に重なるような位置に設け、画素電極102間の隙間を遮光するようにしている。しかしながら、この遮光部分では、図49に示すように、画素電極102と共通電極144間の液晶142の配向状態に歪みを生ずる。すなわち、画素電極102とゲートバスライン106の間には、その電位差に応じて横方向電界が印加し、これにより液晶142が配向する。このため、横方向電界による配向方向が、液晶142の配向方向と反対の場合には、図49に示すように、その画素電極102の端部近傍の液晶142に、配向方向が反転する反転境界143があらわれ、この反転境界143から光が漏れるという問題がある。

[第1の実施形態]

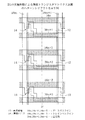

本発明の第1の実施形態による薄膜トランジスタマトリクス装置を図1乃至図3を用いて説明する。図1はパターンレイアウトを示し、図2はD−D′線断面を示し、図3は等価回路を示す。

透明絶縁基板10上に、図1の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられ、図2の縦方向に延びるドレインバスライン18m、18m+1、…が平行に複数本設けられている。

薄膜トランジスタ14は、ゲートバスライン16n、16n+1、16n+2、…とドレインバスライン18m、18m+1、…が交差する位置に設けられている。薄膜トランジスタ14のゲート電極はゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極はドレインバスライン18m、18m+1、…により共通接続されている。薄膜トランジスタ14のソース電極には画素電極12が接続されている。

本実施形態における各画素電極12は、ゲートバスライン16n、16n+1、16n+2、…にまたがって形成されている。例えば、ゲートバスライン16nに薄膜トランジスタ14を介して接続された画素電極12は、上端がゲートバスライン16nとゲートバスライン16n+1の間にあり、下端がゲートバスライン16n+1とゲートバスライン16n+2の間にある。すなわち、薄膜トランジスタ14は、ゲートバスライン16nとドレインバスライン18mの交差位置にあるが、薄膜トランジスタ14のソース電極が下方に延びて、画素電極12の上端に接続されている。

これにより、ゲートバスライン16n、16n+1、16n+2、…間に、隣接する画素電極12間の隙間ができるので、この隙間を遮光するために遮光膜20n、20n+1、20n+2、…が設けられている。

図2に示すように、透明絶縁基板10上にゲートバスライン16n、16n+1、16n+2、…と遮光膜20n、20n+1、20n+2、…が形成されている。ゲートバスライン16n、16n+1、16n+2、…と、遮光膜20n、20n+1、20n+2、…上には、薄膜トランジスタ14のゲート絶縁膜22が形成されている。ゲート絶縁膜22上には、薄膜トランジスタ14を保護する保護膜24が形成されている。保護膜24上には画素電極12が形成されている。各画素電極12は、ゲートバスライン16n、16n+1、16n+2、…をまたがり、端部が遮光膜20n、20n+1、20n+2、…の位置に合致するように形成されている。

図3は、特定の画素電極12に注目した場合の等価回路である。

ゲートバスライン16n、16n+1、16n+2、…とドレインバスライン18m、18m+1、…の交差位置に薄膜トランジスタ14が設けられている。薄膜トランジスタ14のゲート電極はゲートバスライン16nに接続され、ドレイン電極はドレインバスライン18mに接続され、ソース電極は下方に延びて画素電極12に接続されている。その結果、薄膜トランジスタ14のソース電極には液晶による容量である液晶容量Clcが接続されている。

更に、画素電極12と遮光膜20n、20n+1、20n+2、…が重なりあっているので、遮光膜20n、20n+1、20n+2、…をゲートバスライン16n、16n+1、16n+2、…に接続することにより、画素電極12とゲートバスライン16n+1の間に補助容量Csが形成される。

このように、本実施形態によれば、画素電極間の隙間をゲートバスラインと遮光膜により遮光するようにしたので、この部分を遮光するためのブラックマトリクスを形成する必要がない。したがって、対向基板のブラックマトリクスは、薄膜トランジスタの部分だけを遮蔽すればよく、位置合わせマージンを非常に小さくすることができる。

[第2の実施形態]

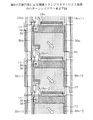

本発明の第2の実施形態による薄膜トランジスタマトリクス装置を図4及び図5を用いて説明する。図4はパターンレイアウトを示し、図5はD−D′線断面を示す。図1乃至図3に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態では、第1の実施形態における遮光膜20n、20n+1、20n+2、…をゲートバスライン16n、16n+1、16n+2、…と接続している。遮光膜20n、20n+1、20n+2、…とゲートバスライン16n、16n+1、16n+2、…を、ドレインバスライン18m、18m+1、…下の接続パターン26n、26n+1、26n+2、…により接続する。画素電極12の上半部は、ゲートバスライン16n、16n+1、16n+2、…と、遮光膜20n、20n+1、20n+2、…と、接続パターン26n、26n+1、26n+2、…により取り囲まれる。画素電極12の下半部は、ゲートバスライン16n、16n+1、16n+2、…と遮光膜20n、20n+1、20n+2、…間の領域に位置する。

画素電極12が、ゲートバスライン16n、16n+1、16n+2、…と、遮光膜20n、20n+1、20n+2、…と、接続パターン26n、26n+1、26n+2、…と重なり合うので、大きな補助容量Csが形成される。

なお、本実施形態では遮光膜20n、20n+1、20n+2、…近傍で、遮光膜20n、20n+1、20n+2、…と画素電極12の間に大きな横方向電界が発生することがある。例えば、遮光膜20n、20n+1、20n+2、…に−12.5Vが印加され、画素電極12に±3〜5Vが印加された場合には、横方向電界により液晶配向が不安定になる。このため、本実施形態では、対向基板に液晶配向処理を施して、図5に示すように、画素電極12と共通電極29間の液晶28の配向方向を遮光膜20n、20n+1、20n+2、…に向かって傾ける。これにより、液晶28の液晶配向を安定化することができる。

このように、本実施形態によれば、画素電極の上半部の周囲をゲートバスラインにより取り囲むようにしたので、この部分を遮光するためのブラックマトリクスを形成する必要がない。したがって、対向基板のブラックマトリクスは、薄膜トランジスタの部分だけを遮蔽すればよく、位置合わせマージンを非常に小さくすることができる。

また、ゲートバスラインと遮光膜とは一定の距離をおいて配置されているので、精度よく製造することができ、製造上の歩留まりが低下することはない。

更に、液晶の配向を遮蔽膜に向かって傾けることにより、液晶配向を安定化することができる。

[第3の実施形態]

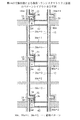

本発明の第3の実施形態による薄膜トランジスタマトリクス装置を図6乃至図8を用いて説明する。図6はパターンレイアウトを示し、図7(a)はE−E′線断面を示し、図7(b)はF−F′線断面を示し、図7(c)はG−G′線断面を示し、図8は等価回路を示す。

透明絶縁基板10上に、図6の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられ、図6の縦方向に延びるドレインバスライン18m、18m+1、…が平行に複数本設けられている。

ゲートバスライン16n、16n+1、16n+2、…には、ドレインバスライン18m、18m+1、…に沿って下方に延びる補助パターン30n、30n+1、30n+2、…が形成されている。

薄膜トランジスタ14は、この補助パターン30n、30n+1、30n+2、…の下端近傍に設けられている。薄膜トランジスタ14のゲート電極32は補助パターン30n、30n+1、30n+2、…を介してゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極34はドレインバスライン18m、18m+1、…により共通接続されている。薄膜トランジスタ14のソース電極36はコンタクトホール38を介して画素電極12に接続されている。

本実施形態における各画素電極12は、次の列のゲートバスライン16n、16n+1、16n+2、…を越えた位置に形成されている。例えば、ゲートバスライン16nに薄膜トランジスタ14を介して接続された画素電極12は、全体がゲートバスライン16n+1とゲートバスライン16n+2との間に位置している。薄膜トランジスタ14は、ゲートバスライン16nの補助パターン30nの下端に設けられ、ソース電極36がゲートバスライン16n+1上まで延びて、画素電極12の上端に接続されている。

画素電極12の下端には、補助容量Csを形成するための中間電極40が形成されている。中間電極40は、コンタクトホール42を介して画素電極12に接続されている。

本実施形態による薄膜トランジスタマトリクス装置の構造を図7(a)、図7(b)、図7(c)を用いて説明する。

図7(a)のE−E′線断面図に示すように、薄膜トランジスタ14では、透明絶縁基板10上にゲート電極32が形成され、ゲート電極32上にゲート絶縁膜22が形成されている。ゲート絶縁膜22上には、薄膜トランジスタ14のチャネル層となるアモルファスシリコン層44が形成されている。アモルファスシリコン層44上の中央のチャネル領域の両側には、ドレイン電極34とソース電極36が形成されている。薄膜トランジスタ14全体は保護膜24により覆われている。

図7(b)のF−F′線断面図に示すように、薄膜トランジスタ14の下部では、透明絶縁基板10上にゲートバスライン16n+1が形成され、ゲートバスライン16n+1上にゲート絶縁膜22が形成されている。ゲート絶縁膜22上には、薄膜トランジスタ14のチャネル層となるアモルファスシリコン層44が形成されている。アモルファスシリコン層44上にソース電極36が形成されている。ソース電極36全体は保護膜24により覆われている。保護膜24上には画素電極12が形成されている。画素電極12は、保護膜24に形成されたコンタクトホール38を介してソース電極36に接続されている。

図7(c)のG−G′線断面図に示すように、画素電極12の下端近傍では、透明絶縁基板10上にゲートバスライン16n+2が形成され、ゲートバスライン16n+2上にゲート絶縁膜22が形成されている。ゲート絶縁膜22上には、ソース電極36と同一層の中間電極40が形成されている。中間電極40全体は保護膜24により覆われている。保護膜24上には画素電極12が形成されている。画素電極12は、保護膜24に形成されたコンタクトホール42を介して中間電極40に接続されている。

図8は、特定の画素電極12に注目した場合の等価回路である。

ゲートバスライン16nとドレインバスライン18mの交差位置からゲートバスライン16n+1に近い位置に薄膜トランジスタ14が設けられている。薄膜トランジスタ14のゲート電極はゲートバスライン16nに接続され、ドレイン電極はドレインバスライン18mに接続され、ソース電極は下方に延びて画素電極12に接続されている。その結果、薄膜トランジスタ14のソース電極には液晶による容量である液晶容量Clcが接続されている。

また、ソース電極36がゲートバスライン16n+1上を覆うように大きく形成されているので、画素電極12とゲートバスライン16n+1の間に補助容量Cs′が形成される。ソース電極36がゲートバスライン16n+1と重なる面積を変化することにより、補助容量Csの容量値を調整することができる。

更に、画素電極12に接続された中間電極40がゲートバスライン16n+2上を覆うように形成されているので、画素電極12とゲートバスライン16n+2の間に補助容量Cs″が形成される。中間電極40がゲートバスライン16n+2と重なる面積を変化することにより、補助容量Cs″を調整することができる。

このように、本実施形態によれば、画素電極間の隙間をゲートバスラインにより遮光するようにしたので、この部分を遮光するためのブラックマトリクスを形成する必要がない。しかも、遮光するために設けた全ての膜が補助容量を形成するためにも用いられているので、パターンの無駄がなく、極めて高い開口率と、高い製造歩留まりを実現することができる。

[第4の実施形態]

本発明の第4の実施形態による薄膜トランジスタマトリクス装置を図9及び図10を用いて説明する。図9はパターンレイアウトを示し、図10は等価回路を示す。図6乃至図8に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の基本構成は第3の実施形態と同じであるが、ソース電極36の大きさと中間電極40の大きさが異なっている。前述したように、ソース電極36がゲートバスライン16n+1と重なる面積を変化することにより、補助容量Csの容量値を調整することができ、中間電極40がゲートバスライン16n+2と重なる面積を変化することにより、補助容量Cs″を調整することができる。

本実施形態では、ソース電極36の大きさを必要最小限にし、中間電極40の面積を最大限大きくすることにより、補助容量Cs″に対して補助容量Cs′が無視できる値となり(補助容量Cs″>>補助容量Cs′)、図10に示すように、実質的に補助容量Cs′が形成されていないようにしている。

通常のデータ書き込み動作の場合、ある行の画素電極12に書き込みが行われた直後に、次の行の画素電極12に書き込みが行われる。このため、画素電極12が、次の行のゲートバスライン16n+1と容量結合していると、薄膜トランジスタ14が完全にオフする前に次の行の書き込み動作が行われ、書き込み信号が異なってしまうおそれがある。そこで、本実施形態では、画素電極12が次の行のゲートバスライン16n+1とは容量結合せず、次の次の行のゲートバスライン16n+2と容量結合するようにしている。

したがって、本実施形態によれば、データ信号の書き込み時に、他の行の書き込み動作の影響を受けないようにして、表示品質を向上させることができる。

[第5の実施形態]

本発明の第5の実施形態による薄膜トランジスタマトリクス装置を図11乃至図16を用いて説明する。図11はパターンレイアウトを示し、図12はH−H′線断面を示し、図13は等価回路を示し、図14は液晶表示ユニットを示し、図15及び図16は駆動方法の説明図である。図6乃至図8に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の基本構成は第3の実施形態とほぼ同じであるが、図11に示すように、中間電極40を設けていない。前述したように、ソース電極36がゲートバスライン16n+1と重なる面積を変化することにより、補助容量Csの容量値を調整することができ、中間電極40がゲートバスライン16n+2と重なる面積を変化することにより、補助容量Cs″を調整することができる。

本実施形態では、中間電極40を全く設けずに、ソース電極36の面積を最大限大きくすることにより、図13に示すように、補助容量Cs′に対して補助容量Cs″が無視できる値となり(補助容量Cs′>>補助容量Cs″)、実質的に補助容量Cs″が形成されていないようにしている。

このように、本実施形態によれば、中間電極を設けないので、コンタクトホールの数を減らすことができ、接続不良による欠陥を防止することができる。また、中間電極を設けないので、ソース電極をパターン形成する際の制限や無駄がなくなり、開口率を向上することができる。

ここまでの説明では、画素電極12とゲートバスライン16間の寄生容量について注目していたが、画素電極12とゲートバスライン16間の寄生容量だけでなく、画素電極12間の寄生容量も問題となる。

画素電極12間の構造を、図12(a)のH−H′線断面図に示す。画素電極12の間の領域では、透明絶縁基板10上にゲートバスライン16n+1が形成され、ゲートバスライン16n+1上にゲート絶縁膜22が形成されている。ゲート絶縁膜22上には、ソース電極36が形成されている。ソース電極36全体は保護膜24により覆われている。保護膜24上には2つの隣接する画素電極12が形成されている。隣接する画素電極12は、ゲートバスライン16n+1、ソース電極36、ゲート絶縁膜22、保護膜24を介して接続されているので、画素電極12同士が接近すると、図12(b)に示すように、画素電極12間の寄生容量Cssが無視できなくなる。

画素電極12間の寄生容量Cssが大きい場合には、ある行の画素電極12にデータを書き込んでも、隣接する行の画素電極12にデータを書き込む際に、容量結合により画素電極12の電位が変化してしまう。

このため、たとえパターン上の余裕があったとしても、画素電極12同士を例えば5μmより近づけることはできず、一定程度以上に開口率を向上することができなかった。

本実施形態では、画素電極12同士の寄生容量が大きい場合でも、画素電極12の電位が変化しない薄膜トランジスタマトリクス装置の新規な駆動方法を提案する。

図14に、本実施形態による薄膜トランジスタマトリクス装置を用いて液晶表示ユニットを示す。

液晶パネル50は、本実施形態による薄膜トランジスタマトリクス装置に対向して対向基板(図示せず)を配置し、薄膜トランジスタマトリクス装置と対向基板との間に液晶(図示せず)を挟んで形成されている。この液晶パネル50を駆動する駆動回路してスキャンドライバ52とデータドライバ54が設けられている。スキャンドライバ52及びデータドライバ54は、接続配線56により液晶パネル50に接続されている。

スキャンドライバ52は、書き込みパルスを順次ゲートバスライン16に出力し、マトリクス状に配置された画素電極12を順次走査する。データドライバ54は、書き込むべきデータ信号をドレインバスライン18に出力して画素電極12に所望の表示を行う。

本実施形態による薄膜トランジスタマトリクス装置の駆動方法を図15及び図16を用いて説明する。

本実施形態では、ひとつの表示画像を、奇数行目の画素により構成された奇数フレームと、偶数行目の画素により構成された偶数フレームによりあらわす。奇数フレームは奇数番目のゲートバスライン16n、16n+2、…に書き込みパルスを入力して画素電極12に信号を書き込む。偶数フレームは偶数番目のゲートバスライン16n+1、16n+3、…に書き込みパルスを入力して画素電極12に信号を書き込む。このとき、本実施形態では、ひとつの画素電極12を挟んだ両側の画素電極12に対する書き込み電圧を互いに正負反対になるように駆動する。これにより、画素電極12は一方の側の画素電極12により、正負いずれかの電位に引っ張られても、他方の側の画素電極12により反対の電位に引っ張られて補償されるので、画素電極12間の寄生容量の影響を最小限に抑えることができる。

図15は、本実施形態の駆動方法の説明図である。第n番目の行の画素電極12n、第n+1番目の行の画素電極12n+1、第n+2番目の行の画素電極12n+2、第n+3番目の行の画素電極12n+3の駆動状態を示している。

第1の画像Iの奇数フレームでは、画素電極12nを負電位から正電位に駆動すると共に、画素電極12n+2を正電位から負電位に駆動する。つづいて、第1の画像Iの偶数フレームでは、画素電極12n+1を正電位から負電位に駆動すると共に、画素電極12n+3を負電位から正電位に駆動する。

つづいて、次の第2の画像IIの奇数フレームでは、画素電極12nを正電位から負電位に駆動すると共に、画素電極12n+2を負電位から正電位に駆動する。つづいて、第2の画像IIの偶数フレームでは、画素電極12n+1を負電位から正電位に駆動すると共に、画素電極12n+3を正電位から負電位に駆動する。第2の画像IIでは第1の画像Iとは正負の駆動方向を反対にしている。

以降は、同様の動作を繰り返す

図16は、図15の駆動方法を実現するためのゲートバスライン16とドレインバスライン18の駆動波形である。

第1の画像Iの奇数フレームでは、ドレインバスライン18mを正電位にしてゲートバスライン16nに書き込みパルスを印加する。これにより、画素電極12nを負電位から正電位に駆動する。その直後に、ドレインバスライン18mを負電位にしてゲートバスライン16n+2に書き込みパルスを印加する。これにより、画素電極12n+2を正電位から負電位に駆動する。

つづいて、第1の画像Iの偶数フレームでは、ドレインバスライン18mを負電位にしてゲートバスライン16n+1に書き込みパルスを印加する。これにより、画素電極12n+1を正電位から負電位に駆動する。その直後に、ドレインバスライン18mを正電位にしてゲートバスライン16n+3に書き込みパルスを印加する。これにより、画素電極12n+3を負電位から正電位に駆動する。

第2の画像IIの奇数フレームでは、ドレインバスライン18mを負電位にしてゲートバスライン16nに書き込みパルスを印加する。これにより、画素電極12nを正電位から負電位に駆動する。その直後に、ドレインバスライン18mを正電位にしてゲートバスライン16n+2に書き込みパルスを印加する。これにより、画素電極12n+2を負電位から正電位に駆動する。

つづいて、第2の画像IIの偶数フレームでは、ドレインバスライン18mを正電位にしてゲートバスライン16n+1に書き込みパルスを印加する。これにより、画素電極12n+1を負電位から正電位に駆動する。その直後に、ドレインバスライン18mを負電位にしてゲートバスライン16n+3に書き込みパルスを印加する。これにより、画素電極12n+3を正電位から負電位に駆動する。

以降は、同様の動作を繰り返す

このように、本実施形態の駆動方法によれば、各画素電極を挟む両側の画素電極に対する書き込み電圧を互いに正負反対になるように駆動するので、画素電極が一方の画素電極により正負いずれかの電位に引っ張られても、他方の画素電極により反対の電位に引っ張られて補償され、画素電極間の寄生容量の影響を最小限に抑えることができる。

画素電極間の距離が3μmにした薄膜トランジスタマトリクス装置に対して、次に示す駆動方法により駆動して画素電極間の電圧変動を測定した。薄膜トランジスタマトリクス装置において、5Vでオン状態となる液晶に対して全画素がオン状態の全黒になるように駆動する。各画素電極には+5Vと−5Vの電圧を交互に印加するので、電圧変動は10Vとなる。このような駆動方法により薄膜トランジスタマトリクス装置を駆動したところ、画素電極間の電圧変動は0.3Vとなった。

同じ薄膜トランジスタマトリクス装置を、本実施形態の駆動方法により駆動したところ、画素電極の電圧変動は0.1V以下と大幅に改善された。

また、画素電極間の距離を2μmと近づけた薄膜トランジスタマトリクス装置に対しても、本実施形態の駆動方法により駆動したところ、画素電極間の電圧変動は0.2V程度に抑えられた。

[第6の実施形態]

本発明の第6の実施形態による薄膜トランジスタマトリクス装置を図17を用いて説明する。図17はパターンレイアウトを示す。図11に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の基本構成は第6の実施形態とほぼ同じであるが、図17に示すように、ソース電極36を大きくして、前行の画素電極12との間の隙間を遮光するようにしている。これにより、対向基板側のブラックマトリクスの一部分が不要となり、開口率を更に向上することができる。

ソース電極36を大きくした結果、ソース電極36と前行のゲートバスライン16との重なり面積が増えると共に、ソース電極36と前行の画素電極12との重なり面積が増える。したがって、図13の等価回路の補助容量Cs′が増加すると共に、ソース電極36と前行の画素電極12との間の寄生容量が増加する。

ソース電極36と前行の画素電極12間に寄生容量が増加するが、画素電極12の印加電圧は最大で±5V程度しか変動しない。したがって、ゲート電圧VGの変動幅(26V)に比べるとかなり小さいので、増加した寄生容量が表示品質に与える影響は小さい。また、先に述べた駆動方法を用いることで更に影響は小さくできる。

このように、本実施形態によれば、ソース電極を大きくして隙間を遮光するようにしたので、開口率が向上して光利用効率が高くなり、明るい表示を実現すると共に低消費電力化を図ることができる。また、ソース電極が大きくなって寄生容量が増加しても、表示品質に与える影響は小さくてすみ、表示品質を劣化させることがない。

[第7の実施形態]

本発明の第7の実施形態による薄膜トランジスタマトリクス装置を図18を用いて説明する。図18はパターンレイアウトを示す。

本実施形態による薄膜トランジスタマトリクス装置は、カラー用の液晶表示ユニットに用いられる薄膜トランジスタマトリクス装置である。ひとつの画素に対してRGB用の3つの画素電極が設けられている。図6乃至図8に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

透明絶縁基板10上に、図18の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられ、図18の縦方向に延びるドレインバスライン18m、18m+1、18m+2、…が平行に複数本設けられている。

ゲートバスライン16n、16n+1、16n+2、…は、ドレインバスライン18m、18m+1、18m+2、…に沿って下方に延びる補助パターン30n、30n+1、30n+2、…が形成されている。

薄膜トランジスタ14は、この補助パターン30n、30n+1、30n+2、…の下端近傍に設けられている。薄膜トランジスタ14のゲート電極32は補助パターン30n、30n+1、30n+2、…を介してゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極34はドレインバスライン18m、18m+1、18m+2、…により共通接続されている。薄膜トランジスタ14のソース電極36は画素電極12に連続している。

本実施形態では、ひとつの画素に対して3つの画素電極12R、12G、12Bが設けられている。画素電極12R、12G、12Bは、次の列のゲートバスライン16n、16n+1、16n+2、…を越えた位置に形成されている。例えば、ゲートバスライン16nに薄膜トランジスタ14を介して接続された画素電極12R、12G、12Bは、全体がゲートバスライン16n+1とゲートバスライン16n+2との間に位置している。

このように、本実施形態によれば、画素電極間の隙間をゲートバスラインにより遮光するようにしたので、この部分を遮光するためのブラックマトリクスを形成する必要がない。しかも、遮光するために設けた全ての膜が補助容量を形成するためにも用いられているので、パターンの無駄がなく、極めて高い開口率と、高い製造歩留まりのカラー用の液晶パネルを実現することができる。

[第8の実施形態]

本発明の第8の実施形態による薄膜トランジスタマトリクス装置を図19及び図20を用いて説明する。図19はパターンレイアウトを示し、図20はI−I′線断面を示す。

薄膜トランジスタマトリクス装置のパターンレイアウトを図19を用いて説明する。画素電極12は、透明絶縁基板10上にマトリクス状に配置されている。各画素電極12には薄膜トランジスタ14が設けられている。薄膜トランジスタ14のゲート電極32を共通接続するため、図19の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が設けられている。薄膜トランジスタ14のドレイン電極34を共通接続するため、図19の縦方向に延びるドレインバスライン18m、18m+1、18m+2、…が設けられている。薄膜トランジスタ14のソース電極36はコンタクトホール38を介して画素電極12に接続されている。

本実施形態の薄膜トランジスタマトリクス装置においても、ゲートバスライン16n、16n+1、16n+2、…を用いて、画素電極12間の隙間を遮光するようにしているが、図48に示す従来の薄膜トランジスタマトリクス装置と異なり、ゲートバスライン16n、16n+1、16n+2、…が両側の画素電極12と重なる部分の面積を異なるようにしている。すなわち、図19に太い矢印で示すように、画素電極12内において液晶28が右下から左上に向かうような配向処理がなされている場合、ゲートバスライン16n、16n+1、16n+2、…の上方の画素電極12と大きく重なり、下方の画素電極12と小さく重なるようにしている。

このようにすることにより、図20に示すように、画素電極12とゲートバスライン16の間の電位差に応じた横方向電界により液晶142が配向し、画素電極12の端部近傍の液晶28に、配向方向が反転する反転境界27があらわれても、ゲートバスライン16n、16n+1、16n+2、…により遮蔽され、この歪みによる反転境界27から光が漏れることはない。

すなわち、本実施形態でも、画素電極12とゲートバスライン16の間の電位差に応じた横方向電界により液晶28の配向状態の歪みによる反転境界27が発生するが、その発生位置は画素電極12の縁部から一定距離のところである。したがって、ゲートバスライン16n、16n+1、16n+2、…を、歪みによる反転境界27が発生する画素電極12と大きく重なるようにして、光漏れを遮蔽する。

横方向電界により発生する配向状態の歪みの発生位置は、液晶28の配向状態に関連している。図20に示すように、画素電極12とゲートバスライン16間の電位差に応じた横方向電界は、液晶28をゲートバスライン16の方向に傾かせる。図20の右側の画素電極12では、横方向電界による配向方向と液晶28の配向処理方向が一致するので歪みは発生しないが、図20の左側の画素電極12では、横方向電界による配向方向が液晶28の配向処理方向の反対となるため、画素電極12の縁部から一定距離の位置に歪みによる反転境界27が発生する。

例えば、画素ピッチが65×65μmで640×480画素の薄膜トランジスタマトリクス装置の場合、歪みによる反転境界27は画素電極12の縁部から4〜5μmの位置に発生するので、ゲートバスライン16を上方の画素電極12に約7μmと大きく重なり、下方の画素電極12とは約2μmと小さく重なるようにしている。

なお、本実施形態では、液晶28の配向処理方向が画素電極12に対して約45度斜めに傾いているが、いかなる斜めの角度でも良く、画素電極12に対して上下方向に配向処理されていてもよい。液晶28の配向処理方向が、ゲートバスライン16に直交する方向の成分を有しておれば、その成分の方向に応じてゲートバスライン16の画素電極12に対する重なりが異なるようにすればよい。

このように本実施形態によれば、液晶中の歪みによる反転境界をゲートバスラインの位置をずらすことにより遮蔽したので、光漏れのない優れた表示品質の薄膜トランジスタマトリクス装置を実現できる。

[第9の実施形態]

本発明の第9の実施形態による薄膜トランジスタマトリクス装置を図21を用いて説明する。図21はパターンレイアウトを示す。図6に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

透明絶縁基板上に、図21の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられ、図21の縦方向に延びるドレインバスライン18m、18m+1、…が平行に複数本設けられている。

ゲートバスライン16n、16n+1、16n+2、…には、ドレインバスライン18m、18m+1、…に沿って下方に延びる補助パターン30n、30n+1、30n+2、…が形成されている。

薄膜トランジスタ14は、この補助パターン30n、30n+1、30n+2、…の下端近傍に設けられている。薄膜トランジスタ14のゲート電極32は補助パターン30n、30n+1、30n+2、…を介してゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極34はドレインバスライン18m、18m+1、…により共通接続されている。薄膜トランジスタ14のソース電極36はコンタクトホール38を介して画素電極12に接続されている。

本実施形態における各画素電極12は、次の列のゲートバスライン16n、16n+1、16n+2、…を越えた位置に形成されている。例えば、ゲートバスライン16nに薄膜トランジスタ14を介して接続された画素電極12は、全体がゲートバスライン16n+1とゲートバスライン16n+2との間に位置している。薄膜トランジスタ14は、ゲートバスライン16nの補助パターン30nの下端に設けられ、ソース電極36がゲートバスライン16n+1上まで延びて、画素電極12の上端に接続されている。

本実施形態の薄膜トランジスタマトリクス装置においても、第8の実施形態と同様に、ゲートバスライン16n、16n+1、16n+2、…を用いて、画素電極12間の隙間を遮光するようにしている。本実施形態では、図21に太い矢印で示すように、画素電極12内において液晶28が左上から右下に向かうような配向処理がなされているので、ゲートバスライン16n、16n+1、16n+2、…の下方の画素電極12と大きく重なり、上方の画素電極12と小さく重なるようにしている。

これは、横方向電界による液晶28の配向状態の歪みによる反転境界27が、ゲートライン16n、16n+1、16n+2、…下方の画素電極12の上縁部から一定距離のところに発生するからである。ゲートライン16n、16n+1、16n+2、…により液晶28の反転境界27を遮蔽する。

このように本実施形態によれば、液晶中の歪みによる反転境界をゲートバスラインにより遮蔽したので、光漏れのない優れた表示品質の薄膜トランジスタマトリクス装置を実現できる。

[第10の実施形態]

本発明の第10の実施形態による薄膜トランジスタマトリクス装置を図22を用いて説明する。図21はパターンレイアウトを示す。図21に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置では、ソース電極36が画素電極12と接続するための必要最小限の大きさであったが、本実施形態では、ソース電極36を画素電極12の大きさ程度に横方向に延ばしている。図22に太い矢印で示すように、画素電極12内において液晶28が左上から右下に向かうような配向処理がなされている。

本実施形態の薄膜トランジスタマトリクス装置では、画素電極12の間にソース電極36が挟まれた配置となっている。ゲートバスライン16n、16n+1、16n+2、…を用いて、画素電極12とソース電極36間の隙間を遮光する。ソース電極36は画素電極12とほぼ同電位となっているので、液晶28の反転境界27はソース電極36の上縁部から一定距離、例えば、4〜5μmの位置に発生する。したがって、ゲートバスライン16を下方のソース電極36及び画素電極12に約7μmと大きく重ならせ、上方の画素電極12とは約2μmと小さく重なるようにする。

このように本実施形態によれば、液晶中の歪みによる反転境界をゲートバスラインにより遮蔽したので、光漏れのない優れた表示品質の薄膜トランジスタマトリクス装置を実現できる。

[第11の実施形態]

本発明の第11の実施形態による薄膜トランジスタマトリクス装置を図23を用いて説明する。図23(a)に詳細なパターンレイアウトを示し、図23(b)に画素電極とゲートバスラインと容量バスラインの配置関係を示す。

本実施形態による薄膜トランジスタマトリクス装置は、カラー用の液晶表示ユニットに用いられる薄膜トランジスタマトリクス装置である。ひとつの画素に対してRGB用の3つの副画素が設けられている。本実施形態の画素電極はひとつの画素中の副画素を構成するものである。

透明絶縁基板(図示せず)上に、図23の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられている。また、ゲートバスライン16n、16n+1、16n+2、…の間には、図23の横方向に延びる容量バスライン60n、60n+1、60n+2、…が平行に複数本設けられている。更に、図23の縦方向に延びるドレインバスライン18m、18m+1、…が平行に複数本設けられている。

ゲートバスライン16n、16n+1、16n+2、…からは、ドレインバスライン18m、18m+1、18m+2、…に沿って補助パターンが下方に延びている。

薄膜トランジスタ14は、この補助パターンの下端近傍に設けられている。薄膜トランジスタ14のゲート電極32は補助パターンを介してゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極34はドレインバスライン18m、18m+1、…により共通接続されている。薄膜トランジスタ14のソース電極36はコンタクトホール38を介して画素電極12に接続されている。

本実施形態における各画素電極12は、自己の列の容量バスライン60n、60n+1、60n+2、…と、次の行のゲートバスライン16n、16n+1、16n+2、…とを越えた位置まで形成されている。例えば、ゲートバスライン16n+1に薄膜トランジスタ14を介して接続された画素電極12は、薄膜トランジスタ14から容量バスライン60n+1、ゲートバスライン16n+2を越えて、次の行の薄膜トランジスタ14までの間に位置している。薄膜トランジスタ14は、ゲートバスライン16n+1の補助パターンの下端に設けられ、ソース電極36がコンタクトホール38を解して画素電極12の上端に接続されている。

画素電極12中央の容量バスライン60n、60n+1、60n+2、…上には、補助容量Csを形成するための中間電極62が形成されている。中間電極62は、コンタクトホール64を介して画素電極12に接続されている。補助容量Csは、中間電極62と容量バスライン60n、60n+1、60n+2、…間に形成される。

画素電極12間の隙間、画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間は、対向基板上に形成されたブラックマトリクスと呼ばれる遮光膜70により遮光されている。

なお、本実施形態において、中間電極62は、小さな面積で大きな補助容量を実現するために設けられたものであり、本発明の実施に特に必須なものではない。

このように、本実施形態によれば、画素電極が自己を制御するゲートバスラインから離れた領域に設けられているので、画素電極とゲートバスライン間の容量を増加することがない。また、容量バスラインは書き込み時に電圧変動しないので、駆動電圧による変動を考慮することなく、容量バスラインを用いて画素電極の隙間を遮光することができる。

[第12の実施形態]

本発明の第12の実施形態による薄膜トランジスタマトリクス装置を図24を用いて説明する。図24(a)に詳細なパターンレイアウトを示し、図24(b)に画素電極とゲートバスラインと容量バスラインの配置関係を示す。図23に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

透明絶縁基板(図示せず)上に、図24の横方向に延びるゲートバスライン16n、16n+1、16n+2、…が平行に複数本設けられている。また、ゲートバスライン16n、16n+1、16n+2、…間のほぼ中央には、図24の横方向に延びる容量バスライン60n、60n+1、60n+2、…が平行に複数本設けられている。更に、図24の縦方向に延びるドレインバスライン18m、18m+1、…が平行に複数本設けられている。

ゲートバスライン16n、16n+1、16n+2、…からは、ドレインバスライン18m、18m+1、18m+2、…に沿って補助パターンが容量バスライン60n、60n+1、60n+2、…近傍まで下方に延びている。

薄膜トランジスタ14は、この補助パターンの下端近傍に設けられている。薄膜トランジスタ14のゲート電極32は補助パターンを介してゲートバスライン16n、16n+1、16n+2、…により共通接続され、ドレイン電極34はドレインバスライン18m、18m+1、…により共通接続されている。薄膜トランジスタ14のソース電極36はコンタクトホール38を介して画素電極12に接続されている。

本実施形態における各画素電極12は、自己の列の容量バスライン60n、60n+1、60n+2、…から、次の行の容量バスライン60n、60n+1、60n+2、…の間に形成されている。薄膜トランジスタ14は、ゲートバスライン16n+1の補助パターンの下端に設けられ、ソース電極36がコンタクトホール38を解して画素電極12の上端に接続されている。

容量バスライン60n、60n+1、60n+2、…は、薄膜トランジスタ14の直ぐ下方であって、画素電極12間に設けられている。容量バスライン60n、60n+1、60n+2、…上には、補助容量Csを形成するための中間電極62が形成されている。中間電極62は、コンタクトホール64を介して画素電極12に接続されている。

本実施形態では、図24に示すように、画素電極12間の隙間は容量バスライン60n、60n+1、60n+2、…により遮光されている。画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間は、対向基板上に形成されたブラックマトリクスと呼ばれる遮光膜70により遮光されている。

このように、本実施形態によれば、容量バスラインは書込み時に電圧変動しないので、駆動電圧による変動を考慮することなく、容量バスラインを用いて画素電極の隙間を遮光することができる。

[第13の実施形態]

本発明の第13の実施形態による薄膜トランジスタマトリクス装置を図25を用いて説明する。図24に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図24に示す第12の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、中間電極62の幅を容量バスライン60n、60n+1、60n+2、…の幅より大きくしている点に特徴がある。このようにして、画素電極12間の隙間を容量バスライン60n、60n+1、60n+2、…ではなく、中間電極62により遮光している。

中間電極62の幅を広げて画素電極12間を遮光することにおり、中間電極62と前の行の画素電極12との間に寄生容量が発生するが、値は小さく、表示品質に与える影響は小さくてすみ、表示品質を劣化させることがない。

このように、本実施形態によれば、画素電極が自己を制御するゲートバスラインから離れた領域に設けられているので、画素電極とゲートバスライン間の容量を増加することなく、画素電極に接続された中間電極を用いて画素電極の隙間を遮光することができる。

[第14の実施形態]

本発明の第14の実施形態による薄膜トランジスタマトリクス装置を図26を用いて説明する。図24に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図24に示す第12の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、ゲートバスライン16n、16n+1、16n+2、…から図26下方のゲート電極32に延びる補助パターン30n、30n+1、30n+2、…を太くすると共に、図26上方の容量パターン30n、30n+1、30n+2、…近傍に達する補助パターン30n、30n+1、30n+2、…を設けている点に特徴がある。この補助パターン30n、30n+1、30n+2、…により、画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間を遮光している。対向基板上の遮光膜70は、薄膜トランジスタ14近傍だけを遮光するように形成されている。したがって、TFT基板と対向基板の位置合せのために大きなマージンを考慮する必要がないので、開口率を向上することができる。

このように、本実施形態によれば、ゲートバスラインの補助パターンを用いて画素電極とドレインバスラインの間の隙間を遮光しているので、対向基板上の遮光膜による遮光領域を少なくすることができ、開口率を向上することができる。[第15の実施形態]

本発明の第15の実施形態による薄膜トランジスタマトリクス装置を図27を用いて説明する。図24に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図24に示す第12の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、容量バスライン30n、30n+1、30n+2、…から図26下方のゲートバスライン16n、16n+1、16n+2、…に延びる補助パターン66n、66n+1、66n+2、…を設けている点に特徴がある。この補助パターン66n、66n+1、66n+2、…により、画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間を遮光している。対向基板上の遮光膜70は、ゲートバスライン16n、16n+1、16n+2、…から薄膜トランジスタ14間の画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間と、薄膜トランジスタ14近傍の隙間だけを遮光するように形成されている。したがって、TFT基板と対向基板の位置合せのために大きなマージンを考慮する必要がないので、開口率を向上することができる。

このように、本実施形態によれば、容量バスラインの補助パターンを用いて画素電極とドレインバスラインの間の隙間を遮光しているので、対向基板上の遮光膜による遮光領域を少なくすることができ、開口率を向上することができる。

[第16の実施形態]

本発明の第16の実施形態による薄膜トランジスタマトリクス装置を図28を用いて説明する。図24に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図24に示す第12の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、ゲートバスライン16n、16n+1、16n+2、…から図26下方のゲート電極32に延びる補助パターン30n、30n+1、30n+2、…を太くすると共に、容量バスライン30n、30n+1、30n+2、…から図26下方のゲートバスライン16n、16n+1、16n+2、…に延びる補助パターン66n、66n+1、66n+2、…を設けている点に特徴がある。この補助パターン30n、30n+1、30n+2、…及び補助パターン66n、66n+1、66n+2、…により、画素電極12とドレインバスライン18m、18m+1、18m+2、…間の隙間を遮光している。対向基板上の遮光膜70は、薄膜トランジスタ14近傍だけを遮光するように形成されている。したがって、TFT基板と対向基板の位置合せのために大きなマージンを考慮する必要がないので、開口率を向上することができる。

このように、本実施形態によれば、ゲートバスラインの補助パターンと容量バスラインの補助パターンとを用いて画素電極とドレインバスラインの間の隙間を遮光しているので、対向基板上の遮光膜による遮光領域を少なくすることができ、開口率を向上することができる。

[第17の実施形態]

本発明の第17の実施形態による薄膜トランジスタマトリクス装置を図29を用いて説明する。図26に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図26に示す第14の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、第14の実施形態におけるソース電極36と中間電極62とを一体化してひとつの中間電極62にしている点に特徴がある。画素電極12に接続するコンタクトホールの数を減らすことができ、薄膜トランジスタ14と容量バスライン60n、60n+1、60n+2、…とを近接することができる。

このように、本実施形態によれば、ソース電極と中間電極を一体化して、コンタクトホールの数を減らすことができ、薄膜トランジスタと容量バスラインとを近接することができ、開口率を更に向上することができる。

[第18の実施形態]

本発明の第18の実施形態による薄膜トランジスタマトリクス装置を図30を用いて説明する。図29に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図29に示す第17の実施形態による薄膜トランジスタマトリクス装置の構成を、デルタ配列と呼ばれるカラー用の副画素配列に適用したものである。デルタ配列では、ひとつの画素に対するRGB用の3つの副画素を三角形の3つの頂点に位置するように配置されている。AV(Audio Visual)用のカラー液晶表示装置に多く採用されている。

カラー用の3つの画素電極12R、12G、12Bがデルタ配列されるように、各行の画素電極12R、12G、12Bが半ピッチずつずれて配置されている。したがって、ドレインバスライン18m、18m+1、18m+2、…は、画素電極12R、12G、12Bのずれに沿って屈曲している。薄膜トランジスタ14は、各画素電極12R、12G、12Bの上縁部中央の右側に位置している。各画素電極12R、12G、12Bと接続された中間電極62の上縁中央の右側は、薄膜トランジスタ14のソース電極として機能するように凸形状となっている。各画素電極12R、12G、12Bの下縁部は、ドレインバスライン18m、18m+1、18m+2、…の屈曲形状に合致した形状となっている。

ゲートバスライン16n、16n+1、16n+2、…から下方に延びる補助パターン30n、30n+1、30n+2、…は、ドレインバスライン18m、18m+1、18m+2、…の屈曲形状に沿って屈曲しており、画素電極12R、12G、12Bとドレインバスライン18m、18m+1、18m+2、…の間の隙間を遮光している。

このように、本実施形態によれば、デルタ配列のカラー液晶表示装置用の薄膜トランジスタマトリクス装置に対しても、ゲートバスラインの補助パターンを用いて画素電極とドレインバスラインの間の隙間を遮光し、対向基板上の遮光膜による遮光領域を少なくして、開口率を向上することができる。

[第19の実施形態]

本発明の第19の実施形態による薄膜トランジスタマトリクス装置を図31を用いて説明する。図30に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図30に示す第18の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、容量バスライン60n、60n+1、60n+2、…に補助パターン66n、66n+1、66n+2、…を設けることにより、中間電極62上縁のドレインバスライン18m、18m+1、18m+2、…と画素電極12R、12G、12Bの間の隙間を遮光している点に特徴がある。第18の実施形態のように、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…を屈曲形状にすることなく遮光することができる。

このように、本実施形態によれば、ゲートバスラインの補助パターンと容量バスラインの補助パターンを用いて画素電極とドレインバスラインの間の隙間を遮光し、対向基板上の遮光膜による遮光領域を少なくして、開口率を向上することができる。

[第20の実施形態]

本発明の第20の実施形態による薄膜トランジスタマトリクス装置を図32を用いて説明する。図30に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図30に示す第18の実施形態による薄膜トランジスタマトリクス装置と同様に、デルタ配列と呼ばれるカラー用の副画素配列に本発明を適用したものである。第18の実施形態では、カラー用の3つの画素電極12R、12G、12Bをデルタ配列するために、ドレインバスライン18m、18m+1、18m+2、…を直角に屈曲したが、本実施形態では、ドレインバスライン18m、18m+1、18m+2、…を90度より小さな角度で曲げている点に特徴がある。ドレインバスライン18m、18m+1、18m+2、…は、容量バスライン60n、60n+1、60n+2、…の上縁部で約45度曲がり、そのまま斜めに延びて、下縁部で再び約45度曲がっている。中間電極62は、ドレインバスライン18m、18m+1、18m+2、…の形状に合わせて平行四辺形の形状をしている。ドレインバスライン18m、18m+1、18m+2、…と画素電極12R、12G、12Bとの間の隙間は、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…により遮光されている。

このように、本実施形態によれば、ドレインバスラインを直角に屈曲することなく、デルタ配列のカラー液晶表示装置用の薄膜トランジスタマトリクス装置を実現することができる。

[第21の実施形態]

本発明の第21の実施形態による薄膜トランジスタマトリクス装置を図33を用いて説明する。図32に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図32に示す第20の実施形態による薄膜トランジスタマトリクス装置とほぼ同様の構成であるが、薄膜トランジスタ14を設けている位置に特徴がある。容量バスライン60n、60n+1、60n+2、…のドレインバスライン18m、18m+1、18m+2、…下の領域を凹ませて、その凹部に、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…の端部を入れている。薄膜トランジスタ14はこの凹部に形成される。補助パターン30n、30n+1、30n+2、…の端部がゲート電極として機能し、ドレインバスライン18m、18m+1、18m+2、…の一部がドレイン電極として機能し、中間電極62の一部がソース電極として機能する。

ドレインバスライン18m、18m+1、18m+2、…と画素電極12R、12G、12Bとの間の隙間は、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…により遮光されている。遮光膜70は、容量バスライン60n、60n+1、60n+2、…の凹部近傍だけに設けられる。

このように、本実施形態によれば、薄膜トランジスタを容量バスラインの形成領域に設けたので、画素電極の実効面積を増大して、開口率を更に向上することができる。

[第22の実施形態]

本発明の第22の実施形態による薄膜トランジスタマトリクス装置を図34を用いて説明する。図26に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図26に示す第14の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、薄膜トランジスタ14を設けている位置に特徴がある。容量バスライン60n、60n+1、60n+2、…のドレインバスライン18m、18m+1、18m+2、…下の領域を凹ませて、その凹部に、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…の端部のゲート電極32を入れている。薄膜トランジスタ14はこの凹部に形成される。ゲート電極32とドレイン電極34と中間電極62の一部のソース電極により、薄膜トランジスタ14が構成される。

ドレインバスライン18m、18m+1、18m+2、…と画素電極12R、12G、12Bとの間の隙間は、ゲートバスライン16n、16n+1、16n+2、…の補助パターン30n、30n+1、30n+2、…により遮光されている。遮光膜70は、容量バスライン60n、60n+1、60n+2、…の凹部近傍だけに設けられる。

このように、本実施形態によれば、薄膜トランジスタを容量バスラインの形成領域に設けたので、画素電極の実効面積を増大して、開口率を更に向上することができる。

[第23の実施形態]

本発明の第23の実施形態による薄膜トランジスタマトリクス装置を図35を用いて説明する。図34に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図34に示す第22の実施形態による薄膜トランジスタマトリクス装置の構成を、デルタ配列と呼ばれるカラー用の副画素配列に適用したものである。ドレインバスライン18m、18m+1、18m+2、…が、画素電極12R、12G、12Bのずれに沿って直角に屈曲している。ドレインバスライン18m、18m+1、18m+2、…を、容量バスライン60n、60n+1、60n+2、…の上縁部の一部を凹ませた凹部で屈曲するようにして、この凹部内に薄膜トランジスタ14を形成する。補助パターン30n、30n+1、30n+2、…の端部がゲート電極として機能し、ドレインバスライン18m、18m+1、18m+2、…の一部がドレイン電極として機能し、中間電極62の一部がソース電極として機能する。

ゲートバスライン16n、16n+1、16n+2、…から下方に延びる補助パターン30n、30n+1、30n+2、…は、ドレインバスライン18m、18m+1、18m+2、…の屈曲形状に沿って屈曲しており、画素電極12R、12G、12Bとドレインバスライン18m、18m+1、18m+2、…の間の隙間を遮光している。

このように、本実施形態によれば、デルタ配列のカラー液晶表示装置用の薄膜トランジスタマトリクス装置に対しても、薄膜トランジスタを容量バスラインの形成領域に設けて、画素電極の実効面積を増大して、開口率を更に向上することができる。

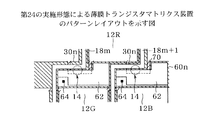

[第24の実施形態]

本発明の第24の実施形態による薄膜トランジスタマトリクス装置を図36を用いて説明する。図35に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図35に示す第23の実施形態による薄膜トランジスタマトリクス装置とほぼ同様の構成であるが、容量バスライン60n、60n+1、60n+2、…の凹部を小さくしている点が異なっている。ドレインバスライン18m、18m+1、18m+2、…の全ての屈曲部分を含むように凹部を形成するのではなく、薄膜トランジスタ14に必要最小限の領域だけを凹ませている。中間電極62の面積を大きくすることができ、大きな補助容量を実現できる。

このように、本実施形態によれば、デルタ配列のカラー液晶表示装置用の薄膜トランジスタマトリクス装置に対しても、薄膜トランジスタを容量バスラインの形成領域に設けて、画素電極の実効面積を増大して、開口率を更に向上することができる。

[第25の実施形態]

本発明の第25の実施形態による薄膜トランジスタマトリクス装置を図37を用いて説明する。図29に示す薄膜トランジスタマトリクス装置と同一又は同種の構成要素には同一の符号を付して説明を省略又は簡略にする。

本実施形態の薄膜トランジスタマトリクス装置は、図29に示す第17の実施形態による薄膜トランジスタマトリクス装置とほぼ同様な構成であるが、ゲート電極32の更に大きくして、薄膜トランジスタ14近傍の隙間を遮光するようにした点に特徴がある。ゲート電極32により、ドレインバスライン18m、18m+1、18m+2、…及びドレイン電極34と、画素電極12との間の隙間を覆うようにしている。対向基板の遮光膜70は薄膜トランジスタ14と容量バスライン60n、60n+1、60n+2、…間の隙間だけを遮光すればよい。

このように、ゲート電極32を大きくすることにおり、ゲート電極32と前の行の画素電極12との間に寄生容量が発生するが、値は小さく、表示品質に与える影響は小さくてすみ、表示品質を劣化させることがない。

このように、本実施形態によれば、ゲート電極を用いて画素電極の隙間を遮光することにより、対向基板の遮光膜による遮光領域を更に少なくすることができ、開口率を更に向上することができる。

[変形例]

本発明は上述した実施の形態に限らず種々の変形が可能である。

例えば、上述した実施の形態では、トランジスタとして薄膜トランジスタを記載したが、画素電極にスイッチングする素子であれば、MOSトランジスタ等の他の非線形素子であってもよい。