JP2005260235A - トレンチ内に独立制御可能な制御ゲートを有する埋込ビット線型不揮発性浮遊ゲートメモリセル、そのアレイ、及び製造方法 - Google Patents

トレンチ内に独立制御可能な制御ゲートを有する埋込ビット線型不揮発性浮遊ゲートメモリセル、そのアレイ、及び製造方法 Download PDFInfo

- Publication number

- JP2005260235A JP2005260235A JP2005065101A JP2005065101A JP2005260235A JP 2005260235 A JP2005260235 A JP 2005260235A JP 2005065101 A JP2005065101 A JP 2005065101A JP 2005065101 A JP2005065101 A JP 2005065101A JP 2005260235 A JP2005260235 A JP 2005260235A

- Authority

- JP

- Japan

- Prior art keywords

- region

- trench

- floating gate

- forming

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

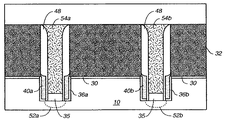

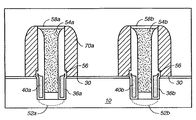

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

Landscapes

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/797,296 US7307308B2 (en) | 2003-04-07 | 2004-03-09 | Buried bit line non-volatile floating gate memory cell with independent controllable control gate in a trench, and array thereof, and method of formation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005260235A true JP2005260235A (ja) | 2005-09-22 |

| JP2005260235A5 JP2005260235A5 (enExample) | 2008-04-24 |

Family

ID=35085603

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005065101A Pending JP2005260235A (ja) | 2004-03-09 | 2005-03-09 | トレンチ内に独立制御可能な制御ゲートを有する埋込ビット線型不揮発性浮遊ゲートメモリセル、そのアレイ、及び製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JP2005260235A (enExample) |

| KR (1) | KR20060043534A (enExample) |

| CN (1) | CN1691336A (enExample) |

| TW (1) | TW200601461A (enExample) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016515771A (ja) * | 2013-04-16 | 2016-05-30 | シリコン ストーリッジ テクノロージー インコーポレイテッドSilicon Storage Technology, Inc. | 自己整列浮遊及び消去ゲートを有する不揮発性メモリセル及びその製造方法 |

| CN110010606A (zh) * | 2018-01-05 | 2019-07-12 | 硅存储技术公司 | 衬底沟槽中具有浮栅的双位非易失性存储器单元 |

| WO2025074208A1 (ja) * | 2023-10-04 | 2025-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4868629A (en) * | 1984-05-15 | 1989-09-19 | Waferscale Integration, Inc. | Self-aligned split gate EPROM |

| US5160986A (en) * | 1988-12-05 | 1992-11-03 | Sgs-Thomson Microelectronics S.R.L. | Matrix of EPROM memory cells with a tablecloth structure having an improved capacitative ratio and a process for its manufacture |

| US5278439A (en) * | 1991-08-29 | 1994-01-11 | Ma Yueh Y | Self-aligned dual-bit split gate (DSG) flash EEPROM cell |

| US5412600A (en) * | 1991-10-09 | 1995-05-02 | Mitsubishi Denki Kabushiki Kaisha | Non-volatile semiconductor device with selecting transistor formed between adjacent memory transistors |

| US5414693A (en) * | 1991-08-29 | 1995-05-09 | Hyundai Electronics Industries Co., Ltd. | Self-aligned dual-bit split gate (DSG) flash EEPROM cell |

| US5786612A (en) * | 1995-10-25 | 1998-07-28 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device comprising trench EEPROM |

| US6331721B1 (en) * | 1996-12-09 | 2001-12-18 | Mosel Vitelic Inc | Memory cell with built in erasure feature |

| US20030223296A1 (en) * | 2002-04-05 | 2003-12-04 | Hu Yaw Wen | Self-aligned method of forming a semiconductor memory array of floating gate memory cells with buried source line and floating gate, and a memory array made thereby |

-

2005

- 2005-02-22 TW TW094105237A patent/TW200601461A/zh unknown

- 2005-03-08 KR KR1020050019259A patent/KR20060043534A/ko not_active Withdrawn

- 2005-03-08 CN CNA2005100550905A patent/CN1691336A/zh active Pending

- 2005-03-09 JP JP2005065101A patent/JP2005260235A/ja active Pending

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4868629A (en) * | 1984-05-15 | 1989-09-19 | Waferscale Integration, Inc. | Self-aligned split gate EPROM |

| US5160986A (en) * | 1988-12-05 | 1992-11-03 | Sgs-Thomson Microelectronics S.R.L. | Matrix of EPROM memory cells with a tablecloth structure having an improved capacitative ratio and a process for its manufacture |

| US5278439A (en) * | 1991-08-29 | 1994-01-11 | Ma Yueh Y | Self-aligned dual-bit split gate (DSG) flash EEPROM cell |

| US5414693A (en) * | 1991-08-29 | 1995-05-09 | Hyundai Electronics Industries Co., Ltd. | Self-aligned dual-bit split gate (DSG) flash EEPROM cell |

| US5412600A (en) * | 1991-10-09 | 1995-05-02 | Mitsubishi Denki Kabushiki Kaisha | Non-volatile semiconductor device with selecting transistor formed between adjacent memory transistors |

| US5786612A (en) * | 1995-10-25 | 1998-07-28 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device comprising trench EEPROM |

| US6331721B1 (en) * | 1996-12-09 | 2001-12-18 | Mosel Vitelic Inc | Memory cell with built in erasure feature |

| US20030223296A1 (en) * | 2002-04-05 | 2003-12-04 | Hu Yaw Wen | Self-aligned method of forming a semiconductor memory array of floating gate memory cells with buried source line and floating gate, and a memory array made thereby |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016515771A (ja) * | 2013-04-16 | 2016-05-30 | シリコン ストーリッジ テクノロージー インコーポレイテッドSilicon Storage Technology, Inc. | 自己整列浮遊及び消去ゲートを有する不揮発性メモリセル及びその製造方法 |

| CN110010606A (zh) * | 2018-01-05 | 2019-07-12 | 硅存储技术公司 | 衬底沟槽中具有浮栅的双位非易失性存储器单元 |

| EP3735705A4 (en) * | 2018-01-05 | 2022-01-26 | Silicon Storage Technology, Inc. | DOUBLE-BIT NON-VOLATILE MEMORY CELLS WITH FLOATING GATES IN SUBSTRATE TREES |

| CN110010606B (zh) * | 2018-01-05 | 2023-04-07 | 硅存储技术公司 | 衬底沟槽中具有浮栅的双位非易失性存储器单元 |

| EP4301107A3 (en) * | 2018-01-05 | 2024-04-03 | Silicon Storage Technology Inc. | Twin bit non-volatile memory cells with floating gates in substrate trenches |

| WO2025074208A1 (ja) * | 2023-10-04 | 2025-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20060043534A (ko) | 2006-05-15 |

| TW200601461A (en) | 2006-01-01 |

| CN1691336A (zh) | 2005-11-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7307308B2 (en) | Buried bit line non-volatile floating gate memory cell with independent controllable control gate in a trench, and array thereof, and method of formation | |

| US7315056B2 (en) | Semiconductor memory array of floating gate memory cells with program/erase and select gates | |

| US9293204B2 (en) | Non-volatile memory cell with self aligned floating and erase gates, and method of making same | |

| US6952034B2 (en) | Semiconductor memory array of floating gate memory cells with buried source line and floating gate | |

| US8148768B2 (en) | Non-volatile memory cell with self aligned floating and erase gates, and method of making same | |

| JP5035775B2 (ja) | ソース側消去を伴うフローティングゲートメモリセルの半導体メモリアレイを形成する自己整合法及びこれによって形成されるメモリアレイ | |

| US20050045940A1 (en) | Self-aligned method of forming a semiconductor memory array of floating gate memory cells with buried floating gate, and a memory array made thereby | |

| US8546217B2 (en) | Flash memory and method for forming the same | |

| CN100440514C (zh) | 非易失浮栅存储单元及其阵列以及其形成方法 | |

| US20150179749A1 (en) | Non-volatile Memory Cell With Self Aligned Floating And Erase Gates, And Method Of Making Same | |

| US20140264540A1 (en) | Scalable and reliable non-volatile memory cell | |

| KR100621553B1 (ko) | 비휘발성 메모리 소자 및 그 제조방법 | |

| US7190018B2 (en) | Bi-directional read/program non-volatile floating gate memory cell with independent controllable control gates, and array thereof, and method of formation | |

| WO2016118530A1 (en) | High density split-gate memory cell | |

| US6822287B1 (en) | Array of integrated circuit units with strapping lines to prevent punch through | |

| US6936883B2 (en) | Bi-directional read/program non-volatile floating gate memory cell and array thereof, and method of formation | |

| EP3994731A1 (en) | Method of forming split-gate flash memory cell with spacer defined floating gate and discretely formed polysilicon gates | |

| JP2005260235A (ja) | トレンチ内に独立制御可能な制御ゲートを有する埋込ビット線型不揮発性浮遊ゲートメモリセル、そのアレイ、及び製造方法 | |

| EP1146562A2 (en) | Cell array, operating method of the same and manufacturing method of the same | |

| JP4427431B2 (ja) | 半導体記憶装置、半導体記憶装置の製造方法および半導体記憶装置の動作方法 | |

| US20070069275A1 (en) | Bi-directional read/program non-volatile floating gate memory array, and method of formation |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080310 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080310 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101108 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110411 |