JP2004506388A - 完全電子化高解像度ディジタルスチルカメラ - Google Patents

完全電子化高解像度ディジタルスチルカメラ Download PDFInfo

- Publication number

- JP2004506388A JP2004506388A JP2002518734A JP2002518734A JP2004506388A JP 2004506388 A JP2004506388 A JP 2004506388A JP 2002518734 A JP2002518734 A JP 2002518734A JP 2002518734 A JP2002518734 A JP 2002518734A JP 2004506388 A JP2004506388 A JP 2004506388A

- Authority

- JP

- Japan

- Prior art keywords

- pixels

- sensor array

- camera system

- array

- electronic camera

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 94

- 238000003860 storage Methods 0.000 claims abstract description 89

- 230000004044 response Effects 0.000 claims abstract description 22

- 238000000034 method Methods 0.000 claims description 36

- 230000010354 integration Effects 0.000 claims description 28

- 230000003287 optical effect Effects 0.000 claims description 28

- 238000001514 detection method Methods 0.000 claims description 7

- 238000004364 calculation method Methods 0.000 claims description 5

- 238000005286 illumination Methods 0.000 claims 1

- 230000000977 initiatory effect Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 22

- 230000004888 barrier function Effects 0.000 description 21

- 238000005070 sampling Methods 0.000 description 20

- 238000012545 processing Methods 0.000 description 14

- 230000002829 reductive effect Effects 0.000 description 14

- 238000012546 transfer Methods 0.000 description 11

- 230000006870 function Effects 0.000 description 10

- 230000008901 benefit Effects 0.000 description 9

- 230000000295 complement effect Effects 0.000 description 9

- 238000013461 design Methods 0.000 description 9

- 230000000737 periodic effect Effects 0.000 description 8

- 230000008859 change Effects 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 230000009467 reduction Effects 0.000 description 6

- 230000035945 sensitivity Effects 0.000 description 6

- 230000008569 process Effects 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- 230000001186 cumulative effect Effects 0.000 description 3

- 230000001934 delay Effects 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000036961 partial effect Effects 0.000 description 3

- 229920006395 saturated elastomer Polymers 0.000 description 3

- 230000000007 visual effect Effects 0.000 description 3

- 238000012935 Averaging Methods 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 229920001971 elastomer Polymers 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 230000033001 locomotion Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 230000003466 anti-cipated effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000806 elastomer Substances 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- XDDAORKBJWWYJS-UHFFFAOYSA-N glyphosate Chemical compound OC(=O)CNCP(O)(O)=O XDDAORKBJWWYJS-UHFFFAOYSA-N 0.000 description 1

- 230000036039 immunity Effects 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000011514 reflex Effects 0.000 description 1

- 238000010187 selection method Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/60—Control of cameras or camera modules

- H04N23/67—Focus control based on electronic image sensor signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

- H04N23/73—Circuitry for compensating brightness variation in the scene by influencing the exposure time

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/60—Control of cameras or camera modules

- H04N23/63—Control of cameras or camera modules by using electronic viewfinders

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/40—Extracting pixel data from image sensors by controlling scanning circuits, e.g. by modifying the number of pixels sampled or to be sampled

- H04N25/44—Extracting pixel data from image sensors by controlling scanning circuits, e.g. by modifying the number of pixels sampled or to be sampled by partially reading an SSIS array

- H04N25/441—Extracting pixel data from image sensors by controlling scanning circuits, e.g. by modifying the number of pixels sampled or to be sampled by partially reading an SSIS array by reading contiguous pixels from selected rows or columns of the array, e.g. interlaced scanning

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/53—Control of the integration time

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N3/00—Scanning details of television systems; Combination thereof with generation of supply voltages

- H04N3/10—Scanning details of television systems; Combination thereof with generation of supply voltages by means not exclusively optical-mechanical

- H04N3/14—Scanning details of television systems; Combination thereof with generation of supply voltages by means not exclusively optical-mechanical by means of electrically scanned solid-state devices

- H04N3/15—Scanning details of television systems; Combination thereof with generation of supply voltages by means not exclusively optical-mechanical by means of electrically scanned solid-state devices for picture signal generation

- H04N3/155—Control of the image-sensor operation, e.g. image processing within the image-sensor

- H04N3/1562—Control of the image-sensor operation, e.g. image processing within the image-sensor for selective scanning, e.g. windowing, zooming

Abstract

電子カメラシステムの複数の画素を有する半導体センサアレイはレンズシステムと光学的に連結される。各画素は入射光の関数である出力信号を生成する。センサ制御回路はユーザ入力に応じて半導体センサアレイ中の画素の動作を制御するセンサ制御信号を生成する。半導体センサアレイから、センサ制御信号が第1の状態にあるとき第1のセットの画素における光の強度を表す第1のセットの画像出力信号を生成し、センサ制御信号が第2の状態にあるとき第2のセットの画素における光の強度を表す第2のセットの画像出力信号を生成し、第1のセットの画素は第2のセットの画素より多くの画素を有する回路が設けられる。記憶媒体はセンサアレイと連結され、センサ制御信号が第1の状態にあるとき第1のセットの画像出力信号の表現を格納する。ディスプレイはセンサ制御信号が第2の状態にあるとき第2のセットの画像出力信号を表示する。

Description

【0001】

【発明の属する技術分野】

本願は、2000年8月4日に出願された米国仮出願第60/222,810号に対する優先権を主張する。

【0002】

【従来の技術】

本願は、ディジタルスチルカメラに関し、特に、新しいタイプの完全電子化高解像度ディジタルスチルカメラに関する。

【0003】

図1に、最もシンプルな形の従来技術におけるディジタルスチルカメラを示す。図1の左側の場面からの光線10は、主光学系12によって、センサチップ14上に焦点が合わせられる。光学系12及びセンサチップ14は、光を通さないハウジング16の中に収容されていて、迷光がセンサチップ14上に入射することを防止していて、それによって、光線10によって形成される画像が劣化することを防止している。同じ場面からの別の光線18は、それらがカメラのユーザの目22によって見ることができるように、副光学系20によって焦点が合わされる。光を通さないバッフル24は、副光学系20からチャンバハウジングのセンサチップ14を分離している。図1に示した構成は、箱型のフィルムカメラのそれと同じであり、フィルムがセンサチップ14に置き換えられている。

【0004】

図1に示した従来技術におけるディジタルスチルカメラの一般的な電子システムを図2に示す。センサチップ14からの出力信号は、処理回路26によって処理され、記憶媒体28に格納される。センサチップ14は、電荷結合素子(CCD)または相補型金属酸化膜半導体(CMOS)のどちらのタイプのセンサでもよい。記憶媒体28は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路30は、センサチップ14、処理回路26、及び記憶媒体28を制御して動作させる信号を供給する。このタイプのカメラは、一般に低コストで固定焦点のシャッターを押すだけの種類のものであり、自動焦点メカニズムは持っていない。

【0005】

図3に、関連しているが僅かに洗練された従来技術におけるカメラの構成を示す。ここでは、ファインダの像は、反射面32及び34によって、主光学系12を通過する主光線10から得られ、そして、副光学系20によって、カメラのユーザの目22によって見ることができるように焦点が合わせられる。電子露出が要求されると、図示されていない機械系が、センサチップ14への直接的な光の経路から反射面32を旋回させる。図3の構成は、一眼レフタイプのフィルムカメラのそれと同じであり、ここでも、フィルムがセンサチップに置き換えられている。

【0006】

図4に、図3に示した従来技術におけるディジタルスチルカメラに用いられる一般的な電子システムを示す。センサチップ14からの出力信号は、処理回路26によって処理され、記憶媒体28に格納される。センサチップ14は、CCDもしくはCMOSタイプのどちらでもよい。記憶媒体28は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路30は、センサチップ14、処理回路26、及び記憶媒体28を制御して動作させる信号を供給する。

【0007】

このタイプのカメラは、対応するフィルムカメラ内で見いだされるのと同じ自動焦点及び自動露出メカニズムを用いている。自動焦点は、副次的なミラー及びセンサを用いて完成されるが、これらは、正確に並べられていなければならない。このタイプのカメラ設計の適切な概観が、サイエンティフィックアメリカンの2000年8月号に掲載されている。このような設計の注目に値する特性は、機械的複雑さであり、これは、ミラーを動かすことを必要としていて、かつ、迅速な動きの後に再び高い精度で位置決めされなければならない。これらの非常に正確な機械的メカニズムは脆く、そして温度変化の際に機能不全となる傾向がある。また、それらは、製造するのに多くの費用がかかる。

【0008】

図4に示した電子システムは、自動焦点及び自動露出のサブシステムを動作させるための、いくつかの構成要素を備えている。制御回路30は、焦点センサ36及び露出センサ38からの入力を受け取り、制御信号を生成して、これにより、アクチュエータ40への通電を行い、反射面32を旋回させ、かつ主光学系12のアパチャ及び焦点を制御する。制御回路30は、焦点及び露出のための制御信号を計算する際に、センサ14から得られる信号を利用せずに、これらの計算のためのセンサ36及び38に頼らなければならないことが分かる。従って、主イメージセンサチップ14とセンサ36及び38との偏差は、不十分な焦点、不十分な露出、或いはこれらの両方によって、直ちに媒体28に格納される画像の品位を下げるであろう。従って、ファインダ、自動焦点及び自動露出の問題に対して、主センサチップ14によって生成される情報を用いて、追加のセンサを必要としない、完全な電子化という解決策を見いだすことが望ましく、これにより、機械的複雑さ、及び、複数の部品の正確な位置合せが不要になる。

【0009】

図5に、第2の形の従来技術におけるディジタルスチルカメラを示す。図5の左側の場面からの光線50は、主光学系52によってセンサチップ54上に焦点が合わされる。図5に示していないが、図7に詳細に示す電子システムは、センサチップ54から電気信号を受け取り、フラットパネルディスプレイを駆動するのに適した電気信号を得る。このディスプレイは、一般的には、液晶タイプのものである。フラットパネルディスプレイからの光線は、カメラのユーザの目によって直接見られる。

【0010】

図6に、ディジタルスチルカメラに関連する設計を示す。図6の左側の場面からの光線50は、主光学系52によってセンサチップ54上に焦点が合わされる。図6には示していないが、図7に詳細に示す電子システムは、センサチップ54から電気信号を受け取り、ブラウン管68を駆動するのに適した電気信号を得る。ブラウン管68からの光線64は、それらがカメラのユーザの目62によって見ることができるように、副光学系66によって焦点が合わされる。図5及び図6のファインダシステムは、ビデオカメラに用いられるものと同じ形であり、これらの原理で動作するスチルカメラは、ユーザが露出ボタンを押したときに1フレームのみが記憶されるビデオカメラと見なすこともできる。図5及び図6に示した設計のカメラは、これらの特徴を組み込んだビデオカメラからよく分かるように、イメージセンサ54からの信号を用いることによる初歩的な自動焦点及び自動露出が可能である。しかしながら、そのような方法で達成可能な焦点及び露出制御の質は、極度に限られていて、高解像度スチール写真にとって必要な品質レベルのかなり下になる。

【0011】

図7に、図5及び6に示した従来技術におけるディジタルスチルカメラの電子システムを示す。センサチップ54からの出力信号は、処理回路70によって処理され、記憶媒体72に格納される。センサチップ54は、CCDもしくはCMOSタイプのどちらでもよい。記憶媒体72は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路74は、センサチップ54、処理回路70、及び記憶媒体72を制御して動作させる信号を供給する。更に、処理回路70は、フラットパネルディスプレイ58またはブラウン管68のいずれかを駆動するのに適した出力信号を供給し、制御回路74は、フラットパネルディスプレイ58またはブラウン管68のいずれかを制御して動作させる信号を供給する。

【0012】

【発明が解決しようとする課題】

図1,2,3,4,5,6及び7に示した全ての部品及び構成は、この分野では良く知られていて、世界中のカメラメーカーから入手できる数百もの商品において具体化されている。いくつかの場合においては、これらの図に示した技術の組み合わせを、1つの製品の中から見いだすことができる。

【0013】

【課題を解決するための手段】

従来技術の欠点及び不利な点は、完全電子化高解像度ディジタルスチルカメラによって克服される。電子カメラシステムは、カメラと結合しているレンズシステムの焦点面における光軸の位置に配置された複数の画素を有する半導体センサアレイを備えている。各画素は、その上への入射光の関数である出力信号を生成する。センサ制御回路は、半導体センサアレイと連結されていて、カメラシステムのユーザからの入力に応じて半導体センサアレイ中の画素の動作を制御するためのセンサ制御信号を生成するのに適合している。半導体センサアレイからの2セットの画像出力信号を生成する回路が設けられている。センサ制御信号が第1の状態にあるとき、第1のセットの画像出力信号は、第1のセットの画素における光の強度を表していて、センサ制御信号が第2の状態にあるとき、第2のセットの画像出力信号は、第2のセットの画素における光の強度を表している。第1のセットの画素は、第2のセットの画素より多くの数の画素を含んでいる。記憶媒体は、センサアレイと連結されていて、センサ制御信号が第1の状態にあるとき、第1のセットの画像出力信号の表現(representation)を格納するのに適合している。ディスプレイは、センサ制御信号が第2の状態にあるとき、第2のセットの画像出力信号を表示するのに適合している。

【0014】

1つのカメラシステム内で、第1のセットの画素は、アレイ中の画素の大多数であり、第2のセットの画素は、アレイ中の画素の予め設定された一部分であり、これは、アレイ中の画素の合計の半分未満である。アレイは、画素の複数の行及び列として配列され、第2のセットの画素は、少なくともアレイのM列毎の画素の大多数、及び、少なくともアレイのN行毎の画素の大多数を含んでいる。ここでM及びNは1より大きい。MとNは、お互いに等しくてもよい。

【0015】

本発明の他の特徴によれば、半導体センサアレイは、CMOSセンサアレイであり、垂直(vertical)色フィルタCMOSセンサアレイであってもよい。記憶媒体は、半導体メモリアレイであることが好ましい。また、ここに開示されたカメラシステムは、合焦信号を用いて焦点を合わせることができるレンズシステムを備えていてもよく、かつ、センサ制御信号が第2の状態にあるときに、画像出力信号から光の合焦の質を示す合焦信号を計算し、この合焦信号に応じてレンズ制御信号を生成する装置を備えていてもよい。

【0016】

【発明の実施の形態】

本願は、主センサチップによって生成される情報を用いて、追加のセンサを必要としない、ファインダ、自動焦点及び自動露出問題に対する完全電子化の実現を提供する。従って、本発明は、機械的複雑さ、及び、複数の部品の正確な位置合せを不要にする。

【0017】

図8に、ディジタルスチルカメラを示す。図の左側の場面からの光線80は、主光学系82によってセンサチップ84上に焦点が合わされる。センサチップ84において用いられる好ましい光変換器は、3重井戸(triple−well)フォトダイオード構成であり、これは、以下で詳細に説明され、かつ図9に示される。使用に適したセンサ回路は、自動露出検出を有する高感度記憶画素センサ(high−sensitivitystoragepixelsensor)であり、これは、以下で詳細に説明され、かつ図10〜12に示される。光学系82及びセンサチップ84は、光を通さないハウジング86内に収容されていて、迷光がセンサチップ84上に入射することを防止していて、それによって、光線80によって形成される画像が劣化することを防止している。図8には示していないが、図13に詳細に示す電子システムは、センサチップ84から電気信号を受け取り、表示チップ94を駆動するのに適した電気信号を得るが、これは、Texas Instrumentsから供給されるようなマイクロマシンで作られた反射タイプのものであっても、Kopin、MicroDisplay Corp.またはInvisoのようなマイクロディスプレイの供給業者から供給されるような液晶で覆われたタイプのものであってもよい。

【0018】

表示チップ94は、発光ダイオード(LED)アレイ96によって照らされる。表示チップ94からの反射光は、それらがカメラのユーザの目92によって見ることができるように、副光学系90によって焦点が合わされる。もう一つの選択肢として、表示チップ94は、有機(organic)発光アレイであってもよく、これは、直接、光を発するので、LEDアレイ96を必要としない。両方の技術は、優れた色の彩度を有する明るい表示をもたらし、かつパワーをほとんど消費しないので、図8に示したようなコンパクトカメラのハウジング内に組み込むのに適している。光を通さないバッフル88は、チャンバハウジングのセンサチップ14を、そのハウジングのLEDアレイ96、表示チップ94、及び副光学系90から分離している。明るい太陽光の中で表示チップ94からの像を見ることは、ゴムすなわちエラストマーのアイカップ98を設けることによって、より容易になる。

【0019】

図8の構成の動作は、図13を参照することによって最もよく理解される。図13は、図8のカメラを動作させ、かつ制御するために用いられる電子回路のブロック図を示している。センサチップ84からの出力信号は、処理回路100によって処理され、記憶媒体102に格納される。センサチップ84は、それが本発明に用いられることを可能にする、ある特有の能力を備えていなければならない。記憶媒体102は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものであってもよい。制御回路106は、センサチップ84、処理回路100、及び記憶媒体102を制御して動作させる信号を供給する。更に、処理回路100は、表示チップ94を駆動するのに適した出力信号を供給し、制御回路106は、LEDアレイ96を制御して駆動するための信号を供給する。処理回路100は、好ましい状況においては、センサチップ84上に位置していて、これに組み込まれている。

【0020】

高解像度スチルカメラのために、センサチップ84は、表示チップ94のそれより、はるかに高い解像度(画素数)を有している。このため、取り込まれた画像に用いられたデータの一部分のみが、ファインダの像のために用いられる。従って、信号101は、フレーム毎に、わずかな画素しか持っていなくて、信号103より、はるかに高いフレームレートを持っている。信号103は、処理回路100によって媒体102上への記憶のために生成される。

【0021】

大きな利点が、画素のサブセットをアドレスすることが可能なセンサチップ84のための設計を用いることによって得られる。好ましい実施形態においては、以下で説明され、かつ図14〜19に示されるようなアドレス指定ロジックが用いられる。例えば、4番目毎の行における4番目毎の画素が、連続してアドレスされることによって、フレーム毎のスキャンアウト(scanout)時間を、16の率で短くすることが可能になる。

【0022】

実際の高解像度センサチップにおいては、スキャンアウト時間は、ファインダのフレームリフレッシュレートを左右する。例えば、4000X4000画素のセンサチップは、16,000,000画素を有している。20MHzのレートでスキャンされると、フレームレートは、1秒当たり1.25フレームであり、これでは、リアルタイムの現実感のあるファインダとしては、あまりにも遅い。4番目毎の行における4番目毎の画素を20MHzでスキャンすれば、1000X1000の表示チップを、1秒当たり25フレームで更新することができ、ユーザに提示されるレートは、非常に現実感があり、快適なリアルタイムのファインダをもたらす。この分野においてよく知られているように、CCDセンサは、各クロックサイクル内のいくつかの画素を「捨てる(binning)」ことによって、同様のフレームレートの利点を得ることができる。速いフレームレートを用いて、リアルタイムで、生き生きした、ユーザにわかりやすいファインダを達成することは、不可欠な特徴である。露光が取り込まれると、上記で用いられた例における16,000,000画素の全ては、制御回路106による制御の下で、スキャンされて、処理回路100を介して記憶媒体102内に格納される。

【0023】

自動焦点及び自動露出の動作の両方が、リアルタイムに、ユーザに分かるほどの遅延なしで起こることは重要である。露出及び焦点の情報の両方は、主センサとの位置合わせ不良の影響を受けやすい他のセンサから間接的に得られる信号から計算されるよりは、主センサの画像そのものから計算されるのが最も望ましい。上述したフレームレートの利点は、好ましい実施形態において、直接、主センサチップ84によって生成された信号から得られる完全電子化自動焦点を提供するのに用いられる。焦点位置(metric)回路104は、処理回路100から高いフレーム速度でファインダ信号101を受け取り、そこから所定のファインダフレームの焦点の質を表す信号105を計算する。前記焦点位置を計算する方法は、より十分に以下で説明され、かつ図20〜35に示される。制御回路106は、それによって、電気信号83を通して主光学系82の焦点を操作して、2、3フレーム後に、センサチップ84上の画像の焦点を合わせる。主光学系82は、好ましい実施形態においては、この分野ではよく知られているEOSファミリーの交換できる超音波のレンズである。

【0024】

露出中の真のthrough−the−lens(TTL)測光を遂行することが要求されるのであれば、露出情報は、焦点情報より更に迅速に計算されなければならない。このモードの動作において、センサチップ84上への光の積分は、所望の露出条件が達成されるまで続くことが可能である。その時、積分期間は終了し、画像は媒体102に格納される。好ましい実施形態においては、所望の露出条件の達成は、センサチップ84内の像面そのもので計算される。これは、更に十分に以下で説明され、かつ図10〜12に示される。信号87は、センサチップ84から制御回路106に露出条件を伝達する。制御回路106は、所望の露出条件の達成を示す信号87上の情報を受け取ると、信号85を通してセンサチップ84上での積分時間を終了させる。そして、露光がTTLフラッシュユニット108を用いて行われた場合には、この分野ではよく知られているように、フラッシュが制御回路106によって信号109を通して終了させられる。

【0025】

前述したように、センサチップ84として用いるのに適した光変換器の本発明を限定するわけではない例として、垂直色フィルタ多重フォトダイオード構成がある。以下、垂直色フィルタ多重フォトダイオード構成を詳細に説明する。

【0026】

図9に示したように、交互にp型及びn型領域が繰り返される6層の構造が形成され、第1の導電型の半導体基板200が底層として用いられていて、この中に、第1の導電型の拡散障壁埋め込み(implant)層202と、第2の反対の導電型の1つの井戸204とが配置されている。拡散障壁202は、基板で生成されたキャリアが、緑のフォトダイオードに向かって上方へ移動するのを防止する。そして、井戸204は、赤のフォトダイオードとしての検出器として動作する。この実施形態においては、第1の導電型の拡散障壁埋め込み層208を有する第1の導電型の第1のエピタキシャル層206が、半導体基板200及び基板の井戸204の表面上に配置され、第2の導電型の井戸210が、第1のエピタキシャル層206の中に配置されている。拡散障壁埋め込み層208は、第1のエピタキシャル層206の中で生成されたキャリアが、青のフォトダイオードに向かって上方へ移動するのを防止する。そして、井戸208は、緑のフォトダイオードとしての検出器として動作する。第1の導電型の第2のエピタキシャル層212が、第1のエピタキシャル層206及びその井戸210の表面上に配置されている。そして、第2の導電型のドープされた領域214(これは、低ドープドレイン埋め込み領域であってもよい)が、第2のエピタキシャル層212の中に形成されている。ドープされた領域214は、青の検出器を形成している。

【0027】

埋め込まれた緑の検出器210及び埋め込まれた赤の検出器204へのコンタクトが、深いコンタクトを介して行われている。埋め込まれた緑の検出器210のためのコンタクトは、第2のエピタキシャル層212を通して形成されていて、埋め込まれた赤の検出器204のためのコンタクトは、第2のエピタキシャル層212及び第1のエピタキシャル層206を通して形成されている。

【0028】

図9のハッチングされた領域は、この構造のp型及びn型の領域を造るために用いられた埋め込み領域の概略の位置を示している。破線216は、青い検出器214のための有効P(net−P)、及び、有効Nドーピングの間の概略の境界を定義する。同様に、破線218は、緑の検出器210のための有効Pと有効Nのドーピング間の概略の境界を示していて、これは、緑の検出器210へのコンタクトを形成している、第2のエピタキシャル層206の表面への、その垂直部分を有している。破線220は、赤の検出器204のための有効Pと有効Nのドーピング間の概略の境界を示していて、これは、赤の検出器204へのコンタクトを形成している、第2のエピタキシャル層206の表面への、その垂直部分を有している。

【0029】

ここに開示された6層構造の他の実施形態は、基板、基板に配置された1つ以上の井戸、1つ以上のエピタキシャル層、及び、1つ以上のエピタキシャル層に配置された1つ以上の井戸の中から選択された、層の様々な組み合わせを用いることが予想され、かつ、これを用いることによって実現されてもよい。

【0030】

また、上記のように、センサチップ84として用いるのに適した光変換器は、垂直色フィルタ多重フォトダイオード構成である。以下、光変換器及び光変換器を用いる方法について述べる。

【0031】

図10に、自動露出制御を組み込んだ高感度画素センサ230の一例の概略図を示す。フォトダイオード232は、(接地として示された)固定されたポテンシャルの供給源と連結されたアノードと、カソードとを有している。フォトダイオード232のカソードは、MOS Nチャネルバリアトランジスタ234のソースと連結されている。MOS Nチャネルバリアトランジスタ234のゲートは、BARRIERラインと連結されている。このBARRIERラインは、BARRIER制御ポテンシャルとされる可能性がある。この分野における通常の技術者であれば、記憶画素センサ230に、MOS Nチャネルバリアトランジスタ234を用いることが、いくらかの感度を犠牲にして、取捨選択可能であることは、分かるであろう。回路における他のトランジスタとは無関係に、画像の暗い領域において、感度(電荷−電圧変換利得)を上げるために、バリアトランジスタ234を追加することが可能である。MOS Nチャネルバリアトランジスタ234は、実質的に全てのフォトダイオードからの電荷を、高利得をもたらす第1のソースフォロアトランジスタ240のゲート容量にチャージして、そのゲート電圧を低下させ、更に、バリアトランジスタ234をオンにすることを可能にする。この後に、記憶画素センサ230は、(明るい領域のために)低利得モードで動作して、この中で、電荷が、フォトダイオードの容量と、ゲートの容量との両方をチャージする。

【0032】

フォトダイオード232のカソードは、MOS Nチャネルバリアトランジスタ234を介して光電荷積分ノード236(図10中では破線のキャパシタとして表されている)と連結されている。MOS Nチャネルリセットトランジスタ238は、光電荷積分ノード236と連結されたソースと、RESET信号がアサートされる可能性があるRESETラインに結合されたゲートと、リセットポテンシャルVRに結合されたドレインとを有している。

【0033】

光電荷積分ノード236は、第1のMOS Nチャネルソースフォロアトランジスタ240の本来のゲート容量を含んでいる。このトランジスタ240は、電圧ポテンシャルVSFD1に接続されたドレインを有している。電圧ポテンシャルVSFD1は、供給電圧V+(これは、例えば、技術に応じて約3〜5ボルトである可能性がある)に固定されていてもよいし、もしくは、以下で開示されるように、パルス化されていてもよい。MOS Nチャネルソースフォロアトランジスタ240のソースは、ソースフォロアトランジスタの出力ノード242を形成していて、電流源として動作するMOS Nチャネルバイアストランジスタ244のドレインと連結されている。MOS Nチャネルバイアストランジスタ244のソースは、固定された電圧ポテンシャル、例えば、接地と連結されている。MOS Nチャネルソースフォロアバイアストランジスタ244のゲートは、バイアス電圧ノードに接続されている。バイアス電圧ノードに現れる電圧は、MOS Nチャネルソースフォロアバイアストランジスタ244にバイアス電流を流す。この電圧は、固定されていても、パワーを節約するためにパルス化されていてもよい。MOS Nチャネルソースフォロアバイアストランジスタ244の使用は、任意である。このデバイスは、自動露出検出機能を実現するために、飽和レベルトランジスタと組み合わせて用いることができる。

【0034】

ソースフォロアトランジスタの出力ノード242は、容量性の記憶ノード246(図10中では、破線のコンデンサとして表されている)と連結されている。ソースフォロアトランジスタの出力ノード242は、MOS Nチャネル転送トランジスタ248を介して容量性の記憶ノード246と連結可能となっている。MOS Nチャネル転送トランジスタ248のゲートは、XFR信号がアサートされる可能性があるXFRラインと連結されている。MOS Nチャネル転送トランジスタ248は、記憶画素センサにおける任意の構成要素である。

【0035】

容量性の記憶ノード246は、第2のMOS Nチャネルソースフォロアトランジスタ250の本来のゲート容量を含んでいる。このトランジスタ250は、ソースフォロア−ドレイン(SFD)ポテンシャルに接続されたドレインと、ソースとを有している。第2のMOS Nチャネルソースフォロアトランジスタ250のソースは、MOS Nチャネル行選択トランジスタ254を介してCOLUMN OUTPUTライン252と連結されている。MOS Nチャネル行選択トランジスタ254のゲートは、ROW SELECTライン256と連結されている。

【0036】

第2のMOS Nチャネルソースフォロアトランジスタ250は、大きいデバイスであって、第1のMOS¥Nチャネルソースフォロアトランジスタ240の面積の10〜100倍のサイズのゲートを有していることが好ましい。回路の他のトランジスタ、すなわち第1のMOS¥Nチャネルソースフォロアトランジスタ240は、最小の長さ及び幅に近いサイズであることが好ましい。

【0037】

画素のサブセットをアドレスすることが可能なセンサチップ84のための設計を用いることによって、大きな利点が得られる。例えば、4番目毎の行における4番目毎の画素を連続してアドレスすることによって、ファインダの像のフレーム毎のスキャンアウト時間を16の率で短くすることが可能になる。

【0038】

以下、図11を参照すると、タイミング図が、(図10に示した)画素センサ10を使用する方法を示している。初めに、RESET信号が、ハイにアサートされる。MOS¥Nチャネルリセットトランジスタ238のドレインにおけるVRノードは、ゼロボルトから電圧VRにされる。この動作は、各フォトダイオード232のカソードに(MOS¥Nチャネルバリアトランジスタ234のしきい値よりは小さい)電圧ポテンシャルVRを印加することによって、アレイ中の全ての画素センサをリセットする。図11に示した高感度画素センサを動作させる好ましい方法によれば、電圧VRは、初めはロー(low)レベル(例えばゼロボルト)で、一方、アレイ中の全てのフォトダイオードのカソード電圧を、像の遅れを防ぐために迅速にそれらの状態を等しくするための低い値にリセットするために、RESETはハイ(high)である。次に、電圧VRが、予め定められた時間(好ましくは2、3ミリ秒のオーダー)、(例えば約2ボルトまで)上げられ、一方、RESET信号はまだアサートされていて、全ての画素センサにおけるフォトダイオードが、それらに結合されたMOS¥Nチャネルバリアトランジスタ234を通して、約1.4ボルトまで充電されることを可能にする。このトランジスタ234のゲートは、約2ボルトに保たれている。従って、積分ノードにおける黒レベルはVRに設定され、これは、MOS¥Nチャネルリセットトランジスタの容量性のターンオフ過渡現象のためには少し小さい。そして、フォトダイオードは、それぞれのバリアトランジスタのしきい値によって決められたような、それぞれの適切なレベルにリセットされる。この方法の利点は、それらのしきい値が、読み取られる黒レベルに影響を及ぼさないことである。リセットが終了して積分が開始された後にも、いくらかの電荷が、副しきい値条件によって、バリアを越えて、まだリークするであろう。しかし、それは、全ての画素について、ほぼ同じであるべきである。或いは、少なくとも、明るさのレベルの単調関数であるべきである。

【0039】

記憶画素センサの特に有利な動作によれば、バリアトランジスタ234及びリセットトランジスタ238は、同じサイズとされ、これにより、同じ電圧しきい値(Vth)を示す。RESET信号のアクティブレベルは、VRESET<VR+Vthとなるように選ばれ、より良い非線形性のトラッキングが達成される。

【0040】

RESET信号がディアサート(de−assert)されて光積分が始まると、電荷が光電荷積分ノード236に蓄積される。MOS¥Nチャネルバリアトランジスタ234が、わずかに導通しているので、フォトダイオード232のカソードの電圧を下げずに、(その電圧を下げることによって、)光誘導電荷が、そのチャネルを通して少しずつ流れて、光電荷積分ノード236をチャージする。これは、有利である。なぜなら、それが光電流によってチャージされるキャパシタンスを最小限にして、それによって感度(光子当たりのボルト)を最大限にするからである。

【0041】

この分野における通常の技術者であれば、MOS¥Nチャネルリセットトランジスタ238を、直接、フォトダイオード232のカソードに接続可能であることが分かるであろうが、そのような構成は、電圧VRがバリア電圧及びしきい値に対して正確にセットされることを必要とする。しきい値は変化する可能性があるので、これは、好ましくない。

【0042】

第1のMOS¥Nチャネルソースフォロアトランジスタ240のソースの電圧と、従ってその出力ノード242とは、そのゲート(光電荷積分ノード236)の電圧に従う。MOS¥Nチャネル転送トランジスタ248を用いる実施形態においては、図11に示したように、XFR信号は、リセット期間及び積分期間を通してアサートされていて、積分期間を終えるためにディアサートされる。XFR信号のローレベルは、転送トランジスタ248を完全にターンオフするために、好ましくはゼロまたは僅かに負の電圧、例えば約−0.2ボルトに設定される。

【0043】

画素センサを読み出すために、第2のMOS¥NチャネルソースフォロアトランジスタのドレインのSFDノード(図11中ではVSD2と表示されている)が電圧VSFDになるように駆動され、画素センサ230を含むアレイの行のためのROW SELECT信号がアサートされ、それによって出力信号がCOLUMN OUTPUTライン252を駆動する。VSFD2信号のアサートのタイミングは、図11に示したように、ROW SELECT信号がディアサートされた後までハイの状態を維持するべきであるということを除けば重要ではない。VSFD2が最初に立ち上がるのであれば、ROW SELECT信号の立ち上がりエッジにおける電圧の勾配を制限することは有利であるかもしれない。

【0044】

以下、図12を参照し、XFRトランジスタが存在しないならば、記憶ノードは、(好ましくはゼロまたは僅かに負の電圧、例えば約−0.2ボルトに)SFBIASを下げ、VRをローに設定し、そしてRESET信号をアサートすることによって、分離されてもよい。このシーケンスは、その負荷電流がターンオフされるとき、そのゲートの電圧を下げることによって、第1のソースフォロア240をターンオフし、それによって、その出力電圧を記憶する。

【0045】

図12に、VRの立ち下がりエッジ及びRESETの立ち上がりエッジが、終了(terminate)信号のすぐ後に続くことが示されている。これは、これらのトランジスタが、露出を終了するために、記憶ノードを分離するからである。図10においては、対応する遷移は、更に遅れて示される。なぜなら、XFRの立ち下がりが記憶ノードを分離すれば、それらは重要ではないからである。SFBIAS信号は、図12の場合にのみ立ち下げる必要があり、転送トランジスタがあるとき、バイアスは一定にすることができる。

【0046】

また、図12は、信号VSFD1がパルス化されていることを示している。ここに開示したように、VSFD1ノードは、常にハイの状態に保たれてもよいし、もしくは、図12に示したようにされてもよい。VSFD1は、パルス化されて、パワーを節約することができる。VSFD1がパルス化される実施形態において、終了(terminate)は、パルスの間に真の状態になる。RESETがハイになるまで、VSFD1はハイに保たれる。もしくは、転送トランジスタを用いる実施形態においては、XFRがローになるまで、VSFD1はハイに保たれる。

【0047】

第2のMOS¥Nチャネルソースフォロアトランジスタ250は、第1のMOS¥Nチャネルソースフォロアトランジスタ240より大きく、従って、そのゲート容量(容量性の記憶ノード246)も、それに応じて大きい。これは、画素センサ230にノイズ耐性を追加するという利点を提供する。なぜなら、所定の電圧変化を引き起こすために、光電荷積分ノード236を有する場合より多くの電荷が、容量性の記憶ノード246へ、もしくは容量性の記憶ノード246から転送される必要があるからである。

【0048】

図11及び12に示した制御信号は、従来のタイミング及び制御ロジックを用いて生成することができる。このために、タイミング及び制御ロジック回路258が図10に示されている。タイミング及び制御ロジック回路258の構成は、個々の実施形態によって変わるが、いずれにせよ、従来の回路構成であり、ひとたび個々の実施形態が選択されたら、個々の設計は、この分野における通常の技術者にとっては、図11及び12を試験することを含めても、ささいな仕事である。

【0049】

再び図10を参照し、別の実施形態による画素センサと共に用いる自動露出回路260が開示される。アレイ中の各画素は、MOS¥Nチャネル飽和レベルトランジスタ262を備えていて、このトランジスタ262は、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242に接続されたソースと、SAT.LEVELライン264に接続されたゲートと、全体電流合計ノード266に接続されたドレインとを有している。全体電流合計ノード266は、電流比較器268に接続されている。この分野における通常の技術者であれば、電流比較器268が、電圧源と全体電流合計ノード266との間に接続されるダイオード負荷または抵抗器を備えていて、電圧比較器の一方の入力を駆動するものであってもよいことが分かるであろう。電圧比較器のもう一方の入力は、所望の数の飽和した画素を表す電圧に接続される。もう一つの選択肢として、アナログ−ディジタル変換器が用いられて、比較がディジタル的に行われてもよい。

【0050】

バイアストランジスタ244が存在しさえすれば、飽和レベルトランジスタ262を用いて、飽和した画素センサからのバイアス電流を全体電流合計ライン上に流すことができ、それを、露出の間、何個の画素が飽和レベルトに達したかを調べるために、監視することができる。外部回路によって、飽和と判断するしきい値を制御することができ、また、単にそれをしきい値と比較する代りに、電流を測定することもできる。従って、この追加されたトランジスタ及び全体電流合計ラインによって、何個の画素センサが任意の特定レベルを越えたかを調べることが可能である。従って、しきい値(SAT.LEVEL)の素早い変更及び素早い測定(例えば、A/D変換器及びプロセッサへの入力によって)を実行することによって、露出の間の露出レベルの完全な累積ヒストグラムを得ることが可能である。この情報から、良好な露出レベルを、好ましい実施形態に用いた簡単なしきい値法を越えて、より複合的に決定することが可能である。

【0051】

バイアストランジスタ244が存在するとき、記憶ノードを分離するためには、タイミング信号によって、バイアストランジスタ244と第1のソースフォロア240との両方をターンオフする必要がある。転送トランジスタ248を設けることは、簡単であり、かつ記憶の完全性に関して有利である可能性がある。それは、1つのロジック信号による制御によって記憶ノードを分離することができる。また、同様の利点のために、バイアストランジスタなしであっても、転送トランジスタ248を基本回路に加えることができる。なぜなら、確実に第1のソースフォロアトランジスタ240をターンオフするには、Reset及びVR信号を統合することが必要になり、これは複雑であるが、それは、転送トランジスタ248によって除去することができる。

【0052】

動作において、SAT.LEVELライン44は、選択された光電荷飽和レベルに相当する電圧VSATになるように駆動される。光電荷の累算は、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242の電圧を下げるので、MOS¥Nチャネル飽和レベルトランジスタ262は、初めはターンオフされる。なぜなら、VSATにおけるそのゲート電圧は、ノード236の電圧より低いからである。光電荷積分ノード236における光電荷の蓄積が、その電圧をVSATより低くするまで、MOS¥Nチャネル飽和レベルトランジスタ262はオフを保つ(そして、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242と共通電位のMOS¥Nチャネル飽和レベルトランジスタ262のソースにおけるそれは、電圧VSATより1Vt低いレベルになる)。この時点で、MOS¥Nチャネル飽和レベルトランジスタ262はターンオンして、(バイアストランジスタ244に流れるバイアス電流より少ないか、もしくはこれに等しい)電流を全体電流合計ノード266から引き込み始める。

【0053】

この分野における通常の技術者であれば分かるように、アレイ中の他の画素センサも、それらのMOS¥Nチャネル飽和レベルトランジスタ262をターンオンするために十分な光電荷の蓄積を開始する。従って、ノード266から追加の電流を引き込み、更に、全体電流合計ノード266の電圧を低下させる。この分野における通常の技術者であれば分かるように、比較器268は電圧比較器であってもよく、その1つの入力は、全体電流合計ノード266に接続され、もう1つの入力は、選択された数の画素が飽和している(すなわち、それらのMOS¥Nチャネル飽和レベルトランジスタ262がターンオンされている)ときの全体電流合計ノード266の電圧に応じて選択された電圧VTERMに接続される。全体電流合計ノード266の電圧がVTERMに等しくなると、比較器268は露出終了(TERMINATE EXPOSURE)信号を生成する。これは、たくさんの方法のうちの1つによって、例えば、機械的なシャッタを閉じることによって、或いは、露出終了(end−of−exposure)信号(例えばXFR信号)を発して画素センサを制御することによって、露出期間を終了するために用いられる。露出終了(TERMINATE EXPOSURE)信号は、必要であれば、ストロボの閃光の発光を停止させるために用いることもできる。

【0054】

もう一つの選択肢として、A/D変換器270を全体電流合計ライン266に接続して、全体が合計された電流を表す電圧を、ディジタル値に変換してもよい。このディジタル値は、参照符号272で示したスマート自動露出アルゴリズムを用いて処理される。

【0055】

自動露出回路260は、ソースフォロアトランジスタ240のドレインへのVSFD1信号と、ソースフォロアバイアストランジスタ244のゲートに供給されるSFバイアス信号及び飽和レベルトランジスタ262のゲートに供給されるSAT.LEVEL信号のうちの1つまたは両方とを同時にパルス化することによって、パワーセーブモードで動作されるのが好ましい。そのようなモードにおいては、これらの信号のパルスが入力された時にのみ、自動露出検出電流が流れて、そのとき露出オーバーの検出が行われる。光積分の間のその他の時間には、各画素からの露出オーバー電流は流れないので、パワーが節約される。この動作モードが用いられると、自動露出回路260は、より良い信号対雑音比のために、より高い電流レベルで有利に用いられることが可能である。

【0056】

自動露出回路260の他の動作モードにおいては、アレイ中の全ての飽和レベルトランジスタ262のゲートにおけるSAT.LEVEL電圧が、ゼロから最高レベルまで掃引されて、アレイ中の全ての画素の状態の完全な累積分布を生じさせる。A/D変換器270が自動露出回路260に用いられるとき、この動作モードは最も有益である。オプションの転送トランジスタ248を用いる実施形態においては、このデバイスは、各測定サイクルにおけるSAT.LEVEL電圧の傾斜の前にターンオフされるべきである。或いは、追加のサイクルが、SAT.LEVEL電圧が低いときに実行されるべきである。これは、変化するSAT.LEVEL電圧で切られていない信号電圧を記憶するためである。この累積分布情報を用いる自動露出アルゴリズムの一例は、分布を分析して、逆光であるか否かによって場面を分類し、それに応じて、露出の間、SAT.LEVEL及びi−thresholdを異なる値に設定する。

【0057】

前述したように、大きな利点が、画素のサブセットをアドレス可能な、センサチップ84のための設計を用いることによって達成される。以下、センサチップ84内に組み込まれるアドレス指定ロジックを詳細に説明する。

【0058】

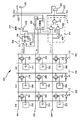

図14を参照すると、走査回路を用いた電子カメラ280のブロック図が示されている。電子カメラ280は、画素センサアレイ282、例えば、アクティブ画素センサアレイを備えている。画素センサアレイ282は、フレキシブルアドレス発生器回路284によって制御される。フレキシブルアドレス発生器回路284は、制御回路286によって制御され、これは、アレイ282から画素データを読み出す制御にとって必要な信号の全てを供給する。フレキシブルアドレス発生器回路284及び制御回路286は、画素センサアレイ282から完全な高解像度画像データを読み出して、そのデータを記憶システム288に格納するために用いられる。画素センサアレイ282は、ディジタルスチルカメラもしくはビデオカメラに用いるのに適した高解像度アクティブ画素センサアレイである。そのようなアクティブ画素センサアレイは、一般に、視野画面上に表示されるので、ユーザは、画像を見て、これを調節することができる。フレキシブルアドレス発生器回路284及び制御回路286は、同じシリコン上にセンサアレイ282として組み込まれてもよく、かつ、画素データを、画素センサアレイ282から生成された完全な画像のそれよりは低い解像度を有するファインダディスプレイに供給するのに用いられてもよい。

【0059】

図15に、図14のフレキシブルアドレス発生器回路284及び制御回路286を含む走査回路の詳細なブロック図を示す。走査回路の好ましい実施形態における主な構成要素が図15に示されている。アクティブ画素センサアレイ282は、N行及びM列の画素センサを有している。アクティブ画素センサアレイ282は、行選択ライン300及び列出力ライン302を介して、走査回路の残りの構成要素に接続されている。アクティブ画素センサアレイ282中の各行の画素センサに対して、1本の列選択ラインがあり、かつまた、アクティブ画素センサアレイ282中の各列の画素センサに対して、1本の列出力ラインがある。従って、図示したアクティブ画素センサアレイ282には、N本の行アドレスライン300と、M本の列出力ライン302とがある。

【0060】

行アドレスラインの信号は、行アドレス発生器306が駆動する行アドレスデコーダ304によって生成される。列ライン出力の選択は、列アドレス発生器310が駆動する列セレクタ308によって行われる。列セレクタ308は、この分野において知られているデコーダまたはその他のマルチプレクシング手段を備えていてもよい。行アドレス発生器306及び列アドレス発生器310は、一般的なカウンタと考えられ、制御回路312によって制御される。

【0061】

図15中の制御回路286については詳述しない。この分野における通常の技術者であれば、ここに開示された、選択されたイメージャーアレイの初期化及び制御要求に応じて、アクティブ画素センサアレイが、繰り返し初期化されて読み出されることを可能にする機能から、行及び列アドレス発生器306及び310の制御を容易に実施することができる。

【0062】

行アドレス発生器306及び列アドレス発生器310は、制御回路312の制御下で動作するロード可能なカウンタである。各カウンタは、開始アドレスをロードされ、次に、クロックが与えられて、増分Kずつのカウントを行い、停止アドレスに達し、この時、「停止に等しい(Equal to stop)」出力信号を制御回路に供給する。次に、カウンタは、開始アドレスにリセットされ、このシーケンスが再度開始される。行及び列アドレス発生器306及び310内のカウンタは、開始アドレスの値、停止アドレス、及びKの値の1つ以上のモードのためのセットを格納するレジスタを有している。制御回路312と、行及び列アドレス発生器306及び310とは、1つの行における各々の選択された列を通してクロックを供給するように構成されている。そして、行アドレス発生器をKずつインクリメントして、次に選択された行における各々の選択された列にクロックを供給する。

【0063】

行アドレス発生器からの「停止に等しい(Equal to stop)」信号は最後の行を示していて、制御回路312は、これ続いてセンサアレイの初期化を行い、これにより、各々の完全な行のサイクルが完了した後に、新しい像が取り込まれる。

【0064】

センサアレイの分野における通常の技術者であれば、他のタイミング信号及び遅延が、行間もしくは画像間に必要とされる可能性があることを認識しているであろう。そして、そのような遅延及び追加のタイミング信号を実現するため、及び、画像露出を同期させてカメラシステムの他の部分へ読み出すために、遅延素子や、その他のロジック及びタイミング素子を用いることができることを認識しているであろう。制御回路312は、本実施形態の重要な部分ではなく、一般に、センサアレイ及びフレキシブルアドレス指定回路と同じシリコン基板上には形成されない。図15に示したモードデータ(Mode Data)ラインは、モード定義データをカウンタのレジスタに格納するため、及び、任意の個々の時間に動作すべきモードを選択するための、一般的な経路を示している。各カウンタのための補数(complement)制御信号は、モードデータ(Mode Data)に含まれている。

【0065】

また、この分野における通常の技術者には明らかであろうが、フレキシブルアドレス発生器の停止検出機能は、取捨選択可能であり、それを実行する機能は、代替の実施形態において、いくつかの異なる方法で実現可能である。例えば、画像データをイメージャーから記憶システムに送る制御ロジックは、行及び列をカウントして、予め定められた量の画素データが送られたときに停止することができる。同様に、アレイから画素データを受け取るユニットも、行及び列をカウントして、予め定められた量の画素データが受け取られたときに停止するための信号をコントローラに送ることができる。これらの体系のどちらが用いられても、カウントまたはアドレス情報が、イメージャー集積回路まで、もしくはイメージャー集積回路からリアルタイムで送られる必要がないという利点が得られる。

【0066】

アクティブ画素センサアレイ282からの画像の、XあるいはY方向のいずれかにおける鏡像をとることが必要であれば、補数制御信号が用いられる。画像は、通常、色分解プリズムによって、3本の別々の色ビームに分割され、それぞれの個別の色ビームは、別々のアクティブ画素センサアレイへ送られる。そのようなプリズムは、他の2本の色分解ビームに対して鏡像となった1本の色分解ビームを生じさせる可能性がある。3本の色分解ビームが最終的な画像を形成するために再結合される前に、特定の色ビーム画像を他の色ビーム画像と同じ方向に戻すために、反転読み出しによる再ミラーリングが必要であるかもしれない。補数制御信号は、最大の行または列アドレスからカウントを減じることによって、行または列アドレスカウンタの画素センサアドレス指定方法を反転させる。イメージャーが2の累乗に等しいサイズを有している一般的な場合において、この減算は、「1の補数」として知られていて、これは各ビットの反転であり、特定のアクティブ画素センサアレイが、鏡像となった方式で読み出されるようにし、その結果生じる画像を所望の方向に戻す。

【0067】

制御回路312からロード(Load)信号を受け取った後に、行アドレス発生器306は、そのモードデータから、アクティブ画素センサアレイ282の中から選択されるべき、画素センサの最初の行アドレスをロードする。行アドレス発生器306にクロックが送られるたびに、それは、選択されるべき次の行アドレスを行デコーダ304に供給する。行アドレスカウンタ306は、個々のモードの画像解像度出力に対応する、いくつかの異なる行アドレス計算モードを保持するように設計されている。

【0068】

行アドレス発生器306は、選択的にアクティブ画素センサアレイ282の画素センサのある行を飛ばすために、KN毎のカウント(count−by−KN)体系を実行する。例えば、画素センサが飛ばされない詳細モードにおいては、KN=1であり、行アドレス発生器306は、行デコーダ300に、行を飛ばすように指示しない。中間及び最大ズームモードの両方においては、KN>1であり、行アドレス発生器306は、KNによって選択されるべき次の行のアドレスの計算をインクリメントする。行アドレス発生器306は、それぞれ計算された行アドレスを行デコーダ304に供給する。中間ズーム及び最大フレーム視野画面表示モードにおいては、アクティブ画素センサアレイ282上のある行は、アレイの読み出しの間に飛ばされる。

【0069】

選択されるべき各行アドレスは、行アドレス発生器306によって行デコーダ304に供給され、これは、この分野において知られているように、供給されたアドレスに基づいて、適切な行選択ライン300を選択する。行ラインを選択することは、選択された行ラインと結合した画素センサの選択ノードをアクティブにするために、信号を行ライン上に流すことに相当する。

【0070】

列アドレス発生器310も、行アドレス発生器306と同じ仕方で機能する。ひとたびロード(Load)信号を制御回路286から受け取ると、列アドレス発生器310は、そのモードデータから、アクティブ画素センサアレイ282から読み出されるべき最初の列アドレスをロードする。列アドレス発生器310は、KM毎のカウント(count−by−KM)体系を実行して、選択されるべき次の列のアドレスを計算する。そして、列アドレスカウンタ310は、列アドレスを列セレクタ308に供給する。列アドレス発生器310のアドレス指定方法によって、列セレクタ308は選択的にアクティブ画素センサアレイ282上の画素センサのある列を飛ばす。列アドレス発生器310は、異なるモードの画像解像度及び位置出力を考慮して、開始、KM、及び停止データのいくつかのセットを保持するように設計されている。

【0071】

列セレクタ308のいくつかの異なる実施形態が可能である。列セレクタ308は、列出力ラインに接続された列デコーダと、スイッチを介した画素値出力ラインとを備えていてもよい。スイッチは、列デコーダが、適切な列出力ラインをオンにすることを可能にし、その列から画素値出力ラインに所望の画素センサ出力値を送る。もう一つの選択肢として、列セレクタ38は、列出力ラインに接続される2進樹(binary tree)列セレクタを備えていてもよい。

【0072】

図16は、走査回路によって実行される様々な画素センサ選択モードのために、画素センサ選択体系を実行する好ましい方法を示すフローチャートである。このフローチャートにおいて、現在の行アドレス番号は、nとして与えられ、現在の列アドレス番号は、mとして与えられる。このロジックは、KN毎カウント(count−by−KN)行スキップ体系、及び、KM毎カウント(count−by−KM)列スキップ体系を実行する。読出しは、Nstart行及びMstart列から始まり、Nstop行及びMstop列で停止する。

【0073】

まず、ステップ320で、走査回路は、最初の行アドレス番号を初期化して、選択されたn=Nstartにする。ステップ322で、走査回路は、最初の列アドレス番号を初期化して、選択されたm=Mstartにする。ステップ324で、走査回路は、画素センサ(n、m)を読み出す。走査回路は、現在読み出している行における最後の所望の列に達したかどうかをチェックする。ステップ326で、走査回路は、m=Mstopであるかどうかを調べる。ノーであれば、走査回路は、ステップ328で、m=m+KMをセットして、列アドレス番号のカウントをインクリメントする。走査回路は、それからステップ324に戻る。イエスであれば、走査回路は、ステップ330に進む。

【0074】

ステップ326で、m=Mstopが真であったならば、ステップ330で、n=Nstopかどうか、すなわち行カウントが最後の所望の行に等しいか否かを調べる。ノーであれば、行カウントは、ステップ332で、n=n+KNにセットされる。走査回路は、それからステップ322に戻り、ここで、列アドレスをMstartに再初期化して、次の行の中から画素センサを選択し続ける。イエスであれば、全ての所望の画素センサは読み出されたので、画素センサ読出しは、ステップ334で終了する。

【0075】

各画素センサアレイ読出しモードは、Nstart、Mstart、Nstop、Mstop、KN及びKMの異なる値を有している。高解像度部分画像表示モードにおいては、ユーザは、Nstart及びMstartを選択する。このモードは、画素センサを全く飛ばさないので、KN及びKMは、双方共に1に等しい。Nstop及びMstopは、アクティブ画素センサアレイのサイズに対する視野画面(viewscreen)のサイズによって決定される。走査回路は、任意に選択された開始位置から、もはや画素センサを利用可能な視野画面のスペース上に表示させることができなくなるまで、順次にアクティブ画素センサアレイから画素センサを読み出す。

【0076】

最大フレーム視野画面表示モードにおいては、画像全体が、視野画面上に表示されるので、Nstart及びMstartは、双方共にゼロに等しくてよい。N行M列のアクティブ画素センサアレイであれば、Nstop及びMstopは、各々、N及びMよりは小さい、KN及びKMの最も大きい倍数にセットされるので、ゼロからのKN及びKM毎のカウントは、正確に停止値に達する。

もう一つの選択肢として、簡単な等しいことの検出器よりむしろ、ディジタル大きさ比較器を用いてもよい。これによれば、停止値としてN−KN及びM−KMを用いることができる。KN及びKMは、視野画面サイズに対するアクティブ画素センサアレイのサイズの比率に基づいて決定される。

【0077】

中間ズームモードにおいては、Nstart及びMstartは、ユーザによって任意に選択される。KN及びKMは、高解像度部分画像表示モードと、低解像度最大フレーム視野画面モードとの中間の、視野画面画像解像度を生成するように選択された、予め記憶された値とされる。Nstop及びMstopは、視野画面のサイズと、KN及びKM値とによって決定される。走査回路は、KNずつ行をカウントし、かつKMずつ列をカウントして、順次にアクティブ画素センサアレイから画素センサを読み出す。アクティブ画素センサアレイの読出しは、任意に選択された開始位置から始まり、もはや画素が視野画面上に表示されることができなくなるまで続く。

【0078】

図16に示した画素センサアドレス指定方法は、x−y行列状に配列された行及び列の画素センサから成るアクティブ画素センサアレイのために設計されている。このx−y座標系の行列は、アクティブ画素センサアレイの現時点での好ましい実施形態であるが、図示した画素センサ選択方法は、また、異なる座標系を用いる行列にも適用することができる。

【0079】

行アドレス発生器306と列アドレス発生器310との両方の実例となる実施形態のための構成要素を図17に示す。図17は、フレキシブルアドレスカウンタ340の1ビットスライスを示す概略図である。フレキシブルアドレスカウンタ340に使われるビットの総数は、アクティブ画素センサアレイのサイズによって変わる。画素センサアレイのサイズが大きければ大きいほど、より大きい最大行及び列アドレスのカウントを必要とするので、追加のフレキシブルアドレスカウンタのビットを必要とする。

【0080】

フレキシブルアドレス発生器340は、3つのグループのアドレス選択パラメータを記憶するために3つのグループのレジスタを備えている。モードOは、レジスタグループ342によって生み出され、モード1は、レジスタグループ344によって生み出され、モード2は、レジスタグループ346によって生み出される。各レジスタグループは、3つのレジスタビットと、3つのCMOS伝送ゲートとを含んでいる。モードOに対応するグループ342は、レジスタビット348、350及び352と、CMOS伝送ゲート354、356及び358とを含んでいる。モード1に対応するグループ344は、レジスタビット360、362及び364と、CMOS伝送ゲート366、368及び370を含んでいる。モード2に対応するグループ346は、レジスタビット372、374及び376と、CMOS伝送ゲート378、380及び382を含んでいる。レジスタに格納されたモードO、モード1及びモード2のデータ間の選択は、それぞれ、モードO、モード1及びモード2制御ライン384、386及び388を用いて行われる。

【0081】

この分野における通常の技術者であれば、図17に示した3つの異なるレジスタグループが、単なる例であると認識するであろう。フレキシブルアドレス発生器340は、走査回路の個々の画素センサ選択モードに応じて、どのような数のレジスタグループを備えることも可能である。

【0082】

各一群の画素センサアドレス選択モードに対応する各レジスタグループは、個々のカウントシーケンスのために、Start、K及びStop値を保持している。これらの値は、アドレス指定カウント体系の開始アドレス値(Start)をセットするため、画素センサアドレスのカウントをインクリメントする増分値(K)をセットするため、及び終了指示(Stop)のための比較を行うために、カウンタに入力を提供する。それぞれの個々のモードにおいて、個々の画素センサアドレスカウント体系が生み出される。各々のカウントシーケンスモードのためのレジスタは、この分野において知られているような従来の手段によってロード可能なので、それらの値は、開始位置及びユーザによって選択された表示(viewing)モードに応じて変更することができる。

【0083】

開始(Start)値は、レジスタビット352、364及び376に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、開始(Start)値をライン390上に送り出す。K値は、レジスタビット350、362及び374に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、K値をライン392上に送り出す。停止(Stop)値は、レジスタビット348、360及び372に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、停止(Stop)値をライン394上に送り出す。

【0084】

図14に示した制御回路286は、図17に示したフレキシブルアドレス発生器340に、ロード(Load)、クロック(Clock)及び補数(Complement)信号を供給する。Load信号396によって、カウンタ状態フリップフロップ398は、選択されたモードから供給されるライン390上のStart値にセットされる。Clock信号400は、フレキシブルアドレス発生器の状態変化の同期化をもたらす。

【0085】

Clock信号400によって、加算器402の和出力、現在のカウントの増分(plus)Kは、次のカウンタの状態としてフリップフロップ398に格納される。カウンタ状態フリップフロップ398がクロックの進行によってインクリメントすると、それは、フリップフロップ398内の現在の値を停止チェック404に供給する。停止チェック404は、1つのインバータ406と、3つのNANDゲート408、410及び412と、ANDゲート414とを含んでいる。停止チェック404は、フリップフロップ398に格納された現在の値を、ライン394上の停止(Stop)値と比較する。フリップフロップ398に格納された現在の値が停止(Stop)値に等しいとき、Equal−Inライン422がアサートされ、停止チェック404からの出力は、Equal−Outライン416をアサートする。

【0086】

図17に示したフレキシブルアドレス発生器340はリップルカウンタであり、より詳細にはリップルキャリーアキュムレータである。リップルカウンタは、この分野においてよく知られている。このデバイスは、一般にリップルカウンタと呼ばれている。なぜなら、各々の上位ステージが、正当な結果を生み出すために、先行する下位ステージから送られるデータを受け取るからである。図示したリップルカウンタは、ここに開示された走査回路のための好ましいカウンタの実施形態であるが、他のタイプのディジタルカウンタが、フレキシブルアドレス発生器340のカウント機能を実現するために用いられてもよい。

【0087】

フレキシブルアドレス発生器340の各々のビットスライスは、バイナリ全加算器(binary full adder)402を備えている。全加算器402は、3つの入力、すなわち、A、B、及び、先行する下位ステージからのキャリー入力(carry−in;Ci)を有している。また、全加算器402は、2つの出力、すなわち、結果としての和S、及び、次の上位ステージへのキャリー出力(carryout;Co)を有している。入力Aはライン392上のK値からとられる。キャリー入力Ciはライン398からとられ、キャリー出力Coはライン420上に送り出される。

【0088】

フレキシブルアドレスカウンタの先行する下位ステージからの入力リップルequal−to−stop信号(Eqi)は、ライン422を介して伝送される。停止チェック404の出力、及び、入力リップルequal−to−stop信号(Eqi)422は、ANDゲート414に入力される。ANDゲート414は、出力リップルequal−to−stop信号(Eqo)を生成して、ライン416上に送り出し、これは、フレキシブルアドレス発生器340の次の上位ステージに入力される。Eqi422及びEqo416信号は、フレキシブルアドレスカウンタ340のいくつかのビットスライスを相互接続しているので、最上位ステージからのEqoは、カウンタの全ビットが停止値に一致したことを意味する。ただし、最下位ステージのEqiは、ロジックの1に結線されているものとする。

【0089】

Complement信号424は、フレキシブルアドレス発生器340によって生成されるカウントシーケンスを逆転させるために、マルチプレクサ426におけるフリップフロップ398からの出力信号の補数の使用を開始させる。出力アドレスビット(Ai)428は、所望の行または列アドレスを求めるために、フレキシブルアドレス発生器340の他の全てのビットスライスの出力アドレスビットと結合される。この最終行または列アドレスは、それぞれ、次の所望の画素センサの行または列アドレスを選択するために、行デコーダまたは列セレクタに送られる。

【0090】

追加の柔軟性を提供するために、カウンタをインクリメントするために使われるK値を、整数ではない値に設定することもできる。例えば、2つの追加のビットスライスを、K値に用いることができ、これは、全ての開始、K、停止及びアドレスの分解能を、1/4画像単位にすることを可能にする。カウンタ内では、余分の下位2ビットがに含まれているが、デコーダへ向かう途中で廃棄される。最大フレームを、所定のディスプレイサイズに、より近くなるように合わせることを可能にする、この例の式は、以下の通りである。

K=(1/4)*ceiling(4*max(N/Vr,M/Vc))

これは、Kレジスタに、整数に相当するビットをロードすることを意味する。

ceiling(4*max(N/Vr,M/Vc)).

【0091】

他の2の累乗への一般化は、この分野における通常の技術者にとって明らかであり、上記の式における「4」は、2jによって置き換えられる。ただし、jは小数ビットの精度である。

【0092】

カウンタに含ませることによって、余分の2ビットは、ズーム機能の細粒子(fine−grained)制御を可能にする。例えば、Kが2.25であるようにプログラムされれ、start=1であれば、カウンタは、1、3.25、5.5、7.75、10、12.25、14.5、16.75、19等のアドレスを生成する。このカウンタシーケンスは、1、3、5、7、10、12、14、16、19に切り捨てられ、通常は2ずつジャンプするが、4回に1回は3ずつジャンプし、2.25の平均ジャンプをもたらす。このような追加の小数ビットを用いると、K値を1より小さい値にすることも可能であり、この場合には、行及び列を複数回読み出すことが可能なタイプのイメージャーのために、画素反復によるズームインモードが可能である。

【0093】

同様に、KNまたはKMが双方共にゼロに設定された場合に、1つの行または1つの列を、画面を満たすために反復することができるが、停止検出機能が、これらのモードで働かないことは、この分野における通常の技術者にとっては明らかである。

【0094】

以下、図18を参照すると、単純化された概略図が、図17のフレキシブルアドレス発生器の複数のビットスライス340から形成される、一例としてのnビットフレキシブルアドレス発生器を示している。図18に示したフレキシブルアドレス発生器の2つの下位ビットスライスは、2つのオプションの小数アドレスビットを有しているが、それらのアドレス出力208は、ここに開示されたように、使用されない。

【0095】

図18は、フレキシブルアドレス発生器を作り上げている個々のビットスライス間の相互接続の全てを示している。図18の左側の制御ラインには、図17における、それらに対応するものと同じ参照符号が付されている。更に、Dclock制御ライン430、及び、データ入力シリアルデータ入力ライン432が、図18に示されている。これらのラインは、この分野で良く知られている従来の直列の方法で、データを、モードO、モード1及びモード2レジスタ342、344及び346にロードするために使われる。データ入力構造が、図18に示したシリアルデータ入力ライン432の代りに、パラレルデータ入力バスとしても実現可能であることは、この分野における通常の技術者であれば認識するであろう。

【0096】

NまたはM或いはその両方が2の累乗に必ずしも等しくないサイズを有するアレイも、用いることができる。図19は、例えばN=80であっても役に立つ、一例としての実施形態の単純化された概略図である。このNのサイズは、64と128(それぞれ、6と7アドレスビット)の間にある。従って、アドレス発生器は、7アドレスビットを必要とする。

【0097】

図19に、フレキシブルアドレス発生器の7ビットスライス全てのためのフリップフロップ及びマルチプレクサが示されている。フリップフロップには、参照符号398−0から398−6までが付され、マルチプレクサには、参照符号426−0から426−6までが付されている。それぞれの場合において、参照符号の接尾部は、図19における回路の構成要素が関連しているアドレスビットを示している。

【0098】

図19に示した、アドレスビット0から3までの、フリップフロップとマルチプレクサとの間の接続は、図17のビットスライスに示したものと同様である。フリップフロップ398−4、398−5及び398−6と、それぞれのマルチプレクサ426−4、426−5及び426−6との間の接続は、79の最大アドレスに対して補数化(complementation)を実行するために、図18に示したようになされる。特に、マルチプレクサ426−4の入力は、双方共にフリップフロップ398−4のQ出力に接続されている。マルチプレクサ426−5の2番目の入力は、XORゲート434によって駆動され、その2つの入力は、フリップフロップ398−4及び398−5のQ出力からとられる。マルチプレクサ426−6の2番目の入力は、ORゲート436及びXORゲート438によって駆動される。ORゲート436への2つの入力は、フリップフロップ398−4及び398−5のQ出力からとられ、XORゲート438への2つの入力は、フリップフロップ398−6のQ出力、及び、ORゲート436の出力からとられる。

【0099】

上述した回路は、127−(A+48)または79−Aの二進演算、48を加算する追加ロジック、補数マルチプレクサ426−4、426−5及び426−6に入る下側の経路における反転を実行する。図19の回路は、補数化を有するチャネルにおける別々のSTART値の必要性をなくすが、そのような回路は、同様に、予想されるものである。

【0100】

以下、本発明で用いるための焦点位置を計算する適切な方法を更に詳細に説明する。

【0101】

簡単な焦点調節は、ぎざぎざを最大にするように、カメラを調節するはずである。その結果、元の像内のくっきりと焦点が合ったエッジは、階段状のぎざぎざにエイリアシングされる。画像の任意の領域において、特定の深度で、最良の焦点(すなわち最高のシャープさ)は、最大のぎざぎざ(すなわち最大量の局所的変化または表示におけるコントラスト)と一致する。しかしながら、その効果は微かであり、目で見て最大にするのは難しい。

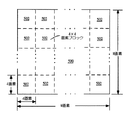

【0102】

サブサンプリングは、一般に、n番目毎の行からn番目毎の画素の値をとることによって行われる。もしくは、図20に示したように、元のNxM画素アレイ500を構成する全ての隣接するnxn画素ブロック502のうちの1つの特定の位置から画素値をとることによって行われても同じである。これは、また、水平及び垂直スケールが同じように減少されたサブサンプル画像をもたらす。図20に示した例から、nxn=4x4の場合には、どの画素を画素のnxnブロックの代表に選ぶかのn2=16通りの選択があることが分かる。各々のnxnブロック中の特定の全く同じ位置の画素の選択は、元の画像の特有の一様にサブサンプリングされた表現をもたらす。4x4ブロック内での各々の特定の画素位置によって、別々の、しかし同じように効果的な、高解像度画像の減少された解像度表現が得られる。

【0103】

前記で示したこと、すなわちn2通りの画素位置の中から代表の画素位置として1つを選択することによるサブサンプリングを利用する改良された焦点調節方法は、n2通りの別々で有益な一様にサンプリングされた画像が、サブサンプリングによって作成されることを可能にする。n2通りのサブサンプリングされた画像のうちの全て、または、いくつかを順次に表示することによって、その結果として生じる動的な表示は、周期的なパターンの動画化されたぎざぎざをもたらし、それは、より多くの元の画素データを表示する。周期的なパターンは、全体の置換にわたる置換の閉じられたサイクルと一致し、それは、表示されるサンプル間の間隔より短い。この動的な表示は、生き生きしたファインダ表示をもたらし、これは、データフィールド全体にわたる焦点調節を、反復して表示される静的な1つのサブサンプリングされたフレームに焦点を合わせることよりも容易にする。これは、人間の目が、画像の非常に小さい一時的な変化に対して、すばらしく敏感であることによる。従って、異なるサンプル画素位置を選択することは、低い空間周波数成分よりも、エイリアシングされた(aliased)画像成分に対して、はるかに大きい視覚的な影響を与える。

【0104】

どのサブサンプリング体系が、焦点調節のために最も効果的な周期的パターンを生み出すかを決定するために、様々な周期的パターンが調査された。人間の視覚は3から5ヘルツ(Hz)の周波数領域でのちらつきに対して最大の感度を持っていて、かつ、画像取り込み及び表示の速度は1秒当たり12から30画像の範囲にあるので、3から8の範囲の削減率が、ちらつきが強められた画像をもたらし、これは、3から5Hzの好ましいちらつき速度の範囲内であるか、或いは、これに近い。

【0105】

好ましいサブサンプリング体系は、同じに規定された距離毎に水平及び垂直に分離される画素の選択に帰着する。従って、その結果として生じる水平及び垂直方向のスケールの変更は同じである。図21〜23に、適切なサブサンプリング体系の例を示す。その中で、図21及び22においては、3x3画素ブロック502の9画素の中から1画素が選択され、図23においては、4x4画素ブロック502の16画素の中から1画素が選択される。図21において、画像は、各3x3ブロック502の画素1からスタートして、順次、サンプリングされ、そして、順次、時計回りに、残っている画素位置2〜8のために、シーケンシャル画像フレーム500の各3x3ブロック502が再度サンプリングされる。このシーケンスは周期的なので、このシーケンスは、8表示フレーム毎に繰り返される。これによって、フリッカ(ちらつき)速度は、表示フレーム速度の1/8になる(例えば、1秒当たり12〜30フレームのフレーム速度に対して1.5〜3.75Hz)。図23のサンプリングパターンは、このシーケンスを繰り返す前に、シーケンシャルフレーム500中の各3x3ブロック502に対して4つの画素位置(1〜4)を通るシーケンスである。これによって、フリッカ速度はフレーム速度の1/4になり、一般に、3〜7.5Hzのフリッカ速度になる。同様に、図23に示したパターンは、繰り返しの前に、各4x4ブロック502の16画素のうちの1画素を、画素位置1〜4からサンプリングする。従って、フレーム速度の1/4に等しいフリッカ速度が生成される。その結果生じるフリッカ速度は、一般に、3〜7.5Hzの範囲内になる。好ましいサブサンプリングパターンは、3x3または4x4画素ブロックにおいて生成される4もしくは8の個々のオフセットの周期的なパターンであるので、オフセットは、4画素の小さい正方形パターン内を動くか、もしくは、8画素の大きい正方形パターン内を動く。図21及び22では、時計回りのサブサンプリングシーケンスが用いられているが、反時計回りのシーケンス、または、選択された画素位置による、いかなるシーケンスであっても、エイリアシングされた画像の要素の所望の動画を生成するために用いることができることに注意すべきである。

【0106】

図24−30に、サブサンプリングによって作られる周期的な画像シーケンスと、電子ファインダ上の表示との例を示す。図24には、画像フレーム500の一部分が示されている。各最高解像度フレーム500は、3x3画素ブロック502を用いてサブサンプリングされるべきである。4つのサブサンプル画像を生成するために用いられるべき各画素ブロック502内での画素の位置には、1から4までの符号が付されている。網掛けにされた画素は、ディジタルカメラのフォトセルアレイによって生成された個々のサンプリングされた画像内の鋭い輝度エッジを表している。行及び列座標、(r, c)は、それぞれ、各画素ブロックを識別している。もし(1〜4のうちの)1つの画素位置が、減少された解像度画像503を生成するために、図24の全ての画素ブロック502内で使われるならば、3対1のスケールで減少された個々の画像が、各々の4つの画素位置に対して作成される。従って、図25〜28に、それぞれ、サンプルリング画素位置1から4に応じてサブサンプリングされた画像を示す。図25〜28の行及び列のための指標は、サブサンプリングされる画素がとられる図24の画素ブロック座標と一致する。図25〜28の4つのサブサンプリングされた画像の全てが、順次、表示されるならば、図29の画像が生じ、これは、表示フレーム速度の1/4のフリッカ速度を持つ。図29における、結果として生じた画像505の相対的なぎざぎざもまた、増加する。なぜなら、縮小された(scaled)サブサンプル画像内での1画素の不連続性は、元の画像内での3画素の不連続性に対応するからである。図29における網掛けの程度(degree)は、重ねられたサブサンプル画像のセットにおける網掛けされた画素の数による強度の変化を示している。図30に、フレーム間隔とサンプル画素番号との両方の関数として選択された画素(0, 6)、(0, 7)、(1, 2)及び(1, 3)の明−暗(もしくはオン−オフ)の時間履歴を示す。そこから、4フレーム間隔のフリッカ期間が生成されることが分かる。

【0107】

本発明のファインダ画像を、対応するフレームを平均化する従来技術の方法のそれと区別する、重要な視覚的な特徴は、動き及びフリッカの使用であり、これは、シャープに焦点が合う画像領域において、容易に明らかになる。

【0108】

上記の記述は、本実施形態の説明を明瞭にするための具体的な例にすぎない。例えば、サブサンプリングは、3対1及び4対1の倍率(或いは9及び16の削減率)に限られていたが、これは適切ではないかもしれない。なぜなら、ディジタルカメラの解像度と、ファインダの解像度との間の特定の差異が、他の倍率を必要とするかもしれないからであり、それは、整数ではない減少率を含んでいてもよい。しかしながら、上述した原理は、一般的な整数ではない場合を受け入れるように、容易に適合させることができる。

【0109】

例えば、2.75という整数ではない解像度減少率について考える。小数画素は、最高解像度画像には存在しないので、図24の画素アレイ500を2.75x2.75画素ブロック502に分割することはできない。図31は、いかにして、この方法を整数ではない場合に応用するかを示す表である。列Aは、一連の一定の水平及び垂直画素アドレス(10進数)であり、ここでは、小数画素が用いられれば、画素ブロックのエッジが置かれる。列Bは、バイナリコード化された列Aの等価値である。列Cは、列Bの切り捨てられたバージョンであり、ここで、列B項目の小数部が落とされるので、列Bの整数近似が生じる。高解像度画像の画素アレイのサイズが増加すると、平均画素ブロック間隔は、漸近的に所望の整数ではない間隔に近づく。ほぼ一定のサブサンプリング間隔のために、画像のほぼ一定の水平及び垂直スケーリングが生じる。

【0110】

図32に、図31の列Cの値を用いた結果を示す。最高解像度画像アレイが、2.75x2.75の平均削減率のサブサンプル画像を生成するのに適した割合で、3x3、3x2、2x3及び2x2画素ブロック502に分割されていることが示されている。(列Bの値が切り捨ての前に丸められたならば、大きいサイズの画像アレイのための画素ブロックサイズの分配は、同じであったであろう。従って、好ましい実施は、切り捨ての前に丸めることを含まない。)

【0111】

各画素ブロック内での表示されるべき画素の位置は、好ましくは、全ての画素位置が最も小さいもの(図32の例では2x2)を含む全ての画素ブロック内にはめ込まれるように選択されるべきである。結果として、全体の置換にわたる置換の閉じられたサイクルは、サンプル間の最小間隔より短くなる。シーケンシャルな表示のために選択される画素位置の数は、フリッカ速度を決定する。例えば、図32に、4つの特有の画素位置が、各画素ブロックに対して示されているので、選択された特有の画素位置に対応する各サブサンプル画像が、フリッカ期間の間に1度、表示されるならば、フリッカ速度は、フレーム表示速度の4分の1になる。フリッカ期間は、特有の画素位置の数を増やすことによって、もしくは、フリッカ期間の間に1度より多くの回数、1つ以上の特有の画素位置をサンプリングすることによって、長くすることができる。

【0112】

図32における破線の境界504は、サンプルは、等しいサイズの正方形のブロックからとられるが、これらのブロックは、それらが同等でないブロック502のサブブロックであるので、必ずしも隣接していないことを示している。

【0113】

図33は、画素の座標(アドレス)を決定するための好ましい方法600のフローチャートであり、これは、所定の整数もしくは整数ではない解像度減少率mを達成するために必要となる。ステップ602で、初期サンプル座標Y=Y0をセットする。ステップ604で、X=X0をセットする。ステップ606で、座標Xint、Yintにおける画素値が、高解像度画像から読み取られる。ここで、添字はフロア関数(floorfunction)すなわち整数部分であることを示す。ステップ608で、次の恐らくは整数ではない水平アドレスが、その以前の値及びmを用いて計算される。ステップ610で、Xが水平画素範囲を越えていないと判断されれば、このプロセスはステップ606に戻る。さもなければ、ステップ612に進み、次の恐らくは整数ではない行アドレスYが計算される。ステップ614で、Yが高解像度の限界における行の限界より小さいと判断されれば、このプロセスはステップ606に戻る。さもなければ、このプロセスは終了し、サブサンプリングが完了する。

【0114】

初期画素位置(X0, Y0)の選択されたセットに対して、このプロセスを繰り返すことによって、方法700を用いて、表示のための減少された解像度画像の周期的なシーケンスを生成することができる。

【0115】

図34は、ディジタルカメラ700のブロック図であり、低解像度ファインダディスプレイ704上への表示のために高解像度画素センサアレイ702をサブサンプリングする走査回路を用いていて、それは、ここに開示された方法に従って用いることができる。フレキシブルアドレス発生器706によって生成されるアドレス及び制御信号は、画素センサアレイ702からの画素データの読み出しを制御するのに必要な信号の全てを供給する。フレキシブルアドレス発生器706は、記憶システム708における記憶装置のために、画素センサアレイ702から高解像度画像を読み出すために用いられる。また、フレキシブルアドレス発生器706は、ファインダディスプレイ704上への表示のために、画素センサアレイ702によって生成された高解像度画像をサブサンプリングするためにも用いられるので、取り込まれた画像は、ファインダ704の減少された解像度のディスプレイにおいて、焦点が調節されて合焦することができる。

【0116】

図35は、N行及びM列を有する図34のフレキシブルアドレス発生器と画素センサアレイとの間の関係をより詳細に示す、一例としてのブロック図である。フレキシブルアドレス発生器800は、行アドレス発生器802、行デコーダ804、列アドレス発生器806、列セレクタ808及びコントローラ810を有している。行アドレス発生器802及び列アドレス発生器806は、コントローラ810の制御下にあるロード可能なカウンタである。コントローラ810は、クロック信号、カウント間隔(倍率)m及び初期オフセットアドレス(X0, Y0)を行及び列アドレス発生器802及び806に供給し、行及び列アドレス発生器802及び806から状態信号を受け取る。画素センサアレイ812からのサブサンプル画像の読出しは、行アドレス発生器802及び列アドレス発生器806へのそれぞれの初期アドレスとしての初期オフセット座標(X0、Y0)のローディングで始まる。次に、列アドレスカウンタは、クロックが供給されて、mずつインクリメントされ、切り捨てられていない座標(X, Y)を生成し、このうちの整数部分ビットのみが、それぞれ行デコーダ804及び列セレクタ808に供給され、図34のファインダ704上への表示のために出力ライン814から読み出されるべき画素の行及び列が選択される。所定の行における最後のサブサンプリングされた画素が読み出されると、列アドレス発生器は、その行がサブサンプリングされたことを示すために、ラインEQをアクティブにする。行アドレス発生器802のカウンタは、次のY値を生成するために、mだけインクリメントされ、列アドレス発生器806は、X0にリセットされる。以上に述べた動作が、選択された列を読み出すために、繰り返される。最後の行及び列が読み出されると、走査完了信号(EQ)が、行及び列アドレス発生器802及び806からコントローラ810に送られる。コントローラは、新しいセットの規定された初期座標オフセットを用いて、このプロセスを初期化することによって、新しいサブサンプル画像の表示を生み出す。

【0117】

以上、斬新で有益な完全電子化カメラシステムを説明してきた。この中で、正確なthrough−the−lens自動焦点、自動露出、ファインダ及びフラッシュ制御が、カメラボディ内の部品を動かさずに実現され、全ての量は、直接、主センサチップ上の情報から導き出される。

【0118】

本発明の実施形態及び応用を、図示し、かつ説明したが、ここでの本発明の概念からはずれずに、上述されたものの多くの更なる修正が可能であることは、この分野に熟練した者にとっては明らかである。従って、本発明は、付加された請求項の精神を除いては、限定されるべきではない。

【図面の簡単な説明】

【図1】従来技術におけるディジタルカメラの一例の断面図である。

【図2】図1に示した従来技術におけるディジタルカメラに用いられる具体例としての電子制御システムのブロック図である。

【図3】従来技術におけるディジタルカメラの別の例の断面図である。

【図4】図3に示した従来技術におけるディジタルカメラに用いられる具体例としての電子制御システムのブロック図である。

【図5】従来技術におけるディジタルカメラの別の例の断面図である。

【図6】図5に示したものと設計が類似した従来技術におけるディジタルカメラの別の例の断面図である。

【図7】図5及び6に示した従来技術におけるディジタルカメラに用いられる具体例としての電子制御システムのブロック図である。

【図8】本発明によるディジタルスチルカメラの断面図である。

【図9】エピタキシャル半導体技術を用いた垂直色フィルタ画素センサを示す半導体の断面図である。

【図10】自動露出検出回路を組み込んだ一例としての金属酸化膜半導体(MOS)アクティブ画素センサの概略図である。

【図11】図10の画素センサの動作を示すタイミング図である。

【図12】図10の画素センサの動作を示すタイミング図である。

【図13】本発明のディジタルカメラに用いられるのに適した電子制御システムのブロック図である。

【図14】走査回路構成を用いた電子カメラのブロック図である。

【図15】アクティブ画素センサアレイのための走査回路の主な構成要素を示すブロック図である。

【図16】画素センサの選択のための行及び列アドレスカウンタ内で用いられるアドレスカウントロジックの方法を示すフローチャートである。

【図17】アクティブ画素センサアレイと結合している走査回路内で用いるための、一例としての代表的なフレキシブルアドレス発生器の1ビットスライスの概略図である。

【図18】複数の図17のフレキシブルアドレス発生器のビットスライスから形成されたフレキシブルアドレス発生器の単純化された概略図である。

【図19】アレイのサイズが正確に2の累乗に等しくないときに用いるための、フレキシブルアドレス発生器の一例としての実施形態の単純化された概略図である。

【図20】NxMの解像度の画像のために隣接する4x4の画素ブロックを用いるサブサンプリングを示す。

【図21】3x3の画素ブロックの中から選択される9画素のうちの1画素のサブサンプリングの一例である。

【図22】3x3の画素ブロックの中から選択される9画素のうちの1画素のサブサンプリングの別の例である。

【図23】4x4の画素ブロックの中から選択される16画素のうちの1画素のサブサンプリングの一例を示す。

【図24】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図25】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図26】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図27】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図28】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図29】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図30】減少された解像度の電子ファインダにおいて見られるような、サブサンプリングによって生成される周期的な焦点合わせ画像の例を示す。

【図31】整数ではない画素ブロックの座標を計算する方法を示す表である。

【図32】整数ではない解像度を減少させるための画像の画素ブロックへの分割を示す。

【図33】サブサンプル画像の生成に用いるための、画素アドレスを計算する方法を示すフローチャートである。

【図34】走査を用いるディジタルカメラのブロック図である。

【図35】アクティブ画素センサアレイのための走査回路の主な構成要素のブロック図である。

【符号の説明】

280 電子カメラ

282 センサアレイ

284 フレキシブルアドレス発生器

286 制御回路

288 記憶システム

290 ファインダディスプレイ

304 行デコーダ

306 行アドレス発生器

308 列セレクタ

310 列アドレス発生器

312 制御回路

【発明の属する技術分野】

本願は、2000年8月4日に出願された米国仮出願第60/222,810号に対する優先権を主張する。

【0002】

【従来の技術】

本願は、ディジタルスチルカメラに関し、特に、新しいタイプの完全電子化高解像度ディジタルスチルカメラに関する。

【0003】

図1に、最もシンプルな形の従来技術におけるディジタルスチルカメラを示す。図1の左側の場面からの光線10は、主光学系12によって、センサチップ14上に焦点が合わせられる。光学系12及びセンサチップ14は、光を通さないハウジング16の中に収容されていて、迷光がセンサチップ14上に入射することを防止していて、それによって、光線10によって形成される画像が劣化することを防止している。同じ場面からの別の光線18は、それらがカメラのユーザの目22によって見ることができるように、副光学系20によって焦点が合わされる。光を通さないバッフル24は、副光学系20からチャンバハウジングのセンサチップ14を分離している。図1に示した構成は、箱型のフィルムカメラのそれと同じであり、フィルムがセンサチップ14に置き換えられている。

【0004】

図1に示した従来技術におけるディジタルスチルカメラの一般的な電子システムを図2に示す。センサチップ14からの出力信号は、処理回路26によって処理され、記憶媒体28に格納される。センサチップ14は、電荷結合素子(CCD)または相補型金属酸化膜半導体(CMOS)のどちらのタイプのセンサでもよい。記憶媒体28は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路30は、センサチップ14、処理回路26、及び記憶媒体28を制御して動作させる信号を供給する。このタイプのカメラは、一般に低コストで固定焦点のシャッターを押すだけの種類のものであり、自動焦点メカニズムは持っていない。

【0005】

図3に、関連しているが僅かに洗練された従来技術におけるカメラの構成を示す。ここでは、ファインダの像は、反射面32及び34によって、主光学系12を通過する主光線10から得られ、そして、副光学系20によって、カメラのユーザの目22によって見ることができるように焦点が合わせられる。電子露出が要求されると、図示されていない機械系が、センサチップ14への直接的な光の経路から反射面32を旋回させる。図3の構成は、一眼レフタイプのフィルムカメラのそれと同じであり、ここでも、フィルムがセンサチップに置き換えられている。

【0006】

図4に、図3に示した従来技術におけるディジタルスチルカメラに用いられる一般的な電子システムを示す。センサチップ14からの出力信号は、処理回路26によって処理され、記憶媒体28に格納される。センサチップ14は、CCDもしくはCMOSタイプのどちらでもよい。記憶媒体28は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路30は、センサチップ14、処理回路26、及び記憶媒体28を制御して動作させる信号を供給する。

【0007】

このタイプのカメラは、対応するフィルムカメラ内で見いだされるのと同じ自動焦点及び自動露出メカニズムを用いている。自動焦点は、副次的なミラー及びセンサを用いて完成されるが、これらは、正確に並べられていなければならない。このタイプのカメラ設計の適切な概観が、サイエンティフィックアメリカンの2000年8月号に掲載されている。このような設計の注目に値する特性は、機械的複雑さであり、これは、ミラーを動かすことを必要としていて、かつ、迅速な動きの後に再び高い精度で位置決めされなければならない。これらの非常に正確な機械的メカニズムは脆く、そして温度変化の際に機能不全となる傾向がある。また、それらは、製造するのに多くの費用がかかる。

【0008】

図4に示した電子システムは、自動焦点及び自動露出のサブシステムを動作させるための、いくつかの構成要素を備えている。制御回路30は、焦点センサ36及び露出センサ38からの入力を受け取り、制御信号を生成して、これにより、アクチュエータ40への通電を行い、反射面32を旋回させ、かつ主光学系12のアパチャ及び焦点を制御する。制御回路30は、焦点及び露出のための制御信号を計算する際に、センサ14から得られる信号を利用せずに、これらの計算のためのセンサ36及び38に頼らなければならないことが分かる。従って、主イメージセンサチップ14とセンサ36及び38との偏差は、不十分な焦点、不十分な露出、或いはこれらの両方によって、直ちに媒体28に格納される画像の品位を下げるであろう。従って、ファインダ、自動焦点及び自動露出の問題に対して、主センサチップ14によって生成される情報を用いて、追加のセンサを必要としない、完全な電子化という解決策を見いだすことが望ましく、これにより、機械的複雑さ、及び、複数の部品の正確な位置合せが不要になる。

【0009】

図5に、第2の形の従来技術におけるディジタルスチルカメラを示す。図5の左側の場面からの光線50は、主光学系52によってセンサチップ54上に焦点が合わされる。図5に示していないが、図7に詳細に示す電子システムは、センサチップ54から電気信号を受け取り、フラットパネルディスプレイを駆動するのに適した電気信号を得る。このディスプレイは、一般的には、液晶タイプのものである。フラットパネルディスプレイからの光線は、カメラのユーザの目によって直接見られる。

【0010】

図6に、ディジタルスチルカメラに関連する設計を示す。図6の左側の場面からの光線50は、主光学系52によってセンサチップ54上に焦点が合わされる。図6には示していないが、図7に詳細に示す電子システムは、センサチップ54から電気信号を受け取り、ブラウン管68を駆動するのに適した電気信号を得る。ブラウン管68からの光線64は、それらがカメラのユーザの目62によって見ることができるように、副光学系66によって焦点が合わされる。図5及び図6のファインダシステムは、ビデオカメラに用いられるものと同じ形であり、これらの原理で動作するスチルカメラは、ユーザが露出ボタンを押したときに1フレームのみが記憶されるビデオカメラと見なすこともできる。図5及び図6に示した設計のカメラは、これらの特徴を組み込んだビデオカメラからよく分かるように、イメージセンサ54からの信号を用いることによる初歩的な自動焦点及び自動露出が可能である。しかしながら、そのような方法で達成可能な焦点及び露出制御の質は、極度に限られていて、高解像度スチール写真にとって必要な品質レベルのかなり下になる。

【0011】

図7に、図5及び6に示した従来技術におけるディジタルスチルカメラの電子システムを示す。センサチップ54からの出力信号は、処理回路70によって処理され、記憶媒体72に格納される。センサチップ54は、CCDもしくはCMOSタイプのどちらでもよい。記憶媒体72は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものでもよい。制御回路74は、センサチップ54、処理回路70、及び記憶媒体72を制御して動作させる信号を供給する。更に、処理回路70は、フラットパネルディスプレイ58またはブラウン管68のいずれかを駆動するのに適した出力信号を供給し、制御回路74は、フラットパネルディスプレイ58またはブラウン管68のいずれかを制御して動作させる信号を供給する。

【0012】

【発明が解決しようとする課題】

図1,2,3,4,5,6及び7に示した全ての部品及び構成は、この分野では良く知られていて、世界中のカメラメーカーから入手できる数百もの商品において具体化されている。いくつかの場合においては、これらの図に示した技術の組み合わせを、1つの製品の中から見いだすことができる。

【0013】

【課題を解決するための手段】

従来技術の欠点及び不利な点は、完全電子化高解像度ディジタルスチルカメラによって克服される。電子カメラシステムは、カメラと結合しているレンズシステムの焦点面における光軸の位置に配置された複数の画素を有する半導体センサアレイを備えている。各画素は、その上への入射光の関数である出力信号を生成する。センサ制御回路は、半導体センサアレイと連結されていて、カメラシステムのユーザからの入力に応じて半導体センサアレイ中の画素の動作を制御するためのセンサ制御信号を生成するのに適合している。半導体センサアレイからの2セットの画像出力信号を生成する回路が設けられている。センサ制御信号が第1の状態にあるとき、第1のセットの画像出力信号は、第1のセットの画素における光の強度を表していて、センサ制御信号が第2の状態にあるとき、第2のセットの画像出力信号は、第2のセットの画素における光の強度を表している。第1のセットの画素は、第2のセットの画素より多くの数の画素を含んでいる。記憶媒体は、センサアレイと連結されていて、センサ制御信号が第1の状態にあるとき、第1のセットの画像出力信号の表現(representation)を格納するのに適合している。ディスプレイは、センサ制御信号が第2の状態にあるとき、第2のセットの画像出力信号を表示するのに適合している。

【0014】

1つのカメラシステム内で、第1のセットの画素は、アレイ中の画素の大多数であり、第2のセットの画素は、アレイ中の画素の予め設定された一部分であり、これは、アレイ中の画素の合計の半分未満である。アレイは、画素の複数の行及び列として配列され、第2のセットの画素は、少なくともアレイのM列毎の画素の大多数、及び、少なくともアレイのN行毎の画素の大多数を含んでいる。ここでM及びNは1より大きい。MとNは、お互いに等しくてもよい。

【0015】

本発明の他の特徴によれば、半導体センサアレイは、CMOSセンサアレイであり、垂直(vertical)色フィルタCMOSセンサアレイであってもよい。記憶媒体は、半導体メモリアレイであることが好ましい。また、ここに開示されたカメラシステムは、合焦信号を用いて焦点を合わせることができるレンズシステムを備えていてもよく、かつ、センサ制御信号が第2の状態にあるときに、画像出力信号から光の合焦の質を示す合焦信号を計算し、この合焦信号に応じてレンズ制御信号を生成する装置を備えていてもよい。

【0016】

【発明の実施の形態】

本願は、主センサチップによって生成される情報を用いて、追加のセンサを必要としない、ファインダ、自動焦点及び自動露出問題に対する完全電子化の実現を提供する。従って、本発明は、機械的複雑さ、及び、複数の部品の正確な位置合せを不要にする。

【0017】

図8に、ディジタルスチルカメラを示す。図の左側の場面からの光線80は、主光学系82によってセンサチップ84上に焦点が合わされる。センサチップ84において用いられる好ましい光変換器は、3重井戸(triple−well)フォトダイオード構成であり、これは、以下で詳細に説明され、かつ図9に示される。使用に適したセンサ回路は、自動露出検出を有する高感度記憶画素センサ(high−sensitivitystoragepixelsensor)であり、これは、以下で詳細に説明され、かつ図10〜12に示される。光学系82及びセンサチップ84は、光を通さないハウジング86内に収容されていて、迷光がセンサチップ84上に入射することを防止していて、それによって、光線80によって形成される画像が劣化することを防止している。図8には示していないが、図13に詳細に示す電子システムは、センサチップ84から電気信号を受け取り、表示チップ94を駆動するのに適した電気信号を得るが、これは、Texas Instrumentsから供給されるようなマイクロマシンで作られた反射タイプのものであっても、Kopin、MicroDisplay Corp.またはInvisoのようなマイクロディスプレイの供給業者から供給されるような液晶で覆われたタイプのものであってもよい。

【0018】

表示チップ94は、発光ダイオード(LED)アレイ96によって照らされる。表示チップ94からの反射光は、それらがカメラのユーザの目92によって見ることができるように、副光学系90によって焦点が合わされる。もう一つの選択肢として、表示チップ94は、有機(organic)発光アレイであってもよく、これは、直接、光を発するので、LEDアレイ96を必要としない。両方の技術は、優れた色の彩度を有する明るい表示をもたらし、かつパワーをほとんど消費しないので、図8に示したようなコンパクトカメラのハウジング内に組み込むのに適している。光を通さないバッフル88は、チャンバハウジングのセンサチップ14を、そのハウジングのLEDアレイ96、表示チップ94、及び副光学系90から分離している。明るい太陽光の中で表示チップ94からの像を見ることは、ゴムすなわちエラストマーのアイカップ98を設けることによって、より容易になる。

【0019】

図8の構成の動作は、図13を参照することによって最もよく理解される。図13は、図8のカメラを動作させ、かつ制御するために用いられる電子回路のブロック図を示している。センサチップ84からの出力信号は、処理回路100によって処理され、記憶媒体102に格納される。センサチップ84は、それが本発明に用いられることを可能にする、ある特有の能力を備えていなければならない。記憶媒体102は、磁気テープ、磁気ディスク、半導体フラッシュメモリ、或いは、この分野において知られている他のタイプのものであってもよい。制御回路106は、センサチップ84、処理回路100、及び記憶媒体102を制御して動作させる信号を供給する。更に、処理回路100は、表示チップ94を駆動するのに適した出力信号を供給し、制御回路106は、LEDアレイ96を制御して駆動するための信号を供給する。処理回路100は、好ましい状況においては、センサチップ84上に位置していて、これに組み込まれている。

【0020】

高解像度スチルカメラのために、センサチップ84は、表示チップ94のそれより、はるかに高い解像度(画素数)を有している。このため、取り込まれた画像に用いられたデータの一部分のみが、ファインダの像のために用いられる。従って、信号101は、フレーム毎に、わずかな画素しか持っていなくて、信号103より、はるかに高いフレームレートを持っている。信号103は、処理回路100によって媒体102上への記憶のために生成される。

【0021】

大きな利点が、画素のサブセットをアドレスすることが可能なセンサチップ84のための設計を用いることによって得られる。好ましい実施形態においては、以下で説明され、かつ図14〜19に示されるようなアドレス指定ロジックが用いられる。例えば、4番目毎の行における4番目毎の画素が、連続してアドレスされることによって、フレーム毎のスキャンアウト(scanout)時間を、16の率で短くすることが可能になる。

【0022】

実際の高解像度センサチップにおいては、スキャンアウト時間は、ファインダのフレームリフレッシュレートを左右する。例えば、4000X4000画素のセンサチップは、16,000,000画素を有している。20MHzのレートでスキャンされると、フレームレートは、1秒当たり1.25フレームであり、これでは、リアルタイムの現実感のあるファインダとしては、あまりにも遅い。4番目毎の行における4番目毎の画素を20MHzでスキャンすれば、1000X1000の表示チップを、1秒当たり25フレームで更新することができ、ユーザに提示されるレートは、非常に現実感があり、快適なリアルタイムのファインダをもたらす。この分野においてよく知られているように、CCDセンサは、各クロックサイクル内のいくつかの画素を「捨てる(binning)」ことによって、同様のフレームレートの利点を得ることができる。速いフレームレートを用いて、リアルタイムで、生き生きした、ユーザにわかりやすいファインダを達成することは、不可欠な特徴である。露光が取り込まれると、上記で用いられた例における16,000,000画素の全ては、制御回路106による制御の下で、スキャンされて、処理回路100を介して記憶媒体102内に格納される。

【0023】

自動焦点及び自動露出の動作の両方が、リアルタイムに、ユーザに分かるほどの遅延なしで起こることは重要である。露出及び焦点の情報の両方は、主センサとの位置合わせ不良の影響を受けやすい他のセンサから間接的に得られる信号から計算されるよりは、主センサの画像そのものから計算されるのが最も望ましい。上述したフレームレートの利点は、好ましい実施形態において、直接、主センサチップ84によって生成された信号から得られる完全電子化自動焦点を提供するのに用いられる。焦点位置(metric)回路104は、処理回路100から高いフレーム速度でファインダ信号101を受け取り、そこから所定のファインダフレームの焦点の質を表す信号105を計算する。前記焦点位置を計算する方法は、より十分に以下で説明され、かつ図20〜35に示される。制御回路106は、それによって、電気信号83を通して主光学系82の焦点を操作して、2、3フレーム後に、センサチップ84上の画像の焦点を合わせる。主光学系82は、好ましい実施形態においては、この分野ではよく知られているEOSファミリーの交換できる超音波のレンズである。

【0024】

露出中の真のthrough−the−lens(TTL)測光を遂行することが要求されるのであれば、露出情報は、焦点情報より更に迅速に計算されなければならない。このモードの動作において、センサチップ84上への光の積分は、所望の露出条件が達成されるまで続くことが可能である。その時、積分期間は終了し、画像は媒体102に格納される。好ましい実施形態においては、所望の露出条件の達成は、センサチップ84内の像面そのもので計算される。これは、更に十分に以下で説明され、かつ図10〜12に示される。信号87は、センサチップ84から制御回路106に露出条件を伝達する。制御回路106は、所望の露出条件の達成を示す信号87上の情報を受け取ると、信号85を通してセンサチップ84上での積分時間を終了させる。そして、露光がTTLフラッシュユニット108を用いて行われた場合には、この分野ではよく知られているように、フラッシュが制御回路106によって信号109を通して終了させられる。

【0025】

前述したように、センサチップ84として用いるのに適した光変換器の本発明を限定するわけではない例として、垂直色フィルタ多重フォトダイオード構成がある。以下、垂直色フィルタ多重フォトダイオード構成を詳細に説明する。

【0026】

図9に示したように、交互にp型及びn型領域が繰り返される6層の構造が形成され、第1の導電型の半導体基板200が底層として用いられていて、この中に、第1の導電型の拡散障壁埋め込み(implant)層202と、第2の反対の導電型の1つの井戸204とが配置されている。拡散障壁202は、基板で生成されたキャリアが、緑のフォトダイオードに向かって上方へ移動するのを防止する。そして、井戸204は、赤のフォトダイオードとしての検出器として動作する。この実施形態においては、第1の導電型の拡散障壁埋め込み層208を有する第1の導電型の第1のエピタキシャル層206が、半導体基板200及び基板の井戸204の表面上に配置され、第2の導電型の井戸210が、第1のエピタキシャル層206の中に配置されている。拡散障壁埋め込み層208は、第1のエピタキシャル層206の中で生成されたキャリアが、青のフォトダイオードに向かって上方へ移動するのを防止する。そして、井戸208は、緑のフォトダイオードとしての検出器として動作する。第1の導電型の第2のエピタキシャル層212が、第1のエピタキシャル層206及びその井戸210の表面上に配置されている。そして、第2の導電型のドープされた領域214(これは、低ドープドレイン埋め込み領域であってもよい)が、第2のエピタキシャル層212の中に形成されている。ドープされた領域214は、青の検出器を形成している。

【0027】

埋め込まれた緑の検出器210及び埋め込まれた赤の検出器204へのコンタクトが、深いコンタクトを介して行われている。埋め込まれた緑の検出器210のためのコンタクトは、第2のエピタキシャル層212を通して形成されていて、埋め込まれた赤の検出器204のためのコンタクトは、第2のエピタキシャル層212及び第1のエピタキシャル層206を通して形成されている。

【0028】

図9のハッチングされた領域は、この構造のp型及びn型の領域を造るために用いられた埋め込み領域の概略の位置を示している。破線216は、青い検出器214のための有効P(net−P)、及び、有効Nドーピングの間の概略の境界を定義する。同様に、破線218は、緑の検出器210のための有効Pと有効Nのドーピング間の概略の境界を示していて、これは、緑の検出器210へのコンタクトを形成している、第2のエピタキシャル層206の表面への、その垂直部分を有している。破線220は、赤の検出器204のための有効Pと有効Nのドーピング間の概略の境界を示していて、これは、赤の検出器204へのコンタクトを形成している、第2のエピタキシャル層206の表面への、その垂直部分を有している。

【0029】

ここに開示された6層構造の他の実施形態は、基板、基板に配置された1つ以上の井戸、1つ以上のエピタキシャル層、及び、1つ以上のエピタキシャル層に配置された1つ以上の井戸の中から選択された、層の様々な組み合わせを用いることが予想され、かつ、これを用いることによって実現されてもよい。

【0030】

また、上記のように、センサチップ84として用いるのに適した光変換器は、垂直色フィルタ多重フォトダイオード構成である。以下、光変換器及び光変換器を用いる方法について述べる。

【0031】

図10に、自動露出制御を組み込んだ高感度画素センサ230の一例の概略図を示す。フォトダイオード232は、(接地として示された)固定されたポテンシャルの供給源と連結されたアノードと、カソードとを有している。フォトダイオード232のカソードは、MOS Nチャネルバリアトランジスタ234のソースと連結されている。MOS Nチャネルバリアトランジスタ234のゲートは、BARRIERラインと連結されている。このBARRIERラインは、BARRIER制御ポテンシャルとされる可能性がある。この分野における通常の技術者であれば、記憶画素センサ230に、MOS Nチャネルバリアトランジスタ234を用いることが、いくらかの感度を犠牲にして、取捨選択可能であることは、分かるであろう。回路における他のトランジスタとは無関係に、画像の暗い領域において、感度(電荷−電圧変換利得)を上げるために、バリアトランジスタ234を追加することが可能である。MOS Nチャネルバリアトランジスタ234は、実質的に全てのフォトダイオードからの電荷を、高利得をもたらす第1のソースフォロアトランジスタ240のゲート容量にチャージして、そのゲート電圧を低下させ、更に、バリアトランジスタ234をオンにすることを可能にする。この後に、記憶画素センサ230は、(明るい領域のために)低利得モードで動作して、この中で、電荷が、フォトダイオードの容量と、ゲートの容量との両方をチャージする。

【0032】

フォトダイオード232のカソードは、MOS Nチャネルバリアトランジスタ234を介して光電荷積分ノード236(図10中では破線のキャパシタとして表されている)と連結されている。MOS Nチャネルリセットトランジスタ238は、光電荷積分ノード236と連結されたソースと、RESET信号がアサートされる可能性があるRESETラインに結合されたゲートと、リセットポテンシャルVRに結合されたドレインとを有している。

【0033】

光電荷積分ノード236は、第1のMOS Nチャネルソースフォロアトランジスタ240の本来のゲート容量を含んでいる。このトランジスタ240は、電圧ポテンシャルVSFD1に接続されたドレインを有している。電圧ポテンシャルVSFD1は、供給電圧V+(これは、例えば、技術に応じて約3〜5ボルトである可能性がある)に固定されていてもよいし、もしくは、以下で開示されるように、パルス化されていてもよい。MOS Nチャネルソースフォロアトランジスタ240のソースは、ソースフォロアトランジスタの出力ノード242を形成していて、電流源として動作するMOS Nチャネルバイアストランジスタ244のドレインと連結されている。MOS Nチャネルバイアストランジスタ244のソースは、固定された電圧ポテンシャル、例えば、接地と連結されている。MOS Nチャネルソースフォロアバイアストランジスタ244のゲートは、バイアス電圧ノードに接続されている。バイアス電圧ノードに現れる電圧は、MOS Nチャネルソースフォロアバイアストランジスタ244にバイアス電流を流す。この電圧は、固定されていても、パワーを節約するためにパルス化されていてもよい。MOS Nチャネルソースフォロアバイアストランジスタ244の使用は、任意である。このデバイスは、自動露出検出機能を実現するために、飽和レベルトランジスタと組み合わせて用いることができる。

【0034】

ソースフォロアトランジスタの出力ノード242は、容量性の記憶ノード246(図10中では、破線のコンデンサとして表されている)と連結されている。ソースフォロアトランジスタの出力ノード242は、MOS Nチャネル転送トランジスタ248を介して容量性の記憶ノード246と連結可能となっている。MOS Nチャネル転送トランジスタ248のゲートは、XFR信号がアサートされる可能性があるXFRラインと連結されている。MOS Nチャネル転送トランジスタ248は、記憶画素センサにおける任意の構成要素である。

【0035】

容量性の記憶ノード246は、第2のMOS Nチャネルソースフォロアトランジスタ250の本来のゲート容量を含んでいる。このトランジスタ250は、ソースフォロア−ドレイン(SFD)ポテンシャルに接続されたドレインと、ソースとを有している。第2のMOS Nチャネルソースフォロアトランジスタ250のソースは、MOS Nチャネル行選択トランジスタ254を介してCOLUMN OUTPUTライン252と連結されている。MOS Nチャネル行選択トランジスタ254のゲートは、ROW SELECTライン256と連結されている。

【0036】

第2のMOS Nチャネルソースフォロアトランジスタ250は、大きいデバイスであって、第1のMOS¥Nチャネルソースフォロアトランジスタ240の面積の10〜100倍のサイズのゲートを有していることが好ましい。回路の他のトランジスタ、すなわち第1のMOS¥Nチャネルソースフォロアトランジスタ240は、最小の長さ及び幅に近いサイズであることが好ましい。

【0037】

画素のサブセットをアドレスすることが可能なセンサチップ84のための設計を用いることによって、大きな利点が得られる。例えば、4番目毎の行における4番目毎の画素を連続してアドレスすることによって、ファインダの像のフレーム毎のスキャンアウト時間を16の率で短くすることが可能になる。

【0038】

以下、図11を参照すると、タイミング図が、(図10に示した)画素センサ10を使用する方法を示している。初めに、RESET信号が、ハイにアサートされる。MOS¥Nチャネルリセットトランジスタ238のドレインにおけるVRノードは、ゼロボルトから電圧VRにされる。この動作は、各フォトダイオード232のカソードに(MOS¥Nチャネルバリアトランジスタ234のしきい値よりは小さい)電圧ポテンシャルVRを印加することによって、アレイ中の全ての画素センサをリセットする。図11に示した高感度画素センサを動作させる好ましい方法によれば、電圧VRは、初めはロー(low)レベル(例えばゼロボルト)で、一方、アレイ中の全てのフォトダイオードのカソード電圧を、像の遅れを防ぐために迅速にそれらの状態を等しくするための低い値にリセットするために、RESETはハイ(high)である。次に、電圧VRが、予め定められた時間(好ましくは2、3ミリ秒のオーダー)、(例えば約2ボルトまで)上げられ、一方、RESET信号はまだアサートされていて、全ての画素センサにおけるフォトダイオードが、それらに結合されたMOS¥Nチャネルバリアトランジスタ234を通して、約1.4ボルトまで充電されることを可能にする。このトランジスタ234のゲートは、約2ボルトに保たれている。従って、積分ノードにおける黒レベルはVRに設定され、これは、MOS¥Nチャネルリセットトランジスタの容量性のターンオフ過渡現象のためには少し小さい。そして、フォトダイオードは、それぞれのバリアトランジスタのしきい値によって決められたような、それぞれの適切なレベルにリセットされる。この方法の利点は、それらのしきい値が、読み取られる黒レベルに影響を及ぼさないことである。リセットが終了して積分が開始された後にも、いくらかの電荷が、副しきい値条件によって、バリアを越えて、まだリークするであろう。しかし、それは、全ての画素について、ほぼ同じであるべきである。或いは、少なくとも、明るさのレベルの単調関数であるべきである。

【0039】

記憶画素センサの特に有利な動作によれば、バリアトランジスタ234及びリセットトランジスタ238は、同じサイズとされ、これにより、同じ電圧しきい値(Vth)を示す。RESET信号のアクティブレベルは、VRESET<VR+Vthとなるように選ばれ、より良い非線形性のトラッキングが達成される。

【0040】

RESET信号がディアサート(de−assert)されて光積分が始まると、電荷が光電荷積分ノード236に蓄積される。MOS¥Nチャネルバリアトランジスタ234が、わずかに導通しているので、フォトダイオード232のカソードの電圧を下げずに、(その電圧を下げることによって、)光誘導電荷が、そのチャネルを通して少しずつ流れて、光電荷積分ノード236をチャージする。これは、有利である。なぜなら、それが光電流によってチャージされるキャパシタンスを最小限にして、それによって感度(光子当たりのボルト)を最大限にするからである。

【0041】

この分野における通常の技術者であれば、MOS¥Nチャネルリセットトランジスタ238を、直接、フォトダイオード232のカソードに接続可能であることが分かるであろうが、そのような構成は、電圧VRがバリア電圧及びしきい値に対して正確にセットされることを必要とする。しきい値は変化する可能性があるので、これは、好ましくない。

【0042】

第1のMOS¥Nチャネルソースフォロアトランジスタ240のソースの電圧と、従ってその出力ノード242とは、そのゲート(光電荷積分ノード236)の電圧に従う。MOS¥Nチャネル転送トランジスタ248を用いる実施形態においては、図11に示したように、XFR信号は、リセット期間及び積分期間を通してアサートされていて、積分期間を終えるためにディアサートされる。XFR信号のローレベルは、転送トランジスタ248を完全にターンオフするために、好ましくはゼロまたは僅かに負の電圧、例えば約−0.2ボルトに設定される。

【0043】

画素センサを読み出すために、第2のMOS¥NチャネルソースフォロアトランジスタのドレインのSFDノード(図11中ではVSD2と表示されている)が電圧VSFDになるように駆動され、画素センサ230を含むアレイの行のためのROW SELECT信号がアサートされ、それによって出力信号がCOLUMN OUTPUTライン252を駆動する。VSFD2信号のアサートのタイミングは、図11に示したように、ROW SELECT信号がディアサートされた後までハイの状態を維持するべきであるということを除けば重要ではない。VSFD2が最初に立ち上がるのであれば、ROW SELECT信号の立ち上がりエッジにおける電圧の勾配を制限することは有利であるかもしれない。

【0044】

以下、図12を参照し、XFRトランジスタが存在しないならば、記憶ノードは、(好ましくはゼロまたは僅かに負の電圧、例えば約−0.2ボルトに)SFBIASを下げ、VRをローに設定し、そしてRESET信号をアサートすることによって、分離されてもよい。このシーケンスは、その負荷電流がターンオフされるとき、そのゲートの電圧を下げることによって、第1のソースフォロア240をターンオフし、それによって、その出力電圧を記憶する。

【0045】

図12に、VRの立ち下がりエッジ及びRESETの立ち上がりエッジが、終了(terminate)信号のすぐ後に続くことが示されている。これは、これらのトランジスタが、露出を終了するために、記憶ノードを分離するからである。図10においては、対応する遷移は、更に遅れて示される。なぜなら、XFRの立ち下がりが記憶ノードを分離すれば、それらは重要ではないからである。SFBIAS信号は、図12の場合にのみ立ち下げる必要があり、転送トランジスタがあるとき、バイアスは一定にすることができる。

【0046】

また、図12は、信号VSFD1がパルス化されていることを示している。ここに開示したように、VSFD1ノードは、常にハイの状態に保たれてもよいし、もしくは、図12に示したようにされてもよい。VSFD1は、パルス化されて、パワーを節約することができる。VSFD1がパルス化される実施形態において、終了(terminate)は、パルスの間に真の状態になる。RESETがハイになるまで、VSFD1はハイに保たれる。もしくは、転送トランジスタを用いる実施形態においては、XFRがローになるまで、VSFD1はハイに保たれる。

【0047】

第2のMOS¥Nチャネルソースフォロアトランジスタ250は、第1のMOS¥Nチャネルソースフォロアトランジスタ240より大きく、従って、そのゲート容量(容量性の記憶ノード246)も、それに応じて大きい。これは、画素センサ230にノイズ耐性を追加するという利点を提供する。なぜなら、所定の電圧変化を引き起こすために、光電荷積分ノード236を有する場合より多くの電荷が、容量性の記憶ノード246へ、もしくは容量性の記憶ノード246から転送される必要があるからである。

【0048】

図11及び12に示した制御信号は、従来のタイミング及び制御ロジックを用いて生成することができる。このために、タイミング及び制御ロジック回路258が図10に示されている。タイミング及び制御ロジック回路258の構成は、個々の実施形態によって変わるが、いずれにせよ、従来の回路構成であり、ひとたび個々の実施形態が選択されたら、個々の設計は、この分野における通常の技術者にとっては、図11及び12を試験することを含めても、ささいな仕事である。

【0049】

再び図10を参照し、別の実施形態による画素センサと共に用いる自動露出回路260が開示される。アレイ中の各画素は、MOS¥Nチャネル飽和レベルトランジスタ262を備えていて、このトランジスタ262は、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242に接続されたソースと、SAT.LEVELライン264に接続されたゲートと、全体電流合計ノード266に接続されたドレインとを有している。全体電流合計ノード266は、電流比較器268に接続されている。この分野における通常の技術者であれば、電流比較器268が、電圧源と全体電流合計ノード266との間に接続されるダイオード負荷または抵抗器を備えていて、電圧比較器の一方の入力を駆動するものであってもよいことが分かるであろう。電圧比較器のもう一方の入力は、所望の数の飽和した画素を表す電圧に接続される。もう一つの選択肢として、アナログ−ディジタル変換器が用いられて、比較がディジタル的に行われてもよい。

【0050】

バイアストランジスタ244が存在しさえすれば、飽和レベルトランジスタ262を用いて、飽和した画素センサからのバイアス電流を全体電流合計ライン上に流すことができ、それを、露出の間、何個の画素が飽和レベルトに達したかを調べるために、監視することができる。外部回路によって、飽和と判断するしきい値を制御することができ、また、単にそれをしきい値と比較する代りに、電流を測定することもできる。従って、この追加されたトランジスタ及び全体電流合計ラインによって、何個の画素センサが任意の特定レベルを越えたかを調べることが可能である。従って、しきい値(SAT.LEVEL)の素早い変更及び素早い測定(例えば、A/D変換器及びプロセッサへの入力によって)を実行することによって、露出の間の露出レベルの完全な累積ヒストグラムを得ることが可能である。この情報から、良好な露出レベルを、好ましい実施形態に用いた簡単なしきい値法を越えて、より複合的に決定することが可能である。

【0051】

バイアストランジスタ244が存在するとき、記憶ノードを分離するためには、タイミング信号によって、バイアストランジスタ244と第1のソースフォロア240との両方をターンオフする必要がある。転送トランジスタ248を設けることは、簡単であり、かつ記憶の完全性に関して有利である可能性がある。それは、1つのロジック信号による制御によって記憶ノードを分離することができる。また、同様の利点のために、バイアストランジスタなしであっても、転送トランジスタ248を基本回路に加えることができる。なぜなら、確実に第1のソースフォロアトランジスタ240をターンオフするには、Reset及びVR信号を統合することが必要になり、これは複雑であるが、それは、転送トランジスタ248によって除去することができる。

【0052】

動作において、SAT.LEVELライン44は、選択された光電荷飽和レベルに相当する電圧VSATになるように駆動される。光電荷の累算は、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242の電圧を下げるので、MOS¥Nチャネル飽和レベルトランジスタ262は、初めはターンオフされる。なぜなら、VSATにおけるそのゲート電圧は、ノード236の電圧より低いからである。光電荷積分ノード236における光電荷の蓄積が、その電圧をVSATより低くするまで、MOS¥Nチャネル飽和レベルトランジスタ262はオフを保つ(そして、第1のMOS¥Nチャネルソースフォロアトランジスタ240の出力ノード242と共通電位のMOS¥Nチャネル飽和レベルトランジスタ262のソースにおけるそれは、電圧VSATより1Vt低いレベルになる)。この時点で、MOS¥Nチャネル飽和レベルトランジスタ262はターンオンして、(バイアストランジスタ244に流れるバイアス電流より少ないか、もしくはこれに等しい)電流を全体電流合計ノード266から引き込み始める。

【0053】

この分野における通常の技術者であれば分かるように、アレイ中の他の画素センサも、それらのMOS¥Nチャネル飽和レベルトランジスタ262をターンオンするために十分な光電荷の蓄積を開始する。従って、ノード266から追加の電流を引き込み、更に、全体電流合計ノード266の電圧を低下させる。この分野における通常の技術者であれば分かるように、比較器268は電圧比較器であってもよく、その1つの入力は、全体電流合計ノード266に接続され、もう1つの入力は、選択された数の画素が飽和している(すなわち、それらのMOS¥Nチャネル飽和レベルトランジスタ262がターンオンされている)ときの全体電流合計ノード266の電圧に応じて選択された電圧VTERMに接続される。全体電流合計ノード266の電圧がVTERMに等しくなると、比較器268は露出終了(TERMINATE EXPOSURE)信号を生成する。これは、たくさんの方法のうちの1つによって、例えば、機械的なシャッタを閉じることによって、或いは、露出終了(end−of−exposure)信号(例えばXFR信号)を発して画素センサを制御することによって、露出期間を終了するために用いられる。露出終了(TERMINATE EXPOSURE)信号は、必要であれば、ストロボの閃光の発光を停止させるために用いることもできる。

【0054】

もう一つの選択肢として、A/D変換器270を全体電流合計ライン266に接続して、全体が合計された電流を表す電圧を、ディジタル値に変換してもよい。このディジタル値は、参照符号272で示したスマート自動露出アルゴリズムを用いて処理される。

【0055】

自動露出回路260は、ソースフォロアトランジスタ240のドレインへのVSFD1信号と、ソースフォロアバイアストランジスタ244のゲートに供給されるSFバイアス信号及び飽和レベルトランジスタ262のゲートに供給されるSAT.LEVEL信号のうちの1つまたは両方とを同時にパルス化することによって、パワーセーブモードで動作されるのが好ましい。そのようなモードにおいては、これらの信号のパルスが入力された時にのみ、自動露出検出電流が流れて、そのとき露出オーバーの検出が行われる。光積分の間のその他の時間には、各画素からの露出オーバー電流は流れないので、パワーが節約される。この動作モードが用いられると、自動露出回路260は、より良い信号対雑音比のために、より高い電流レベルで有利に用いられることが可能である。

【0056】

自動露出回路260の他の動作モードにおいては、アレイ中の全ての飽和レベルトランジスタ262のゲートにおけるSAT.LEVEL電圧が、ゼロから最高レベルまで掃引されて、アレイ中の全ての画素の状態の完全な累積分布を生じさせる。A/D変換器270が自動露出回路260に用いられるとき、この動作モードは最も有益である。オプションの転送トランジスタ248を用いる実施形態においては、このデバイスは、各測定サイクルにおけるSAT.LEVEL電圧の傾斜の前にターンオフされるべきである。或いは、追加のサイクルが、SAT.LEVEL電圧が低いときに実行されるべきである。これは、変化するSAT.LEVEL電圧で切られていない信号電圧を記憶するためである。この累積分布情報を用いる自動露出アルゴリズムの一例は、分布を分析して、逆光であるか否かによって場面を分類し、それに応じて、露出の間、SAT.LEVEL及びi−thresholdを異なる値に設定する。

【0057】

前述したように、大きな利点が、画素のサブセットをアドレス可能な、センサチップ84のための設計を用いることによって達成される。以下、センサチップ84内に組み込まれるアドレス指定ロジックを詳細に説明する。

【0058】

図14を参照すると、走査回路を用いた電子カメラ280のブロック図が示されている。電子カメラ280は、画素センサアレイ282、例えば、アクティブ画素センサアレイを備えている。画素センサアレイ282は、フレキシブルアドレス発生器回路284によって制御される。フレキシブルアドレス発生器回路284は、制御回路286によって制御され、これは、アレイ282から画素データを読み出す制御にとって必要な信号の全てを供給する。フレキシブルアドレス発生器回路284及び制御回路286は、画素センサアレイ282から完全な高解像度画像データを読み出して、そのデータを記憶システム288に格納するために用いられる。画素センサアレイ282は、ディジタルスチルカメラもしくはビデオカメラに用いるのに適した高解像度アクティブ画素センサアレイである。そのようなアクティブ画素センサアレイは、一般に、視野画面上に表示されるので、ユーザは、画像を見て、これを調節することができる。フレキシブルアドレス発生器回路284及び制御回路286は、同じシリコン上にセンサアレイ282として組み込まれてもよく、かつ、画素データを、画素センサアレイ282から生成された完全な画像のそれよりは低い解像度を有するファインダディスプレイに供給するのに用いられてもよい。

【0059】

図15に、図14のフレキシブルアドレス発生器回路284及び制御回路286を含む走査回路の詳細なブロック図を示す。走査回路の好ましい実施形態における主な構成要素が図15に示されている。アクティブ画素センサアレイ282は、N行及びM列の画素センサを有している。アクティブ画素センサアレイ282は、行選択ライン300及び列出力ライン302を介して、走査回路の残りの構成要素に接続されている。アクティブ画素センサアレイ282中の各行の画素センサに対して、1本の列選択ラインがあり、かつまた、アクティブ画素センサアレイ282中の各列の画素センサに対して、1本の列出力ラインがある。従って、図示したアクティブ画素センサアレイ282には、N本の行アドレスライン300と、M本の列出力ライン302とがある。

【0060】

行アドレスラインの信号は、行アドレス発生器306が駆動する行アドレスデコーダ304によって生成される。列ライン出力の選択は、列アドレス発生器310が駆動する列セレクタ308によって行われる。列セレクタ308は、この分野において知られているデコーダまたはその他のマルチプレクシング手段を備えていてもよい。行アドレス発生器306及び列アドレス発生器310は、一般的なカウンタと考えられ、制御回路312によって制御される。

【0061】

図15中の制御回路286については詳述しない。この分野における通常の技術者であれば、ここに開示された、選択されたイメージャーアレイの初期化及び制御要求に応じて、アクティブ画素センサアレイが、繰り返し初期化されて読み出されることを可能にする機能から、行及び列アドレス発生器306及び310の制御を容易に実施することができる。

【0062】

行アドレス発生器306及び列アドレス発生器310は、制御回路312の制御下で動作するロード可能なカウンタである。各カウンタは、開始アドレスをロードされ、次に、クロックが与えられて、増分Kずつのカウントを行い、停止アドレスに達し、この時、「停止に等しい(Equal to stop)」出力信号を制御回路に供給する。次に、カウンタは、開始アドレスにリセットされ、このシーケンスが再度開始される。行及び列アドレス発生器306及び310内のカウンタは、開始アドレスの値、停止アドレス、及びKの値の1つ以上のモードのためのセットを格納するレジスタを有している。制御回路312と、行及び列アドレス発生器306及び310とは、1つの行における各々の選択された列を通してクロックを供給するように構成されている。そして、行アドレス発生器をKずつインクリメントして、次に選択された行における各々の選択された列にクロックを供給する。

【0063】

行アドレス発生器からの「停止に等しい(Equal to stop)」信号は最後の行を示していて、制御回路312は、これ続いてセンサアレイの初期化を行い、これにより、各々の完全な行のサイクルが完了した後に、新しい像が取り込まれる。

【0064】

センサアレイの分野における通常の技術者であれば、他のタイミング信号及び遅延が、行間もしくは画像間に必要とされる可能性があることを認識しているであろう。そして、そのような遅延及び追加のタイミング信号を実現するため、及び、画像露出を同期させてカメラシステムの他の部分へ読み出すために、遅延素子や、その他のロジック及びタイミング素子を用いることができることを認識しているであろう。制御回路312は、本実施形態の重要な部分ではなく、一般に、センサアレイ及びフレキシブルアドレス指定回路と同じシリコン基板上には形成されない。図15に示したモードデータ(Mode Data)ラインは、モード定義データをカウンタのレジスタに格納するため、及び、任意の個々の時間に動作すべきモードを選択するための、一般的な経路を示している。各カウンタのための補数(complement)制御信号は、モードデータ(Mode Data)に含まれている。

【0065】

また、この分野における通常の技術者には明らかであろうが、フレキシブルアドレス発生器の停止検出機能は、取捨選択可能であり、それを実行する機能は、代替の実施形態において、いくつかの異なる方法で実現可能である。例えば、画像データをイメージャーから記憶システムに送る制御ロジックは、行及び列をカウントして、予め定められた量の画素データが送られたときに停止することができる。同様に、アレイから画素データを受け取るユニットも、行及び列をカウントして、予め定められた量の画素データが受け取られたときに停止するための信号をコントローラに送ることができる。これらの体系のどちらが用いられても、カウントまたはアドレス情報が、イメージャー集積回路まで、もしくはイメージャー集積回路からリアルタイムで送られる必要がないという利点が得られる。

【0066】

アクティブ画素センサアレイ282からの画像の、XあるいはY方向のいずれかにおける鏡像をとることが必要であれば、補数制御信号が用いられる。画像は、通常、色分解プリズムによって、3本の別々の色ビームに分割され、それぞれの個別の色ビームは、別々のアクティブ画素センサアレイへ送られる。そのようなプリズムは、他の2本の色分解ビームに対して鏡像となった1本の色分解ビームを生じさせる可能性がある。3本の色分解ビームが最終的な画像を形成するために再結合される前に、特定の色ビーム画像を他の色ビーム画像と同じ方向に戻すために、反転読み出しによる再ミラーリングが必要であるかもしれない。補数制御信号は、最大の行または列アドレスからカウントを減じることによって、行または列アドレスカウンタの画素センサアドレス指定方法を反転させる。イメージャーが2の累乗に等しいサイズを有している一般的な場合において、この減算は、「1の補数」として知られていて、これは各ビットの反転であり、特定のアクティブ画素センサアレイが、鏡像となった方式で読み出されるようにし、その結果生じる画像を所望の方向に戻す。

【0067】

制御回路312からロード(Load)信号を受け取った後に、行アドレス発生器306は、そのモードデータから、アクティブ画素センサアレイ282の中から選択されるべき、画素センサの最初の行アドレスをロードする。行アドレス発生器306にクロックが送られるたびに、それは、選択されるべき次の行アドレスを行デコーダ304に供給する。行アドレスカウンタ306は、個々のモードの画像解像度出力に対応する、いくつかの異なる行アドレス計算モードを保持するように設計されている。

【0068】

行アドレス発生器306は、選択的にアクティブ画素センサアレイ282の画素センサのある行を飛ばすために、KN毎のカウント(count−by−KN)体系を実行する。例えば、画素センサが飛ばされない詳細モードにおいては、KN=1であり、行アドレス発生器306は、行デコーダ300に、行を飛ばすように指示しない。中間及び最大ズームモードの両方においては、KN>1であり、行アドレス発生器306は、KNによって選択されるべき次の行のアドレスの計算をインクリメントする。行アドレス発生器306は、それぞれ計算された行アドレスを行デコーダ304に供給する。中間ズーム及び最大フレーム視野画面表示モードにおいては、アクティブ画素センサアレイ282上のある行は、アレイの読み出しの間に飛ばされる。

【0069】

選択されるべき各行アドレスは、行アドレス発生器306によって行デコーダ304に供給され、これは、この分野において知られているように、供給されたアドレスに基づいて、適切な行選択ライン300を選択する。行ラインを選択することは、選択された行ラインと結合した画素センサの選択ノードをアクティブにするために、信号を行ライン上に流すことに相当する。

【0070】

列アドレス発生器310も、行アドレス発生器306と同じ仕方で機能する。ひとたびロード(Load)信号を制御回路286から受け取ると、列アドレス発生器310は、そのモードデータから、アクティブ画素センサアレイ282から読み出されるべき最初の列アドレスをロードする。列アドレス発生器310は、KM毎のカウント(count−by−KM)体系を実行して、選択されるべき次の列のアドレスを計算する。そして、列アドレスカウンタ310は、列アドレスを列セレクタ308に供給する。列アドレス発生器310のアドレス指定方法によって、列セレクタ308は選択的にアクティブ画素センサアレイ282上の画素センサのある列を飛ばす。列アドレス発生器310は、異なるモードの画像解像度及び位置出力を考慮して、開始、KM、及び停止データのいくつかのセットを保持するように設計されている。

【0071】

列セレクタ308のいくつかの異なる実施形態が可能である。列セレクタ308は、列出力ラインに接続された列デコーダと、スイッチを介した画素値出力ラインとを備えていてもよい。スイッチは、列デコーダが、適切な列出力ラインをオンにすることを可能にし、その列から画素値出力ラインに所望の画素センサ出力値を送る。もう一つの選択肢として、列セレクタ38は、列出力ラインに接続される2進樹(binary tree)列セレクタを備えていてもよい。

【0072】

図16は、走査回路によって実行される様々な画素センサ選択モードのために、画素センサ選択体系を実行する好ましい方法を示すフローチャートである。このフローチャートにおいて、現在の行アドレス番号は、nとして与えられ、現在の列アドレス番号は、mとして与えられる。このロジックは、KN毎カウント(count−by−KN)行スキップ体系、及び、KM毎カウント(count−by−KM)列スキップ体系を実行する。読出しは、Nstart行及びMstart列から始まり、Nstop行及びMstop列で停止する。

【0073】

まず、ステップ320で、走査回路は、最初の行アドレス番号を初期化して、選択されたn=Nstartにする。ステップ322で、走査回路は、最初の列アドレス番号を初期化して、選択されたm=Mstartにする。ステップ324で、走査回路は、画素センサ(n、m)を読み出す。走査回路は、現在読み出している行における最後の所望の列に達したかどうかをチェックする。ステップ326で、走査回路は、m=Mstopであるかどうかを調べる。ノーであれば、走査回路は、ステップ328で、m=m+KMをセットして、列アドレス番号のカウントをインクリメントする。走査回路は、それからステップ324に戻る。イエスであれば、走査回路は、ステップ330に進む。

【0074】

ステップ326で、m=Mstopが真であったならば、ステップ330で、n=Nstopかどうか、すなわち行カウントが最後の所望の行に等しいか否かを調べる。ノーであれば、行カウントは、ステップ332で、n=n+KNにセットされる。走査回路は、それからステップ322に戻り、ここで、列アドレスをMstartに再初期化して、次の行の中から画素センサを選択し続ける。イエスであれば、全ての所望の画素センサは読み出されたので、画素センサ読出しは、ステップ334で終了する。

【0075】

各画素センサアレイ読出しモードは、Nstart、Mstart、Nstop、Mstop、KN及びKMの異なる値を有している。高解像度部分画像表示モードにおいては、ユーザは、Nstart及びMstartを選択する。このモードは、画素センサを全く飛ばさないので、KN及びKMは、双方共に1に等しい。Nstop及びMstopは、アクティブ画素センサアレイのサイズに対する視野画面(viewscreen)のサイズによって決定される。走査回路は、任意に選択された開始位置から、もはや画素センサを利用可能な視野画面のスペース上に表示させることができなくなるまで、順次にアクティブ画素センサアレイから画素センサを読み出す。

【0076】

最大フレーム視野画面表示モードにおいては、画像全体が、視野画面上に表示されるので、Nstart及びMstartは、双方共にゼロに等しくてよい。N行M列のアクティブ画素センサアレイであれば、Nstop及びMstopは、各々、N及びMよりは小さい、KN及びKMの最も大きい倍数にセットされるので、ゼロからのKN及びKM毎のカウントは、正確に停止値に達する。

もう一つの選択肢として、簡単な等しいことの検出器よりむしろ、ディジタル大きさ比較器を用いてもよい。これによれば、停止値としてN−KN及びM−KMを用いることができる。KN及びKMは、視野画面サイズに対するアクティブ画素センサアレイのサイズの比率に基づいて決定される。

【0077】

中間ズームモードにおいては、Nstart及びMstartは、ユーザによって任意に選択される。KN及びKMは、高解像度部分画像表示モードと、低解像度最大フレーム視野画面モードとの中間の、視野画面画像解像度を生成するように選択された、予め記憶された値とされる。Nstop及びMstopは、視野画面のサイズと、KN及びKM値とによって決定される。走査回路は、KNずつ行をカウントし、かつKMずつ列をカウントして、順次にアクティブ画素センサアレイから画素センサを読み出す。アクティブ画素センサアレイの読出しは、任意に選択された開始位置から始まり、もはや画素が視野画面上に表示されることができなくなるまで続く。

【0078】

図16に示した画素センサアドレス指定方法は、x−y行列状に配列された行及び列の画素センサから成るアクティブ画素センサアレイのために設計されている。このx−y座標系の行列は、アクティブ画素センサアレイの現時点での好ましい実施形態であるが、図示した画素センサ選択方法は、また、異なる座標系を用いる行列にも適用することができる。

【0079】

行アドレス発生器306と列アドレス発生器310との両方の実例となる実施形態のための構成要素を図17に示す。図17は、フレキシブルアドレスカウンタ340の1ビットスライスを示す概略図である。フレキシブルアドレスカウンタ340に使われるビットの総数は、アクティブ画素センサアレイのサイズによって変わる。画素センサアレイのサイズが大きければ大きいほど、より大きい最大行及び列アドレスのカウントを必要とするので、追加のフレキシブルアドレスカウンタのビットを必要とする。

【0080】

フレキシブルアドレス発生器340は、3つのグループのアドレス選択パラメータを記憶するために3つのグループのレジスタを備えている。モードOは、レジスタグループ342によって生み出され、モード1は、レジスタグループ344によって生み出され、モード2は、レジスタグループ346によって生み出される。各レジスタグループは、3つのレジスタビットと、3つのCMOS伝送ゲートとを含んでいる。モードOに対応するグループ342は、レジスタビット348、350及び352と、CMOS伝送ゲート354、356及び358とを含んでいる。モード1に対応するグループ344は、レジスタビット360、362及び364と、CMOS伝送ゲート366、368及び370を含んでいる。モード2に対応するグループ346は、レジスタビット372、374及び376と、CMOS伝送ゲート378、380及び382を含んでいる。レジスタに格納されたモードO、モード1及びモード2のデータ間の選択は、それぞれ、モードO、モード1及びモード2制御ライン384、386及び388を用いて行われる。

【0081】

この分野における通常の技術者であれば、図17に示した3つの異なるレジスタグループが、単なる例であると認識するであろう。フレキシブルアドレス発生器340は、走査回路の個々の画素センサ選択モードに応じて、どのような数のレジスタグループを備えることも可能である。

【0082】

各一群の画素センサアドレス選択モードに対応する各レジスタグループは、個々のカウントシーケンスのために、Start、K及びStop値を保持している。これらの値は、アドレス指定カウント体系の開始アドレス値(Start)をセットするため、画素センサアドレスのカウントをインクリメントする増分値(K)をセットするため、及び終了指示(Stop)のための比較を行うために、カウンタに入力を提供する。それぞれの個々のモードにおいて、個々の画素センサアドレスカウント体系が生み出される。各々のカウントシーケンスモードのためのレジスタは、この分野において知られているような従来の手段によってロード可能なので、それらの値は、開始位置及びユーザによって選択された表示(viewing)モードに応じて変更することができる。

【0083】

開始(Start)値は、レジスタビット352、364及び376に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、開始(Start)値をライン390上に送り出す。K値は、レジスタビット350、362及び374に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、K値をライン392上に送り出す。停止(Stop)値は、レジスタビット348、360及び372に保持される。モード0、1または2が選択されるかどうかに応じて、これらの3つのレジスタビットのうちの1つが、停止(Stop)値をライン394上に送り出す。

【0084】

図14に示した制御回路286は、図17に示したフレキシブルアドレス発生器340に、ロード(Load)、クロック(Clock)及び補数(Complement)信号を供給する。Load信号396によって、カウンタ状態フリップフロップ398は、選択されたモードから供給されるライン390上のStart値にセットされる。Clock信号400は、フレキシブルアドレス発生器の状態変化の同期化をもたらす。

【0085】

Clock信号400によって、加算器402の和出力、現在のカウントの増分(plus)Kは、次のカウンタの状態としてフリップフロップ398に格納される。カウンタ状態フリップフロップ398がクロックの進行によってインクリメントすると、それは、フリップフロップ398内の現在の値を停止チェック404に供給する。停止チェック404は、1つのインバータ406と、3つのNANDゲート408、410及び412と、ANDゲート414とを含んでいる。停止チェック404は、フリップフロップ398に格納された現在の値を、ライン394上の停止(Stop)値と比較する。フリップフロップ398に格納された現在の値が停止(Stop)値に等しいとき、Equal−Inライン422がアサートされ、停止チェック404からの出力は、Equal−Outライン416をアサートする。

【0086】

図17に示したフレキシブルアドレス発生器340はリップルカウンタであり、より詳細にはリップルキャリーアキュムレータである。リップルカウンタは、この分野においてよく知られている。このデバイスは、一般にリップルカウンタと呼ばれている。なぜなら、各々の上位ステージが、正当な結果を生み出すために、先行する下位ステージから送られるデータを受け取るからである。図示したリップルカウンタは、ここに開示された走査回路のための好ましいカウンタの実施形態であるが、他のタイプのディジタルカウンタが、フレキシブルアドレス発生器340のカウント機能を実現するために用いられてもよい。

【0087】