JP2004040730A - リミッタ回路 - Google Patents

リミッタ回路 Download PDFInfo

- Publication number

- JP2004040730A JP2004040730A JP2002198906A JP2002198906A JP2004040730A JP 2004040730 A JP2004040730 A JP 2004040730A JP 2002198906 A JP2002198906 A JP 2002198906A JP 2002198906 A JP2002198906 A JP 2002198906A JP 2004040730 A JP2004040730 A JP 2004040730A

- Authority

- JP

- Japan

- Prior art keywords

- current

- potential

- differential amplifier

- photodiode

- limiter circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Tone Control, Compression And Expansion, Limiting Amplitude (AREA)

- Amplifiers (AREA)

Abstract

【課題】電流/電圧変換器の飽和を防止することが可能なリミッタ回路を提供する。

【解決手段】フォトダイオード170に過大光が入射し、当該フォトダイオード170の出力電流IPDが増加して、差動増幅器150の出力端子の電位が電源130の電位V1になった場合には、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値にまで低下する。このため、npnトランジスタ120は導通し、コレクタ電流ID2が流れ、抵抗素子152を流れる電流ID1は、フォトダイオード170が出力する電流IPDからnpnトランジスタ120のコレクタ電流ID2を差し引いた値に維持される。

【選択図】 図1

【解決手段】フォトダイオード170に過大光が入射し、当該フォトダイオード170の出力電流IPDが増加して、差動増幅器150の出力端子の電位が電源130の電位V1になった場合には、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値にまで低下する。このため、npnトランジスタ120は導通し、コレクタ電流ID2が流れ、抵抗素子152を流れる電流ID1は、フォトダイオード170が出力する電流IPDからnpnトランジスタ120のコレクタ電流ID2を差し引いた値に維持される。

【選択図】 図1

Description

【0001】

【発明の属する技術分野】

本発明は、入力電流、特にフォトダイオードからの入力電流に応じた電圧の信号を出力する電流/電圧変換器が飽和することを防止するリミッタ回路に関する。

【0002】

【従来の技術】

光ピックアップ用のフォトダイオードを備えた集積回路(PDIC)は、コンパクトディスク等に光を照射し、反射光を検出することにより、当該コンパクトディスク等に記録された信号を読み取るために用いられる。

【0003】

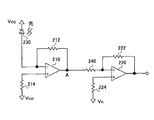

図2は、従来のPDICの回路図である。同図に示すPDICは、2段の差動増幅器210、220を備える。1段目の差動増幅器210は、フォトダイオード230に光が入射したときに、当該フォトダイオード230から出力される電流に応じた電圧の信号を出力する電流/電圧変換アンプ(I−Vアンプ)である。この差動増幅器210は、逆相入力端子がフォトダイオード230のアノードに接続され、逆相入力端子と出力端子とが抵抗素子212によって接続されるとともに、正相入力端子が抵抗素子214を介して電位Vcの端子に接続される。

【0004】

2段目の差動増幅器220は、1段目の差動増幅器210から出力される電圧の信号を増幅する電圧増幅器である。この差動増幅器220は、逆相入力端子と出力端子との間が抵抗素子222によって接続され、正相入力端子が抵抗素子224を介して電位Vcの端子に接続される。また、1段目の差動増幅器210の出力端子と2段目の差動増幅器220の逆相入力端子とが抵抗素子240により接続される。

【0005】

【発明が解決しようとする課題】

ところで、上述した従来のPDICにおいて、ノイズ特性は重要な項目である。このアンプのノイズ特性は以下のようにして決まる。

【0006】

Vn=(I−Vアンプノイズ)×(2段目アンプゲイン)

つまり、差動増幅器210のノイズがゲイン倍されることになる。ノイズ特性を向上させるためには、差動増幅器210の抵抗値を上げ、差動増幅器220のゲインを下げる方法が考えられる。差動増幅器210の変換抵抗が持つノイズより、差動増幅器220のゲインの方が直接に働くためである。

【0007】

しかし、抵抗素子212、214の抵抗値を上げる方法では、フォトダイオード230に過大光が入射すると、当該フォトダイオード230から出力される電流が増加し、差動増幅器210の出力端子における電位(図2の点Aにおける電位)が低下する。このため、差動増幅器210の出力電流源のnpnトランジスタのVceが低下し、飽和することによる動作不良が生じる。

【0008】

例えば、フォトダイオード230の感度が0.2μ/W、I−Vアンプ抵抗が120kΩの場合、フォトダイオード230に100μWの光が入射されると、20μAの電流が流れる。差動増幅器210は、Vc(2.5V)基準の反転アンプであるため、出力は以下のようになる。

【0009】

Vout=2.5V−120kΩ×20μA=0.1V

上記の電圧では、出力電流源のnpnトランジスタは飽和してしまう。

【0010】

本発明は、上記問題点を解決するものであり、その目的は、電流/電圧変換器の飽和を防止することが可能なリミッタ回路を提供することにある。

【0011】

【課題を解決するための手段】

上記の目的を達成するため、請求項1に記載の発明は、入力電流に応じた電圧の信号を出力する電流/電圧変換器が飽和することを防止するリミッタ回路において、ベースが前記電流/電圧変換器の出力端子に接続される第1のnpnトランジスタと、ベースが電源に接続され、コレクタが前記電流/電圧変換器の入力端子に接続される第2のnpnトランジスタと、前記第1及び第2のnpnトランジスタのエミッタ同士を接続する抵抗素子とを備えることを特徴とする。

【0012】

また、請求項2に記載の発明は、請求項1に記載のリミッタ回路において、前記入力電流は、光が入射されたフォトダイオードから入射されることを特徴とする。

【0013】

また、請求項3に記載の発明は、請求項1又は2に記載のリミッタ回路において、前記電流/電圧変換器は、差動増幅器であることを特徴とする。

【0014】

電流/電圧変換器に入力される電流が大きい場合には、当該電流/電圧変換器の出力端子の電位が低下する。しかし、本発明によれば、第2のnpnトランジスタのベースに接続された電源の電位を適切な値に設定しさえすれば、電流/電圧変換器の出力端子の電位が低下したときに、入力電流の一部を第2のnpnトランジスタのコレクタへ分流することにより、電流/電圧変換器の出力端子の電位が低下することを防止し、当該電流/電圧変換器の飽和を防止することが可能となる。

【0015】

【発明の実施の形態】

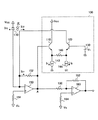

以下、本発明の実施の形態を図面に基づいて説明する。図1は、本発明の実施の形態に係るリミッタ回路を用いたPDICの回路図である。同図に示すPDICは、例えば、コンパクトディスク等に光を照射し、反射光を検出することにより、当該コンパクトディスク等に記録された信号を読み取るために用いられる。このPDICは、リミッタ回路100、1段目の差動増幅器150、抵抗素子152、154、2段目の差動増幅器160、抵抗素子162、164、フォトダイオード170、抵抗素子180を備える。

【0016】

1段目の差動増幅器150は、フォトダイオード170に光が入射したときに、当該フォトダイオード170から出力される電流IPDに応じた電圧の信号を出力する電流/電圧変換アンプ(I−Vアンプ)である。この差動増幅器150は、逆相入力端子がフォトダイオード170のアノードに接続され、逆相入力端子と出力端子とが抵抗素子152によって接続されるとともに、正相入力端子が抵抗素子154を介して電位Vcの端子に接続される。

【0017】

2段目の差動増幅器160は、1段目の差動増幅器150から出力される電圧の信号を増幅する電圧増幅器である。この差動増幅器160は、逆相入力端子と出力端子との間が抵抗素子162によって接続され、正相入力端子が抵抗素子164を介して電位Vcの端子に接続される。また、1段目の差動増幅器150の出力端子と2段目の差動増幅器160の逆相入力端子とが抵抗素子180により接続される。

【0018】

リミッタ回路100は、フォトダイオード170に過大光が入射した場合に、電流クランプを行う。これにより出力電流源のnpnトランジスタの飽和が防止される。このリミッタ回路100は、2つのnpnトランジスタ110、120、電源130、抵抗素子140、2つの変圧器142、144を備える。なお、2つのnpnトランジスタ110、120は、同一の仕様のものが用いられる。

【0019】

npnトランジスタ110は、ベースが1段目の差動増幅器150の出力端子に接続され、コレクタが電位Vccの端子に接続される。更に、npnトランジスタ110のエミッタは、変圧器142の一方の端子に接続される。この変圧器142は、他方の端子が接地されている。

【0020】

npnトランジスタ120は、ベースが電位V1の電源130に接続され、コレクタが1段目の差動増幅器150の逆相入力端子に接続される。更に、npnトランジスタ120のエミッタは、変圧器144の一方の端子に接続される。この変圧器144は、他方の端子が接地されている。

【0021】

また、npnトランジスタ110及び120のエミッタ同士が抵抗素子140により接続される。

【0022】

電源130の電位V1は、1段目の差動増幅器150の出力電流源のnpnトランジスタが飽和に入らない値(飽和が防止される電圧0.8〜1V程度)に設定される。これにより、リミッタ回路100は、フォトダイオード170に過大光が入射した場合にも、1段目の差動増幅器150の出力端子の電位を当該差動増幅器150が飽和しないような電位に維持することができる。具体的には、以下の動作となる。

【0023】

フォトダイオード170に過大光が入射していない通常の動作時においては、1段目の差動増幅器150の出力端子の電位(図1のAの電位)は、電源130の電位V1よりも高くなる。このため、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値より高くなり、当該npnトランジスタ120には、コレクタ電流が流れない。

【0024】

従って、フォトダイオード170から出力される電流IPDは全て1段目の差動増幅器150の逆相入力端子と出力端子とを接続する抵抗素子152を流れる電流ID1となる。

【0025】

フォトダイオード170に入射する光のエネルギーが増加すると、当該フォトダイオード170から出力される電流IPDが大きくなり、それに伴って電流ID1が大きくなる。このため、1段目の差動増幅器150の出力端子の電位は低下する。但し、電源130の電位V1よりも高ければ、当該差動増幅器150は通常の動作を行う。

【0026】

一方、フォトダイオード170に過大光が入射し、当該フォトダイオード170から出力される電流IPDが増加することにより、1段目の差動増幅器150の出力端子の電位(図1のAの電位)が電源130の電位V1になった場合には、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値にまで低下する。

【0027】

このため、npnトランジスタ120は導通し、コレクタ電流ID2が流れる。このコレクタ電流ID2は、フォトダイオード170から出力される電流IPDの一部を分流したものであり、変圧器142及び143を流れる電流I1、I2となる。

【0028】

従って、1段目の差動増幅器150の逆相入力端子と出力端子とを接続する抵抗素子152を流れる電流ID1は、フォトダイオード170が出力する電流IPDからnpnトランジスタ120のコレクタ電流ID2(電流I1、I2)を差し引いた値に維持される。このため、1段目の差動増幅器150の出力端子の電位が電源130の電位V1より低下せず、当該差動増幅器150の飽和を防止することができる。

【0029】

【発明の効果】

本発明によれば、第2のnpnトランジスタのベースに接続された電源の電位を適切な値に設定しさえすれば、電流/電圧変換器の出力端子の電位が低下したときに、入力電流の一部を第2のnpnトランジスタのコレクタへ分流することにより、電流/電圧変換器の出力端子の電位が低下することを防止し、当該電流/電圧変換器の飽和を防止することが可能となる。

【図面の簡単な説明】

【図1】本実施形態のPDICの回路図である

【図2】従来のPDICの回路図である

【符号の説明】

100 リミッタ回路

110、120 npnトランジスタ

130 電源

140、152、154、162、164、180 抵抗素子

142、144 変圧器

150、160 差動増幅器

170 フォトダイオード

【発明の属する技術分野】

本発明は、入力電流、特にフォトダイオードからの入力電流に応じた電圧の信号を出力する電流/電圧変換器が飽和することを防止するリミッタ回路に関する。

【0002】

【従来の技術】

光ピックアップ用のフォトダイオードを備えた集積回路(PDIC)は、コンパクトディスク等に光を照射し、反射光を検出することにより、当該コンパクトディスク等に記録された信号を読み取るために用いられる。

【0003】

図2は、従来のPDICの回路図である。同図に示すPDICは、2段の差動増幅器210、220を備える。1段目の差動増幅器210は、フォトダイオード230に光が入射したときに、当該フォトダイオード230から出力される電流に応じた電圧の信号を出力する電流/電圧変換アンプ(I−Vアンプ)である。この差動増幅器210は、逆相入力端子がフォトダイオード230のアノードに接続され、逆相入力端子と出力端子とが抵抗素子212によって接続されるとともに、正相入力端子が抵抗素子214を介して電位Vcの端子に接続される。

【0004】

2段目の差動増幅器220は、1段目の差動増幅器210から出力される電圧の信号を増幅する電圧増幅器である。この差動増幅器220は、逆相入力端子と出力端子との間が抵抗素子222によって接続され、正相入力端子が抵抗素子224を介して電位Vcの端子に接続される。また、1段目の差動増幅器210の出力端子と2段目の差動増幅器220の逆相入力端子とが抵抗素子240により接続される。

【0005】

【発明が解決しようとする課題】

ところで、上述した従来のPDICにおいて、ノイズ特性は重要な項目である。このアンプのノイズ特性は以下のようにして決まる。

【0006】

Vn=(I−Vアンプノイズ)×(2段目アンプゲイン)

つまり、差動増幅器210のノイズがゲイン倍されることになる。ノイズ特性を向上させるためには、差動増幅器210の抵抗値を上げ、差動増幅器220のゲインを下げる方法が考えられる。差動増幅器210の変換抵抗が持つノイズより、差動増幅器220のゲインの方が直接に働くためである。

【0007】

しかし、抵抗素子212、214の抵抗値を上げる方法では、フォトダイオード230に過大光が入射すると、当該フォトダイオード230から出力される電流が増加し、差動増幅器210の出力端子における電位(図2の点Aにおける電位)が低下する。このため、差動増幅器210の出力電流源のnpnトランジスタのVceが低下し、飽和することによる動作不良が生じる。

【0008】

例えば、フォトダイオード230の感度が0.2μ/W、I−Vアンプ抵抗が120kΩの場合、フォトダイオード230に100μWの光が入射されると、20μAの電流が流れる。差動増幅器210は、Vc(2.5V)基準の反転アンプであるため、出力は以下のようになる。

【0009】

Vout=2.5V−120kΩ×20μA=0.1V

上記の電圧では、出力電流源のnpnトランジスタは飽和してしまう。

【0010】

本発明は、上記問題点を解決するものであり、その目的は、電流/電圧変換器の飽和を防止することが可能なリミッタ回路を提供することにある。

【0011】

【課題を解決するための手段】

上記の目的を達成するため、請求項1に記載の発明は、入力電流に応じた電圧の信号を出力する電流/電圧変換器が飽和することを防止するリミッタ回路において、ベースが前記電流/電圧変換器の出力端子に接続される第1のnpnトランジスタと、ベースが電源に接続され、コレクタが前記電流/電圧変換器の入力端子に接続される第2のnpnトランジスタと、前記第1及び第2のnpnトランジスタのエミッタ同士を接続する抵抗素子とを備えることを特徴とする。

【0012】

また、請求項2に記載の発明は、請求項1に記載のリミッタ回路において、前記入力電流は、光が入射されたフォトダイオードから入射されることを特徴とする。

【0013】

また、請求項3に記載の発明は、請求項1又は2に記載のリミッタ回路において、前記電流/電圧変換器は、差動増幅器であることを特徴とする。

【0014】

電流/電圧変換器に入力される電流が大きい場合には、当該電流/電圧変換器の出力端子の電位が低下する。しかし、本発明によれば、第2のnpnトランジスタのベースに接続された電源の電位を適切な値に設定しさえすれば、電流/電圧変換器の出力端子の電位が低下したときに、入力電流の一部を第2のnpnトランジスタのコレクタへ分流することにより、電流/電圧変換器の出力端子の電位が低下することを防止し、当該電流/電圧変換器の飽和を防止することが可能となる。

【0015】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて説明する。図1は、本発明の実施の形態に係るリミッタ回路を用いたPDICの回路図である。同図に示すPDICは、例えば、コンパクトディスク等に光を照射し、反射光を検出することにより、当該コンパクトディスク等に記録された信号を読み取るために用いられる。このPDICは、リミッタ回路100、1段目の差動増幅器150、抵抗素子152、154、2段目の差動増幅器160、抵抗素子162、164、フォトダイオード170、抵抗素子180を備える。

【0016】

1段目の差動増幅器150は、フォトダイオード170に光が入射したときに、当該フォトダイオード170から出力される電流IPDに応じた電圧の信号を出力する電流/電圧変換アンプ(I−Vアンプ)である。この差動増幅器150は、逆相入力端子がフォトダイオード170のアノードに接続され、逆相入力端子と出力端子とが抵抗素子152によって接続されるとともに、正相入力端子が抵抗素子154を介して電位Vcの端子に接続される。

【0017】

2段目の差動増幅器160は、1段目の差動増幅器150から出力される電圧の信号を増幅する電圧増幅器である。この差動増幅器160は、逆相入力端子と出力端子との間が抵抗素子162によって接続され、正相入力端子が抵抗素子164を介して電位Vcの端子に接続される。また、1段目の差動増幅器150の出力端子と2段目の差動増幅器160の逆相入力端子とが抵抗素子180により接続される。

【0018】

リミッタ回路100は、フォトダイオード170に過大光が入射した場合に、電流クランプを行う。これにより出力電流源のnpnトランジスタの飽和が防止される。このリミッタ回路100は、2つのnpnトランジスタ110、120、電源130、抵抗素子140、2つの変圧器142、144を備える。なお、2つのnpnトランジスタ110、120は、同一の仕様のものが用いられる。

【0019】

npnトランジスタ110は、ベースが1段目の差動増幅器150の出力端子に接続され、コレクタが電位Vccの端子に接続される。更に、npnトランジスタ110のエミッタは、変圧器142の一方の端子に接続される。この変圧器142は、他方の端子が接地されている。

【0020】

npnトランジスタ120は、ベースが電位V1の電源130に接続され、コレクタが1段目の差動増幅器150の逆相入力端子に接続される。更に、npnトランジスタ120のエミッタは、変圧器144の一方の端子に接続される。この変圧器144は、他方の端子が接地されている。

【0021】

また、npnトランジスタ110及び120のエミッタ同士が抵抗素子140により接続される。

【0022】

電源130の電位V1は、1段目の差動増幅器150の出力電流源のnpnトランジスタが飽和に入らない値(飽和が防止される電圧0.8〜1V程度)に設定される。これにより、リミッタ回路100は、フォトダイオード170に過大光が入射した場合にも、1段目の差動増幅器150の出力端子の電位を当該差動増幅器150が飽和しないような電位に維持することができる。具体的には、以下の動作となる。

【0023】

フォトダイオード170に過大光が入射していない通常の動作時においては、1段目の差動増幅器150の出力端子の電位(図1のAの電位)は、電源130の電位V1よりも高くなる。このため、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値より高くなり、当該npnトランジスタ120には、コレクタ電流が流れない。

【0024】

従って、フォトダイオード170から出力される電流IPDは全て1段目の差動増幅器150の逆相入力端子と出力端子とを接続する抵抗素子152を流れる電流ID1となる。

【0025】

フォトダイオード170に入射する光のエネルギーが増加すると、当該フォトダイオード170から出力される電流IPDが大きくなり、それに伴って電流ID1が大きくなる。このため、1段目の差動増幅器150の出力端子の電位は低下する。但し、電源130の電位V1よりも高ければ、当該差動増幅器150は通常の動作を行う。

【0026】

一方、フォトダイオード170に過大光が入射し、当該フォトダイオード170から出力される電流IPDが増加することにより、1段目の差動増幅器150の出力端子の電位(図1のAの電位)が電源130の電位V1になった場合には、npnトランジスタ120のエミッタの電位は、電源130の電位V1からベース−エミッタ間の電圧を差し引いた値にまで低下する。

【0027】

このため、npnトランジスタ120は導通し、コレクタ電流ID2が流れる。このコレクタ電流ID2は、フォトダイオード170から出力される電流IPDの一部を分流したものであり、変圧器142及び143を流れる電流I1、I2となる。

【0028】

従って、1段目の差動増幅器150の逆相入力端子と出力端子とを接続する抵抗素子152を流れる電流ID1は、フォトダイオード170が出力する電流IPDからnpnトランジスタ120のコレクタ電流ID2(電流I1、I2)を差し引いた値に維持される。このため、1段目の差動増幅器150の出力端子の電位が電源130の電位V1より低下せず、当該差動増幅器150の飽和を防止することができる。

【0029】

【発明の効果】

本発明によれば、第2のnpnトランジスタのベースに接続された電源の電位を適切な値に設定しさえすれば、電流/電圧変換器の出力端子の電位が低下したときに、入力電流の一部を第2のnpnトランジスタのコレクタへ分流することにより、電流/電圧変換器の出力端子の電位が低下することを防止し、当該電流/電圧変換器の飽和を防止することが可能となる。

【図面の簡単な説明】

【図1】本実施形態のPDICの回路図である

【図2】従来のPDICの回路図である

【符号の説明】

100 リミッタ回路

110、120 npnトランジスタ

130 電源

140、152、154、162、164、180 抵抗素子

142、144 変圧器

150、160 差動増幅器

170 フォトダイオード

Claims (3)

- 入力電流に応じた電圧の信号を出力する電流/電圧変換器が飽和することを防止するリミッタ回路において、

ベースが前記電流/電圧変換器の出力端子に接続される第1のnpnトランジスタと、

ベースが電源に接続され、コレクタが前記電流/電圧変換器の入力端子に接続される第2のnpnトランジスタと、

前記第1及び第2のnpnトランジスタのエミッタ同士を接続する抵抗素子と、

を備えることを特徴とするリミッタ回路。 - 請求項1に記載のリミッタ回路において、

前記入力電流は、光が入射されたフォトダイオードから入射されることを特徴とするリミッタ回路。 - 請求項1又は2に記載のリミッタ回路において、

前記電流/電圧変換器は、差動増幅器であることを特徴とするリミッタ回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002198906A JP2004040730A (ja) | 2002-07-08 | 2002-07-08 | リミッタ回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002198906A JP2004040730A (ja) | 2002-07-08 | 2002-07-08 | リミッタ回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004040730A true JP2004040730A (ja) | 2004-02-05 |

Family

ID=31706230

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002198906A Pending JP2004040730A (ja) | 2002-07-08 | 2002-07-08 | リミッタ回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004040730A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007028372A (ja) * | 2005-07-20 | 2007-02-01 | Matsushita Electric Ind Co Ltd | 受光増幅回路およびそれを用いた光ピックアップ装置 |

-

2002

- 2002-07-08 JP JP2002198906A patent/JP2004040730A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007028372A (ja) * | 2005-07-20 | 2007-02-01 | Matsushita Electric Ind Co Ltd | 受光増幅回路およびそれを用いた光ピックアップ装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7057423B2 (en) | Current-voltage transforming circuit employing limiter circuit | |

| US6710915B2 (en) | Light amplifier device and optical pickup device employing it | |

| JP4397841B2 (ja) | 受光アンプ回路およびそれを備えた光ピックアップ装置 | |

| US8055139B2 (en) | Light receiver | |

| US7427738B2 (en) | Light-receiving amplifier and optical pickup device | |

| TW200301842A (en) | Photo-detector amplifier circuit for optical disk device | |

| JP3192295B2 (ja) | 光受信装置 | |

| JP2004040730A (ja) | リミッタ回路 | |

| JPH0516508Y2 (ja) | ||

| JP4148045B2 (ja) | フォトダイオード回路 | |

| CN1388924A (zh) | 电流镜像电路 | |

| US6768384B1 (en) | High-speed differential preamplifier | |

| JP3535029B2 (ja) | 受光増幅回路 | |

| JP3844544B2 (ja) | 光受信回路 | |

| JP2004288243A (ja) | 受光アンプ回路およびそれを備えた光ピックアップ装置 | |

| JPH10107563A (ja) | アナログスイッチ回路およびこれを用いた受光増幅装置 | |

| JP4107067B2 (ja) | 光受信器 | |

| JP2005252810A (ja) | 電流電圧変換回路 | |

| JP2004032003A (ja) | 増幅器 | |

| JP2005210147A (ja) | 受光アンプ回路及びそれを備える光ピックアップ素子 | |

| JP2923169B2 (ja) | 受光増幅装置 | |

| JP3434334B2 (ja) | 受光増幅装置 | |

| JP5255533B2 (ja) | 受光回路 | |

| JP3267184B2 (ja) | 光電式煙感知器 | |

| JP2006101110A (ja) | 電流電圧変換回路およびそれを用いた光ピックアップ装置 |