-

Diese Erfindung bezieht sich im allgemeinen auf den Bereich von elektrischen Kontakten und spezieller auf Verfahren für die Herstellung von elektrischen Kontakten.

-

Existierende elektrische Kontaktkonzepte umfassen Zwischenanordnungseinrichtungen, die aus einem elastomeren Material konstruiert sind, und Zwischenanordnungseinrichtungen, die aus Kugeln aus Draht konstruiert sind. Beide diese Lösungen weisen Einschränkungen auf, die ihrem Konzept eigen sind. Aktuelle elastomere Materialien können im Hinblick auf Zeit und Temperatur keine adäquate Kontaktfederkraft aushalten und weisen einen kleinen Bereich von Arbeitshöhen auf. Zwischenanordnungseinrichtungen, die aus Kugeln aus Draht konstruiert sind, sind zerbrechlich, neigen dazu, sich zu lösen, erfordern oft eine kostenaufwendige Inspektion und liefern einen eingeschränkten Betrag eines Kontaktwegs.

-

Die Patentveröffentlichung

US-5,173,055 bezieht sich auf eine Flächen-Array-Verbindungseinrichtung zum Miteinanderverbinden von elektronischen Bauteilen, wobei eine Mehrzahl von Kontaktelementen jeweils einen oder mehrere einseitig eingespannte Kontaktfinger aufweisen, die sich ausgehend von einer Seite einer Platte mit den Kontakten, die elektrisch und mechanisch an den Kontaktanschlussflächen eines der Bauteile befestigt sind, schräg nach außen erstrecken.

-

Die Patentveröffentlichung

US 5,152,695 A bezieht sich auf einen elektrischen Verbinder zur Oberflächenbefestigung. Der elektrische Verbinder umfasst eine Plattform mit einseitig eingespannten Federarmen, die sich von derselben schräg nach außen erstrecken. Die Federarme umfassen erhöhte Kontaktoberflächen.

-

Die Patentveröffentlichung

JP 8287983 bezieht sich auf ein Elastomer-Verbindungselement.

-

Es ist eine Aufgabe der vorliegenden Erfindung, ein Verfahren zur Herstellung von elektrischen Kontakten mit weichen Fedderraten, einer hohen Belastbarkeit und erheblichen Kontaktwegen zu schaffen.

-

Diese Aufgabe wird durch ein Verfahren gemäß Anspruch 1 gelöst.

-

Es liegt ein Verfahren zur Herstellung von elektrischen Kontakten unter Verwendung von Metallformungs-, Maskierungs-, Ätz- und Lötverfahren vor. Das Verfahren produziert eine Mehrzahl von spezialisierten elektrischen Kontakten, die in einer Zwischenanordnungseinrichtung oder einem anderen Gerät verwendet werden können, einschließlich nichtpermanenter oder permanenter elektrischer Verbindungen, die einen Kontaktarm, weiche Federraten, Dauerhaftigkeit und erhebliche Kontaktwegbeträge liefern.

-

Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend Bezug nehmend auf die beiliegenden Zeichnungen näher erläutert. Es zeigen:

-

1 eine perspektivische Ansicht eines Ausführungsbeispiels einer gedruckten Schaltungsplatine, die eine Quantität von durchkontaktierten Durchgangslöchern gemäß der vorliegenden Erfindung aufweist.

-

2 eine perspektivische Ansicht eines Ausführungsbeispiels einer Metallage, die eine Quantität von Kuppeln gemäß der vorliegenden Erfindung aufweist.

-

3 eine perspektivische Ansicht der Metallage von 2 nach dem Maskieren und Ätzen der Lage zum Erzeugen einer Quantität von elektrischen Kontakten gemäß der vorliegenden Erfindung.

-

4 eine perspektivische Ansicht der Struktur, die durch Löten der Metallage von 3 auf die gedruckte Schaltungsplatine von 1 gemäß der vorliegenden Erfindung erzeugt wurde.

-

5 eine perspektivische Ansicht der Struktur von 4, nachdem die Verbindungen zwischen den einzelnen elektrischen Kontakten gemäß der vorliegenden Erfindung weggeätzt worden sind.

-

6 eine perspektivische Ansicht der Struktur von 5, nachdem die elektrischen Kontakte gemäß der vorliegenden Erfindung plattiert worden sind.

-

7 ein Flußdiagramm eines Verfahrens zur Erzeugung von elektrischen Kontakten gemäß der vorliegenden Erfindung.

-

8 ein Flußdiagramm eines Verfahrens für die Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen gemäß der vorliegenden Erfindung aufweist.

-

9 ein Flußdiagramm eines Verfahrens für die Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen und Kugelrasterfeld-Kugeln (BGA; BGA = ball grid array = Kugelrasterfeld) gemäß der vorliegenden Erfindung aufweist.

-

10 ein Flußdiagramm eines Verfahrens für die Erzeugung von Mikrospinnen gemäß der vorliegenden Erfindung.

-

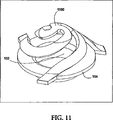

11 eine perspektivische Ansicht eines Ausführungsbeispiels einer dreibeinigen Mikrospinne gemäß der vorliegenden Erfindung.

-

12 eine perspektivische Ansicht eines Ausführungsbeispiels einer Mehrzahl von dreibeinigen Mikrospinnen auf einem Substrat gemäß der vorliegenden Erfindung.

-

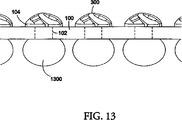

13 eine Querschnittsansicht eines Ausführungsbeispiels der vorliegenden Erfindung, die Mikrospinnen, die auf einer ersten Seite eines Substrats konstruiert sind, und Kugelrasterfeld-Kugeln darstellt, die auf einer zweiten Seite eines Substrats konstruiert sind.

-

1 ist eine perspektivische Ansicht eines Ausführungsbeispiels einer gedruckten Schaltungsplatine, die eine Quantität von durchkontaktierten Durchgangslöchern 106 gemäß der vorliegenden Erfindung aufweist. Bei einem Ausführungsbeispiel der vorliegenden Erfindung ist ein gedrucktes Schaltungsplatinensubstrat 100 auf beiden Seiten des Substrats mit Kupfer plattiert, und das Kupfer ist geätzt, wodurch sich Bereiche von Kupfer 104, die jedes der Löcher 102 umgeben, auf einander gegenüberliegenden Seiten des Substrats ergeben. Obgleich die Kupferbereiche 104 in diesem Ausführungsbeispiel eine irgendwie elliptische Form aufweisen, funktionieren innerhalb des Schutzbereichs der vorliegenden Erfindung andere Formen von Kupferbereichen 104 gleichermaßen gut. Zum Beispiel kann der Kupferbereich 104 bei manchen Ausführungsbeispielen der vorliegenden Erfindung kreisförmig, viereckig oder rechteckig sein oder andere komplexere Formen aufweisen. Obgleich Kupfer ein bevorzugtes Metall ist, können bei anderen Ausführungsbeispielen der vorliegenden Erfindung andere Materialien für die Plattierung verwendet werden. Das Substrat 100 kann eine große Vielfalt an Materialien aufweisen, wobei Glasfaser eine übliche Materialwahl darstellt. Die Löcher 102 werden dann durch die Mitte von jedem Kupferbereich 104 gebohrt. Die Fassungen der Löcher werden dann durchplattiert, um die entsprechenden Kupferbereiche 104 auf den gegenüberliegenden Seiten des Substrats 100 zu verbinden, wodurch ein Array von durchplattierten Durchgangslöchern 106 gebildet wird. Diese gebohrte und plattierte PCB (PCB = printed circuit board = gedruckte Schaltungsplatine) kann durch jedes Standard-PCB-Fertigungssystem erzeugt werden, und wird, wie das Substrat für eine Mehrzahl von spezialisierten elektrischen Kontakten, hierin als Mikrospinnenkontakte bezeichnet. Eine PCB mit diesen Mikrospinnenkontakten kann als eine Zwischenanordnungseinrichtung in einem elektronischen System verwendet werden.

-

2 ist eine perspektivische Ansicht eines Ausführungsbeispiels einer Metallage, die eine Quantität von Kuppeln gemäß der vorliegenden Erfindung aufweist. Eine Metallage 200 wird so verarbeitet, daß sie eine Mehrzahl von kleinen Kuppeln 202 aufweist. Die Metallage 200 kann aus Kupfer oder anderen leitfähigen Metallen bestehen, die für eine spezielle Implementierung der vorliegenden Erfindung benötigt werden. Die Größe der Kuppeln 202 kann auch nach Bedarf für eine spezielle Implementierung der vorliegenden Erfindung variiert werden. Bei einem Ausführungsbeispiel der vorliegenden Erfindung weisen die Kuppeln 202 in der Metallage 200 eine Eins-zu-eins-Entsprechung mit den durchplattieren Löchern 102 auf dem PCB-Substrat 100 auf, jedoch müssen andere Ausführungsbeispiele der vorliegenden Erfindung diese Eins-zu-eins-Entsprechung nicht aufrechterhalten.

-

3 ist eine perspektivische Ansicht der Metallage von 2 nach der Maskierung und Ätzung der Platte 200, um eine Quantität von Mikrospinnen gemäß der Erfindung zu erzeugen, jede auf ihrem eigenen Fundament 304. Nachdem die Metallage 200 maskiert und geätzt worden ist, verbleiben die Mikrospinnen 300, die Fundamente 304 und die Verbinder 302 zwischen den einzelnen Fundamenten 304 und bilden eine geätzte Metallage 310. Es ist zu beachten, daß, obwohl 3 ein regelmäßiges Array von Mikrospinnen 300 zeigt, kein Bedarf besteht, daß die Mehrzahl von Mikrospinnen 300 ein regelmäßiges Array bildet; statt dessen können sie nur an Positionen gebildet sein, wo sie benötigt werden und längere Verbinder 302 verwendet werden, um die Mehrzahl von Mikrospinnen 300 zu verbinden.

-

4 ist eine perspektivische Ansicht eines Ausführungsbeispiels der Struktur, die durch Löten der Metallage von 3 auf die gedruckte Schaltungsplatine von 1 gemäß der vorliegenden Erfindung erzeugt wurde. Die geätzte Metallage 310 wird auf die PCB-Struktur von 1 gelötet, wodurch ein Array von durchplattierten Durchgangslöchern 106 gebildet wird, das durch ein entsprechendes Array von Mikrospinnen 300 bedeckt ist. Das Lot kann auf das Array von durchplattierten Durchgangslöchern 106 siebgedruckt sein, um nur die freiliegenden Metallbereiche 104 abzudecken, wenn gewünscht ist, daß die Mikrospinnen 300 einen elektrischen Kontakt herstellen. An diesem Punkt des Verfahrens sind die einzelnen Mikrospinnen 300 mit den einzelnen Bereichen der Metallplattierung 104, die ihr entsprechendes Durchgangsloch 103 in dem PCB-Substrat 100 umgeben, physisch und elektrisch verbunden.

-

5 ist eine perspektivische Ansicht der Struktur von 4, nachdem die Verbindungen zwischen den einzelnen Mikrospinnen gemäß der vorliegenden Erfindung weggeätzt worden sind. An diesem Punkt des Verfahrens sind alle Mikrospinnen 300 physisch und elektrisch voneinander getrennt worden, indem alle Verbinder 302 zwischen den einzelnen Mikrospinnen 300 weggeätzt worden sind. Es ist zu beachten, daß bei manchen Implementierungen der vorliegenden Erfindung eventuell gewünscht wird, daß bei Vollendung der Zwischenanordnungseinrichtung eine Mehrzahl von Mikrospinnen 300 physisch und elektrisch miteinander verbunden sind. In diesem Fall können die Maskierung und die Ätzung des PCB-Substrats 100 und der dünnen Metallage 200 konzipiert sein, um größere Metallbereiche 104, die die PCB-Durchgangslöcher 102 umgeben, frei zu lassen, so daß eine Mehrzahl von Durchgangslöchern elektrisch verbunden ist und entsprechende Bereiche der dünnen Metallage 200 für ein späteres Löten auf das Array von durchplattieren Durchgangslöchern 106 ungeätzt belassen wird. Ein solches Ausführungsbeispiel der vorliegenden Erfindung kann für Leistungsversorgungsverbindungen nützlich sein, die im allgemeinen einen großen Betrag an Stromführungsfähigkeit erfordern.

-

6 ist eine perspektivische Ansicht der Struktur von 5, nachdem die Mikrospinnen gemäß der vorliegenden Erfindung plattiert worden sind. Bei einem Ausführungsbeispiel der vorliegenden Erfindung können die Mikrospinnen 300 mit Nickel und Gold plattiert sein, wodurch sich ihre Haltbarkeit und Leitfähigkeit verbessert und wodurch ein Array von plattieren Mikrospinnen 600 gebildet wird.

-

7 ist ein Flußdiagramm eines Verfahrens für die Erzeugung von Mikrospinnen 300 gemäß der vorliegenden Erfindung. Bei einem Schritt 702 wird ein PCB-Substrat 100 plattiert, geätzt und gebohrt, um eine Mehrzahl von durchplattierten Durchgangslöchern 106 in dem Substrat 100 zu produzieren. Bei einem Schritt 704 wird eine Quantität von Kuppeln in einer ersten Metallage 200 erzeugt. Bei einem Ausführungsbeispiel der vorliegenden Erfindung kann die erste Metallage 200 aus Kupfer bestehen. Bei einem Schritt 706 wird eine erste Maskenschicht über der ersten Metallage 200 erzeugt. Bei einem Schritt 708 wird die erste Metallage 200 in Bereichen, die nicht durch die Maske geschützt sind, vollständig weggeätzt, wodurch eine Quantität von Mikrospinnen 300, Fundamenten 304 und Verbindern 302 produziert wird. Bei einem Schritt 710, nachdem die Maskenschicht entfernt worden ist, wird die erste Metallage 200, die eine Quantität von Mikrospinnen 300 aufweist, auf die Mehrzahl von durchplattieren Durchgangslöchern 106 in dem Substrat 100 gelötet. Bei einem Schritt 712 wird eine zweite Maskenschicht über der ersten Metallage 200 erzeugt. Bei einem Schritt 714 werden alle Bereiche der ersten Metallage 200, die nicht durch die zweite Maskenschicht geschützt sind, durch Ätzen vollständig entfernt. Bei einem bevorzugten Ausführungsbeispiel der vorliegenden Erfindung werden die Verbinder 302 durch die zweite Maskenschicht ungeschützt belassen und werden im Schritt des Ätzens entfernt. Bei einem Schritt 716 wird die Quantität von Mikrospinnen 300 metallplattiert.

-

Einige Verfahren zum Aufbringen und Strukturieren der ersten Maskenschicht weisen eventuell Schwierigkeiten beim Erzeugen einer adäquaten Maskenschicht über einer unregelmäßigen Oberfläche auf, wie jene, die aus Schritt 704 resultiert (Erzeugen einer Quantität von Kuppeln in einer Metallage). Ferner, können einige Photolithographiesysteme Schwierigkeiten beim Strukturieren einer Maskenschicht über einer unregelmäßigen Oberfläche aufweisen, insbesondere bei den Seiten der Kuppeln. Bei der Verwendung von Maskierungssystemen, die keine adäquate Maskenschicht über einer unregelmäßigen Oberfläche erzeugen können, kann es notwendig sein, die Schritte der vorliegenden Erfindung in einer anderen Ordnung als jener, die in 7 gezeigt ist, auszuführen. Aus diesen Gründen kann es bei einigen Ausführungsbeispielen der vorliegenden Erfindung von Nutzen sein, den Schritt 706 zum Erzeugen einer ersten Maskenschicht über der ersten Metallage vor dem Schritt 704 des Erzeugens einer Quantität von Kuppeln in der ersten Metallage auszuführen.

-

8 ist ein Flußdiagramm eines Verfahrens zur Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen gemäß der vorliegenden Erfindung aufweist. Das Verfahren für die Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen umfaßt, die in diesem Ausführungsbeispiel der vorliegenden Erfindung gezeigt sind, umfaßt die Schritte des Verfahrens, das in 7 gezeigt ist, wobei Schritte hinzugefügt worden sind, um vorzugsweise eine zusätzliche Quantität von Mikrospinnen auf der gegenüberliegenden Seite des gedruckten Schaltungsplatinensubstrats zu erzeugen. Wie in Verbindung mit 7 erörtert worden ist, wird die Quantität von Mikrospinnen 300 bei einem Schritt 716 metallplattiert. Bei einem Schritt 802 wird eine Quantität von Kuppeln in einer zweiten Metallage 200 erzeugt. Nach Wunsch kann dieser Schritt 802 gleichzeitig mit dem Schritt 702 erfolgen. Bei einem Schritt 804 wird eine dritte Maskenschicht über der zweiten Metallage 200 erzeugt. Dieser Schritt 804 kann nach Wunsch gleichzeitig mit dem Schritt 706 erfolgen. Bei einem Schritt 806 wird die zweite Metallage 200 vollständig in den Bereichen weggeätzt, die nicht durch die dritte Maske geschützt sind, wodurch eine Quantität von Mikrospinnen 300 produziert wird. Dieser Schritt 806 kann nach Wunsch gleichzeitig mit dem Schritt 708 erfolgen. Bei einem Schritt 808, nachdem die dritte Maskenschicht entfernt worden ist, wird die zweite Metallage 200, die eine Quantität von Mikrospinnen 300 umfaßt, auf die Mehrzahl von durchplattierten Durchgangslochern 106 gelötet. Dieser Schritt 808 kann nach Wunsch gleichzeitig mit dem Schritt 710 erfolgen. Bei einem Schritt 810 wird eine vierte Maskenschicht über der zweiten Metallage 200 erzeugt. Dieser Schritt 810 kann nach Wunsch gleichzeitig mit dem Schritt 712 erfolgen. Bei einem Schritt 812 werden alle Bereiche der zweiten Metallage 200, die nicht durch die vierte Maskenschicht geschützt ist, vollständig durch Ätzen entfernt. Dieser Schritt 812 kann nach Wunsch gleichzeitig mit dem Schritt 714 erfolgen. Bei einem Schritt 814 wird die zweite Quantität von Mikrospinnen 300 metallplattiert. Dieser Schritt 814 kann nach Wunsch gleichzeitig mit dem Schritt 716 erfolgen. Bei einigen Ausführungsbeispielen der vorliegenden Erfindung kann es erneut wünschenswert sein, die Maskenschichten über den dünnen Metallagen vor dem Bilden der Kuppeln in den dünnen Metallagen zu erzeugen. Dieses Ausführungsbeispiel (8) der vorliegenden Erfindung kann verwendet werden, um eine Dual-Mikrospinnen-Zwischenanordnungseinrichtung zur Verwendung zwischen einer gedruckten Schaltungsplatine und einem Schaltungsmodul, wie einem anwendungsspezifischen integrierten Schaltungs-Gehäuse, oder einem Multi-Chip-Modul zu erzeugen. Die Dual-Mikrospinnen-Zwischenanordnungseinrichtung kann ohne weiteres von der gedruckten Schaltungsplatine ohne kostspielige Überarbeitung der Platine entfernt werden. Dies ermöglicht nach Bedarf schnelle und einfache Veränderungen des Schaltungsmoduls einschließlich Veränderungen im Einsatzgebiet.

-

9 ist ein Flußdiagramm eines Verfahrens für die Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen und Kugelrasterfeld-Kugeln gemäß der vorliegenden Erfindung aufweist. Das Verfahren für die Erzeugung einer Zwischenanordnungseinrichtung, die Mikrospinnen und Kugelrasterfeldkugeln umfaßt, die in diesem Ausführungsbeispiel der vorliegenden Erfindung gezeigt sind, umfaßt die Schritte des Verfahrens, das in 7 gezeigt ist, wobei Schritte hinzugefügt worden sind, um vorzugsweise eine Quantität von BGA-Kugeln auf der gegenüberliegenden Seite des gedruckte-Schaltungsplatine-Substrats zu erzeugen. Wie in Verbindung mit 7 erörtert worden ist, wird die Quantität von Mikrospinnen 300 bei einem Schritt 716 metallplattiert. Bei einem Schritt 902 werden die Kugelrasterfeldkugeln an der Seite des Substrats gegenüber den Mikrospinnen angebracht.

-

Bei einigen Ausführungsbeispielen der vorliegenden Erfindung kann es erneut wünschenswert sein, die Maskenschicht über den dünnen Metallagen vor dem Bilden der Kuppeln in den dünnen Metallagen zu erzeugen. Durch Erzeugen einer Zwischenanordnungseinrichtung, die Mikrospinnen auf der einen Seite und Kugelrasterfeldkugeln auf der anderen Seite aufweist, kann ein dünneres Gold auf einer gedruckten Schaltungsplatine verwendet werden, an der die BGA-Seite der Zwischenanordnungseinrichtung angebracht ist. Dies ermöglicht die Verwendung von Standard-BGA-Anbringungsprozessen, um die Zwischenanordnungseinrichtung an der gedruckten Schaltungsplatine anzubringen. Obgleich diese Implementierung der vorliegenden Erfindung (9) eine kostengünstigere Plattierung auf der gedruckten Schaltungsplatine ermöglicht, ermöglicht die Entfernbarkeit der Dual-Mikrospinnen-Zwischenanordnungseinrichtung (8) eine einfachere Überarbeitung als die Mikrospinnen-BGA-Zwischenanordnungseinrichtung.

-

10 ist ein Flußdiagramm eines Verfahrens für die Erzeugung von Mikrospinnen gemäß der vorliegenden Erfindung. Bei einem Ausführungsbeispiel der vorliegenden Erfindung, das dem Verfahren von 7 ähnlich ist, wird eine Metallage in eine Mikrospinnenkonfiguration geätzt, bevor die Mikrospinnen gewölbt (in eine domförmige Form gebracht werden) werden. Dieses Verfahren ermöglicht die Maskierung und Ätzung der Metallage vor der Kuppelbildung, wodurch die Schwierigkeiten des Maskierens und Ätzens einer mit Kuppeln versehenen Oberfläche eliminiert werden. Bei einem Schritt 702 wird ein PCB-Substrat 100 plattiert, geätzt und gebohrt, um eine Mehrzahl von durchplattierten Durchgangslöchern 106 zu produzieren. Bei einem Schritt 706 wird eine erste Maskenschicht über einer ersten Metallage 200 erzeugt. Bei einem Schritt 708 wird die erste Metallage 200 vollständig in den Bereichen, die nicht durch die Maske geschützt sind, weggeätzt, wodurch eine Quantität von Mikrospinnen 300, Fundamenten 304 und Verbindern 302 produziert wird. Bei einem Schritt 1000, wird ein im wesentlichen inkompressibles Material zwischen den Beinen der Mikrospinnen, die in die Metallage geätzt sind, aufgebracht. Das im wesentlichen inkompressible Material wird verwendet, um zu verhindern, daß sich die Beine der Mikrospinne während des Schritts 704 des Bildens der Kuppeln unordnungsgemäß verbiegen. Es kann aus einem Material, wie z. B. Gips, bestehen, und ein Ausführungsbeispiel der vorliegenden Erfindung verwendet einen Siebdruckprozeß zum Aufbringen des Materials. Anschließend wird bei einem Schritt 704 eine Quantität von Kuppeln in der ersten Metallage 200 erzeugt. Bei einem Schritt 1002 wird das im wesentlichen inkompressible Material zwischen den Beinen der Mikrospinnen entfernt. Abhängig von dem verwendeten Material, kann das im wesentlichen inkompressible Material durch Auflösen oder andere äquivalente Prozesse entfernt werden. Bei einem Schritt 710, nachdem die Maskenschicht entfernt worden ist, wird die erste Metallage 200, die eine Quantität von Mikrospinnen 300 umfaßt, auf die Mehrzahl von durchplattierten Durchgangslöchern 106 gelötet. Bei einem Schritt 712 wird eine zweite Maskenschicht über der ersten Metallage 200 erzeugt. Bei einem Schritt 714 werden alle Bereiche der ersten Metallage 200, die nicht durch die zweite Maskenschicht geschützt sind, vollständig durch Ätzen entfernt. Bei einem Schritt 716 wird die Quantität von Mikrospinnen 300 metallplattiert. 11 ist eine perspektivische Ansicht eines Ausführungsbeispiels einer dreibeinigen Mikrospinne gemäß der vorliegenden Erfindung. Eine dreibeinige Mikrospinne 1100 ist gezeigt, die mit dem Metallbereich 104, der ein durchplattiertes Loch 102 in einem Substrat 100 umgibt, verbunden ist.

-

12 ist eine perspektivische Ansicht eines Ausführungsbeispiels einer Mehrzahl von dreibeinigen Mikrospinnen 1100 auf einem Substrat 100 gemäß der vorliegenden Erfindung. Obgleich diese Figur ein regelmäßiges Array von Mikrospinnen 1100 zeigt, können andere Ausführungsbeispiele der vorliegenden Erfindung ein unregelmäßiges Array von Mikrospinnen 1100 verwenden, wenn dies gemäß der geplanten Verwendung der Mehrzahl von Mikrospinnen 1100 gewünscht ist. Ferner können die Mikrospinnen innerhalb des Schutzbereichs der vorliegenden Erfindung mit einer beliebigen Anzahl von Beinen (größer 1) konstruiert sein, wenn dies gemäß einer geplanten Verwendung gewünscht ist.

-

Bei einem spezifischen Ausführungsbeispiel der vorliegenden Erfindung sind die Mikrospinnen 300 vorzugsweise auf einer ersten Seite des Substrats 100 konstruiert, und die Kugelrasterfeldkugeln 1000 sind vorzugsweise auf einer zweiten Seite des Substrats 100 konstruiert, wodurch eine Zwischenanordnungseinrichtung zur Verwendung in nichtpermanent befestigten elektronischen Geräten, wie einem Multi-Chip-Modul (MCM), auf einer Schaltungsplatine erzeugt wird. 13 ist eine Querschnittsansicht eines solchen Ausführungsbeispiels. Das Ausführungsbeispiel der vorliegenden Erfindung, das in 13 gezeigt ist, zeigt eine Mehrzahl von Mikrospinnen 300, die auf einer ersten Seite eines Substrats konstruiert sind, und Kugelrasterfeldkugeln 1300, die auf einer zweiten Seite eines Substrats 100 konstruiert sind, die durch durchplattierte Löcher 102 verbunden sind, die durch Metallbereiche 104 umgeben sind, die die Mikrospinnen 300 kontaktieren,. Dieses Ausführungsbeispiel der vorliegenden Erfindung kann als eine Zwischenanordnungseinrichtung zur Verwendung in nichtpermanent befestigten elektronischen Geräten, wie z. B. einem MCM, auf einer eine Schaltungsplatine eingesetzt werden, während die Zwischenanordnungseinrichtung an der Schaltungsplatine durch die Kugelrasterfeldkugeln 1300 befestigt ist. Das Ausführungsbeispiel der vorliegenden Erfindung kann unter Verwendung des Prozesses, der in Verbindung mit 9 beschrieben ist, hergestellt werden.