DE102011005690B4 - Leistungshalbleitermodul - Google Patents

Leistungshalbleitermodul Download PDFInfo

- Publication number

- DE102011005690B4 DE102011005690B4 DE102011005690.4A DE102011005690A DE102011005690B4 DE 102011005690 B4 DE102011005690 B4 DE 102011005690B4 DE 102011005690 A DE102011005690 A DE 102011005690A DE 102011005690 B4 DE102011005690 B4 DE 102011005690B4

- Authority

- DE

- Germany

- Prior art keywords

- wiring board

- semiconductor chip

- insulating wiring

- heat dissipation

- dissipation plate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 58

- 230000017525 heat dissipation Effects 0.000 claims abstract description 20

- 229910000679 solder Inorganic materials 0.000 claims abstract description 17

- 229920001296 polysiloxane Polymers 0.000 claims abstract description 13

- 239000003822 epoxy resin Substances 0.000 claims abstract description 5

- 230000002093 peripheral effect Effects 0.000 claims abstract description 5

- 229920000647 polyepoxide Polymers 0.000 claims abstract description 5

- 229920001721 polyimide Polymers 0.000 claims abstract description 5

- 229920002379 silicone rubber Polymers 0.000 claims abstract description 5

- 239000004945 silicone rubber Substances 0.000 claims abstract description 5

- 239000009719 polyimide resin Substances 0.000 claims abstract description 4

- 238000005192 partition Methods 0.000 claims description 4

- 238000009413 insulation Methods 0.000 description 11

- 230000007547 defect Effects 0.000 description 8

- 239000000758 substrate Substances 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/16—Fillings or auxiliary members in containers or encapsulations, e.g. centering rings

- H01L23/18—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device

- H01L23/24—Fillings characterised by the material, its physical or chemical properties, or its arrangement within the complete device solid or gel at the normal operating temperature of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/04—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls

- H01L23/053—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls the container being a hollow construction and having an insulating or insulated base as a mounting for the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3157—Partial encapsulation or coating

- H01L23/3185—Partial encapsulation or coating the coating covering also the sidewalls of the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/58—Structural electrical arrangements for semiconductor devices not otherwise provided for, e.g. in combination with batteries

- H01L23/60—Protection against electrostatic charges or discharges, e.g. Faraday shields

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

- H01L25/072—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/27—Manufacturing methods

- H01L2224/27011—Involving a permanent auxiliary member, i.e. a member which is left at least partly in the finished device, e.g. coating, dummy feature

- H01L2224/27013—Involving a permanent auxiliary member, i.e. a member which is left at least partly in the finished device, e.g. coating, dummy feature for holding or confining the layer connector, e.g. solder flow barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/291—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/2919—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/32227—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the layer connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/45124—Aluminium (Al) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83009—Pre-treatment of the layer connector or the bonding area

- H01L2224/83051—Forming additional members, e.g. dam structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83909—Post-treatment of the layer connector or bonding area

- H01L2224/83951—Forming additional members, e.g. for reinforcing, fillet sealant

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/06—Polymers

- H01L2924/0665—Epoxy resin

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Dispersion Chemistry (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

Leistungshalbleitermodul, aufweisend:eine Wärmeableitungsplatte (1);eine isolierende Verdrahtungsplatine (13) mit einer oberen Elektrode (14) und einer unteren Elektrode (15), wobei die untere Elektrode (15) durch ein erstes Lot (16) mit der Wärmeableitungsplatte (1) verbunden ist;einen Halbleiterchip (18), der mit der oberen Elektrode (14) durch ein zweites Lot (17) verbunden ist;einen schwach dielektrischen Film (20), welcher Seiten des Halbleiterchips (18) und des zweiten Lots (17) bedeckt;ein Gehäuse (9) auf der Wärmeableitungsplatte (1), welches die isolierende Verdrahtungsplatine (13) und den Halbleiterchip (18) umgibt; undein Silikongel (11), welches in das Gehäuse (9) eingefüllt ist und die isolierende Verdrahtungsplatine (13), den Halbleiterchip (18) und den dielektrischen Film (20) bedeckt, wobeider schwach dielektrische Film (20) aus einem der folgenden Bestandteile aufgebaut ist: Silikongummi, Polyimid und Epoxidharz, unddie isolierende Verdrahtungsplatine (13) einen konvexen Abschnitt (21) aufweist, welcher von einem umfangsseitigen Abschnitt einer unteren Oberfläche der isolierenden Verdrahtungsplatine (13) aus nach unten vorsteht.

Description

- Die Erfindung betrifft ein Leistungshalbleitermodul, das eine isolierende Verdrahtungsplatine vom Doppelseitenelektrodentyp aufweist, und insbesondere ein Leistungshalbleitermodul, das Isolationsdefekte reduzieren kann.

- In den letzten Jahren wurde ein Leistungshalbleitermodul in einem Leistungswandler zum Steuern elektrischer Vorrichtungen, wie beispielsweise Motoren, eingesetzt. Bei dem Leistungshalbleitermodul ist eine isolierende Verdrahtungsplatine vom Doppelseitenelektrodentyp mit einem Lot auf einer Wärmeableitungsplatte angebracht, und Halbleiterchips sind mit dem Lot auf der isolierenden Verdrahtungsplatine angebracht. Ein Gehäuse verkapselt die isolierende Verdrahtungsplatine und die Halbleiterchips, und das Gehäuse ist mit Silikongel gefüllt (siehe beispielsweise

JP 2002-76190 A -

DE 10 2007 008 912 B4 offenbart einen Halbleiterchip, der über ein isolierendes Substrat auf einem Kühlkörper angebracht ist. - Dabei ist das isolierende Substrat mittels Lot auf einem Kühlkörper angebracht. Die Druckschrift widmet sich dem Problem, dass durch wiederholte Aufheiz- und Abkühlvorgänge Risse im Lot entstehen, die wegen der geringen thermischen Leitfähigkeit von Luft zu einer verringerten Wärmeableitung zum Kühlkörper führen. Gemäß

DE 10 2007 008 912 B4 fließt ein Füllstoff mit größerer thermischer Leitfähigkeit als jener von Luft und höherer Fluidität als jener von Silikongel in die Risse, wodurch die Wärmeableitung verbessert wird. - Wenn ein Strom angelegt wird, können aufgrund von Temperaturveränderungen Blasen aus einem Lot im Silikongel im umfangsseitigen Teil des Moduls ausgebildet werden. Durch diese Blasen kann ein Isolationsdefekt auftreten. Insbesondere bewirken Blasen im umfangsseitigen Teil der isolierenden Verdrahtungsplatine vom Doppelseitenelektrodentyp, welche direkt auf der Wärmeableitungsplatte angebracht ist, Isolationsdefekte.

- Im Hinblick auf die oben beschriebenen Probleme ist es eine Aufgabe der Erfindung, ein Leistungshalbleitermodul anzugeben, welches Isolationsdefekte verringern kann.

- Die Aufgabe wird erfindungsgemäß durch zwei Alternativen eines Leistungshalbleitermoduls nach Anspruch 1 und Anspruch 2 gelöst. Bevorzugte Ausgestaltungen sind in den Unteransprüchen angegeben.

- Die Erfindung ermöglicht es, Isolationsdefekte zu reduzieren.

- Andere und weitere Aufgaben, Merkmale und Vorteile der Erfindung gehen deutlicher aus der folgenden Beschreibung hervor.

- Figurenliste

-

-

1 ist eine Schnittansicht, welche ein Leistungshalbleitermodul gemäß eines ersten Beispiels zur Erläuterung der Erfindung zeigt. -

2 ist eine Draufsicht, welche ein Leistungshalbleitermodul gemäß des ersten Beispiels zur Erläuterung der Erfindung zeigt. -

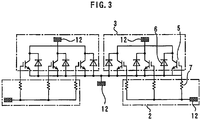

3 ist eine Äquivalenzschaltung eines Schaltungsblocks des in2 gezeigten Leistungshalbleitermoduls. -

4 ist eine vergrößerte Schnittansicht, welche ein Leistungshalbleitermodul gemäß des ersten Beispiels zur Erläuterung der Erfindung zeigt. -

5 ist eine vergrößerte Schnittansicht, welche ein Leistungshalbleitermodul gemäß eines zweiten Beispiels zur Erläuterung der Erfindung zeigt. -

6 ist eine vergrößerte Schnittansicht, welche ein Leistungshalbleitermodul gemäß gemäß einer Ausführungsform einer Alternative nach Anspruch 1 zeigt. -

7 ist eine vergrößerte Schnittansicht, welche ein Leistungshalbleitermodul gemäß gemäß einer Ausführungsform einer Alternative nach Anspruch 2 zeigt. -

8 ist eine vergrößerte Schnittansicht, welche ein Leistungshalbleitermodul gemäß eines dritten Beispiels zur Erläuterung der Erfindung zeigt. - DETAILLIERTE BESCHREIBUNG DER AUSFÜHRUNGSFORMEN

- Ein Leistungshalbleitermodul gemäß den erläuternden Beispielen und Ausführungsformen der beiden Alternativen der Erfindung wird mit Bezug auf die Figuren in der Zeichnung beschrieben. Die gleichen Komponenten werden durch dieselben Bezugszeichen gekennzeichnet, und ihre wiederholte Beschreibung wird ausgelassen.

- Erstes Beispiels zur Erläuterung der Erfindung

-

1 ist eine Schnittansicht, welche ein Leistungshalbleitermodul gemäß des ersten Beispiels zur Erläuterung der Erfindung zeigt, und2 ist eine Draufsicht auf dieses. Das Leistungshalbleitermodul beinhaltet Schaltungsblöcke, welche dafür konfiguriert sind, eine hohe Durchschlagsspannung und gute Stromkenndaten zu erreichen, indem eine Anzahl an Bipolartransistoren mit isolierter Gateelektrode (IGBT) parallel miteinander verbunden werden und gemeinsame Kollektoranschlüsse, Emitteranschlüsse und Gateanschlüsse vorgesehen werden.3 ist eine Äquivalenzschaltung eines Schaltungsblocks in dem Leistungshalbleitermodul, das in2 gezeigt ist. - Auf einer Wärmeableitungsplatte

1 sind Verdrahtungsplatinen2 für Antriebsschaltungen, Verdrahtungsplatinen3 für Leistungshalbleiterschaltungen und Verdrahtungsplatinen4 für Relaisschaltungen installiert. Diese Schaltungsverdrahtungsplatinen sind isolierende Verdrahtungsplatinen, beispielsweise aus Keramik, welche Verdrahtungsstrukturen aus Kupfer, Aluminium oder dergleichen auf beiden Oberflächen aufweisen. Auf den Verdrahtungsplatinen3 für Leistungshalbleiterschaltungen sind IGBTs5 und Freilaufdioden6 angebracht. Chipwiderstände7 sind auf den Verdrahtungsplatinen2 für die Antriebsschaltungen verbunden. - Die Emitter der IGBTs

5 und die Anoden der Freilaufdioden6 sind mit den Verdrahtungsstrukturen der Verdrahtungsplatinen für Relaisschaltungen durch Drähte8 aus Al verbunden. Die Gates der IGBTs5 sind mit den Verdrahtungsstrukturen der Verdrahtungsplatine2 für Antriebsschaltungen durch Drähte8 aus Al verbunden. Die Kollektoren der IGBTs5 und die Kathoden der Freilaufdioden6 sind miteinander durch die Verdrahtungsstrukturen der Verdrahtungsplatinen3 für Leistungshalbleiterschaltungen verbunden. - Ein Kunststoffgehäuse

9 ist auf der Wärmeableitungsplatte1 so vorhanden, dass es die Verdrahtungsplatine2 für Antriebsschaltungen, die Verdrahtungsplatinen3 für Leistungshalbleiterschaltungen und die Verdrahtungsplatinen4 für Relaisschaltungen umgibt, und eine Abdeckung10 ist auf dem oberen Abschnitt des Gehäuses9 platziert. Das Gehäuse9 ist mit Silikongel11 gefüllt, um Luftdichtigkeit und Isolation aufrecht zu erhalten. Jede Schaltungsverdrahtungsplatine ist mit einem Elektrodenanschlussverbindungsbereich12 ausgestattet. Am Elektrodenanschlussverbindungsbereich12 ist ein Elektrodenanschluss (nicht gezeigt) zum Verwirklichen einer elektrischen Verbindung nach außen installiert. Obwohl hier die Verdrahtungsplatine3 für Leistungshalbleiterschaltungen und die Verdrahtungsplatine4 für Relaisschaltungen separat auf verschiedenen isolierenden Verdrahtungsplatinen angebracht sind, können beide auf unterschiedliche Verdrahtungsstrukturen bildenden Bereichen einer isolierenden Verdrahtungsplatine vorhanden sein. -

4 ist eine vergrößerte Querschnittsansicht, welche ein Leistungshalbleitermodul gemäß des ersten Beispiels zur Erläuterung der Erfindung zeigt. Eine isolierende Verdrahtungsplatine13 weist eine obere Elektrode14 und eine untere Elektrode15 auf. Die untere Elektrode15 der isolierenden Verdrahtungsplatine13 ist an der Wärmeableitungsplatte1 durch ein Lot16 angebracht. Ein Halbleiterchip18 aus Si ist auf der oberen Elektrode14 der isolierenden Verdrahtungsplatine13 durch ein Lot17 angebracht. Ein Draht8 aus Al ist an den Halbleiterchip18 gebondet (d.h. kontaktiert diesen). Die isolierende Verdrahtungsplatine13 entspricht der Verdrahtungsplatine3 für Leistungshalbleiterschaltungen, die in den1 bis3 gezeigt ist, und der Halbleiterchip18 entspricht dem IGBT5 oder der Freilaufdiode6 , die in den1 bis3 gezeigt ist. - Ein schwach dielektrischer Film

19 bedeckt Seiten der unteren Elektrode15 und des Lots16 . Ein schwach dielektrischer Film20 bedeckt Seiten des Halbleiterchips18 und des Lots17 . Die schwach dielektrischen Filme19 und20 sind aus Silikongummi, Polyimid oder Epoxidharz aufgebaut. Insbesondere wird, wenn Silikongummi für die schwach dielektrischen Filme19 und20 eingesetzt wird, die Montage erleichtert. Wenn Polyimid verwendet wird, ist die Wärmebeständigkeit verbessert. Wenn Expoxidharz eingesetzt wird, sind die Wärmezykluseigenschaften verbessert. Ein Silikongel11 (flexibler Isolator), das in das Gehäuse9 eingefüllt ist, bedeckt die isolierende Verdrahtungsplatine13 , den Halbleiterchip18 und die schwach dielektrischen Filme19 und20 . - Wie vorstehend beschrieben, bedeckt in dem gezeigten Beispiel der schwach dielektrische Film

19 die Seiten des Lots16 und der unteren Elektrode15 und der schwach dielektrische Film20 bedeckt die Seiten des Lots17 und des Halbleiterchips18 . Hierdurch kann die Erzeugung von Blasen aus dem Lot17 unterdrückt werden. Deshalb können Isolationsdefekte reduziert werden, und eine Erhöhung der Lebensdauer der Produkte wird möglich. - Zweites Beispiel zur Erläuterung der Erfindung

-

5 ist eine vergrößerte Querschnittsansicht, welche ein Leistungshalbleitermodul gemäß des zweiten Beispiels zur Erläuterung der Erfindung zeigt. Der schwach dielektrische Film19 bedeckt die gesamte obere Oberfläche der Wärmeableitungsplatte1 unterhalb der isolierenden Verdrahtungsplatine13 . Andere Konfigurationen sind identisch mit den Konfigurationen des ersten erläuternden Beispiels. Hierdurch kann die Erzeugung von Blasen aus dem Lot16 zuverlässiger unterdrückt werden als gemäß dem ersten erläuternden Beispiel. - Eine Ausführungsform der Alternative der Erfindung gemäß Anspruch 1

-

6 ist eine vergrößerte Querschnittsansicht, welche ein Leistungshalbleitermodul gemäß einer Ausführungsform der ersten Alternative zeigt. Obwohl der schwach dielektrische Film19 nicht ausgebildet ist, weist die isolierende Verdrahtungsplatine13 darüber hinaus einen konvexen Abschnitt21 auf, der von dem umfangsseitigen Abschnitt der unteren Oberfläche aus nach unten vorsteht. Andere Konfigurationen sind identisch mit den Konfigurationen des ersten Beispiels zur Erläuterung der Erfindung. Hierdurch werden Blasen, die aus dem Lot16 erzeugt werden, auf der unteren Oberflächenseite der isolierenden Verdrahtungsplatine13 durch den konvexen Abschnitt21 gestoppt. Deshalb können Isolationsdefekte verringert werden. - Eine Ausführungsform der Alternative der Erfindung gemäß Anspruch 2

-

7 ist eine vergrößerte Querschnittsansicht, welche ein Leistungshalbleitermodul gemäß einer Ausführungsform der zweiten Alternative zeigt. Eine Trennwand22 ist auf der inneren Wand des Gehäuses9 ausgebildet. Die Trennwand22 ist zwischen dem Verbindungsabschnitt23 von der Wärmeableitungsplatte1 zum Gehäuse9 und der oberen Oberfläche der isolierenden Verdrahtungsplatine13 platziert. Andere Konfigurationen sind identisch mit den Konfigurationen des ersten Beispiels zur Erläuterung der Erfindung. - Blasen, welche von dem Verbindungsabschnitt

23 erzeugt werden, werden auf der Seite des Gehäuses9 durch die Trennwand22 gestoppt und bewegen sich nicht zur oberen Oberfläche der isolierenden Verdrahtungsplatine13 . Deshalb können Isolationsdefekte weiter reduziert werden. - Der Abstand vom Verbindungsabschnitt

23 zur oberen Oberfläche der isolierenden Verdrahtungsplatine13 ist größer als der Abstand der Lote16 und17 von der oberen Oberfläche der isolierenden Verdrahtungsplatine13 . Deshalb ist die Möglichkeit, dass die Blasen einen Isolationsdefekt verursachen, gering. Jedoch ist diese Ausführungsform effektiv, wenn weiter eine hohe Zuverlässigkeit gefordert wird. - Drittes Beispiel zur Erläuterung der Erfindung

-

8 ist eine vergrößerte Querschnittsansicht, welche ein Leistungshalbleitermodul gemäß einem dritten Beispiel zur Erläuterung der Erfindung zeigt. Bei den vorangegangenen erläuternden Beispielen und Ausführungsformen der beiden Alternativen der Erfindung bedeckt das Silikongel11 alle Drähte8 aus Al. Demgegenüber ist bei dem dritten Beispiel zur Erläuterung der Erfindung die Höhe des Silikongels11 so begrenzt, dass sie etwa einige Millimeter über der oberen Oberfläche des Halbleiterchips18 liegt. Hierdurch ist ein Teil der Drähte8 aus Al nicht mit Silikongel11 bedeckt. Andere Konfigurationen sind identisch mit den Konfigurationen des ersten erläuternden Beispiels. - Selbst wenn Blasen aus den Loten

16 und17 aufgrund einer fehlerhaften Ausbildung der schwach dielektrischen Filme19 und20 erzeugt werden, erreichen die Blasen leicht die obere Oberfläche des Silikongels11 und werden in die Luft abgegeben. Deshalb können Isolationsdefekte weiter reduziert werden.

Claims (4)

- Leistungshalbleitermodul, aufweisend: eine Wärmeableitungsplatte (1); eine isolierende Verdrahtungsplatine (13) mit einer oberen Elektrode (14) und einer unteren Elektrode (15), wobei die untere Elektrode (15) durch ein erstes Lot (16) mit der Wärmeableitungsplatte (1) verbunden ist; einen Halbleiterchip (18), der mit der oberen Elektrode (14) durch ein zweites Lot (17) verbunden ist; einen schwach dielektrischen Film (20), welcher Seiten des Halbleiterchips (18) und des zweiten Lots (17) bedeckt; ein Gehäuse (9) auf der Wärmeableitungsplatte (1), welches die isolierende Verdrahtungsplatine (13) und den Halbleiterchip (18) umgibt; und ein Silikongel (11), welches in das Gehäuse (9) eingefüllt ist und die isolierende Verdrahtungsplatine (13), den Halbleiterchip (18) und den dielektrischen Film (20) bedeckt, wobei der schwach dielektrische Film (20) aus einem der folgenden Bestandteile aufgebaut ist: Silikongummi, Polyimid und Epoxidharz, und die isolierende Verdrahtungsplatine (13) einen konvexen Abschnitt (21) aufweist, welcher von einem umfangsseitigen Abschnitt einer unteren Oberfläche der isolierenden Verdrahtungsplatine (13) aus nach unten vorsteht.

- Leistungshalbleitermodul, aufweisend: eine Wärmeableitungsplatte (1); eine isolierende Verdrahtungsplatine (13) mit einer oberen Elektrode (14) und einer unteren Elektrode (15), wobei die untere Elektrode (15) durch ein erstes Lot (16) mit der Wärmeableitungsplatte (1) verbunden ist; einen Halbleiterchip (18), der mit der oberen Elektrode (14) durch ein zweites Lot (17) verbunden ist; einen ersten schwach dielektrischen Film (19), welcher Seiten der unteren Elektrode (15) und des ersten Lots (16) bedeckt; einen zweiten schwach dielektrischen Film (20), welcher Seiten des Halbleiterchips (18) und des zweiten Lots (17) bedeckt; ein Gehäuse (9) auf der Wärmeableitungsplatte (1), welches die isolierende Verdrahtungsplatine (13) und den Halbleiterchip (18) umgibt; ein Silikongel (11), welches in das Gehäuse (9) eingefüllt ist und die isolierende Verdrahtungsplatine (13), den Halbleiterchip (18) und die ersten und zweiten schwach dielektrischen Filme (19, 20) bedeckt, und eine Trennwand (22), welche auf der inneren Wand des Gehäuses (9) ausgebildet ist und welche zwischen einem Verbindungsabschnitt (23) der Wärmeableitungsplatte (1) mit dem Gehäuse (9) und einer oberen Oberfläche der isolierenden Verdrahtungsplatine (13) platziert ist, wobei die ersten und zweiten schwach dielektrischen Filme (19, 20) aus einem der folgenden Bestandteile aufgebaut sind: Silikongummi, Polyimid und Epoxidharz.

- Leistungshalbleitermodul nach

Anspruch 2 , dadurch gekennzeichnet, dass der erste schwach dielektrische Film (19) die gesamte obere Oberfläche der Wärmeableitungsplatte (1) unterhalb der isolierenden Verdrahtungsplatine (13) bedeckt. - Leistungshalbleitermodul nach einem der

Ansprüche 1 bis3 , aufweisend einen Draht (8), der an den Halbleiterchip (18) gebondet ist, wobei ein Teil des Drahtes (8) frei von Silikongel (11) ist.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010-091291 | 2010-04-12 | ||

| JP2010091291A JP5212417B2 (ja) | 2010-04-12 | 2010-04-12 | パワー半導体モジュール |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| DE102011005690A1 DE102011005690A1 (de) | 2011-10-13 |

| DE102011005690B4 true DE102011005690B4 (de) | 2021-10-28 |

Family

ID=44658269

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| DE102011005690.4A Active DE102011005690B4 (de) | 2010-04-12 | 2011-03-17 | Leistungshalbleitermodul |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8558361B2 (de) |

| JP (1) | JP5212417B2 (de) |

| CN (1) | CN102214622B (de) |

| DE (1) | DE102011005690B4 (de) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5328827B2 (ja) * | 2010-05-28 | 2013-10-30 | 三菱電機株式会社 | パワーモジュール構造、その構造を有するパワーモジュール、およびその構造の製造方法 |

| EP2793258A4 (de) * | 2011-12-12 | 2015-11-11 | Mitsubishi Materials Corp | Strommodulsubstrat, substrat für ein strommodul mit kühlkörper, strommodul, paste zur herstellung einer flusskomponenteneindringungsverhinderungsschicht sowie bindungsverfahren für einen zu bindenden artikel |

| US8847328B1 (en) * | 2013-03-08 | 2014-09-30 | Ixys Corporation | Module and assembly with dual DC-links for three-level NPC applications |

| US9704768B2 (en) * | 2013-12-17 | 2017-07-11 | Mitsubishi Electric Corporation | Power semiconductor module |

| WO2015181770A2 (en) | 2014-05-30 | 2015-12-03 | Eltek S.P.A. | A sensor for detecting the level of a medium |

| WO2016042459A1 (en) * | 2014-09-15 | 2016-03-24 | Eltek S.P.A. | Sensor for detecting the level of a medium |

| WO2016042456A2 (en) | 2014-09-15 | 2016-03-24 | Eltek S.P.A. | Sensor for detecting the level of a medium |

| DE102016106035A1 (de) | 2016-04-01 | 2017-10-05 | Sandvik Materials Technology Deutschland Gmbh | Kaltpilgerwalzanlage und Verfahren zum Herstellen eines Rohres |

| JP6642719B2 (ja) * | 2016-08-10 | 2020-02-12 | 三菱電機株式会社 | 半導体装置 |

| WO2018056287A1 (ja) | 2016-09-21 | 2018-03-29 | 三菱電機株式会社 | 半導体装置および電力変換装置 |

| JP6809294B2 (ja) * | 2017-03-02 | 2021-01-06 | 三菱電機株式会社 | パワーモジュール |

| JP6891075B2 (ja) * | 2017-08-30 | 2021-06-18 | 株式会社 日立パワーデバイス | パワー半導体モジュール |

| WO2020136810A1 (ja) * | 2018-12-27 | 2020-07-02 | 三菱電機株式会社 | 半導体装置、半導体装置の製造方法及び電力変換装置 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE4341269A1 (de) | 1993-12-03 | 1995-06-22 | Bosch Gmbh Robert | Gleichrichterdiode |

| EP0706221A2 (de) | 1994-10-07 | 1996-04-10 | Hitachi, Ltd. | Halbleiteranordnung mit einer Mehrzahl von Halbleiterelementen |

| FR2800017A1 (fr) | 1999-10-25 | 2001-04-27 | Valeo Thermique Moteur Sa | Dispositif de refroidissement pour un vehicule a moteur electrique alimente par une pile a combustible |

| US6231919B1 (en) | 1998-08-28 | 2001-05-15 | Commscope Properties, Llc | Method of making conductor insulated with foamed fluoropolymer |

| JP2002076190A (ja) | 2000-08-24 | 2002-03-15 | Toshiba Corp | 回路基板、半導体装置及びこれらの製造方法 |

| DE102007015534A1 (de) | 2006-09-28 | 2008-04-03 | Mitsubishi Electric Corp. | Leistungshalbleitermodul |

| DE102007008912B4 (de) | 2006-07-04 | 2009-01-29 | Mitsubishi Electric Corp. | Halbleitervorrichtung |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4855872A (en) * | 1987-08-13 | 1989-08-08 | General Electric Company | Leadless ceramic chip carrier printed wiring board adapter |

| JPH08125071A (ja) | 1994-10-25 | 1996-05-17 | Fuji Electric Co Ltd | 半導体装置 |

| JPH1187567A (ja) | 1997-09-02 | 1999-03-30 | Toshiba Corp | 半導体装置 |

| CA2255441C (en) * | 1997-12-08 | 2003-08-05 | Hiroki Sekiya | Package for semiconductor power device and method for assembling the same |

| JP3440824B2 (ja) * | 1998-05-28 | 2003-08-25 | 株式会社日立製作所 | 半導体装置 |

| JP2004200306A (ja) * | 2002-12-17 | 2004-07-15 | Hitachi Ltd | 半導体モジュール |

| JP4253183B2 (ja) | 2002-12-27 | 2009-04-08 | 三菱電機株式会社 | 電力用半導体モジュール |

| JP2005210006A (ja) * | 2004-01-26 | 2005-08-04 | Toshiba Corp | 半導体装置 |

| JP4319591B2 (ja) * | 2004-07-15 | 2009-08-26 | 株式会社日立製作所 | 半導体パワーモジュール |

| JP2006318980A (ja) * | 2005-05-10 | 2006-11-24 | Toyota Industries Corp | 半導体装置および半導体装置の製造方法 |

| JP4609296B2 (ja) * | 2005-12-05 | 2011-01-12 | 株式会社日立製作所 | 高温半田及び高温半田ペースト材、及びそれを用いたパワー半導体装置 |

| US8004075B2 (en) | 2006-04-25 | 2011-08-23 | Hitachi, Ltd. | Semiconductor power module including epoxy resin coating |

| JP4525636B2 (ja) * | 2006-06-09 | 2010-08-18 | 株式会社日立製作所 | パワーモジュール |

| JP4972503B2 (ja) * | 2007-09-11 | 2012-07-11 | 株式会社日立製作所 | 半導体パワーモジュール |

| JP2009070869A (ja) | 2007-09-11 | 2009-04-02 | Panasonic Corp | 半導体発光装置 |

-

2010

- 2010-04-12 JP JP2010091291A patent/JP5212417B2/ja active Active

- 2010-10-22 US US12/910,231 patent/US8558361B2/en active Active

-

2011

- 2011-03-17 DE DE102011005690.4A patent/DE102011005690B4/de active Active

- 2011-03-25 CN CN2011100736492A patent/CN102214622B/zh active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE4341269A1 (de) | 1993-12-03 | 1995-06-22 | Bosch Gmbh Robert | Gleichrichterdiode |

| EP0706221A2 (de) | 1994-10-07 | 1996-04-10 | Hitachi, Ltd. | Halbleiteranordnung mit einer Mehrzahl von Halbleiterelementen |

| US6231919B1 (en) | 1998-08-28 | 2001-05-15 | Commscope Properties, Llc | Method of making conductor insulated with foamed fluoropolymer |

| FR2800017A1 (fr) | 1999-10-25 | 2001-04-27 | Valeo Thermique Moteur Sa | Dispositif de refroidissement pour un vehicule a moteur electrique alimente par une pile a combustible |

| JP2002076190A (ja) | 2000-08-24 | 2002-03-15 | Toshiba Corp | 回路基板、半導体装置及びこれらの製造方法 |

| DE102007008912B4 (de) | 2006-07-04 | 2009-01-29 | Mitsubishi Electric Corp. | Halbleitervorrichtung |

| DE102007015534A1 (de) | 2006-09-28 | 2008-04-03 | Mitsubishi Electric Corp. | Leistungshalbleitermodul |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102011005690A1 (de) | 2011-10-13 |

| CN102214622A (zh) | 2011-10-12 |

| US8558361B2 (en) | 2013-10-15 |

| JP2011222805A (ja) | 2011-11-04 |

| CN102214622B (zh) | 2013-09-18 |

| US20110249407A1 (en) | 2011-10-13 |

| JP5212417B2 (ja) | 2013-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| DE102011005690B4 (de) | Leistungshalbleitermodul | |

| DE102012206596B4 (de) | Halbleitervorrichtung | |

| DE102006012429B4 (de) | Halbleitervorrichtung | |

| DE112015002001B4 (de) | Halbleitermodul | |

| EP0688053B1 (de) | Niederinduktives Leistungshalbleitermodul | |

| DE102015012915B4 (de) | Anordnung von Halbleiterelementen auf einem Halbleitermodul für ein Leistungsmodul oder entsprechendes Verfahren | |

| DE102012218868B3 (de) | Leistungshalbleitermodul | |

| US9780684B2 (en) | Power converter | |

| DE212018000087U1 (de) | Halbleitervorrichtung | |

| DE112014005694B4 (de) | Halbleitermodul | |

| DE112017004739B4 (de) | Halbleitereinheit und Leistungswandler | |

| EP2784809B1 (de) | Leistungshalbleitermodul und Verfahren zur Herstellung eines Leistungshalbleitermoduls | |

| DE60317270T2 (de) | Halbleitermodul und Leistungswandler | |

| DE102015224422A1 (de) | Elektronische Schaltungseinheit | |

| DE102016206233A1 (de) | Leistungsmodul mit einem Ga-Halbleiterschalter sowie Verfahren zu dessen Herstellung, Wechselrichter und Fahrzeugantriebsystem | |

| DE102020109347A1 (de) | Packungsstruktur für stromversorgungsgerät | |

| DE112020006374T5 (de) | Leistungsmodul mit verbesserten elektrischen und thermischen Charakteristiken | |

| DE102017120747B4 (de) | SMD-Gehäuse mit Oberseitenkühlung und Verfahren zu seiner Bereitstellung | |

| EP1672692B1 (de) | Leistungshalbleiter-Modul | |

| DE60306040T2 (de) | Halbleitermodul und Leistungswandlervorrichtung | |

| DE10119502A1 (de) | Halbleitergerät | |

| DE102019212727B4 (de) | Halbleitervorrichtung und elektrische Leistungsumwandlungseinrichtung | |

| DE102019204889A1 (de) | Elektronische Schaltungseinheit | |

| DE102015219225A1 (de) | Halbleitervorrichtung | |

| DE112019002851T5 (de) | Halbleiterbauelement und leistungswandlervorrichtung |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| R012 | Request for examination validly filed | ||

| R016 | Response to examination communication | ||

| R084 | Declaration of willingness to licence | ||

| R016 | Response to examination communication | ||

| R018 | Grant decision by examination section/examining division | ||

| R020 | Patent grant now final |