CN1149780C - 保密部件的解扰器件及带有这种器件的保密部件 - Google Patents

保密部件的解扰器件及带有这种器件的保密部件 Download PDFInfo

- Publication number

- CN1149780C CN1149780C CNB981069703A CN98106970A CN1149780C CN 1149780 C CN1149780 C CN 1149780C CN B981069703 A CNB981069703 A CN B981069703A CN 98106970 A CN98106970 A CN 98106970A CN 1149780 C CN1149780 C CN 1149780C

- Authority

- CN

- China

- Prior art keywords

- descrambling

- clock signal

- frequency

- data

- combination

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000010363 phase shift Effects 0.000 claims description 3

- 238000000034 method Methods 0.000 claims description 2

- 230000001360 synchronised effect Effects 0.000 claims description 2

- 238000000926 separation method Methods 0.000 claims 1

- 230000000694 effects Effects 0.000 description 8

- 230000005540 biological transmission Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000002950 deficient Effects 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/70—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer

- G06F21/71—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information

- G06F21/77—Protecting specific internal or peripheral components, in which the protection of a component leads to protection of the entire computer to assure secure computing or processing of information in smart cards

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F5/00—Methods or arrangements for data conversion without changing the order or content of the data handled

- G06F5/06—Methods or arrangements for data conversion without changing the order or content of the data handled for changing the speed of data flow, i.e. speed regularising or timing, e.g. delay lines, FIFO buffers; over- or underrun control therefor

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/16—Analogue secrecy systems; Analogue subscription systems

- H04N7/162—Authorising the user terminal, e.g. by paying; Registering the use of a subscription channel, e.g. billing

- H04N7/163—Authorising the user terminal, e.g. by paying; Registering the use of a subscription channel, e.g. billing by receiver means only

Abstract

保密部件的解扰器件及带有这种器件的保密部件。在解扰以时钟信号CLK的比特频率到达输入端的加扰数字数据的器件中,在解扰前,将数字数据按比特频率分成n位的组合及以等于比特频率n分之一的频率分为m×n位的组合。m×n组合被解扰,接着以n分之一比特频率分成n位的m个组合并以比特频率转储每组合的n位。工作在比特频率的解扰器件的电路表面积和数量都因此减少。这使解扰器件控制电路的功耗降低。本发明应用于条件存取系统,如智能卡或译码器。

Description

技术领域

本发明涉及一种允许对数字数据流进行处理的保密部件。

本发明特别涉及一种被包括在上述保密部件中的解扰器件。

背景技术

依据本发明的保密部件可以是,比如一种条件存取系统的智能卡,数字数据可以是视频数据。

如所属领域的技术人员所知,条件存取系统使服务提供者将其服务仅提供给那些有权使用这些服务的用户。如,在收费电视系统的情形中。

由服务提供者提供的项目是用控制字进行加扰的项目。这种加扰的项目只能被解扰后由用户读出,与分配给该用户的权利一致。服务提供者给用户提供智能卡和解码器,以便于只有那些被授权的用户才可以得到服务。

这种用于解扰该项目的电路被包括在智能卡或译码器中。

本发明同样涉及用于解扰该项目的电路在智能卡中的情况,以及用于解扰该项目的电路在解码器中的情况。

通常,要被解扰的数字数据是以由串行位所组成的数据包形式被传递到解扰器件中的。

举例来说,在根据NRSS(代表“国家可更新的安全标准”)标准的智能卡的情况下,数据包是由8比特188或131字节的视频数据构成的,并且该视频数据的比特频率是一个高频值,如等于50MHz。如本领域技术人员所知,数据包可能是一个接一个不连续的或是被任何数目的比特期间所分隔开的。

在被解扰之前,串行的视频数据被分成64比特的二进制组合。

因为将64比特的组合解扰的运行需要花时间,因此只要当前数据的解扰仍在进行中,传送给智能卡的待解扰数据被存储在一个够位寄存器中。

根据现有技术,能够构成待解扰的二进制组合的逻辑电路的工作频率为比特频率。

上述的逻辑电路是用CMOS(互补金属氧化物半导体)技术构成的。如本领域普通技术人员所知,CMOS技术电路所消耗的功率是和它们的工作频率成比例的。典型地,对于符合NRSS标准的智能卡,控制整个解扰操作的逻辑电路所消耗的功率大约为400mW。

这一所消耗功率值是很高的并且有许多缺陷。它导致了解扰器件的二流的可靠性以及限制了可用在解扰器件中的保密部件的温度范围。

发明内容

本发明的一个目的是提供一种没有上述缺陷的保密部件的解扰器件。

为此,本发明涉及一种用于解扰数字数据的设备,该设备顺序地包括:一个输入电路,该电路使得形成它与时钟信号CLK同期接收到的串行数字数据的组合成为可能,一个解扰电路,该电路可以将输入电路产生的数据组合解扰,以及一个输出电路,该输出电路可以与时钟信号CLK同期地把由解扰电路产生的已解扰的数据组合变成串行数字数据。根据本发明,输入电路包括第一装置,该装置能够与时钟信号CL1同期地构造数据组合,时钟信号CL1的频率是时钟信号CLK时序的几分之一,输出电路包括第二装置,该装置可以按和信号CL1有相同频率的时钟信号CL2把由解扰电路产生的已解扰的数据组合分解为数据的子组合,以及解扰设备包括产生时钟信号CL1和CL2的同步和控制器件。

按照本发明的一个方面,提供一种用于解扰在第一时钟信号的比特频率下接收到的数字数据的设备,包括:输入电路,在所述第一时钟信号的频率下操作,以构成所述数字数据的n比特的组合;装置,用于加入所述n比特的组合,使之成为m个组合的块,该装置接收第二时钟信号,第二时钟信号的频率小于所述第一时钟信号的频率;以及解扰电路,用于解扰所述块。

按照本发明的另一方面,提供一种用于解扰加扰的数字数据的方法,包括:以第一频率接收所述加扰的数字数据;以所述第一频率构成所述接收的数字数据的组合;以第二频率构成包括至少两个所述组合的块;解扰所述数据块;以所述第二频率将所述解扰的块变换为串行数字数据的解扰组合;以及以所述第一频率提供所述解扰的串行数字数据,作为解扰的数字数据信号。

借助本发明,工作在比特频率的解扰设备的电路的数量和表面面积因此而减少。

本发明的一个优点是降低了由解扰设备而引起的功率消耗。

根据一个具体实施例,输入电路顺序地包括一个解串器,能够把所述的串行数字数据转换为n比特的组合,以及所述第一装置,按照组成所述数据组合的m×n比特组合的分组把n比特的组合联系在一起,输出电路顺序地包括把所述已解扰的数据组合分解为n比特的m个子组合的所述第二装置和能够恢复每个n比特的子组合的已解扰数据的并串行转换器。

根据本发明的一个优选方面,所述第一装置包括一个带有时钟信号CL1的第一FIFO型存贮器以及所述第二装置包括带有时钟信号CL2的第二FIFO型存储器。

根据一个具体实施例,本发明的设备包括能使解扰电路具有一种不解扰它所接收的数据组合的透明模式的装置。

根据一个具体实施例,在端入端接收的数字数据被组成连续的数据包并且时钟信号CL1和CL2的频率等于n分之一的时钟信号CLK的频率以及时钟信号CL2相对于时钟信号CL1被移相,这样做是考虑到分隔二组连续数据包的比特期间的数量。

本发明还涉及一种包括例如上述用于解扰数字数据的设备的保密部件。

根据本发明的一个方面,所述保密部件是条件存取系统的智能卡。

本发明还涉及一种数字解码器,该解码器包括如上所述的用于解扰数字数据的设备。

在说明书的余下部分,举例中用的数字数据是视频数据。然而,通常情况下,本发明涉及如上面所提到的任何一种类型的数字数据。

附图说明

本发明的其它特征和优点将在阅读参考附图所给出的优选实施例中体现出来:

-图1表示现有技术的一个保密部件的解扰器件,

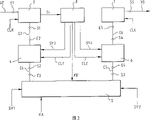

-图2表示根据本发明一个保密部件的解扰器件。

具体实施方式

在所有的图中,相同的标记代表同一个单元。

图1的器件包括一个被分成二个区域Z1和Z2的移位寄存器1和解扰电路2。

Z1区包括一个输入端EZ1和输出端SZ2,Z2区包括一个输入端EZ2和输出端SZ2。解扰电路2包括输入端ED和输出端SD。输出端SZ1和输入端ED相连,输出端SD和输入端EZ2相连。

一个由待解扰的视频数据构成的信号VE施加到输入EZ1上。如前面所提到的,信号VE是由一串数字数据包或串行的一些位构成的。时钟CLK对这些位累积在Z1区中的频率计时。当已在Z1区中聚集了N位时,N可能为例如64,它就以N个并行位构成的组合C1的形式通过建立在输出端SZ1和输入端ED之间的链路传送到解扰电路2中。C1的传送是在同步信号SY1的作用下进行的。

依据用户所获得的权利,解扰可能被授权或未被授权。解扰授权或未授权是通过加到解扰电路2上的命令KA来获知的。如果解扰操作被授权,解扰电路2就完成解扰组合C1的操作。

一旦被解扰,视频数据就构成从解扰电路2传送到寄存器1的Z2区中的N个并行位的组合C2。组合C2的传送是在同步信号SY2的作用下通过建立在输出端SD和输入端EZ2之间的链路完成的。

包含在Z2区中的已解扰数据由输出端SZ2与时钟信号CLK同期地转储从而构成输出信号VS。

在构成信号VE的视频数据不是加扰数据情况下,它们就通过输入端EZ1和输出端SZ2之间的移位寄存器1直接传送。

例如,根据NRSS标准,每个组合C1和C2都由64位构成,并且控制这些组合传送的逻辑电路的工作频率是相等的,比如50MHz。

如前所述,在NRSS标准下运行的逻辑电路所消耗的功率典型地约为400mW,这样有许多缺点。

图2表示根据本发明优选实施例的一个保密部件的解扰器件。

输入电路是由一个带有输入端E1和输出端S1的解串器3和一个带有输入端E2和输出端S2的第一FIFO型存储器4组成的。

输出电路是由一个带有一个输入端E4和一个输出端S4的的第二FIFO型存储器6和一个带有输入端E5和输出端S5的并串行转换器7组成的。

解扰电路5有一个输入端E3和输出端S3。

输出端S 1连接到输入端E2,输出端S2连接到输入端E3,输出端S3连接到输入端E4,以及输出端S4和输入端E5相连。

由待解扰的视频数据构成的信号VE施加到解串器的输入端E1上。

如前所述,信号VE是由一串串行位数据包构成的。时钟CLK对累积在解串器3中的那些位的频率计时。

当第一集合的n位已聚集在解串器3中时,解串器产生一个同步信号Si使同步和控制器件8被初始化。

根据本发明,n是一个小于N大于1的整数。最好n=8。

每个汇集在解串器3中的n位集合构成n个并行位的组合C3。在由器件8输出并施加于存储器4的同步SY3的作用下,每个组合C3从解串器3传送到FIFO型存储器4的第一级。由器件8输出并施加于存储器4的时钟信号CL1可使存储器4中的各种组合C3从一级移到另一级。最好地,FIFO型存储器4中的每一级的大小等于n位。

根据本发明,存储器4中各级的加载允许形成m×n串行位的集合,m是个最好为8的整数。当一m×n串行位的集合已聚集在存储器4中时,它就以m×n并行位的组合C4的形式传送到解扰器5。组合C4的这个传送是在输入到解扰电路5中的同步信号SY1的作用下完成的。

时钟信号CL1的频率是时钟信号CLK频率的几分之一。举例来说,既然时钟信号CLK的频率等于50MHz,那么,时钟信号CL1的频率等于50/nMHz,在n=8的情况下,为6.25MHz。

一般,一个m×n并行位的组合C4可能由加扰数据和非加扰数据组成。

根据本发明,解扰器5不仅能按解扰方式工作,还能在透明方式下工作。术语透明方式被理解为在没有执行解扰操作情况下非加扰数据的一种传送模式。

由器件8输出并输入到解扰器5中的命令信号KD启动被置于解扰方式或透明方式下的解扰器,这两种方式是根据传送到解扰器5中的数据是加扰数据还是非加扰数据来决定的。

在数据被加扰的情况下,只要通过命令KA作了授权,解扰电路5就执行解扰操作。此后被解扰的数据构成m×n并行位的组合C5,该组合C5从解扰器5传送到第二存储器6。组合C5的传送在加到解扰电路5或存储器6上的同步信号SY2的作用下完成。

时钟信号CL2和由器件8输出的同步信号SY4被加到第二FIFO型存储器6上。信号CL2和SY4起到与加到第一FIFO型存储器4上的信号CL1和SY3相对称的作用。

时钟信号CL2的频率和时钟信号CL1是一样的而且由于考虑到将二个连续数据包分隔开的位期间的数量,信号CL2相对于信号CL1的相移被调整。

在时钟信号CL2的作用下,存储器6能够把每个m×n位的组合C5转换为各由n位构成的连续的m个子组合C6。

由存储器6输出的组合C6被传送到并串行转换器7中。在时钟信号CLK的作用下,与加在解串器3上的信号相同,从并串行转换器7中发出的二进制数据则构成一个解扰数据信号VS。

根据上述的实施例,同步信号SY2和SY4被分别加到解扰电路5和存储器6。本发明还涉及其它一些实施例,其中同步信号SY2被加到存储器6上而同步信号SY4被加到并串行转换器7上。

此外,根据上面所描述的优选实施例,输入电路包括串联的解串器和第一FIFO型存储器,输出电路包括串联的第二FIFO型存储器和并串行转换器。

根据本发明,只有解串器3和并串行转换器7工作在比特频率,解扰器件的其余部分都工作在一个较低的频率上。因此,本发明中解扰器件的功率消耗明显地低于现有技术中的解扰器件。

更通常地,本发明涉及任何一种类型的输入电路,该电路包括可将待解扰的二进制组合与时钟信号CL1同期构造的装置,该时钟信号CL1的频率等于定义比特频率的时钟信号CLK频率的几分之一,本发明也包括任何一种类型的输出电路,该电路包括可将由解扰电路输出的被解扰的二进制组合与时钟信号CL2同期地划分成二进制的子组合的装置。

Claims (8)

1.一种用于解扰在第一时钟信号(CLK)的比特频率下接收到的数字数据的设备,包括:

输入电路(3),在所述第一时钟信号(CLK)的频率下操作,以构成所述数字数据的n比特的组合(C3);

装置(4),用于加入所述n比特的组合(C3),使之成为m个组合(C4)的块,所述装置接收第二时钟信号(CL1),第二时钟信号(CL1)的频率小于所述第一时钟信号(CLK)的频率;以及

解扰电路(5),用于解扰所述块。

2.根据权利要求1的设备,还包括输出电路,用于在第一时钟信号(CLK)的比特频率下,将所述解扰电路(5)产生的解扰的数据块(C5)变换为串行的数字数据,所述输出电路包括:

装置(6),用于与第三时钟信号(CL2)同期地分离所述被解扰的数据块为数据的子组合(C6),所述被解扰的数据块是由解扰电路产生的,所述第三时钟信号(CL2)的频率与第二时间信号(CL1)的频率相同;以及

并串行转换器(7),用于恢复每个数据的子组合(C6)的所述被解扰的数据。

3.根据权利要求1的设备,其特征在于所述加入n比特的所述组合的装置(4)包括一个带有第二时钟信号(CL1)的第一FIFO型存储器。

4.根据权利要求2的设备,其特征在于所述分离被解扰的数据块的装置(6)包括带有第三时钟信号(CL2)的第二FIFO型存储器。

5.根据权利要求1-4中任一权利要求的设备,还包括一个同步和控制装置(8),用于产生第二时钟信号(CL1)和第三时钟信号(CL2)。

6.根据权利要求1-4中任一权利要求的设备,其特征在于还包括装置(8),使解扰电路(5)拥有一个透明方式,在这种方式下它接收到的所述数据块不被解扰。

7.根据权利要求2的设备,其中接收到作为输入的数字数据组成连续的数据包,其特征在于,第二时钟信号(CL1)和第三时钟信号(CL2)的频率等于除以n的第一时钟信号(CLK)的频率,以及考虑到将二个连续数据包分隔开的比特期间的数量,第三时钟信号(CL2)相对于第二时钟信号(CL2)发生移相。

8.一种用于解扰加扰的数字数据的方法,包括:

以第一频率接收所述加扰的数字数据;

以所述第一频率构成所述接收的数字数据的组合(C3);

以第二频率构成包括至少两个所述组合的块(C4);

解扰所述数据块;

以所述第二频率将所述解扰的块(C5)变换为串行数字数据的解扰组合(C6);以及

以所述第一频率提供所述解扰的串行数字数据,作为解扰的数字数据信号。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR9701306A FR2759175B1 (fr) | 1997-02-05 | 1997-02-05 | Dispositif de desembrouillage d'element de securite et element de securite comprenant un tel dispositif |

| FR9701306 | 1997-02-05 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1198062A CN1198062A (zh) | 1998-11-04 |

| CN1149780C true CN1149780C (zh) | 2004-05-12 |

Family

ID=9503359

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB981069703A Expired - Fee Related CN1149780C (zh) | 1997-02-05 | 1998-02-05 | 保密部件的解扰器件及带有这种器件的保密部件 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6408077B1 (zh) |

| EP (1) | EP0858185A1 (zh) |

| JP (1) | JPH10262042A (zh) |

| CN (1) | CN1149780C (zh) |

| FR (1) | FR2759175B1 (zh) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020146125A1 (en) * | 2001-03-14 | 2002-10-10 | Ahmet Eskicioglu | CA system for broadcast DTV using multiple keys for different service providers and service areas |

| KR20030048903A (ko) * | 2001-12-13 | 2003-06-25 | 엘지전자 주식회사 | 비동기전송모드 수동광네트워크의 하향 데이터에 대한병렬 분산표본 역혼화 장치 |

| DE10162309A1 (de) * | 2001-12-19 | 2003-07-03 | Philips Intellectual Property | Verfahren und Anordnung zur Erhöhung der Sicherheit von Schaltkreisen gegen unbefugten Zugriff |

| US7724907B2 (en) * | 2002-11-05 | 2010-05-25 | Sony Corporation | Mechanism for protecting the transfer of digital content |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4139839A (en) * | 1977-03-18 | 1979-02-13 | Nasa | Digital data reformatter/deserializer |

| GB2257557B (en) * | 1991-07-08 | 1994-11-16 | Amstrad Plc | Video recorder system |

| MY125706A (en) * | 1994-08-19 | 2006-08-30 | Thomson Consumer Electronics | High speed signal processing smart card |

-

1997

- 1997-02-05 FR FR9701306A patent/FR2759175B1/fr not_active Expired - Fee Related

-

1998

- 1998-02-03 US US09/018,206 patent/US6408077B1/en not_active Expired - Fee Related

- 1998-02-04 JP JP10023299A patent/JPH10262042A/ja active Pending

- 1998-02-04 EP EP98400234A patent/EP0858185A1/en not_active Withdrawn

- 1998-02-05 CN CNB981069703A patent/CN1149780C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6408077B1 (en) | 2002-06-18 |

| FR2759175B1 (fr) | 1999-02-26 |

| EP0858185A1 (en) | 1998-08-12 |

| FR2759175A1 (fr) | 1998-08-07 |

| CN1198062A (zh) | 1998-11-04 |

| JPH10262042A (ja) | 1998-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7752482B2 (en) | Hybrid parallel/serial bus interface | |

| US8332721B2 (en) | Enhanced error detection in multilink serdes channels | |

| US6594275B1 (en) | Fibre channel host bus adapter having multi-frequency clock buffer for reduced power consumption | |

| US5613003A (en) | Packet video signal inverse transport processor memory address circuitry | |

| EP0779746B1 (en) | Out-of-synchronization recovery method and apparatus of data transmission system | |

| US7240233B2 (en) | Hybrid parallel/serial bus interface | |

| CN1224975A (zh) | 数字视频接收器、条件访问模块和其间的数据传输方法 | |

| US7199732B1 (en) | Data converter with reduced component count for padded-protocol interface | |

| CN1167405A (zh) | 条件访问信息的装置 | |

| US7075330B2 (en) | System and method for balancing capacitively coupled signal lines | |

| CN1233899A (zh) | 简化的数据链路 | |

| CN1149780C (zh) | 保密部件的解扰器件及带有这种器件的保密部件 | |

| EP0781054A3 (en) | Method of encoding and decoding for data transmission | |

| KR20080070949A (ko) | 직렬 통신 시스템에서 직렬 데이터의 송수신 방법 및 장치와 이를 위한 직렬 통신 시스템 | |

| CN1148455A (zh) | 数据传输装置、数据传输方法及与它们配套的摄像机系统 | |

| JP2003507929A (ja) | 複数の8b/10bエンコードされたデータストリームを結合するための方法及び装置 | |

| EP0933927A1 (en) | Demultiplexer for a digital video receiver | |

| WO2022156806A1 (zh) | 通信方法、装置、系统、存储介质及计算机程序产品 | |

| CN1122417C (zh) | 用于视频信号编码系统的行程长度编码装置 | |

| CN1066601C (zh) | 用于在数字信号中插入异步数据的方法和装置 | |

| KR20030056306A (ko) | 전송 스트림 데이터의 디스크램블 처리 장치 및 그 방법 | |

| JP7100644B2 (ja) | 送信装置、および通信システム | |

| TW201503615A (zh) | 通訊裝置 | |

| CN1141560A (zh) | 解密器装置 | |

| JP3248503B2 (ja) | 時分割多重回路及び時分割多重方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20040512 |