CN114709166A - 浅沟槽隔离结构的制备方法 - Google Patents

浅沟槽隔离结构的制备方法 Download PDFInfo

- Publication number

- CN114709166A CN114709166A CN202111409309.2A CN202111409309A CN114709166A CN 114709166 A CN114709166 A CN 114709166A CN 202111409309 A CN202111409309 A CN 202111409309A CN 114709166 A CN114709166 A CN 114709166A

- Authority

- CN

- China

- Prior art keywords

- silicon nitride

- nitride layer

- layer

- oxide

- oxide layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W10/014—

-

- H10W10/17—

Landscapes

- Element Separation (AREA)

Abstract

本发明公开了一种浅沟槽隔离结构的制备方法,包括:在硅衬底表面依次形成第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层;形成贯穿第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层的窗口;在窗口侧面形成氮化硅侧墙;于所述窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽;在第二氮化硅层表面、沟槽和窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物;去除第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层的剩余部分及氮化硅侧墙,形成浅沟槽隔离结构。本发明优化了浅沟槽隔离结构的制备工艺,能够在不改变氮化硅单位体积内缺陷密度的情况下,极大程度的降低浅沟槽隔离结构中的硅残留,提高了产品良率。

Description

技术领域

本发明涉及半导体的制造技术领域,具体涉及一种浅沟槽隔离结构的制备方法。

背景技术

随着集成电路尺寸的减小,构成电路的器件必须更密集地放置,以适应芯片上可用的有限空间。由于目前的研究致力于增大半导体衬底的单位面积上有源器件的密度,所以电路间的有效绝缘隔离变得更加重要。现有技术中形成隔离区域的方法主要有局部氧化隔离(Local Oxidation of Silicon,简称LOCOS)工艺或浅沟槽隔离(Shallow TrenchIsolation,简称STI)工艺。LOCOS工艺是在晶片表面淀积一层氮化硅,然后再进行刻蚀,对部分凹进区域进行氧化生长氧化硅,有源器件在氮化硅所确定的区域生成。对于隔离技术来说,LOCOS工艺在电路中的有效局部氧化隔离仍然存在问题,其中一个问题就是在氮化硅边缘生长的“鸟嘴”现象,这是由于在氧化的过程中氮化硅和硅之间的热膨胀性能不同造成的。这个“鸟嘴”占用了实际的空间,增大了电路的体积,并在氧化过程中,对晶片产生应力破坏。因此LOCOS工艺只适用于大尺寸器件的设计和制造。

STI工艺比LOCOS工艺拥有多项的制程及电性隔离效果好和占用面积小的优点,包括可减少占用硅晶圆表面的面积同时增加器件的集成度,保持表面平坦度及较少通道宽度侵蚀等。因此,目前0.18um以下的半导体元件例如MOS电路的有源区隔离层已大多采用浅沟槽隔离工艺来制作。但STI工艺也有很多的技术问题。

在现有的STI(浅沟槽隔离)技术中,通常使用氮化硅(SIN)作为硬掩膜(hardmask)来刻蚀硅衬底,但在后续去除氮化硅的过程中容易产生硅残留缺陷,主要原因有三个,一是光刻胶中的杂质,二是无尘室中依然存在的少量颗粒(particle),三是SIN中的缺陷。前两个可以通过购买更高性能的光刻胶,以及提高无尘室的洁净度来改善,但SIN中的缺陷受限于SIN的制造工艺本身,并不容易去除,因此STI中的硅残留缺陷无法降低至更高级别。

因此,有必要提供改进的技术方案以克服现有技术中存在的以上技术问题。

发明内容

为了解决上述技术问题,本发明提供了一种浅沟槽隔离结构的制备方法,优化了浅沟槽隔离结构的制备工艺,能够在不改变氮化硅单位体积内缺陷密度的情况下,极大程度的降低浅沟槽隔离结构中的硅残留,提高了产品良率。

根据本发明第一方面,提供了一种浅沟槽隔离结构的制备方法,包括:在硅衬底表面依次形成第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层;

形成贯穿所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的窗口;

在所述第二氮化硅层上表面及所述窗口表面形成第三氮化硅层;

去除所述第二氮化硅层上表面和所述窗口底部的第三氮化硅层,形成位于所述窗口侧面的氮化硅侧墙;

于所述窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽;

在所述第二氮化硅层表面、所述沟槽和所述窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物;

去除所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的剩余部分及所述氮化硅侧墙,形成浅沟槽隔离结构。

可选地,所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的总厚度为1100埃~2000埃。

可选地,所述第一氮化硅层、所述第二氮化硅层和所述第三氮化硅层的厚度均远小于所述第二氧化层的厚度。

可选地,所述第一氮化硅层、所述第二氮化硅层和所述第二氧化层的厚度之和为1000埃~1800埃,所述第一氧化层的厚度为50埃~150埃。

可选地,所述第一氧化层的厚度小于所述第二氧化层的厚度。

可选地,所述第三氮化硅层与所述第二氮化硅层的厚度相同。

可选地,在形成的所述浅沟槽隔离结构中,所述氧化物位于所述硅衬底表面之上的部分的厚度为100埃~500埃。

可选地,去除所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的剩余部分及所述氮化硅侧墙的方法包括:

使用湿法刻蚀去除所述第一氮化硅层、所述第二氮化硅层的剩余部分及所述氮化硅侧墙,使包裹在所述第一氮化硅层、所述第二氮化硅以及所述氮化硅侧墙之间的所述第二氧化层自然脱落;

使用干法刻蚀或湿法刻蚀去除所述第一氧化层。

根据本发明第二方面,提供了一种浅沟槽隔离结构的制备方法,包括:在硅衬底表面依次形成氧化层和氮化硅层;

形成贯穿所述氧化层和所述氮化硅层的窗口;

于所述窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽;

在所述氮化硅层表面、所述沟槽和所述窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物,以使得经化学机械研磨后所述沟槽区域内的氧化物的上表面与所述氮化硅层的上表面齐平;

利用湿法刻蚀去除所述氮化硅层的剩余部分;

对所述氧化层的剩余部分和所述氧化物进行干法刻蚀,直至去除所述氧化层的剩余部分,形成浅沟槽隔离结构,

其中,经化学机械研磨后的所述氮化硅层的厚度与形成的所述浅沟槽隔离结构中所述氧化物位于所述硅衬底表面之上的部分的厚度之差的绝对值小于100埃。

可选地,所述氮化硅层的厚度小于所述氧化层的厚度。

可选地,所述氧化层的形成材料与所述氧化物的材料相同。

可选地,所述氧化层的厚度为1100埃~1900埃。

可选地,所述氮化硅层的厚度为100埃~500埃。

本发明的有益效果至少包括:

本发明公开的第一种浅沟槽隔离结构的制备方法中,1.采用包括第一氧化层+第一氮化硅层+第二氧化层+第二氮化硅层的多层结构以及第三氮化硅层的结构来代替现有制备工艺中具有和第一氧化层+第一氮化硅层+第二氧化层+第二氮化硅层的多层结构同样的总体厚度的氧化层加氮化硅层的结构,也即,本发明在保持第一氧化层+第一氮化硅层+第二氧化层+第二氮化硅层的多层结构总厚度不变的情况下,使用第二氧化层结构来代替现有技术中的一部分氮化硅,减小了需要刻蚀的氮化硅的厚度,减少了氮化硅层中的缺陷数量,进而经后续刻蚀后,极大程度的降低了浅沟槽隔离结构中的硅残留数量,提高了产品良率。2.在形成沟槽的过程中,包括对氮化硅结构的两次刻蚀过程,且每次刻蚀过程中所需刻蚀的氮化硅的厚度也得到了降低,进而可通过采用比例高的干法刻蚀工艺对氮化硅进行过刻蚀,保证即使氮化硅中存在缺陷也能够被刻蚀干净,且在刻蚀氮化硅时相邻氧化层的损失量小,避免出现刻蚀深度深浅不一的情况,提高了形成的窗口底部的平整度。3.在浅沟槽隔离结构的制备过程中所形成的氮化硅侧墙结构,可以在进行纵向刻蚀以形成沟槽的过程中保护沟槽两边的氧化层结构不被腐蚀,也可以在去除沟槽两边的氮化硅结构时使得被氮化硅包裹的氧化层结构自然脱落,既减少了相应去除氧化层的工艺步骤,也能够在刻蚀过程中保护不会对沟槽区域内的氧化物造成影响,有助于保持浅沟槽隔离结构的完整性。

本发明公开的第二种浅沟槽隔离结构的制备方法中,在保证氧化层和氮化硅层的总体厚度不变的情况下,通过调整氧化层和氮化硅层的厚度比,降低了其中氮化硅层的厚度,减少了氮化硅层中的缺陷数量,进而经后续刻蚀后,极大程度的降低了浅沟槽隔离结构中的硅残留数量,提高了产品良率。其中进一步将氮化硅层的厚度设置为与浅沟槽隔离结构中氧化物位于硅衬底表面之上的部分的厚度相同,也能够降低后续化学机械研磨工艺的操作难度,优化了浅沟槽隔离结构制备的工艺过程。

应当说明的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

附图说明

图1a-图1m示出现有的一种浅沟槽隔离结构的制备方法的各个阶段的截面示意图;

图2示出根据本发明第一实施例提供的浅沟槽隔离结构的制备方法的流程示意图;

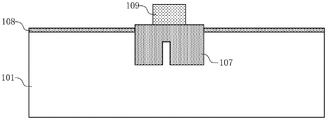

图3a-图3h示出根据本发明第一实施例提供的浅沟槽隔离结构的制备方法的各个阶段的截面示意图;

图4示出根据本发明第二实施例提供的浅沟槽隔离结构的制备方法的流程示意图;

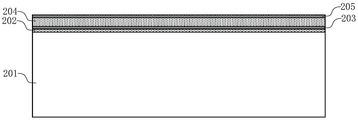

图5a-图5g示出根据本发明第二实施例提供的浅沟槽隔离结构的制备方法的各个阶段的截面示意图。

具体实施方式

为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳实施例。但是,本发明可以通过不同的形式来实现,并不限于本文所描述的实施例。相反的,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

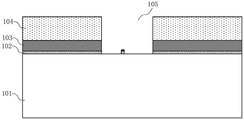

利用光刻版或光刻胶104打开STI区域,并使用干法刻蚀氮化硅层103和氧化层102,以形成ST1窗口105,如图1b所示。

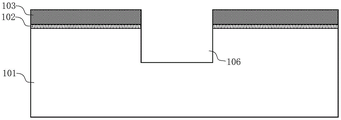

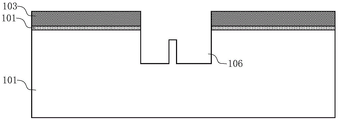

刻蚀硅衬底101以形成深度约为4000埃的沟槽106,如图1c所示。

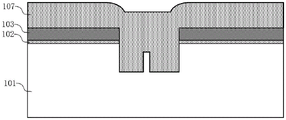

在氮化硅层103上表面和沟槽106内淀积氧化物107,如图1d所示。

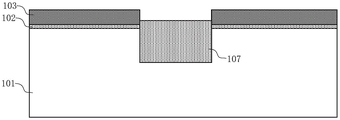

使用CMP(化学机械研磨)氧化物107,直至沟槽106区域内的氧化物107的上表面比硅衬底101的上表面高出300埃左右,如图1e所示。

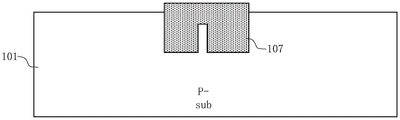

去除氮化硅层103及硅衬底101表面的氧化层102,如图1f所示。

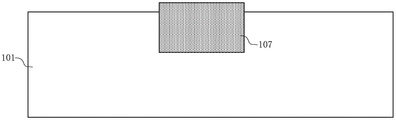

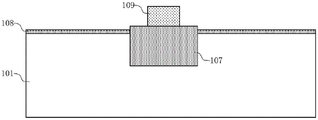

于硅衬底101表面生长栅氧层108,并通过淀积、曝光、刻蚀等步骤在沟槽106区域的氧化物107的部分表面形成多晶硅(POLY)109,如图1g所示。

但是,如果形成氮化硅层103的SIN中存在缺陷,那么缺陷处的SIN的刻蚀速率会变慢,如图1h所示,在与图1b中形成窗口105的类似刻蚀过程中,就会形成氧化层加SIN残留(或只是氧化层残留),由此,现有图1c~1g的过程就变成图1i~图1m的过程,最终在多晶硅109的下方,不完全是厚度为4000埃的氧化物107,还会包括有残留的硅表面,该硅表面至多晶硅109之间的氧化物107的厚度是小于4000埃,最严重的时候是甚至可能达到接近或等于栅氧层108的厚度,使得形成的浅沟槽隔离结构的隔离效果变差,影响晶体管的阈值电压,这将导致产品的良率降低。

针对现有技术中存在的上述问题,申请人经过认真研究和分析得出,氮化硅中的存在的缺陷数量是与氮化硅层的厚度正相关的,基于此,申请人提出了改进后的浅沟槽隔离结构的制备工艺,通过减小浅沟槽隔离结构制备过程中使用的氮化硅层的厚度,实现降低氮化硅中存在的缺陷数量,进而达到降低浅沟槽隔离结构中硅残留数量的目的。

在本发明第一实施例所公开的浅沟槽隔离结构的制备方法中,通过采用多个氧化层和多个氮化硅层交替排布的多层结构以及额外的氮化硅侧墙结构来代替现有的制备工艺中的氧化层102加氮化硅层103的结构,也即,在保持多个氧化层和多个氮化硅层交替排布的多层结构总厚度不变的情况下,使用额外的氧化层来代替现有技术中的一部分氮化硅结构,减小了整个制备过程需要刻蚀的氮化硅的厚度,减少了氮化硅层中的缺陷数量,进而经后续刻蚀后,极大程度的降低了浅沟槽隔离结构中的硅残留数量。同时在形成沟槽的过程中,对氮化硅结构进行两次刻蚀,以降低每次刻蚀过程中所需刻蚀的氮化硅的厚度,使得在刻蚀完成后,能够极大程度的降低浅沟槽隔离结构中的硅残留数量,提高产品良率。其中,本发明实施例中的多个氧化层和多个氮化硅层的总体厚度可以与图1a-图1g中所示出的氧化层102和氮化硅层103的总体厚度相同。如图2所示,本实施例所公开的制备方法具体包括执行如下步骤:

在步骤S11中,在硅衬底表面依次形成第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层。

示例性地,如图3a所示,在硅衬底201的上表面生长氧化物例如氧化硅,以形成第一氧化层202;然后在第一氧化层202的上表面沉积氮化硅,以形成尽可能薄的第一氮化硅层203;接着在第一氮化硅层203的上表面沉积氧化物例如氧化硅,以形成第二氧化层204;之后继续在第二氧化层204的上表面沉积氮化硅,以形成尽可能薄的第二氮化硅层205。其中,第一氧化层202例如可采用传统的热氧化法形成,也可采用传统的化学气相沉积法形成,第一氮化硅层203、第二氧化层204和第二氮化硅层205例如可采用传统的化学气相沉积法形成。

本发明一个可能的实施例中,第一氮化硅层203和第二氮化硅层205的均远小于第二氧化层204的厚度。相较于如图1a~图1m所示出的现有技术中的方案,本发明于浅沟槽隔离结构的制备过程中,在保持所有的氧化层和氮化硅层总厚度不变的情况下使用第二氧化层204来代替现有技术中的大部分氮化硅结构,减小了需要刻蚀的氮化硅的厚度,减少了氮化硅层中的缺陷数量,进而经后续刻蚀后,极大程度的降低了浅沟槽隔离结构中的硅残留数量,提高了产品良率。

进一步地,本实施例所形成的第一氧化层202的厚度小于第二氧化层204的厚度。

在步骤S12中,形成贯穿第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层的窗口。

示例性地,如图3b所示,在第二氮化硅层205的上表面设置光刻胶206,利用传统的光刻工艺在预定的沟槽区域曝光以打开STI窗口。之后,利用传统的干法刻蚀工艺刻蚀掉该STI窗口区域上的第一氧化层202、第一氮化硅层203、第二氧化层204和第二氮化硅层205部分,形成贯穿第一氧化层202、第一氮化硅层203、第二氧化层204和第二氮化硅层205的窗口207。

可以理解的是,在利用传统的干法刻蚀工艺分别刻蚀氧化层和氮化硅层时所采用的刻蚀材料是不相同。而本发明实施例中采用多个氧化层和多个氮化硅层层叠的结构来充当硬掩膜,其在刻蚀形成窗口207的过程中,可通过采用比例高(刻蚀时采用的针对氮化硅层和氧化层的刻蚀材料剂量的比例)的干法刻蚀工艺对氮化硅进行过刻蚀,进而能够保证即使第一氮化硅层203和第二氮化硅层205的氮化硅中存在缺陷也能够被刻蚀干净,且在刻蚀某一氮化硅层时相邻氧化层的损失量小,能够避免该氮化硅层刻蚀完毕后相邻氧化层表面出现刻蚀深度深浅不一的情况,有助于提高形成的窗口207底部的平整度。

在步骤S13中,在第二氮化硅层上表面及窗口表面形成第三氮化硅层。

示例性地,如图3c所示,利用传统的化学气相沉积法在第二氮化硅层205的上表面及窗口207内沉积氮化硅,以形成尽可能薄的第三氮化硅层208。

本发明一个可能的实施例中,所形成的第三氮化硅层208的厚度也远小于第二氧化层204的厚度。同时,本发明实施例中于硅衬底201表面形成的第一氧化层202、第一氮化硅层203、第二氧化层204和第二氮化硅层205的总厚度为1100埃~2000埃,例如为1600埃,即与如图1a~图1m所示出的现有技术中的方案中形成于硅衬底101表面的氧化层102和氮化硅层103的总体厚度相同。其中,所形成的第一氧化层202的厚度为50埃~150埃,例如为100埃;所形成的第一氮化硅层203、第二氮化硅层205和第二氧化层204的厚度之和为1000埃~1800埃,例如为1500埃。

在步骤S14中,去除第二氮化硅层上表面和窗口底部的第三氮化硅层部分,形成位于窗口侧面的氮化硅侧墙。

示例性地,如图3d所示,利用传统的干法刻蚀工艺将第二氮化硅层205上表面的第三氮化硅层部分和窗口207底部的第三氮化硅层部分(即窗口207内硅衬底201上的第三氮化硅层部分)去除,仅保留窗口207内两侧面的第三氮化硅层部分,形成氮化硅侧墙。

本发明实施例在形成沟槽209的过程中分别于步骤S12和步骤S14中采用传统的干法刻蚀工艺对沟槽区域的氮化硅进行了两次刻蚀(第一次刻蚀的是第一氮化硅层203和第二氮化硅层205,第二次刻蚀的是第三氮化硅层208),也即是说,本发明实施例所示出的浅沟槽隔离结构的制备方法中,不仅相比现有的工艺方法减薄了氮化硅的整体厚度,同时对于减薄后的氮化硅还进行了两次的干法刻蚀,使得每次刻蚀过程中所需刻蚀的氮化硅的厚度也得到了降低,如此,增强了对氮化硅的刻蚀效果,能够更进一步地降低了浅沟槽隔离结构中沟槽区域内的硅残留数量。

在步骤S15中,于窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽。

示例性地,如图3e所示,利用传统的干法刻蚀工艺刻蚀窗口207内的硅衬底201部分,形成具有预定深度的沟槽209。本实施例中,基于步骤S14中形成的氮化硅侧墙,可以在步骤S15中进行纵向刻蚀以形成沟槽209的过程中保护沟槽209两边的氧化层(第一氧化层202和第二氧化层204)结构不被腐蚀,有助于保持后续形成的浅沟槽隔离结构的完整性。

在步骤S16中,在第二氮化硅层表面、沟槽和窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物。

示例性地,在形成沟槽209后,首先如图3f所示,利用传统的化学气相沉积法在第二氮化硅层205表面、沟槽209和窗口207内淀积氧化物210例如为氧化硅,接着如图3g所示,利用传统的化学机械研磨CMP工艺去除多余的沉积的氧化物210,使得最终沟槽209内的氧化物210的高度或厚度符合预定要求,例如,在形成的浅沟槽隔离结构中,沟槽209内的氧化物210位于硅衬底201表面之上的部分的厚度为100埃~500埃,例如为300埃。

在步骤S17中,去除第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层的剩余部分及氮化硅侧墙,形成浅沟槽隔离结构。

示例性地,如图3h所示,利用传统的湿法刻蚀工艺去除第一氮化硅层203和第二氮化硅层205的剩余部分及氮化硅侧墙208,使得包裹于第一氮化硅层203、第二氮化硅层205和氮化硅侧墙208之间的第二氧化层204自然脱落;以及在去除氮化硅之后,使用传统的干法刻蚀或湿法刻蚀工艺去除第一氧化层202,形成浅沟槽隔离结构。此步骤中,无需再进行额外的去除第二氧化层204的步骤,一定程度上简化了浅沟槽隔离结构的制备工艺。同时,氮化硅侧墙208也能够在刻蚀过程中保护不会对沟槽区域内的氧化物210造成影响,有助于保持浅沟槽隔离结构的完整性。

在本发明第二实施例所公开的浅沟槽隔离结构的制备方法中,可以在保证氧化层和氮化硅层的总体厚度不变(即本发明实施例中的氧化层和氮化硅层的总体厚度与图1a-图1g中所示出的氧化层102和氮化硅层103的总体厚度相同)的情况下,通过调整氧化层和氮化硅层的厚度比,以降低浅沟槽隔离结构制备过程中使用的氮化硅层的厚度,从而降低了氮化硅层中存在的缺陷数量,使得在后续刻蚀时能够更大程度的降低浅沟槽隔离结构中的硅残留数量。如图4所示,本实施例所公开的制备方法具体包括执行如下步骤:

在步骤S21中,在硅衬底表面依次形成氧化层和氮化硅层。

示例性地,如图5a所示,利用传统的化学气相沉积法在硅衬底301的上表面淀积氧化物例如氧化硅,以形成氧化层302;然后利用传统的化学气相沉积工艺在氧化层302的上表面沉积氮化硅,以形成氮化硅层303。其中,本实施例中所形成的氮化硅层303的厚度与最终形成的浅沟槽隔离结构中氧化物位于硅衬底301表面之上的部分的厚度相当。例如,在本发明一个可能的实施例中,经化学机械研磨后的氮化硅层303的厚度与最终形成的浅沟槽隔离结构中氧化物位于硅衬底301表面之上的部分的厚度之差的绝对值小于100埃。

本发明一个可能的实施例中,于硅衬底301表面形成的氧化层302和氮化硅层303的总厚度为1100埃~2000埃,例如为1600埃,即与如图1a~图1m所示出的现有技术中的方案中形成于硅衬底101表面的氧化层102和氮化硅层103的总体厚度相同。其中,本实施例中所形成的氧化层302的厚度例如为1100埃~1900埃,本实施例中所形成的氮化硅层303的厚度例如为100埃~500埃,也即本实施例中所形成的氮化硅层的厚度小于所形成的氧化层302的厚度。本发明在浅沟槽隔离结构的制备过程中通过调整氧化层302和氮化硅层303的厚度比例,减小了所使用的氮化硅的厚度,进而降低了氮化硅层中存在的缺陷数量。

在步骤S22中,形成贯穿氧化层和氮化硅层的窗口。

示例性地,如图5b所示,在氮化硅层303的上表面设置光刻胶304,利用传统的光刻工艺在预定的沟槽区域曝光以打开STI窗口。之后,利用传统的干法刻蚀工艺刻蚀掉该STI窗口区域上的氧化层302和氮化硅层303部分,形成贯穿氧化层302和氮化硅层303的窗口305。

在步骤S23中,于窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽。

示例性地,如图5c所示,利用传统的干法刻蚀工艺刻蚀窗口305内的硅衬底301部分,形成具有预定深度的沟槽306。

在步骤S24中,在氮化硅层表面、沟槽和窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物,以使得经化学机械研磨后沟槽区域内的氧化物的上表面与氮化硅层的上表面齐平。

示例性地,在形成沟槽306后,首先如图5d所示,利用传统的化学气相沉积法在氮化硅层303表面、沟槽306和窗口305内淀积氧化物307例如为氧化硅。接着如图5e所示,利用传统的化学机械研磨CMP工艺去除多余的沉积的氧化物307,以使得经化学机械研磨后沟槽306区域内的氧化物307的上表面与氮化硅层303的上表面齐平。相较于现有工艺中需要将氧化物307的表面研磨至低于氮化硅层303的上表面,本发明实施例中基于对氮化硅层303的厚度设置,使得只需要将氧化物307的表面研磨至与氮化硅层303的上表面齐平或差距小于预设值即可(具体可参考下文描述进行理解),降低了化学研磨工艺操作的复杂性,优化了浅沟槽隔离结构的制备过程。

本实施例中,氧化层302的形成材料与沟槽306内生长的氧化物307所用的材料相同。

在步骤S25中,利用湿法刻蚀去除氮化硅层的剩余部分。

示例性地,如图5f所示,利用传统的湿法刻蚀工艺去除氮化硅层303。可以理解的是,由于本实施例中经化学机械研磨后沟槽306区域内的氧化物307的上表面与氮化硅层303的上表面齐平,且本实施例所形成的氮化硅层303的厚度与最终形成的浅沟槽隔离结构中氧化物307位于硅衬底301表面之上的部分的厚度相当,因此,经步骤S25刻蚀掉氮化硅层303后,氧化物307位于氧化层302表面之上的部分的厚度即为所需的最终形成的浅沟槽隔离结构中氧化物307位于硅衬底301表面之上的部分的厚度。

在步骤S26中,对氧化层的剩余部分和氧化物进行干法刻蚀,直至去除氧化层的剩余部分,形成浅沟槽隔离结构。

示例性地,如图5g所示,利用传统的干法刻蚀工艺去除硅衬底301表面的氧化层302。可以理解的是,由于氧化层302的形成材料与沟槽306内生长的氧化物307所用的材料相同,因此在干法刻蚀过程中氧化物307也会被刻蚀掉与氧化层302相同的厚度,进而,在完全刻蚀掉氧化层302后所形成的浅沟槽隔离结构中,氧化物307位于硅衬底301表面之上的部分的厚度即为所需的厚度。

需要说明的是,本发明各实施例中所列举的数值仅是示例性的,其不应成为对本发明的限制。

综上,本发明优化了浅沟槽隔离结构的制备工艺,能够在不改变氮化硅单位体积内缺陷密度的情况下,极大程度的降低浅沟槽隔离结构中的硅残留,提高了产品良率。

最后应说明的是:显然,上述实施例仅仅是为清楚地说明本发明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明的保护范围之中。

Claims (12)

1.一种浅沟槽隔离结构的制备方法,其中,包括:

在硅衬底表面依次形成第一氧化层、第一氮化硅层、第二氧化层和第二氮化硅层;

形成贯穿所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的窗口;

在所述第二氮化硅层上表面及所述窗口表面形成第三氮化硅层;

去除所述第二氮化硅层上表面和所述窗口底部的第三氮化硅层,形成位于所述窗口侧面的氮化硅侧墙;

于所述窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽;

在所述第二氮化硅层表面、所述沟槽和所述窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物;

去除所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的剩余部分及所述氮化硅侧墙,形成浅沟槽隔离结构。

2.根据权利要求1所述的浅沟槽隔离结构的制备方法,其中,所述第一氮化硅层、所述第二氮化硅层和所述第三氮化硅层的厚度均远小于所述第二氧化层的厚度。

3.根据权利要求1所述的浅沟槽隔离结构的制备方法,其中,所述第一氧化层的厚度小于所述第二氧化层的厚度。

4.根据权利要求1所述的浅沟槽隔离结构的制备方法,其中,所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的总厚度为1100埃~2000埃。

5.根据权利要求4所述的浅沟槽隔离结构的制备方法,其中,所述第一氮化硅层、所述第二氮化硅层和所述第二氧化层的厚度之和为1000埃~1800埃,所述第一氧化层的厚度为50埃~150埃。

6.根据权利要求1所述的浅沟槽隔离结构的制备方法,其中,在形成的所述浅沟槽隔离结构中,所述氧化物位于所述硅衬底表面之上的部分的厚度为100埃~500埃。

7.根据权利要求1所述的浅沟槽隔离结构的制备方法,其中,去除所述第一氧化层、所述第一氮化硅层、所述第二氧化层和所述第二氮化硅层的剩余部分及所述氮化硅侧墙的方法包括:

使用湿法刻蚀去除所述第一氮化硅层、所述第二氮化硅层的剩余部分及所述氮化硅侧墙,使包裹在所述第一氮化硅层、所述第二氮化硅以及所述氮化硅侧墙之间的所述第二氧化层自然脱落;

使用干法刻蚀或湿法刻蚀去除所述第一氧化层。

8.一种浅沟槽隔离结构的制备方法,其中,包括:

在硅衬底表面依次形成氧化层和氮化硅层;

形成贯穿所述氧化层和所述氮化硅层的窗口;

于所述窗口内刻蚀部分硅衬底,形成具有预定深度的沟槽;

在所述氮化硅层表面、所述沟槽和所述窗口内沉积氧化物,并使用化学机械研磨去除多余的沉积的氧化物,以使得经化学机械研磨后所述沟槽区域内的氧化物的上表面与所述氮化硅层的上表面齐平;

利用湿法刻蚀去除所述氮化硅层的剩余部分;

对所述氧化层的剩余部分和所述氧化物进行干法刻蚀,直至去除所述氧化层的剩余部分,形成浅沟槽隔离结构,

其中,经化学机械研磨后的所述氮化硅层的厚度与形成的所述浅沟槽隔离结构中所述氧化物位于所述硅衬底表面之上的部分的厚度之差的绝对值小于100埃。

9.根据权利要求8所述的浅沟槽隔离结构的制备方法,其中,所述氮化硅层的厚度小于所述氧化层的厚度。

10.根据权利要求8所述的浅沟槽隔离结构的制备方法,其中,所述氧化层的形成材料与所述氧化物的材料相同。

11.根据权利要求8所述的浅沟槽隔离结构的制备方法,其中,所述氧化层的厚度为1100埃~1900埃。

12.根据权利要求8所述的浅沟槽隔离结构的制备方法,其中,所述氮化硅层的厚度为100埃~500埃。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202111409309.2A CN114709166A (zh) | 2021-11-25 | 2021-11-25 | 浅沟槽隔离结构的制备方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202111409309.2A CN114709166A (zh) | 2021-11-25 | 2021-11-25 | 浅沟槽隔离结构的制备方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN114709166A true CN114709166A (zh) | 2022-07-05 |

Family

ID=82167775

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202111409309.2A Pending CN114709166A (zh) | 2021-11-25 | 2021-11-25 | 浅沟槽隔离结构的制备方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN114709166A (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN119447024A (zh) * | 2025-01-09 | 2025-02-14 | 合肥晶合集成电路股份有限公司 | 一种半导体结构的制备方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050071208A (ko) * | 2003-12-31 | 2005-07-07 | 동부아남반도체 주식회사 | 반도체 소자의 소자분리막 형성 방법 |

| US20070077723A1 (en) * | 2005-09-30 | 2007-04-05 | Dongbuanam Semiconductor Inc. | Method of forming shallow trench isolation in a semiconductor device |

| CN1956163A (zh) * | 2005-10-27 | 2007-05-02 | 上海华虹Nec电子有限公司 | 实现浅沟道隔离的工艺方法 |

| CN101673703A (zh) * | 2009-09-22 | 2010-03-17 | 上海宏力半导体制造有限公司 | 浅槽隔离结构的制作方法 |

| US20100304548A1 (en) * | 2009-05-29 | 2010-12-02 | Turner Michael D | Silicon Nitride Hardstop Encapsulation Layer for STI Region |

| CN101958269A (zh) * | 2009-07-14 | 2011-01-26 | 无锡华润上华半导体有限公司 | 一种半导体制造方法 |

| CN102420166A (zh) * | 2011-07-01 | 2012-04-18 | 上海华力微电子有限公司 | 氮化硅-二氧化硅-氮化硅阻挡层的浅沟槽隔离刻蚀方法 |

-

2021

- 2021-11-25 CN CN202111409309.2A patent/CN114709166A/zh active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050071208A (ko) * | 2003-12-31 | 2005-07-07 | 동부아남반도체 주식회사 | 반도체 소자의 소자분리막 형성 방법 |

| US20070077723A1 (en) * | 2005-09-30 | 2007-04-05 | Dongbuanam Semiconductor Inc. | Method of forming shallow trench isolation in a semiconductor device |

| CN1956163A (zh) * | 2005-10-27 | 2007-05-02 | 上海华虹Nec电子有限公司 | 实现浅沟道隔离的工艺方法 |

| US20100304548A1 (en) * | 2009-05-29 | 2010-12-02 | Turner Michael D | Silicon Nitride Hardstop Encapsulation Layer for STI Region |

| CN101958269A (zh) * | 2009-07-14 | 2011-01-26 | 无锡华润上华半导体有限公司 | 一种半导体制造方法 |

| CN101673703A (zh) * | 2009-09-22 | 2010-03-17 | 上海宏力半导体制造有限公司 | 浅槽隔离结构的制作方法 |

| CN102420166A (zh) * | 2011-07-01 | 2012-04-18 | 上海华力微电子有限公司 | 氮化硅-二氧化硅-氮化硅阻挡层的浅沟槽隔离刻蚀方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN119447024A (zh) * | 2025-01-09 | 2025-02-14 | 合肥晶合集成电路股份有限公司 | 一种半导体结构的制备方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100424850C (zh) | 浅沟槽隔离结构的制造方法以及半导体结构 | |

| CN102150253B (zh) | 自对准沟槽的形成方法 | |

| CN1323433C (zh) | 具有沟道隔离结构的半导体装置及其制造方法 | |

| JP3539483B2 (ja) | 半導体装置の製造方法 | |

| US6624043B2 (en) | Metal gate CMOS and method of manufacturing the same | |

| CN114038744B (zh) | 一种mos晶体管制作方法及mos晶体管 | |

| KR960005552B1 (ko) | 반도체 소자의 분리막 형성 방법 | |

| JP2002151689A (ja) | 半導体素子及びその形成方法 | |

| CN111354675B (zh) | 浅沟槽隔离结构的形成方法及浅沟槽隔离结构 | |

| CN114709166A (zh) | 浅沟槽隔离结构的制备方法 | |

| US6313007B1 (en) | Semiconductor device, trench isolation structure and methods of formations | |

| US7736990B2 (en) | Semiconductor device and manufacturing method for the same | |

| KR20010046153A (ko) | 반도체장치의 트렌치 구조의 소자분리막 형성방법 | |

| US6586313B2 (en) | Method of avoiding the effects of lack of uniformity in trench isolated integrated circuits | |

| JP5094055B2 (ja) | 半導体素子のコンタクトホール形成方法 | |

| KR100321174B1 (ko) | 반도체장치의 소자분리막 형성방법 | |

| CN114864479A (zh) | 半导体器件及其制作方法 | |

| US20090170276A1 (en) | Method of Forming Trench of Semiconductor Device | |

| CN115763358B (zh) | 半导体器件的制作方法 | |

| KR100728649B1 (ko) | 반도체소자의 소자분리막 제조방법 | |

| KR100710198B1 (ko) | 반도체소자의 격리막 형성방법 | |

| CN119905394A (zh) | 半导体器件的制造方法 | |

| KR100607729B1 (ko) | 반도체 소자의 sti 형성 방법 | |

| TW413883B (en) | Method for using nitride hard mask for local reversed back-etching and CMP to solve the dishing effect encountered during CMP plantarization process | |

| US20080258145A1 (en) | Semiconductor Devices Including an Amorphous Region in an Interface Between a Device Isolation Layer and a Source/Drain Diffusion Layer |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| CB02 | Change of applicant information |

Country or region after: China Address after: 310030 Zhejiang Province, Hangzhou City, Xihu District, Sandun Town, Shengtangba Street No. 19, Shengtang Xin Cheng Applicant after: Jiehuate Microelectronics Co.,Ltd. Address before: Room 901-23, 9 / F, west 4 building, Xigang development center, 298 Zhenhua Road, Sandun Town, Xihu District, Hangzhou City, Zhejiang Province, 310030 Applicant before: Jiehuate Microelectronics Co.,Ltd. Country or region before: China |