CN101281876A - 半导体器件的制造方法以及半导体器件 - Google Patents

半导体器件的制造方法以及半导体器件 Download PDFInfo

- Publication number

- CN101281876A CN101281876A CNA2008100921241A CN200810092124A CN101281876A CN 101281876 A CN101281876 A CN 101281876A CN A2008100921241 A CNA2008100921241 A CN A2008100921241A CN 200810092124 A CN200810092124 A CN 200810092124A CN 101281876 A CN101281876 A CN 101281876A

- Authority

- CN

- China

- Prior art keywords

- lead

- semiconductor device

- conjunction

- wire

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/4501—Shape

- H01L2224/45012—Cross-sectional shape

- H01L2224/45015—Cross-sectional shape being circular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45147—Copper (Cu) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48095—Kinked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48145—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4845—Details of ball bonds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4846—Connecting portions with multiple bonds on the same bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48471—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area being a ball bond, i.e. wedge-to-ball, reverse stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

- H01L2224/48476—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area

- H01L2224/48477—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding)

- H01L2224/48478—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball

- H01L2224/48479—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/485—Material

- H01L2224/48505—Material at the bonding interface

- H01L2224/48599—Principal constituent of the connecting portion of the wire connector being Gold (Au)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/485—Material

- H01L2224/48505—Material at the bonding interface

- H01L2224/48699—Principal constituent of the connecting portion of the wire connector being Aluminium (Al)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49111—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting two common bonding areas, e.g. Litz or braid wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49113—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting different bonding areas on the semiconductor or solid-state body to a common bonding area outside the body, e.g. converging wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49174—Stacked arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4941—Connecting portions the connecting portions being stacked

- H01L2224/4942—Ball bonds

- H01L2224/49422—Ball bonds outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4941—Connecting portions the connecting portions being stacked

- H01L2224/49425—Wedge bonds

- H01L2224/49427—Wedge bonds outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4945—Wire connectors having connecting portions of different types on the semiconductor or solid-state body, e.g. regular and reverse stitches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

- H01L2224/7825—Means for applying energy, e.g. heating means

- H01L2224/783—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/78301—Capillary

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

- H01L2224/8503—Reshaping, e.g. forming the ball or the wedge of the wire connector

- H01L2224/85035—Reshaping, e.g. forming the ball or the wedge of the wire connector by heating means, e.g. "free-air-ball"

- H01L2224/85045—Reshaping, e.g. forming the ball or the wedge of the wire connector by heating means, e.g. "free-air-ball" using a corona discharge, e.g. electronic flame off [EFO]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

- H01L2224/85051—Forming additional members, e.g. for "wedge-on-ball", "ball-on-wedge", "ball-on-ball" connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85148—Aligning involving movement of a part of the bonding apparatus

- H01L2224/85169—Aligning involving movement of a part of the bonding apparatus being the upper part of the bonding apparatus, i.e. bonding head, e.g. capillary or wedge

- H01L2224/8518—Translational movements

- H01L2224/85181—Translational movements connecting first on the semiconductor or solid-state body, i.e. on-chip, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85148—Aligning involving movement of a part of the bonding apparatus

- H01L2224/85169—Aligning involving movement of a part of the bonding apparatus being the upper part of the bonding apparatus, i.e. bonding head, e.g. capillary or wedge

- H01L2224/8518—Translational movements

- H01L2224/85191—Translational movements connecting first both on and outside the semiconductor or solid-state body, i.e. regular and reverse stitches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/852—Applying energy for connecting

- H01L2224/85201—Compression bonding

- H01L2224/85203—Thermocompression bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/852—Applying energy for connecting

- H01L2224/85201—Compression bonding

- H01L2224/85205—Ultrasonic bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/8593—Reshaping, e.g. for severing the wire, modifying the wedge or ball or the loop shape

- H01L2224/85947—Reshaping, e.g. for severing the wire, modifying the wedge or ball or the loop shape by mechanical means, e.g. "pull-and-cut", pressing, stamping

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/85951—Forming additional members, e.g. for reinforcing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85986—Specific sequence of steps, e.g. repetition of manufacturing steps, time sequence

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20751—Diameter ranges larger or equal to 10 microns less than 20 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20752—Diameter ranges larger or equal to 20 microns less than 30 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20753—Diameter ranges larger or equal to 30 microns less than 40 microns

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/20—Parameters

- H01L2924/207—Diameter ranges

- H01L2924/20754—Diameter ranges larger or equal to 40 microns less than 50 microns

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Wire Bonding (AREA)

Abstract

提供一种在将多根导线连接于半导体芯片上的同一电极上的结构中、能够抑制电极面积的半导体器件的制造方法。首先,进行将第1球压接于半导体芯片上的电极的球形结合以形成第1连接部,然后对内部引线进行楔形结合。接着,进行从正上方将第2球压接于第1连接部上的球形结合以形成第2连接部,然后对内部引线进行楔形结合。

Description

技术领域

本发明涉及半导体器件的制造方法以及半导体器件,特别涉及采用引线框或者布线基板的封装技术。

背景技术

近些年,作为半导体器件的形态,广泛地应用了采用引线框的QFP(quad flatpackage:方形扁平封装)等。下面,采用附图来说明以往的一般QFP型半导体器件。

图17表示以往的一般QFP型半导体器件的剖面图,图18表示放大以往的一般QFP型半导体器件的内部结构的一部分后得到的图。

如图17、图18所示,在以往的一般QFP型半导体器件中,形成有集成电路的半导体芯片1安装于引线框的裸片焊盘(ダイパツド)部2上。另外,引线框的多根引线4呈放射状地配置于裸片焊盘部2的周边,该呈放射状配置的各引线4的内部引线4a的前端与裸片焊盘部2对置。另外,导线5将形成于半导体芯片1的表面上的电极3与内部引线4a连接。另外,树脂密封体6将半导体芯片1、导线5和内部引线4a一起进行树脂密封。另外,与内部引线4a连续的引线框的外部引线4b在树脂密封体6的外部弯曲成形为鸥翼型。另外,图18所示的裸片焊盘支座24将裸片焊盘部2保持于引线框。

接着,说明以往的一般QFP型半导体器件的制造方法。

首先,将半导体芯片1安装于用金属板所形成的引线框的裸片焊盘部2上(芯片接合工序)。

另外,因为引线框与多个半导体器件同时形成、或者按顺序依次形成,所以与各半导体器件对应的矩形图案是在同一平面上的左右方向或者上下方向上用框架连接而得到的结构。另外,各矩形图案的结构如下所述,即裸片焊盘部2配置于中央位置,多个引线4的外端部与框架连接,裸片焊盘支座24将裸片焊盘部2保持在框架上。

接着,用导线5连接形成于半导体芯片1的表面的电极3、以及配置于裸片焊盘部2周围的内部引线4a(导线结合工序)。

接着,通过用密封树脂将半导体芯片1、裸片焊盘部2、导线5以及内部引线4a一起进行树脂密封,从而形成树脂密封体6(树脂密封工序)。

最后,将外部引线4b按照规定长度从框架切断,从而分离成单片,然后将外部引线4b加工成规定的形状。

实行上述各工序,从而得到半导体器件的成品。

另外,作为导线结合方法,同时采用超声波及热压接的结合方式是目前的主流方式。该结合方式的工序如下所述。

(1)通过放电在从毛细管前端突出的导线的前端形成球,(2)通过提供热和超声波,同时用毛细管将该球按压在一侧的连接点上,从而使导线的一端(球)与一侧的连接点连接(球形结合),(3)从毛细管引出导线,同时使毛细管向另一侧的连接点侧移动,(4)通过提供热和超声波,同时用毛细管前端部将导线擦压在另一侧的连接点上,从而使导线的另一端与另一侧的连接点连接(楔形结合)。

另外,一般在半导体芯片的电极一侧上进行球形结合。

在上述结构的QFP型半导体器件中,近些年,随着集成电路的高集成化以及高密度化,半导体器件朝着多引脚化以及引线的窄间距化发展(例如,参照香山晋、成濑 邦彦 监修、[实践讲座VLSI组装技术(下)]、日经株式会社BP、1993年5月31日发行、P165~P170。)。然而,即使多引脚化以及引线的窄间距化不断发展,但QFP型半导体器件的外形和引脚数在业界已经形成标准化了。因此,在QFP型半导体器件中,为了在有限的引脚数中保持高集成化后的半导体芯片,集中将电源电极或接地电极等能够通用的电极与同一引线连接。图19A及图19B是表示将分别与多个电极3连接的各导线5和同一内部引线4a连接的状态的模式图。在图19A中,表示将2根导线5与同一内部引线4a连接的状态。另外,在图19B中,表示将3根导线5与同一内部引线4a连接的状态。

发明内容

如上所述,在以往的QFP型半导体器件中,是集中将电源电极和接地电极等能够通用的电极与同一引线连接。另一方面,由于每1个半导体芯片的电路规模飞速增大,所以开始需要用于确保向电源电极及接地电极提供稳定电流的布线。与其相反,由于半导体组装技术的进步和低成本化的要求,开始谋求实现作为半导体器件的布线材料的以Au导线为代表的金属导线的细线化。为了解决这样的相反的两个问题,在以往的QFP型半导体器件中,用多根导线来连接1个电极和1根内部引线。

然而,通常由于为了要以充足的强度来接合导线则需要一定以上的面积,所以在将多根导线与同一电极连接的情况下,过去,必须将电极的面积设置成能够对多根导线进行球形结合的大小。这种情况阻碍了缩小芯片面积。

另外,虽然也有在引线框的同一引线或BGA(ball grid array:球栅阵列)型半导体器件的布线基板上的同一表层布线上、利用球形结合连接多根导线的情况,但是这种情况也同样,必须将引线或表层布线的面积设置成能够对多根导线进行球形结合的大小。这种情况阻碍了缩小组件面积。

本发明鉴于上述问题,目的在于提供一种半导体器件的制造方法及半导体器件,该半导体器件的制造方法及半导体器件是在多根导线与半导体芯片上的同一电极、引线框的同一引线、或者布线基板上的同一表层布线连接的结构中,能够抑制电极面积或者组件面积。

为了达到上述目的,本发明的半导体器件的制造方法包括:第1结合工序和第2结合工序,其中在第1结合工序中,在从导线提供装置突出的导线的前端形成球,进行将该球压接在半导体芯片上的电极或配置于半导体芯片周围的引线或者布线构件上的球形结合,然后使导线提供装置移动,从而对连接对象构件进行楔形结合;在第2结合工序中,在从导线提供装置突出的导线的前端形成球,进行将该球从正上方压接在上述第1结合工序所进行球形结合后的部分上的球形结合,然后使导线提供装置移动,从而对上述第1结合工序中的连接对象构件或者与之不同的连接对象构件进行楔形结合。

另外,在上述半导体器件的制造方法中,上述第2结合工序反复进行2次以上,从而使多根导线与上述电极或者上述引线或者上述布线构件连接。而且,当反复进行上述第2结合工序时,利用楔形结合使至少1根导线与上述第1结合工序中的连接对象构件实现连接。或者,在反复进行上述第2结合工序时,利用楔形结合使至少2根导线和与上述第1结合工序中的连接对象构件不同的同一连接对象构件实现连接。

另外,在上述半导体器件的制造方法中,还包括:在从导线提供装置突出的导线的前端形成球、将该球压接于上述第1结合工序或者上述第2结合工序中进行楔形结合的部分上并形成凸点的凸点形成工序,当进行上述第1结合工序或者上述第2结合工序时,在上述凸点上进行楔形结合。

另外,本发明的第1半导体器件,其包括:半导体芯片;上述半导体芯片所具有的电极;安装上述半导体芯片的芯片安装部;配置于上述芯片安装部周围的引线或者布线构件;将上述半导体芯片所具有的上述电极和上述引线或布线构件连接的导线;以及至少将上述半导体芯片、上述芯片安装部、上述导线、以及上述引线或布线构件的与上述导线的连接部分进行树脂密封的树脂密封体,在上述半导体芯片所具有的上述电极之中的至少一个上,重叠多根上述导线各自一端的连接部以实现连接,并且将它们的连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。

另外,在上述第1半导体器件中,一端与上述半导体芯片所具有的上述电极重叠并连接的多根上述导线之中的至少一部分,它们的另一端与同一上述引线或布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在上述第1半导体器件中,具有多个上述半导体芯片,一端与至少1处的上述半导体芯片所具有的至少1处的上述电极重叠并连接的多根上述导线之中的至少一部分,它们的另一端与其它的上述半导体芯片所具有的电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在上述第1半导体器件中,具有多个上述半导体芯片,一端与至少1处的上述半导体芯片所具有的至少1处的上述电极重叠并连接的多根上述导线的一部分,该一部分的另一端与其它的上述半导体芯片所具有的电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状;而其它的一部分的另一端与上述引线或布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在上述第1半导体器件中,上述芯片安装部以及上述引线是加工金属板而制作得到的引线框的构成构件。

另外,在上述第1半导体器件中,上述芯片安装部以及上述布线构件是布线基板的构成构件。

另外,本发明的第2半导体器件,其包括:半导体芯片;上述半导体芯片所具有的电极;安装上述半导体芯片的芯片安装部;配置于上述芯片安装部周围的引线或者布线构件;将上述半导体芯片所具有的上述电极和上述引线或布线构件的导线;以及至少将上述半导体芯片、上述芯片安装部、上述导线、以及上述引线或布线构件的与上述导线的连接部分进行树脂密封的树脂密封体,在上述引线或者布线构件之中的至少一个上,重叠多根上述导线各自一端的连接部以实现连接,并且将它们的连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。

另外,在上述第2半导体器件中,一端与上述引线或者布线构件重叠并连接的多根上述导线的一部分,该一部分的另一端与其它的上述引线或者布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状;而其它部分的另一端与上述半导体芯片所具有的上述电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在上述第2半导体器件中,具有多个上述半导体芯片,一端与上述引线或者布线构件重叠并连接的多根上述导线之中的至少一部分,它们的另一端与上述半导体芯片所具有的上述电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在上述第2半导体器件中,上述芯片安装部以及上述引线是加工金属板而制作得到的引线框的构成构件。

另外,在上述第2半导体器件中,上述芯片安装部以及上述布线构件是布线基板的构成构件。

如果采用本发明的最佳形态,则在半导体芯片上的同一电极上,无须扩大电极的面积而能够连接2根以上的导线。因此,在将多根导线与半导体芯片上的同一电极连接的结构中,因为无论所连接的导线数量的多少始终都能够将电极的面积设定为最小,所以能够使整个芯片中占有的电极的个数以及面积为最小。因此,通常在半导体芯片中,能够在其外周部配置一排或多排电极,并且使电极的个数以及面积为最小,从而而能够减小芯片尺寸。另外,因为能够将多根导线与同一电极连接,所以能够使用更加细线化的导线,同时能够确保对电源电极或接地电极的稳定的电流容量。

如上所述,因为能够实现确保对电源电极或接地电极的稳定的电流容量,并且能够实现半导体芯片的小型化,所以能够提供一种小型、廉价且高质量的半导体器件。

另外,近些年,由于设备小型化的要求,出现了将多个半导体芯片安装于内部的半导体器件(组件),在这样结构的QFP型半导体器件中,有的情况下,不仅用导线连接各半导体芯片上的电极和引线(内部引线),而且用导线连接互不相同的半导体芯片上的电极之间。

同样地,即使是采用了布线基板的BGA(球栅阵列)型半导体器件,也出现了内部安装多个半导体芯片的组件,即使在这样结构的BGA型半导体器件中,也有的情况下,不仅用导线连接各半导体芯片上的电极和布线基板上的表层布线(布线构件),而且用导线连接互不相同的半导体芯片上的电极之间。

如果采用本发明的最佳形态,则因为能够将与同一电极连接的多根导线之中的一部分和引线(内部引线)或者布线构件(布线基板的表层布线)实现连接,而且将其它部分与另一方的半导体芯片上的电极连接,所以在不增大芯片尺寸的情况下,能够将连接多根导线的电极作为另一方半导体芯片上的电极和引线的过渡电极来使用。另外,由于能够将与同一引线(内部引线)或者布线构件(布线基板的表层布线)连接的多根导线和各不相同的半导体芯片上的电极连接,所以在不增大引线或布线构件的情况下,即在不增大组件的情况下,能够将与多根导线连接的引线或布线构件作为各半导体芯片的电源来使用,或者作为互不相同的半导体芯片上的电极之间的过渡引线或过渡布线来使用。

因此,能够简化装置内的布线,并且能够以高质量且紧凑地构成使用高集成化及高密度化的半导体芯片的半导体器件(半导体组件)。

如上所述,如果采用本发明的半导体器件的制造方法以及半导体器件,则在多根导线与半导体芯片上的同一电极、引线框的同一引线或布线基板上的同一表层布线连接的结构中,能够抑制电极面积或组件面积。因此,对于QFP或BGA等的半导体组件有用。

附图说明

图1是本发明实施形态1的半导体器件的剖面图。

图2A是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的立体图。

图2B是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的俯视图。

图2C是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的剖面图。

图3是用于说明本发明实施形态1的半导体器件的导线结合工序的工序剖面图。

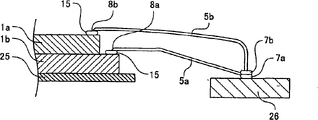

图4是用于说明本发明实施形态1的半导体器件的导线结合工序的其它例1的工序剖面图。

图5是用于说明本发明实施形态1的半导体器件的导线结合工序的其它例2的工序剖面图。

图6是用于说明本发明实施形态1的半导体器件的导线结合工序的其它例3的工序剖面图。

图7是用于说明本发明实施形态2的半导体器件的导线结合部分的内部结构的剖面图。

图8是用于说明本发明实施形态3的半导体器件的导线结合部分的内部结构的剖面图。

图9A是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的俯视图。

图9B是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的剖面图。

图10A是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的其它例子的俯视图。

图10B是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的其它例子的剖面图。

图11是本发明实施形态5的半导体器件的剖面图。

图12是本发明实施形态6的半导体器件的剖面图。

图13A是用于说明本发明实施形态6的半导体器件的导线结合部分的内部结构的俯视图。

图13B是用于说明本发明实施形态6的半导体器件的导线结合部分的内部结构的剖面图。

图14是用于说明本发明实施形态6的半导体器件的导线结合工序的工序剖面图。

图15是本发明实施形态7的半导体器件的剖面图。

图16A是用于说明本发明实施形态7的半导体器件的导线结合部分的内部结构的俯视图。

图16B是用于说明本发明实施形态7的半导体器件的导线结合部分的内部结构的剖面图。

图17是以往的一般QFP型半导体器件的剖面图。

图18表示放大以往的一般QFP型半导体器件的内部结构的一部分后的图。

图19A是表示在以往的一般QFP型半导体器件中将分别与2个电极连接的各导线与同一内部引线连接后的状态的模式图。

图19B是表示在以往的一般QFP型半导体器件中将分别与3个电极连接的各导线与同一内部引线连接后的状态的模式图。

具体实施方式

(实施形态1)

下面,参照附图来说明本发明的实施形态1。

图1是本发明实施形态1的半导体器件的剖面图,图2A是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的立体图,图2B是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的俯视图,图2C是用于说明本发明实施形态1的半导体器件的导线结合部分的内部结构的剖面图。另外,下面的说明中,在同一构件上标有相同的标号,并且适当地省略说明。

该半导体器件是QFP型。如图1所示,在该半导体器件中,形成集成电路的半导体芯片1安装于引线框的冲膜垫部(芯片安装部)2。另外,引线框的引线4呈放射状地配置于冲膜垫部2的周边,该呈放射状配置的各引线4的内部引线4a的前端与冲膜垫部2对置。另外,导线5将形成于半导体芯片1的表面上的电极3与内部引线4a连接。另外,树脂密封体6将半导体芯片1、冲膜垫部2、导线5以及内部引线4a(引线4的导线连接部分)一起进行树脂密封。另外,与内部引线4a连续的引线框的外部引线4b,在树脂密封体6的外部弯曲成形为鸥翼型。

该半导体器件与以往不同之处在于以下2点。即,如图2A~图2C所示,第一点:使2根导线5a、5b的一端的连接部和半导体芯片1上的至少1个电极3重叠以实现连接,并且将它们的连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状;以及第二点:将该2根导线5a、5b的另一端形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状,并且与同一内部引线4a连接。

接着,根据图3所示的工序剖面图来说明将2根导线和同一电极连接的方法。

首先,如图3(a)所示,在从作为导线提供装置的毛细管9的前端所突出的导线5a的前端与焊炬10之间进行放电,从而利用火花形成球11a。

然后,如图3(b)~(d)所示,将球11a压接于半导体芯片1上的电极(球形结合),通过这样形成球形结合侧的连接部7a。

然后,如图3(e)~(g)所示,在水平方向上弯曲并引出导线5a,使毛细管9移动以使导线5a沿着规定的轨迹进行布线,并且将导线5a擦压在作为连接对象构件的内部引线4a上(楔形结合),通过这样形成楔形结合侧的连接部8a。

在进行上述第1结合工序之后,进行第2结合工序。

即,首先,如图3(h)所示,在从毛细管9的前端所突出的导线5b的前端与焊炬10之间进行放电,从而利用火花形成球11b。

接着,如图3(i)所示,从正上方将球11b压接于连接部7a(在第1结合工序中进行球形结合后的部分)上(球形结合),通过这样形成球形结合侧的连接部7b。

然后,如图3(j)~(l)所示,在垂直方向上引出导线5b并弯曲,使毛细管9移动以使导线5b沿着规定的轨迹进行布线,并且将导线5b擦压在作为连接对象构件的内部引线4a上(楔形结合),通过这样形成楔形结合侧的连接部8b。

另外,此处第1结合工序与第2结合工序中的连接对象构件是同一内部引线4a。

如上所述,通过进行第1及第2结合工序,能够利用球形结合法将2根导线各自的一端与同一电极重叠以实现连接。

导线结合工序中所使用的导线中,一般使用以金或铜等金属为原料的直径φ15~40μm的导线。在球形结合法中,形成于导线一端的球的直径是导线直径的1.5倍~4倍左右,当使其与连接点接合时,用毛细管的前端部将其压扁至厚度为5~60μm左右。因此,球形结合侧的连接部形成为从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。

另一方面,因为导线的另一端用毛细管的前端周边部与连接点擦压那样压扁,所以楔形结合侧的连接部形成为无厚度的月牙形或者椭圆形。

另外,例如如图3(g)所示,在球形结合侧的连接部7a的上部存在着导线5a的一部分。因此,为了防止该导线5a的一部分与压接于其上的球11b的连接发生偏移,必须利用毛细管9确实地保持球11b。

对此,如果实施下面所说明的方法,则能够容易地防止连接偏移。

图4是用于说明在同一电极上重叠多根导线以实现连接时、防止连接偏移的方法的工序剖面图。

首先,在第1结合工序后,如图4(a)所示,在从毛细管9的前端所突出的导线5b的前端与焊炬10之间进行放电,从而利用火花形成球11b。

接着,如图4(b)所示,通过将球11b按压在平坦部12上,从而在球11b的下面形成平坦面。

接着,如图4(c)~(d)所示,从正上方将球11b压接于连接部7a上,通过这样形成球形结合侧的连接部7b。

这样,当进行第2结合工序时,在从毛细管9所突出的导线5b的前端上形成球11b之后,通过将球11b按压在平坦部12,在球11b的下面形成平坦部,从而对形成该平坦面后的球11b进行结合。

如果采用该方法,则由于将球11b的下面形成为平坦面,所以能够防止存在于连接部7a的上部的导线5a与球11b接触时的接触偏移。因此,能够实现确实的接合。

另外,作为平坦部12,能够使用例如引线框的一部分或导线接合设备的一部分的平坦面。另外,如后所述,当将本发明应用于BGA型半导体器件时,作为平坦部12,能够使用布线基板的一部分的平坦面。

另外,也可以利用下面说明的方法来防止连接偏移。

即,如图5(a)~(c)所示,在第1结合工序之后,首先,从正上方将前端为圆锥形突起形状的加压工具13按压在连接部7a上,从而压扁连接部7a。

接着,如图5(d)~(e)所示,从正上方将球11b压接于压扁后的连接部7a上,通过这样形成球形结合侧的连接部7b。

因为在被加压工具13的前端部按压的连接部7a的上部具有圆锥形的凹坑,所以能够确实地将球11b对准在该凹坑的中央位置。通过这样能够实现更确实的接合。

另外,加压工具13的前端部的圆锥顶角角度最好设定为120~170°的钝角。

这样,在第2结合工序中,当从正上方将加压工具按压于进行球形结合的部分(连接部7a)上以压扁该部分(连接部7a)之后,在该压扁后的部分上进行球形结合。

另外,也可以利用下面所说明的方法来防止结合偏移。该方法仅在将加压工具的前端形成为球面型的突起形状这一点上,与上述方法不同。

即,如图6(a)~(c)所示,在第1结合工序之后,首先,从正上方将前端为球面型的突起形状的加压工具14按压在连接部7a上,从而压扁连接部7a。

接着,如图6(d)、(e)所示,从正上方将球11b压接于压扁后的连接部7a上,通过这样形成球形结合侧的连接部7b。

在被加压工具13的前端部按压的连接部7a的上部形成球面型的凹坑,当将球11b压接于连接部7a上时,首先,因为球11b和该凹坑的中心部实现点接触,所以能够确实地进行对位。另外,通过将凹坑形成为球面型,从而能够实现没有空隙的确实的接合。

另外,加压工具14的前端部的球面半径最好设定在球11b的半径的1.5~5倍的范围内。

如果采用以上所说明的方法,则再利用球形结合法将其它导线的一端连接在利用球形结合法所形成的连接部上时,能够防止接触偏移。

另外,在本实施形态1中,虽然说明的是将与同一电极连接的多根导线的各自的另一端和同一内部引线连接的情况,但是也可以将这些导线和互不相同的内部引线连接。

(实施形态2)

接着,参照附图来说明本发明的实施形态2。图7是用于说明本发明实施形态2的半导体器件的导线结合部分的内部结构的剖面图。但是,在与上述实施形态1所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件的结构是,利用球形结合法将3根导线各自的一端重叠于半导体芯片上的至少1个电极上以实现连接,利用楔形结合法将该3根导线各自的另一端和同一内部引线上的不同位置连接,这一点与上述实施形态1不同。

即,如图7所示,在半导体芯片1上的同一电极上,重叠并形成导线5a~5c的球形结合侧的连接部7a~7c。另外,在同一内部引线4a上的不同位置,形成导线5a~5c的楔形结合侧的连接部8a~8c。该连接能够通过反复进行2次实施形态1中所说明的第2结合工序来实现。

因为利用该结构能够根据需要来调整电流容量,所以能够提供一种更加小型、高质量且低成本的半导体器件。

另外,在本实施形态2中,虽然说明的是将3根导线连接于同一电极的情况,但是通过反复进行2次以上的第2结合工序,能够将3根以上的导线连接于同一电极上。

(实施形态3)

接着,参照附图来说明本发明的实施形态3。图8是用于说明本发明实施形态3的半导体器件的导线结合部分的内部结构的剖面图。但是,在与上述实施形态1、2所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件的结构是,利用球形结合法将2根导线各自的一端重叠于半导体芯片上的至少1个电极上以实现连接,通过凸点,利用楔形结合法将该2根导线各自的另一端和同一内部引线上的相同连接点连接,这一点与上述实施形态1不同。

即,如图8所示,在导线5a的楔形结合侧的连接部上形成凸点15,并且在该凸点15上形成导线5b的楔形结合侧的连接部。

在从毛细管所突出的导线的前端形成球,再将该球压接于第2结合工序中进行楔形结合的部分,通过这样能够形成该凸点15。

这样,通过在进行导线5b的楔形结合之前实行该凸点形成工序,并且在进行第2结合工序时,在该凸点15上进行楔形结合,从而能够在凸点15上形成导线5b的楔形结合侧的连接部。

如果采用本实施形态3,则因为在球形结合侧和楔形结合侧的两者中,在以往只能够连接1根导线的面积上可以连接多根导线,所以能够在缩小半导体芯片的同时,也能够缩小引线框。另外,提高了布线的自由度。因此,对于半导体器件的小型化有很大的帮助。

另外,因为利用楔形结合法所形成的连接部如上所述是无厚度的月牙形或者椭圆形的形状,所以在保持原样将它垂直重叠进行结合时,使各个导线的连接状态稳定是很重要的。对此,如本实施形态3所述,如果形成凸点,并且在该凸点上进行楔形结合,则由于利用楔形结合所重叠的各导线的连接部能够通过凸点而牢固地接合起来,所以能够实现提高接合可靠性。

另外,在本实施形态3中,虽然说明的是将2个楔形结合侧的连接部重叠的情况,但是通过反复上述的凸点形成工序,并在之前形成好的连接部上形成凸点,则能够重叠3个以上的楔形结合侧的连接部。

(实施形态4)

接着,参照附图来说明本发明的实施形态4。图9A是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的俯视图,图9B是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的剖面图。但是,在与上述实施形态1~3所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件的结构是,将在垂直方向上层叠后的2个半导体芯片安装于裸片焊盘部,且与同一电极连接的多根导线和各不相同的连接对象构件连接,这一点与上述实施形态1~3不同。

即,如图9A、图9B所示,在上方的半导体芯片1a上的同一电极3a上利用球形结合法重叠2根导线5a、5b各自的一端以实现连接,导线5a的另一端利用楔形结合法与下方的半导体芯片1b上的电极3b连接,而导线5b的另一端利用楔形结合法与内部引线4a连接。

另外,此处,在对导线5a进行楔形结合之前,在对导线5a进行楔形结合的部分(电极3b)上形成凸点15,然后在该凸点15上形成导线5a的楔形结合侧的连接部8a。在从毛细管所突出的导线的前端形成球,然后将该球压接于第1结合工序中进行楔形结合的部分(电极3b),从而形成该凸点(凸点形成工序)。

另外,如图10A、图10B所示,也可以将多根导线与下方的半导体芯片1b上的同一电极3b连接。图10A是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的其它例子的俯视图,图10B是用于说明本发明实施形态4的半导体器件的导线结合部分的内部结构的其它例子的剖面图。

即,如图10A、图10B所示,2根导线5a、5b各自的一端利用球形结合法重叠于下方的半导体芯片1b上的同一电极3b上以实现连接,导线5a的另一端利用楔形结合法与内部引线4a连接,而导线5b的另一端利用楔形结合法与上方的导体芯片1a上的电极3a连接。

另外,此处,在对导线5b进行楔形结合之前,在对导线5b形成楔形结合的部分(电极3a)上形成凸点15,然后在该凸点15上形成导线5b的楔形结合侧的连接部8b。在从毛细管所突出的导线的前端形成球,然后将该球压接于第2结合工序中进行楔形结合的部分(电极3a),从而形成该凸点(凸点形成工序)。

另外,虽然说明的是将2根导线各自的一端重叠于半导体芯片上的同一电极上以实现连接的情况,但是,当然也能够将3根以上的导线各自的一端重叠于同一电极上以实现连接。另外,虽然将与同一电极连接的2根导线之中的一根和其它半导体芯片上的电极连接,而将另一根与内部引线连接,但是也不仅限于该连接形态。与同一电极连接的多根导线各自的楔形结合侧的连接对象构件,可以是例如其它半导体芯片上的同一电极,也可以是其它半导体芯片上的不同电极,可以是同一内部引线,也可以是不同的内部引线。另外,当楔形结合侧的连接对象构件是相同时,如实施形态3中所述,也可以通过形成凸点将楔形结合侧的连接部重叠于同一连接点以实现连接。

另外,此处,虽然说明的是将2个半导体芯片配置在垂直方向上的情况,但是即使是在将2个半导体芯片并排配置在同一个面上的结构,或者将3个以上的半导体芯片配置在垂直方向上或并排配置在同一个面上的结构,或者组合并排配置和垂直方向配置而得到的结构,也与本实施形态4相同,能够使与同一电极连接的多根导线连接于互不相同的连接对象构件或者同一连接对象构件上。

如果采用本实施形态4,则能够谋求确保对电源电极或接地电极的稳定的电流容量,同时能够实现导线的细线化,并且能够减少电极的数量或电极的面积、引线的根数或引线的导线连接部的面积、以及芯片间连接用的过渡引线等。因此,如果采用本实施形态4,则能够对于缩小半导体芯片尺寸或高集成化、以及半导体器件的小型化或高集成化做出贡献,并且能够以低成本提供高质量的半导体器件。

(实施形态5)

接着,参照附图来说明本发明的实施形态5。图11是本发明实施形态5的半导体器件的剖面图。但是,在与上述实施形态1~4中所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件是BGA型的半导体器件。如图11所示,对BGA型的半导体器件采用由树脂基材构成、且至少在主面及与主面相反侧的底面上具有金属布线18的布线基板16。

如图11所示,在该半导体器件中,将形成集成电路的半导体芯片1安装于布线基板16的裸片焊盘部(芯片安装部)17上。裸片焊盘部17由作为表层布线的主面侧的金属布线18构成。另外,连接焊盘19呈放射状地配置于裸片焊盘部17的周边,并且连接焊盘19的前端与裸片焊盘部17对置。连接焊盘19由作为表层布线的主面侧的金属布线(布线构件)18构成。另外,导线5将形成于半导体芯片1的表面上的电极3和连接焊盘19连接。再者,主面侧的金属布线18通过穿通孔20与底面侧的金属布线18电连接。另外,树脂密封体21至少对半导体芯片1、裸片焊盘部17、导线5、以及表层布线(布线构件)的和导线5的连接部分(连接焊盘19)进行树脂密封。另外,在底面上形成焊锡球22,该焊锡球22与底面侧的金属布线18电连接。再者,在底面上的没有形成金属布线18的区域,形成抗蚀剂23。

该半导体器件与上述实施形态1相同,在半导体芯片1上的至少1个电极3上利用球形结合法重叠2根导线5各自的一端以实现连接,该2根导线各自的另一端则利用楔形结合法与同一连接焊盘19(布线构件)连接,这一点与以往的情况不同。

另外,该半导体器件中,半导体器件的作为构成材料之一的布线材料不是引线框而是布线基板,仅这一点与上述实施形态1~4不同。因此,通过将上述实施形态1~4中的内部引线换成连接焊盘(布线构件),从而能够实施与上述实施形态1~4中的半导体器件具有相同构造的半导体器件。

即,在BGA型半导体器件中,与实施形态1相同,能够在同一电极上重叠2根导线各自的一端以实现连接(参照图3)。另外,这时与实施形态1相同,也可以在球的下面形成平坦面(参照图4),也可以从正上方将加压工具按压于第2结合工序中进行球形结合的部分上以压扁该部分(参照图5、图6)。

另外,在BGA型半导体器件中,与实施形态2相同,能够利用球形结合法将多根导线各自的一端重叠于半导体芯片上的至少1个电极以实现连接(参照图7)。

另外,在BGA型半导体器件中,与实施形态3相同,能够将与半导体芯片上的至少1个电极连接的多根导线各自的另一端,通过凸点并利用楔形结合法重叠于同一连接焊盘(布线构件)上的同一连接点以实现连接(参照图8)。

另外,在组件内部安装有多个半导体芯片的BGA型半导体器件中,与实施形态4相同,能够将与同一电极连接的多根导线和互不相同的连接对象构件或同一连接对象构件连接(参照图9A、图9B、图10A、图10B)。

因此,即使在以BGA为代表的使用布线基板作为布线材料的半导体器件中,也能够以低成本提供使用高集成化后的高质量的半导体芯片的半导体器件。

(实施形态6)

下面,参照附图来说明本发明的实施形态6。图12是本发明实施形态6的半导体器件的剖面图,图13A是用于说明本发明实施形态6的半导体器件的导线结合部分的内部结构的俯视图,图13B是用于说明本发明实施形态6的半导体器件的导线结合部分的内部结构的剖面图。但是,在与上述实施形态1~5所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件的结构是,利用球形结合法将2根导线各自的一端重叠于布线基板的同一连接焊盘(布线构件)上以实现连接,并且这些导线与互不相同的半导体芯片上的电极连接,这一点与上述的实施形态5不同。

即,在本实施形态6中,如图12、图13A以及图13B所示,2根导线5a、5b各自一端的连接部重叠于同一连接焊盘19以实现连接,并且将这些连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。另外,将在垂直方向上层叠的2个半导体芯片1a、1b安装于裸片焊盘部(芯片安装部)17上。然后,导线5a的另一端与下方的半导体芯片1b的电极3b连接,且将该导线5a的另一端形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外此处,在对导线5a进行楔形结合之前,在对导线5a进行楔形结合的部分(电极3b)上形成凸点15,然后在该凸点15上形成导线5a的楔形结合侧的连接部8a。在从毛细管所突出的导线的前端形成球,并且将该球压接于第1结合工序中进行楔形工序的部分(电极3b)上,从而形成该凸点(凸点形成工序)。

而且,在对导线5b进行楔形结合之前,在对导线5b进行楔形结合的部分(电极3a)上形成凸点15,然后在该凸点15上形成导线5b的楔形结合侧的连接部8b。在从毛细管所突出的导线的前端形成球,并且将该球压接于第2结合工序中进行楔形结合的部分(电极3a)上,从而形成该凸点(凸点形成工序)。

接着,根据图14所示的工序剖面图来说明将2根导线连接在同一连接焊盘上的方法。另外,此处虽然说明的是分别预先在各结合工序中作为连接对象构件的半导体芯片1a、1b的电极3a、3b上形成凸点15的情况,但是形成凸点15的时刻只要在各结合工序中实行楔形结合之前即可。

首先,如图14(a)所示,在从作为导线提供装置的毛细管9的前端所突出的导线5a的前端与焊炬10之间进行放电,从而利用火花形成球11a。

然后,如图14(b)~(d)所示,将球11a压接于布线基板16的连接焊盘19(球形结合),通过这样形成球形结合侧的连接部7a。

然后,如图14(e)~(g)所示,在水平方向上弯曲并引出导线5a,使毛细管9移动以使导线5a沿着规定的轨迹进行布线,并且将导线5a擦压在作为连接对象构件的形成于半导体芯片1b的电极3b上的凸点15上(楔形结合),通过这样形成楔形结合侧的连接部8a。

在进行上述第1结合工序之后,进行第2结合工序。

即,首先,如图14(h)所示,在从毛细管9的前端所突出的导线5b的前端与焊炬10之间进行放电,从而利用火花形成球11b。

接着,如图14(i)所示,从正上方将球11b压接于连接部7a(在第1结合工序中进行球形结合后的部分)上(球形结合),通过这样形成球形结合侧的连接部7b。

然后,如图14(j)~(l)所示,在垂直方向上引出导线5b并弯曲,使毛细管9移动以使导线5b沿着规定的轨迹进行布线,并且将导线5b擦压在作为连接对象构件的形成于半导体芯片1a的电极3a上的凸点15上(楔形结合),通过这样形成楔形结合侧的连接部8b。

通过这样进行第1及第2结合工序,从而能够利用球形结合法将2根导线各自的一端重叠于同一连接焊盘(布线构件)以实现连接。另外,当重叠多根导线各自的一端时,与实施形态1相同,可以在球的下面形成平坦面(参照图4),也可以从正上方将加压工具按压于第2结合工序中进行球形结合的部分上并将该部分压扁(参照图5、图6)。

如上所述,该半导体器件的结构是,利用球形结合法将多根导线各自的一端重叠于布线基板的同一连接焊盘(布线构件)上以实现连接,并且将这些与同一连接焊盘连接的多根导线连接于互不相同的连接对象构件上,这一点与以往的情况不同。

另外,与实施形态2相同,能够利用球形结合法将多根导线各自的一端重叠于同一连接焊盘上以实现连接(参照图7)。

另外,与实施形态3相同,将与同一连接焊盘连接的多根导线各自的另一端,通过凸点并利用楔形结合法重叠于同一半导体芯片上的同一电极、或布线基板上的其它连接焊盘上以实现连接(参照图8)。

如果采用本实施形态6,则在以BGA为代表的使用布线基板作为布线材料的半导体器件中,能够容易地缩小布线基板的导线连接部的面积,并且能够以低成本来提供高质量的半导体器件。

(实施形态7)

下面,参照附图来说明本发明的实施形态7。图15是本发明实施形态7的半导体器件的剖面图,图16A是用于说明本发明实施形态7的半导体器件的导线结合部分的内部结构的俯视图,图16B是用于说明本发明实施形态7的半导体器件的导线结合部分的内部结构的剖面图。但是,在与上述实施形态1~6所说明的构件相同的构件上标有相同的标号,并且省略说明。

该半导体器件是QFN(quad flat non-lead package:无引线方形扁平封装)型或者SON(small outline non-lead package:无引线小外形封装)型的半导体器件。

如图15、图16A及图16B所示,在该半导体器件中,在垂直方向上层叠形成集成电路的半导体芯片1a、1b,并且将该层叠后的半导体芯片1a、1b安装于引线框的裸片焊盘部(芯片安装部)25上。另外,引线框的内部引线(引线)26呈放射状地配置于裸片焊盘部25的周边,且这些内部引线26的前端与裸片焊盘部25对置。另外,导线5将形成于半导体芯片1a、1b的表面的电极3a、3b和内部引线(引线)26连接。再者,树脂密封体6将半导体芯片1、裸片焊盘部25、导线5以及内部引线26一起进行树脂密封。内部引线26的下面从树脂密封体6的下面露出。

该半导体器件的布线材料不是布线基板而是引线框,只有这一点与上述实施形态6不同。即,在本实施形态7中,如图15、图16A及图16B所示,将2根导线5a、5b各自一端的连接部重叠于同一内部引线(引线)26上以实现连接,并且将这些连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。然后,导线5a的另一端与下方的半导体芯片1b的电极3b连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。另外,导线5b的另一端与上方的半导体芯片1a的电极3a连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

另外,在该QFN型或者SON型的半导体器件中,当将多根导线各自的一端重叠于同一内部引线(引线)上以实现连接时,与实施形态1相同,可以在球的下面形成平坦面(参照图4),也可以从正上方将加压工具按压于第2结合工序中进行球形结合的部分上并压扁该部分(参照图5、图6)。

另外,在该QFN型或者SON型的半导体器件中,与实施形态2相同,利用球形结合法,能够将多根导线各自的一端重叠于同一内部引线(引线)上以实现连接(参照图7)。

另外,在该QFN型或者SON型的半导体器件中,与实施形态3相同,能够通过凸点并利用楔形结合法,将与同一内部引线(引线)连接的多根导线各自的另一端重叠于同一半导体芯片上的同一电极、或者其它的内部引线(引线)上以实现连接(参照图8)。

另外此处,虽然说明的是QFN型或者SON型的半导体器件,但是即使在具有与QFN型或者SON型的半导体器件同样内部结构的QFP型半导体器件等的、采用引线框的树脂密封型半导体器件中,也同样能够利用球形结合法将多根导线各自的一端重叠于同一引线上以实现连接,并且将该与同一引线连接的多根导线和互不相同的连接对象构件或者同一连接对象构件连接起来。

如果采用本实施形态7,则在以QFN、SON、QFP为代表的使用引线框作为布线材料的半导体器件中,能够容易地缩小引线上的导线连接部的面积,并且能够以低成本来提供高质量的半导体器件。

Claims (16)

1.一种半导体器件的制造方法,其特征在于,

包括:第1结合工序和第2结合工序,

其中在第1结合工序中,在从导线提供装置突出的导线的前端形成球,进行将该球压接在半导体芯片上的电极或配置于半导体芯片周围的引线或者布线构件上的球形结合,然后使导线提供装置移动,从而对连接对象构件进行楔形结合;

在第2结合工序中,在从导线提供装置突出的导线的前端形成球,进行将该球从正上方压接在所述第1结合工序所进行球形结合后的部分上的球形结合,然后使导线提供装置移动,从而对所述第1结合工序中的连接对象构件或者与之不同的连接对象构件进行楔形结合。

2.如权利要求1中所述的半导体器件的制造方法,其特征在于,

所述第2结合工序反复进行2次以上,从而使多根导线与所述电极或者所述引线或者所述布线构件连接。

3.如权利要求2中所述的半导体器件的制造方法,其特征在于,

当反复进行所述第2结合工序时,利用楔形结合使至少1根导线与所述第1结合工序中的连接对象构件实现连接。

4.如权利要求2中所述的半导体器件的制造方法,其特征在于,

在反复进行所述第2结合工序时,利用楔形结合使至少2根导线和与所述第1结合工序中的连接对象构件不同的同一连接对象构件实现连接。

5.如权利要求1中所述的半导体器件的制造方法,其特征在于,

还包括:在从导线提供装置突出的导线的前端形成球、将该球压接于所述第1结合工序或者所述第2结合工序中进行楔形结合的部分上以形成凸点的凸点形成工序,当进行所述第1结合工序或者所述第2结合工序时,在所述凸点上进行楔形结合。

6.一种半导体器件,其特征在于,

包括:

半导体芯片;

所述半导体芯片所具有的电极;

安装所述半导体芯片的芯片安装部;

配置于所述芯片安装部周围的引线或者布线构件;

将所述半导体芯片所具有的所述电极和所述引线或布线构件连接起来的导线;以及

至少将所述半导体芯片、所述芯片安装部、所述导线、以及所述引线或布线构件的与所述导线的连接部分用树脂密封的树脂密封体,

在所述半导体芯片所具有的所述电极之中的至少一个上,重叠多根所述导线各自一端的连接部以实现连接,并且将它们的连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。

7.如权利要求6所述的半导体器件,其特征在于,

一端与所述半导体芯片所具有的所述电极重叠并连接的多根所述导线之中的至少一部分,它们的另一端与同一所述引线或布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

8.如权利要求6所述的半导体器件,其特征在于,

具有多个所述半导体芯片,一端与至少1处的所述半导体芯片所具有的至少1处的所述电极重叠并连接的多根所述导线之中的至少一部分,它们的另一端与其它的所述半导体芯片所具有的电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

9.如权利要求6所述的半导体器件,其特征在于,

具有多个所述半导体芯片,一端与至少1处的所述半导体芯片所具有的至少1处的所述电极重叠并连接的多根所述导线的一部分,该一部分的另一端与其它的所述半导体芯片所具有的电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状;而其它的一部分的另一端与所述引线或布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

10.如权利要求6所述的半导体器件,其特征在于,

所述芯片安装部以及所述引线是加工金属板而制作得到的引线框的构成构件。

11.如权利要求6所述的半导体器件,其特征在于,

所述芯片安装部以及所述布线构件是布线基板的构成构件。

12.一种半导体器件,其特征在于,

包括:

半导体芯片;

所述半导体芯片所具有的电极;

安装所述半导体芯片的芯片安装部;

配置于所述芯片安装部周围的引线或者布线构件;

将所述半导体芯片所具有的所述电极和所述引线或所述布线构件连接起来的导线;以及

至少将所述半导体芯片、所述芯片安装部、所述导线、以及所述引线或布线构件的与所述导线的连接部分用树脂密封的树脂密封体,

在所述引线或者布线构件之中的至少一个上,重叠多根所述导线各自一端的连接部以实现连接,并且将它们的连接部形成为球形结合法特有的、从压扁成具有厚度的硬币状的突起部的大致中央引出导线的形状。

13.如权利要求12所述的半导体器件,其特征在于,

一端与所述引线或者布线构件重叠并连接的多根所述导线的一部分,该一部分的另一端与其它的所述引线或者布线构件连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状;而其它部分的另一端与所述半导体芯片所具有的所述电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

14.如权利要求12所述的半导体器件,其特征在于,

具有多个所述半导体芯片,一端与所述引线或者布线构件重叠并连接的多根所述导线之中的至少一部分,它们的另一端与所述半导体芯片所具有的所述电极连接,并且将其形成为楔形结合法特有的无厚度的月牙形或者椭圆形的形状。

15.如权利要求12所述的半导体器件,其特征在于,

所述芯片安装部以及所述引线是加工金属板而制作得到的引线框的构成构件。

16.如权利要求12所述的半导体器件,其特征在于,

所述芯片安装部以及所述布线构件是布线基板的构成构件。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007097904 | 2007-04-04 | ||

| JP2007-097904 | 2007-04-04 | ||

| JP2008-029858 | 2008-02-12 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101281876A true CN101281876A (zh) | 2008-10-08 |

Family

ID=40014266

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2008100921241A Pending CN101281876A (zh) | 2007-04-04 | 2008-04-03 | 半导体器件的制造方法以及半导体器件 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2008277751A (zh) |

| CN (1) | CN101281876A (zh) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102339766A (zh) * | 2010-07-22 | 2012-02-01 | 上海华虹Nec电子有限公司 | 线路修复中的超长距离连线方法 |

| CN102804372A (zh) * | 2009-12-22 | 2012-11-28 | 泰塞拉公司 | 具有降低电感的结合键合元件的微电子组件 |

| CN102820236A (zh) * | 2011-06-08 | 2012-12-12 | 无锡华润安盛科技有限公司 | 一种预塑封引线框的引线键合方法 |

| CN111670489A (zh) * | 2018-02-07 | 2020-09-15 | 三菱电机株式会社 | 楔形工具、键合装置以及键合检查方法 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8692370B2 (en) | 2009-02-27 | 2014-04-08 | Semiconductor Components Industries, Llc | Semiconductor device with copper wire ball-bonded to electrode pad including buffer layer |

| JP5411553B2 (ja) * | 2009-03-31 | 2014-02-12 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 半導体装置の製造方法 |

| JP2012044034A (ja) * | 2010-08-20 | 2012-03-01 | Stanley Electric Co Ltd | 半導体発光装置および半導体発光装置の製造方法 |

| JP2014170801A (ja) * | 2013-03-01 | 2014-09-18 | Sumitomo Electric Ind Ltd | 半導体装置 |

| JP2015146393A (ja) * | 2014-02-03 | 2015-08-13 | カルソニックカンセイ株式会社 | 超音波ウェッジボンディング構造 |

-

2008

- 2008-02-12 JP JP2008029858A patent/JP2008277751A/ja not_active Withdrawn

- 2008-04-03 CN CNA2008100921241A patent/CN101281876A/zh active Pending

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102804372A (zh) * | 2009-12-22 | 2012-11-28 | 泰塞拉公司 | 具有降低电感的结合键合元件的微电子组件 |

| CN102339766A (zh) * | 2010-07-22 | 2012-02-01 | 上海华虹Nec电子有限公司 | 线路修复中的超长距离连线方法 |

| CN102820236A (zh) * | 2011-06-08 | 2012-12-12 | 无锡华润安盛科技有限公司 | 一种预塑封引线框的引线键合方法 |

| CN102820236B (zh) * | 2011-06-08 | 2015-08-26 | 无锡华润安盛科技有限公司 | 一种预塑封引线框的引线键合方法 |

| CN111670489A (zh) * | 2018-02-07 | 2020-09-15 | 三菱电机株式会社 | 楔形工具、键合装置以及键合检查方法 |

| CN111670489B (zh) * | 2018-02-07 | 2024-04-19 | 三菱电机株式会社 | 楔形工具、键合装置以及键合检查方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008277751A (ja) | 2008-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101281876A (zh) | 半导体器件的制造方法以及半导体器件 | |

| US8501542B2 (en) | Double-faced electrode package, and its manufacturing method | |

| US10515934B2 (en) | Semiconductor device | |

| US9087827B2 (en) | Mixed wire semiconductor lead frame package | |

| US6583483B2 (en) | Semiconductor device and its manufacturing method | |

| US20100007009A1 (en) | Semiconductor package and method for processing and bonding a wire | |

| US20100200981A1 (en) | Semiconductor package and method of manufacturing the same | |

| US20060088956A1 (en) | Method for fabricating semiconductor package with short-prevented lead frame | |

| CN104143518A (zh) | 制造半导体器件的方法以及半导体器件 | |

| CN102576684A (zh) | 半导体装置及其制造方法 | |

| CN101364578A (zh) | 半导体器件和该半导体器件的制造方法 | |

| US20110151622A1 (en) | Method of manufacturing semiconductor device | |

| US20080001304A1 (en) | Stack package having pattern die redistribution | |

| US8110931B2 (en) | Wafer and semiconductor package | |

| US20030127717A1 (en) | Multi-chip stacking package | |

| TWI358337B (en) | Method and device of continuously wire-bonding bet | |

| US8018075B2 (en) | Semiconductor package, method for enhancing the bond of a bonding wire, and method for manufacturing a semiconductor package | |

| CN101894811A (zh) | 具有散热块外露的四面扁平封装结构、电子组装体与制程 | |

| JP5266371B2 (ja) | 半導体装置及びその製造方法 | |

| JP2005311099A (ja) | 半導体装置及びその製造方法 | |

| US20230275060A1 (en) | Leaded semiconductor package with lead mold flash reduction | |

| CN112670209B (zh) | 一种加热治具及引线上芯片封装方法 | |

| CN101388380A (zh) | 导线架在芯片及芯片在导线架的多芯片堆叠结构 | |

| CN112466830A (zh) | 芯片封装结构 | |

| Gilardoni | Ribbon bonding for high frequency applications advantages of ribbon and the impact on the microwave market |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Open date: 20081008 |