CN100359653C - 用于连结基片的处理和复合元件 - Google Patents

用于连结基片的处理和复合元件 Download PDFInfo

- Publication number

- CN100359653C CN100359653C CNB03808564XA CN03808564A CN100359653C CN 100359653 C CN100359653 C CN 100359653C CN B03808564X A CNB03808564X A CN B03808564XA CN 03808564 A CN03808564 A CN 03808564A CN 100359653 C CN100359653 C CN 100359653C

- Authority

- CN

- China

- Prior art keywords

- substrate

- link

- component

- processing

- link component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 178

- 239000002131 composite material Substances 0.000 title claims abstract description 37

- 238000000034 method Methods 0.000 title abstract description 15

- 239000011521 glass Substances 0.000 claims abstract description 51

- 239000000463 material Substances 0.000 claims abstract description 34

- 238000012545 processing Methods 0.000 claims description 52

- 230000008020 evaporation Effects 0.000 claims description 48

- 238000001704 evaporation Methods 0.000 claims description 48

- 235000012431 wafers Nutrition 0.000 claims description 36

- 239000004065 semiconductor Substances 0.000 claims description 22

- 238000005516 engineering process Methods 0.000 claims description 18

- 238000009739 binding Methods 0.000 claims description 9

- 230000027455 binding Effects 0.000 claims description 9

- 229910002056 binary alloy Inorganic materials 0.000 claims description 8

- 230000005611 electricity Effects 0.000 claims description 8

- 230000015572 biosynthetic process Effects 0.000 claims description 7

- 238000000151 deposition Methods 0.000 claims description 6

- 230000008021 deposition Effects 0.000 claims description 5

- 238000004519 manufacturing process Methods 0.000 claims description 5

- 238000003466 welding Methods 0.000 claims description 5

- 230000000712 assembly Effects 0.000 claims description 3

- 238000000429 assembly Methods 0.000 claims description 3

- 125000006850 spacer group Chemical group 0.000 claims description 3

- 238000007740 vapor deposition Methods 0.000 claims description 3

- 238000013461 design Methods 0.000 claims description 2

- 239000013067 intermediate product Substances 0.000 claims 1

- 230000003287 optical effect Effects 0.000 abstract description 6

- 239000000126 substance Substances 0.000 abstract description 3

- 230000001747 exhibiting effect Effects 0.000 abstract 1

- 238000009834 vaporization Methods 0.000 abstract 1

- 238000007789 sealing Methods 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- 229910052710 silicon Inorganic materials 0.000 description 13

- 229920002120 photoresistant polymer Polymers 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 230000008901 benefit Effects 0.000 description 9

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 8

- 239000000853 adhesive Substances 0.000 description 7

- 230000001070 adhesive effect Effects 0.000 description 7

- 238000012360 testing method Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 239000005352 borofloat Substances 0.000 description 5

- 239000005388 borosilicate glass Substances 0.000 description 5

- 239000007789 gas Substances 0.000 description 5

- 239000007788 liquid Substances 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 230000003321 amplification Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 238000005260 corrosion Methods 0.000 description 4

- 230000007797 corrosion Effects 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 238000003199 nucleic acid amplification method Methods 0.000 description 4

- 238000001259 photo etching Methods 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000005520 cutting process Methods 0.000 description 3

- 238000005566 electron beam evaporation Methods 0.000 description 3

- 238000005538 encapsulation Methods 0.000 description 3

- 238000000879 optical micrograph Methods 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 239000002904 solvent Substances 0.000 description 3

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000010276 construction Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 239000012530 fluid Substances 0.000 description 2

- 230000002045 lasting effect Effects 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 230000035699 permeability Effects 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 230000000717 retained effect Effects 0.000 description 2

- 239000005368 silicate glass Substances 0.000 description 2

- 230000000930 thermomechanical effect Effects 0.000 description 2

- 238000005011 time of flight secondary ion mass spectroscopy Methods 0.000 description 2

- XMTQQYYKAHVGBJ-UHFFFAOYSA-N 3-(3,4-DICHLOROPHENYL)-1,1-DIMETHYLUREA Chemical compound CN(C)C(=O)NC1=CC=C(Cl)C(Cl)=C1 XMTQQYYKAHVGBJ-UHFFFAOYSA-N 0.000 description 1

- -1 Borofloat 33 Chemical compound 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 208000037656 Respiratory Sounds Diseases 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 239000004411 aluminium Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 238000005422 blasting Methods 0.000 description 1

- 150000007516 brønsted-lowry acids Chemical class 0.000 description 1

- 150000007528 brønsted-lowry bases Chemical class 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000004320 controlled atmosphere Methods 0.000 description 1

- 239000012809 cooling fluid Substances 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 239000005293 duran Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 230000009931 harmful effect Effects 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 238000001764 infiltration Methods 0.000 description 1

- 230000008595 infiltration Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 229910000833 kovar Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 239000002086 nanomaterial Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000037361 pathway Effects 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03B—MANUFACTURE, SHAPING, OR SUPPLEMENTARY PROCESSES

- C03B19/00—Other methods of shaping glass

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C1/00—Manufacture or treatment of devices or systems in or on a substrate

- B81C1/00015—Manufacture or treatment of devices or systems in or on a substrate for manufacturing microsystems

- B81C1/00261—Processes for packaging MEMS devices

- B81C1/00269—Bonding of solid lids or wafers to the substrate

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C14/00—Glass compositions containing a non-glass component, e.g. compositions containing fibres, filaments, whiskers, platelets, or the like, dispersed in a glass matrix

- C03C14/006—Glass compositions containing a non-glass component, e.g. compositions containing fibres, filaments, whiskers, platelets, or the like, dispersed in a glass matrix the non-glass component being in the form of microcrystallites, e.g. of optically or electrically active material

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C15/00—Surface treatment of glass, not in the form of fibres or filaments, by etching

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C17/00—Surface treatment of glass, not in the form of fibres or filaments, by coating

- C03C17/02—Surface treatment of glass, not in the form of fibres or filaments, by coating with glass

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C17/00—Surface treatment of glass, not in the form of fibres or filaments, by coating

- C03C17/34—Surface treatment of glass, not in the form of fibres or filaments, by coating with at least two coatings having different compositions

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C4/00—Compositions for glass with special properties

- C03C4/12—Compositions for glass with special properties for luminescent glass; for fluorescent glass

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/06—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the coating material

- C23C14/10—Glass or silica

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/10—Containers; Seals characterised by the material or arrangement of seals between parts, e.g. between cap and base of the container or between leads and walls of the container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/291—Oxides or nitrides or carbides, e.g. ceramics, glass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3114—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed the device being a chip scale package, e.g. CSP

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/842—Containers

- H10K50/8426—Peripheral sealing arrangements, e.g. adhesives, sealants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/842—Containers

- H10K50/8428—Vertical spacers, e.g. arranged between the sealing arrangement and the OLED

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C2203/00—Forming microstructural systems

- B81C2203/01—Packaging MEMS

- B81C2203/0172—Seals

- B81C2203/019—Seals characterised by the material or arrangement of seals between parts

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C2203/00—Forming microstructural systems

- B81C2203/03—Bonding two components

- B81C2203/031—Anodic bondings

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2214/00—Nature of the non-vitreous component

- C03C2214/16—Microcrystallites, e.g. of optically or electrically active material

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2217/00—Coatings on glass

- C03C2217/20—Materials for coating a single layer on glass

- C03C2217/21—Oxides

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2217/00—Coatings on glass

- C03C2217/70—Properties of coatings

- C03C2217/77—Coatings having a rough surface

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2218/00—Methods for coating glass

- C03C2218/10—Deposition methods

- C03C2218/15—Deposition methods from the vapour phase

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2218/00—Methods for coating glass

- C03C2218/30—Aspects of methods for coating glass not covered above

- C03C2218/32—After-treatment

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2218/00—Methods for coating glass

- C03C2218/30—Aspects of methods for coating glass not covered above

- C03C2218/32—After-treatment

- C03C2218/328—Partly or completely removing a coating

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2218/00—Methods for coating glass

- C03C2218/30—Aspects of methods for coating glass not covered above

- C03C2218/32—After-treatment

- C03C2218/328—Partly or completely removing a coating

- C03C2218/33—Partly or completely removing a coating by etching

-

- C—CHEMISTRY; METALLURGY

- C03—GLASS; MINERAL OR SLAG WOOL

- C03C—CHEMICAL COMPOSITION OF GLASSES, GLAZES OR VITREOUS ENAMELS; SURFACE TREATMENT OF GLASS; SURFACE TREATMENT OF FIBRES OR FILAMENTS MADE FROM GLASS, MINERALS OR SLAGS; JOINING GLASS TO GLASS OR OTHER MATERIALS

- C03C2218/00—Methods for coating glass

- C03C2218/30—Aspects of methods for coating glass not covered above

- C03C2218/355—Temporary coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01027—Cobalt [Co]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01057—Lanthanum [La]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/85—Arrangements for extracting light from the devices

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P40/00—Technologies relating to the processing of minerals

- Y02P40/50—Glass production, e.g. reusing waste heat during processing or shaping

- Y02P40/57—Improving the yield, e-g- reduction of reject rates

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- Physics & Mathematics (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Power Engineering (AREA)

- Life Sciences & Earth Sciences (AREA)

- Geochemistry & Mineralogy (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Dispersion Chemistry (AREA)

- Optics & Photonics (AREA)

- Joining Of Glass To Other Materials (AREA)

- Micromachines (AREA)

- Solid State Image Pick-Up Elements (AREA)

Abstract

本发明涉及用于连结具有电、半导体、机械和/或光学部件的基片的处理和一种复合元件。本处理适合于基本上不考虑材料的基片连结,特别地也适合于敏感基片,其具有较高的化学和物理稳定性,并/或能制造密封空腔。根据本发明,通过蒸镀在两个基片的其中一个上施加凸起的框以便用作连结元件,该框特别地由可键合玻璃形成。

Description

技术领域

本发明涉及用于连结一般基片的处理并特别涉及用于连结具有电、半导体、机械和/或光学部件的基片的处理,和一种复合元件。

背景技术

连结技术在技术领域中具有广泛的应用。作为实例,这一方面的参考例如形成电子部件的外壳(housing),通过它将电子电路包封起来。

例如,在已知的处理中,半导体芯片上的或者仍然连结于半导体晶片的部件或者集成电路安装有外壳并具有电连结触点。如果在仍然与晶片相连时,安装芯片或者集成电路并且使芯片的接触区域与导向到外部的外壳触点相连,这种安装方法通常被称作晶片级封装处理。它还已知用于包封单个芯片或单元片(die),其称作单单元片封装。

这些处理使用例如环氧树脂粘着性地键合部件。然而,粘着性连结的缺点是化学稳定性低、光学性能差和部件有被粘着剂污染的危险。而且,粘着部位要进行时效处理,会伴随产生连结质量的降低。

人们主要已知的连结技术或者处理还包括所谓的键合。一种特殊类型的键合被称为阳极键合,其中在热的作用下向界面施加电压,驱动电荷载流子扩散。

尽管键合技术与环氧树脂连结相比有很多的优点,但是它们的应用很受限制,使得它们不灵活。

作为实例,阳极键合的不利限制是材料数目非常有限,因为材料中必须具有电荷载流子。例如,阳极键合典型地需要含有碱金属的材料。因此,阳极键合不能适用于广泛的应用。对于其它键合处理也有同样的实际情况。

而且,键合处理不涉及任何堆建(build-up),因此迄今为止它们仅适合于平面平行连结(plane-parallel connection)。这也大大地限制了它们的应用范围。

文献EP 0 280 905说明了用于制造压力传感器的处理,在压力传感器中,在硅晶片上形成了硼硅酸盐玻璃层。玻璃层被描述作为覆盖相应传感器芯片和导电层的母体。然而,硼硅酸盐玻璃层通过溅射在硅传感器晶片的表面上形成。通过溅射形成相对较大的层厚度相当困难而昂贵。尽管所提及的层厚度为5μm,但是在使用溅射处理时,基片会典型地伴随产生大量的热量,这会产生进一步的困难。

文献US 5,825,233说明了用于红外芯片的微包封,其中焊接剂层的施加是通过真空沉积和lift-off技术或者腐蚀或者通过掩模。然而,焊接剂会带来污染的危险。

文献“低温低电压下使用蒸镀玻璃的阳极键合技术”(AnodicBonding Technique under Low-temperature and Low-voltage usingEvaporated Glass)(作者为Woo-Beom Choi,第9届国际真空微电子会议,圣彼得堡,1996)说明了一种处理,其中通过电子束蒸发向硅晶片施加玻璃层。然而,该处理的应用有限。

无论如何,还是非常需要通用而改良的连结处理。

发明内容

因此,本发明的目的是提供一种连结技术,其使用廉价而通用,特别是能够快速而有效地发挥作用。

本发明进一步的目的是提供一种连结技术,其基本上不受待连结的部件或者基片所用材料类型的限制,且特别地还适合于敏感基片。

本发明的另一个目的是提供一种连结技术,其连结具有很高的化学和/或物理稳定性,从而确保持久密封的连结。

本发明的再一个目的是提供一种连结技术,其允许产生空腔或空穴。

本发明的再一个目的是提供一种连结技术,其不仅适合于电力和电子部件还适合于光学、电光学、电子机械和/或光机电系统。

本发明的目的能够通过附加权利要求的主旨以非常简单的方法实现。本发明的有利改进点在从属权利要求中加以限定。

本发明提出了一种用于连结至少两个基片的处理,特别地这些基片具有电、半导体、机械和/或光学部件。

基片优选地用如下的一种或多种材料制成,包括玻璃、陶瓷、或者半导体材料,特别是硅、III-V如GaAs或者GaAlxAs1-x(VCSELs)、II-VI InP(LEDs)以及其它有机或无机材料,例如金属,如科瓦铁镍钴合金。

特别地,在提供了第一基片之后,通过在第一基片的第一表面上构建产生连结元件或者将其添加到第一基片的第一表面。第二基片可以类似地构建或者选择地被解构(unstructured)。

然后,在提供了第二基片之后,通过连结元件将第一和第二基片连结起来。特别地,第二基片的表面与连结元件的表面相连,连结可以是暂时的,例如在进一步的处理步骤期间提供保护,也可以持久的。这样,便能够用单单元片技术或者作为晶片级封装的一部分以非常简单的方式形成复合元件,例如密封或者包封的(housed)芯片或单元片。

在晶片级封装的实例中,第一和第二基片分别由第一和第二晶片形成。通过蒸镀(evaporation coating)在围绕每个半导体区域或后续芯片的第一基片的第一表面上设置框,从而产生大量横向相邻和/或横向相间的框。在两个晶片被连结形成晶片组件之后,随后特别地通过锯切在框之间进行切片从而形成单个芯片。因此有利地是,在单个工作步骤中同时包封了大量的芯片。

该包封特别适合于电子部件,尤其是半导体、光学和/或微机械系统。

其可能应用的范围非常广泛,例如,根据本发明的处理特别适合于包封微机电系统(MEMS)、微光学系统(MOMS)、微光机电系统(MOEMS)或者待连结的位于两基片之一上的传统半导体区域或者元件。在该应用中,连结元件形成微机械部件的选择性暂时停止(optionally temporary stop),例如微开关,或者微透镜。

连结元件优选地是框或者键合框,其沉积在两基片之一的第一表面上,并且在沉积期间持久而牢固地连结于第一基片。该框的层厚度高出基片的第一表面从而提供了合适的键合表面。

特别当框通过多级构建处理(multi-stage structuring process)加以提供时,框为一个或者多个进一步的基片提供了全部或者至少部分的键合表面。

已经证明,特别有利的是,框用二元系(binary system)材料,特别是玻璃,或者用玻璃质材料在第一表面上沉积或者蒸镀形成。所用的玻璃特别的是硅酸盐或者硼硅酸盐玻璃,例如SCHOTT Glas制造的蒸镀玻璃8329和/或G018-189。这种蒸镀或者沉积处理的一个优点是,绝缘玻璃层的应用从室温升至大约150℃,从而甚至在金属基片的实例中,基片表面也不可能出现损坏或者氧化。关于这些内容可以参考专利申请:

DE 202 05 830.1,于2002年4月15日提出申请;

DE 102 22 964.3,于2002年5月23日提出申请;

DE 102 22 609.1,于2002年5月23日提出申请;

DE 102 22 958.9,于2002年5月23日提出申请;

DE 102 52 787.3,于2002年11月13日提出申请;

DE 103 01 559.0,于2003年1月16日提出申请,它们的申请人相同,因此本文特别引用其公开内容作为参考。

因此,所用的连结元件或者框优选地是结构化(structured)的玻璃层,其通过例如蒸镀施加并通过掩模加以构建。已经证明,光刻处理适合于该构建,光刻处理使用例如光刻胶,被特称为lift-off(抬离)技术,且为本领域技术人员所熟知。

然而,也可能使用掩模,其在蒸镀期间被例如粘着连结于基片或者被布置在靶与基片之间。

根据本发明的连结元件,特别是通过蒸镀施加作为框的玻璃层,具有大量的优点。

首先,玻璃对于溶剂、酸和碱具有特别优良的稳定性、密封性和化学稳定性。这些性质与硼硅酸盐玻璃的性质一致。

连结元件的横向位置非常精确,尤其是在使用光刻构建方法的时候。

通过蒸镀施加的连结元件能够具有非常精确的横向尺寸和高度。在本发明人能够确认的范围之内,这甚至基本上不受所用构建方法的影响。

而且,连结元件或框能够作为组件的一部分以低成本例如以晶片级或者成批地加以制造。

而且,该处理非常清洁,因此特别适合于例如MEMS,其中框甚至可以通过蒸镀直接沉积在由MEMS或者其它部件构成的基片上。

框的制造,或者玻璃层的构建优选地在低温下进行,从而能够保留例如抗蚀剂掩模,并还可以用溶剂,如丙酮,加以除去。因此,该处理也适合于对温度敏感的基片,例如塑料基片或有机基片。

而且,制造连结元件或者构建玻璃层不使用强腐蚀性气体和/或液体,结果也可使用敏感的基片。

特别地,下列技术适合于连结两个基片或者将第二基片连结于框或者键合框:粘着连结、焊接和/或键合。

下文清晰地阐明了本发明的超凡优点。该连结技术的应用范围极其广泛,而且即使当一个基片或者两个基片的材料本身不适合阳极键合时,例如无碱金属的玻璃,如SCHOTT Glas制造的AF45、AF37或者AF32,也可能通过连结元件对基片进行阳极键合。如果适当的话,在两个基片的每一个上都施加或者蒸镀一个连结元件。

用阳极可键合材料制成的框,特别是用碱金属玻璃制成的框,可用于阳极键合。该框可以用键合层通过例如被称作直接键合于玻璃基片上的方法与玻璃基片相连。

作为阳极键合的替代,其他合适的处理包括熔化键合、溶胶-凝胶键合和/或低温键合。本领域技术人员完全熟悉这些处理。然而,本发明的一个进一步优点与此有关,因为蒸镀材料或者键合框的材料能够与期望的处理相匹配,而与基片材料无关。因此,用几乎任何期望材料制成的基片都能够通过连结元件用几乎任何键合处理加以结合,结果开启了全新的具有巨大潜力的应用领域。

作为选择或者扩充,框的表面被金属化,然后被合金焊接或者软焊接。如果适当的话,对键合表面进行活化。

作为实例,用作第一和/或第二基片材料的晶片或者芯片用半导体材料例如硅、有机材料、玻璃特别是硅酸盐或者硼硅酸盐玻璃如Borofloat 33、陶瓷或者金属制造。

特别地,框是连续的,例如用直的或者弯曲的金属网条(web)形成的多边形、圆形或者任何其他期望的形状,且第二基片以密封的方式牢固而持久地与框相连。这在框内部形成了密封或者包封区域,使第一和第二基片彼此隔离,特别是在框内形成了空穴或者空腔。因此,在第一基片的表面上,至少框内的区域保持没有框材料。然而,选择地,也可能在金属网条施加具有中断的开口框,以除去空腔。

特别地,框的厚度与特殊的应用相匹配,在两个基片之间形成空腔。已证明适合于上述应用的蒸镀厚度范围为100μm-1μm,优选地为10μm-2μm或4μm。原理上,有可能获得1mm-0.1μm或10nm的厚度,且<10μm或者<3μm的厚度是特别优选的,尽管还可能获得<0.5μm的厚度。

键合表面的宽度可以有很大变化,基本上只受能够获得的用于构建处理的掩模高宽比的限制。宽框可以具有宽度达数毫米的金属网条或者甚至可以占据基片的整个表面。

框具有的结构或者金属网条的宽度优选地≤10mm,特别地≤1mm或者≤100μm,特别优选地为1μm-500μm。在极窄的框中,可能获得<100nm或者甚至只有数十纳米的金属网条宽度。与例如简单的丝网印刷不同,不受材料晶粒尺寸所施加的限制。

根据本发明,lift-off技术还能够用简单的方法为微结构/纳米结构产生好的高宽比,例如3μm/2μm=3∶2。结果,有可能获得>1或者>1.5的高宽比。

因此,利用根据本发明的处理,可能有利于制造非常窄但非常厚或者高的框,从而在被组合的基片之间产生足够的距离,同时能节省横向空间。

此外,本发明人确定出,窄框能够特别良好地加以键合并且具有优良的密封。另一方面,据发现,适当地控制气氛,甚至金属网条宽度为5μm或10μm-1000μm的窄框或玻璃框也能够对密封罩的气体、湿气和侵蚀性介质的形成有效扩散屏障。

作为实例,在空腔内布置和包封或者密封MEMS、MOMS、MOEMS和/或硅芯片或晶片的半导体区域。

此外,有可能在框内设置一个或者多个支持元件,例如支持点或者区域,它们布置在框内第一基片的第一表面上,这优选地与框的制造在相同的处理步骤中实现。支持元件和/或框具有连续的框形状,例如圆形、多边形或者椭圆形,但也可以是框形状的一部分,例如直线、弯角、圆形部分、点,并且基本上起隔离物的作用。

优选地用键合框的上平面作为键合表面,也就是基本上平行于基片表面延伸的蒸镀玻璃表面。在这种情况下,所施加的框具有限定第一基片与一个或多个第二基片之间预定距离的功能。

作为选择,在使用部分框(partial frame)相对于第一基片安装第二基片期间,有可能形成精确的预定倾角。例如对于光学帽(opticalcap),倾斜的设计是有利的,其被称作“单VCSEL封装”,以便利用监视二极管(monitor diode)激光的部分反射。因此,在连结状态下,第一和第二基片特别地相互平行或者彼此相对倾斜。

此外,作为选择,还可能用框的侧壁作为键合表面。而且,非平面表面也有可能用玻璃加以镀覆。

根据本发明特别优选的改进,多个框彼此相互嵌套。这成倍地提高了密封和可靠性。

此外,在框的内部或者嵌套框之间可以引入用于连结目的的粘合剂。选择地,在连结第一和第二基片之前,将预定的流体,也就是预定的非空气气体、液体和/或微粒引入到嵌套框之间的空腔或者空间内。流体能够流过该空间或者通道,并且可以包括冷却液、传感液(sensing liquid)、滤色器和/或一种或多种反应气体。

在保证其上面的两个基片和/或部件在被包封状态下彼此不相接触的前提下,框优选地具有最小的厚度。

根据本发明特别优选的实施例,在其中一个基片,例如在第一基片上布置互连,例如用于接触连结半导体元件的互连。

优选地,通过蒸镀在互连上沉积呈框形状的玻璃层,从而互连至少在部分区域上能够密封地通过框或者被框包封。互连位于金属网条一端或两端上的部分优选地保持洁净,从而允许随后的接触连结。在每种情况下,框的一个金属网条或边缘优选地横贯该互连。因此在将框与第二基片连结起来之后,互连通过框从外部以密封的方式进入到空腔内。互连不仅可以相对于第一基片横向引出,而且可以垂直引出,并且可以以这种方式延伸通过连结元件,从而形成横向或者垂直通过密封的电连结。

如果适当的话(if appropriate),在第一基片的第一表面上制造出框之后,或者更特别地通过蒸镀施加框之后,通过化学机械抛光或者其他合适的处理特别粗糙地对框进行平面化。这有利地补偿了由于互连的厚度导致的不均匀,从而形成均匀的键合。

而且,使第二表面位于第一表面的相对侧,能够在第一基片的第一表面或第二表面上制造对准元件或器材(aid)。这种呈例如框、点和或线形式的对准器材有利于透镜系统或者其他光学或机械部件的对准。

此外,优选地在第一基片的第二表面上,也就是其背表面上,制造另一个连结元件,以便连结多个基片形成堆叠。这也优选地在切片之前执行,从而进一步提高产量。

在下文中,将根据示例性实施例并参考附图更详细地解释本发明,其中相同和类似的元件用相同的指代符号表示,且各种示例性实施例的特征能够彼此组合。

附图说明

附图中:

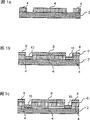

图1a-e显示了根据本发明的第一例证性实施例制造基片组件的各个处理阶段的粗略剖面图,

图2显示了根据本发明第二例证性实施例的基片上嵌套键合框的平面图,

图3显示了沿图2中A-A线的粗略剖面图,

图4显示了图3中C区的放大剪选部分,

图5显示了根据本发明第三例证性实施例的基片上嵌套键合框的粗略平面图,

图6显示了沿图5中D-D线的粗略剖面图,

图7显示了根据本发明第四例证性实施例的具有大量键合框的晶片的粗略平面图,

图8a显示了图7中E区的放大剪选部分,

图8b显示的与图8a相同,但具有通过蒸镀施加的玻璃层,

图8c显示的与图8a相同,但随后进行lift-off步骤,

图9显示了根据本发明第四例证性实施例的键合之后的剪选部分的粗略剖面图,

图10显示了根据本发明的第五例证性实施例具有通过蒸镀加以覆盖的互连的晶片剪选部分的粗略平面图,

图11显示了图10中G区沿H-H线的剖面图的放大图,

图12a显示了图10中G区沿K-K线的剖面图的放大图,

图12b显示的与图12a相同,但显示的是经过平面化步骤之后,

图13显示了键合框形状的八个实例,

图14显示了TOF-SIMS测量的结果,

图15显示了结构化玻璃层的光学显微图象,

图16显示了本发明第六例证性实施例的光学显微图象,

图17显示了本发明第七例证性实施例的光学显微图象,和

图18粗略地描述了具有用于渗透性试验(leaktightness test)的有孔掩模的晶片。

具体实施方式

图1a显示了用金属制成的基片2。选择地,基片2还可以是硅、陶瓷或者玻璃基片。光刻胶4用本领域技术人员已知的处理施加到基片2上,并通过光刻形成图案。在这种情况下,抗蚀剂层代表牢固粘着于基片的掩模。选择地,还可能使用非牢固粘着的遮罩掩模(shadowmask)或者覆盖掩模。

然后,参考图1b,通过蒸镀向基片2和光刻胶4施加由蒸镀玻璃8329构成的连续玻璃层6。

现在参考图1c,用丙酮除去光刻胶4和位于它上面的玻璃层6的部分8。部分10仍保持与金属基片2牢固连结。该处理被称作lift-off处理,且为本领域技术人员所熟知。

现在参考图1d,基片2被保留下来,并具有处于键合框10形式的结构化(structured)的玻璃层。

如图1e所示,用硅制成的覆盖基片12被阳极键合在键合框10上从而形成复合元件20,该键合位置用14表示。由于键合框10的厚度或高度H,形成了高度为H’的空腔16,其高度不会显著大于H,从而上基片12上的半导体部件18与金属基片2具有一定的距离。

再次参考图1b,玻璃层6通过电子束蒸发加以施加。尽管该处理已经为人所知有好几年了,但是迄今为止,它主要用于塑料或玻璃眼镜的机械和光学表面处理,只涉及大面积层(areal layer)的应用。

蒸镀玻璃(脱气的Duran)8329可以实现高达4μm/min的蒸镀速度,特别地为>10nm/min或者>100nm/min。大约500nm/min的速度是特别优选的。这超过例如溅射速度数倍,使得该处理对于根据本发明的应用具有巨大的优点。这是因为由一元系统,例如SiO2,构成的溅射层只能够以每分钟几个纳米的溅射速度加以施加。

给连续玻璃层6设定如下的参数以便将其施加到金属基片2上:

蒸镀期间的BIAS温度:100℃

蒸镀期间的压力:10-4mbar。

而且,所使用的金属基片2的表面粗糙度<50μm,所选用的蒸镀玻璃的热膨胀系数(CTE)的中等dila-thermal方式与金属基片2和/或上基片12相匹配。玻璃8329的CTE为3.3ppm/K,几乎与硅的CTE对应。

通过使用强烈的测试,发明人发现,由SCHOTT Glas制造的玻璃8329或G018-189特别适合于通过热或电子束蒸发镀覆金属。这些蒸镀玻璃对溶剂、湿气(85°,85%,1000h)和温度(T<Tg)具有优良的稳定性。而且,玻璃即使在低温下(<100℃)也具有非常好的热机械性能,因此适合于用作超导电子部件。另一方面,玻璃还能够在高温下(>300℃)使用,因此还可以特别地用于功率电子装置(powerelectronics),例如功率CMOS部件。

图2和3显示了由四个键合框110a-110d构成的布置,它们彼此嵌套,并在基片102上划分出电子部件118的界限。

现在参考图4,向框110a-110d的区域内施加环氧树脂粘合剂124,使框的表面覆盖粘合剂,且框之间的空间也填满粘合剂。这提高了连结强度。而且,框能够更顺利地容纳粘合剂,并简化了粘合剂连结处理。

如果适当的话,粘合剂在真空下施加,以便改良粘合剂中空间收缩(suck)的方式。此外,使用多个框作为裂纹终止以增加复合元件的机械载荷承受能力,并增加可靠性。在这种情况下,多个框,其每一个都具有较小的金属网条宽度b,比具有相同总金属网条宽度B的单个实心框更加轻而稳定。

现在参考图5,在键合框210a-210d内部布置点支持元件226和支持框228,用于支持上基片212和确保空腔的高度H’处于部件218的范围内。

支持元件226和支持框228不与上基片212连结,而是后者仅仅松散地放置在它们上面。

现在参考图7和8a-8c,下文解释微光机电系统(MOEMS)的例证性实施例。结构化的玻璃基片302被用作上基片用来包封图象传感器,作为晶片级封装处理的一部分。在包封中需要空腔作为“隔离物”和“密封元件”。空腔允许微光学系统,例如微透镜和/或微反射镜,发挥作用。

由于玻璃基片302的光学功能,传统的处理不适合于该应用,或者不能够提供廉价的解决方法。尽管材料去除处理,例如腐蚀、研磨、超声波机械加工、喷砂处理或者挤压在原理上能够制造空腔,但是这些处理会对基片302的高品质光学内表面产生不良影响。因此,根据本发明,键合结构通过堆建(build up)提供。

图9图解了具有多个矩形窗口部分303的硅玻璃基片302,每个窗口部分303都完全被光刻胶304覆盖。基片302的热机械性能与第二基片312相匹配,第二基片312是硅晶片并具有CMOS图象传感器(见图9)。基片302用蒸镀玻璃8329形成图案,借此设置大量高度为5μm的框,基片302是经过抛光的Borofloat 33晶片(CTE:3.3ppm/K),其直径为150mm,厚度为500μm。

图7和8a中的光刻胶304已经被结构化,并且在每个窗口部分303的周围都具有矩形凹陷305。抗蚀剂涂层包括,例如,厚度为10μm的AZ,光刻胶在所谓的掩模对准器中加以曝光和显影,然后通过所谓的“软固化”(softcure)加以固化。这允许在例如丙酮中进行后续的lift-off处理。

图8b显示了晶片表面,其在随后的处理步骤中被蒸镀了一个玻璃层。用光刻胶构建的负片图象被蒸镀上一层厚度为5μm的玻璃层,该玻璃层用8329以大约每分钟1μm的沉积速度形成。空腔的后续表面或者窗口部分303用光刻胶掩模加以保护,从而这些区域内的蒸镀玻璃不会与基片302接触,而是沉积在光刻胶掩模上。在未被覆盖的区域305内,玻璃8329直接沉积在基片302上。

然后,通过lift-off技术除去位于抗蚀剂掩模上的沉积玻璃层区域。出于这个目的,在丙酮中溶解光刻胶。区域305中没有光掩模(photomask)的沉积玻璃保留在基片302上,并形成处于键合框310矩阵形式的期望结构。

图8c显示了lift-off处理步骤之后的晶片剪选部分。

现在参考图9,结构化的Borofloat 33晶片302随后被阳极键合到第二基片312上,第二基片312包括多个图象传感器318。因此其结果是大量的光电子复合元件320在晶片水平包封。

最后,通过沿着锯切路径326切片将单个的复合元件320分离开。这种单个的复合元件320在半导体基片312上具有呈图象传感器318形式的光电子复合部件,其在图9中有部分的图解。

在半导体基片上,或者位于图象传感器318上面的晶片312上以及密封空腔318的内部布置呈透镜322形式的凸起的被动光学部件。而且,在空腔316内布置两个可移动的微反射镜324。

透明的Borofloat 33基片302通过键合位置314阳极键合在键合框310上,键合框的高度H为5μm,大于光学部件322和324的高度。结果形成了密封的、至少部分透明的外壳,其空腔高度与图象传感器318、微透镜322和微反射镜324一样,大约为5μm。

由于根据本发明的处理,空腔316区域内的基片玻璃302的光学功能基本上保持不受破坏。

根据本发明制造的框具有进一步的优点,即切片所需的锯切路径保持清晰。

进一步,如下的改变是可能的:

如果基片302将会与另一个玻璃基片相连结,例如对于合金焊接或者阳极键合,则键合层在lift-off处理步骤之前提供。出于这个目的,通过物理气相沉积(PVD)或者化学气相沉积(CVD)沉积金属层作为键合层,或者通过CVD沉积多晶硅键合层。这样,在lift-off处理期间,键合层与框310在同一个工作步骤中构建。

特别是在密封键合的实例中,阳极键合能够在可控的、具有预定气体成分和预定压力的气氛下执行,从而使空腔316具有可控的和预定的气氛。

此外,在空腔316中能够包封气体、生物和/或传感液体、和/或微粒。

图10图解了具有多个半导体区域418的硅晶片402的剪选部分。半导体区域418通过互连430彼此接触连结。通过根据本发明的相应于图1a-1d所示步骤的处理,键合框410的每一个都通过蒸镀施加在属于半导体区域的铝互连上。选择地,互连可以由金、钨或者钛钨形成。金属网条411-414形成矩形键合框410,横贯地布置在互连430上。

这样,特别是对于通过蒸镀施加的键合框或玻璃框410,有可能覆盖不能被阳极键合的结构,例如基片402上的互连430。结果形成了密封的覆盖,特别是具有能够通过互连430的密封路径。在连结到上基片并沿着锯切线426切片之后,形成了大量具有外部接触的密封芯片。

图11显示了图10中G区沿H-H线的剖面的放大剪选部分。

图12a显示了图10中G区在连结到上基片之前沿K-K线的剖面的放大剪选部分。在该实例中,互连430具有2μm的相对大的厚度或高度,且横贯简图的平面。在蒸镀期间,互连430的厚度导致键合框410的上表面415不平整。

现在参考图12b,为了补偿相对延长的形貌和形成合适的平面键合框上表面415,后者通过CMP处理加以平面化。此外,还可能同时进行显著减薄,例如从5μm减薄到4μm。相应的处理过程也能够应用于任何其他的非平面基片。而且,可以想象,键合框可以被切割超出互连430的表面431,从而使互连430能够从上面接触连结(未显示)。

如果互连的厚度更小,典型地为400nm,则如果适当的话,有可能不需要平面化步骤。

如果使用可阳极键合的玻璃,例如8329,进行覆盖,则框能够反过来被阳极键合到上基片。

下文给出了从各种试验中获得的结果,这些试验是都在由玻璃8329通过蒸镀沉积形成的玻璃层上进行的。

图14显示了TOF-SIMS测量的结果,其中计数率被标识为溅射时间的函数。该测量表征了玻璃框元素浓度的概况。确定出玻璃框的厚度恒定度小于层厚度的1%。

图15图解了光刻胶构建的玻璃结构,其由玻璃8329形成,是在lift-off步骤之后通过蒸镀沉积的。

图16显示了复合元件520,其具有Borofloat 33基片502和互连530以及在它们上面蒸镀的玻璃框510,其与第五例证性实施例相似。

互连530的厚度为200nm,玻璃框510的厚度为4μm。在第六例证性实施例中,上基片不经过平面化步骤便被阳极键合。

显然,键合连结仅存在于区域540和542中,而在与互连530相邻的区域544和546中不可能产生键合连结。缺乏键合确实会增加由于互连导致的玻璃框510的表面或上表面不平整。

图17显示了复合元件620,其与复合元件520的结构类似。在复合元件620中,玻璃框610在阳极键合之前被平面化。玻璃框610通过蒸镀施加,厚度为4μm,然后抛光到厚度为大约2μm。互连630的厚度则为200nm。

显然,玻璃框610的整个表面都被键合,结果形成了密封的空腔616。玻璃框610具有300μm的金属网条宽度和3mm×3mm的尺寸。

进而,在玻璃层8329上进行渗透性试验(leaktightness test),如下:

向硅晶片施加腐蚀终止掩模。如图18所示,晶片97被分割成9个有孔区98(1cm×1cm)。在该区域内,孔间的单个间隔行与行之间均不同,如下:

第一行:孔间隔1mm

第二行:孔间隔0.5mm

第三行:孔间隔0.2mm

所有的方孔99都具有15μm的边缘长度。

在晶片的被解构背面上镀覆了8μm(样品A)或者18μm(样品B)的玻璃8329层之后,对晶片上有孔区域内的玻璃进行干腐蚀。腐蚀的效果能够容易地在透光显微镜下进行观察。

有可能获得至少<10-7mbar/sec的渗透速度。对于本例证性实施例,氦渗透测量显示,通过玻璃层的渗透速度<10-8mbar/sec,因此空腔是密闭的。

在测量各个测量区域期间,虽然晶片有相当的膨胀(bulging),但是玻璃层区域仍具有高强度还是出人意料。甚至在200℃的条件之后,玻璃的结构也没有变化。

而且,根据DIN/ISO对玻璃框进行了耐受性和稳定性测量。结果如表1所示。

| 样品名称:8329 | |||

| 水DIN ISO<u>719</u>类 | HCl消耗[ml/g] | Na<sub>2</sub>O当量[μg/g] | 备注 |

| HGB 1 | 0.011 | 3 | 无 |

| 酸DIN<u>12116</u>类 | 材料清除[mg/dm<sup>2</sup>] | 总表面积[cm<sup>2</sup>] | 备注/可见变化 |

| 1 W为材料 | 0.4 | 2×40 | 无变化 |

| 碱DIN ISO<u>695</u>类 | 材料清除[mg/dm<sup>2</sup>] | 总表面积[cm<sup>2</sup>] | 备注/可见变化 |

| A2为材料 | 122 | 2×14 | 无变化 |

本领域技术人员应当清楚,上述的实施例只作为实例,且本发明并不受这些实施例的限制,而是可以有各种改变而不背离本发明的范围。

Claims (40)

1.一种用于连结至少两个基片的处理,所述基片具有电、半导体、机械和光学部件中的至少一个,包括如下步骤:

提供第一基片,

在第一基片的第一表面上形成呈框形式的连结部件,使用二元系材料、玻璃或者玻璃质材料作为框的材料,且二元系材料、玻璃或者玻璃质材料通过以超过100nm/min的沉淀速度进行蒸镀而施加,

提供第二基片,和

通过连结元件连结第一与第二基片。

2.根据权利要求1的处理,其中连结元件沉积在第一基片的第一表面上,并在沉积的同时与第一基片相连结。

3.根据权利要求1或2的处理,其中连结元件通过蒸镀施加到第一基片的第一表面上。

4.根据权利要求1的处理,其中所述框通过蒸镀而被施加,作为连结元件。

5.根据权利要求1的处理,其中在第一基片第一表面上的连结元件内部形成了一个或多个支持元件。

6.根据权利要求1的处理,其中多个嵌套的框通过蒸镀被施加,作为连结元件。

7.根据权利要求1的处理,其中形成连结元件的步骤包括通过蒸镀沉积二元系材料。

8.根据权利要求1的处理,其中玻璃层通过蒸镀施加,并通过掩模加以构建从而形成连结元件。

9.根据权利要求1的处理,其中连结元件通过lift-off技术加以构建。

10.根据权利要求1的处理,其中连结元件和第二基片被粘合地连结、焊接或者键合。

11.根据权利要求1的处理,其中连结元件和第二基片通过阳极键合、熔化键合、溶胶-凝胶键合或者低温键合加以连结。

12.根据权利要求1的处理,其中第一和第二基片分别包括第一和第二晶片,

在第一晶片的第一表面上形成多个横向相邻的连结元件,并且

在第一和第二晶片被连结形成晶片组件之后,晶片组件被切片成单个的芯片。

13.根据权利要求1的处理,其中在第一和第二基片之间和框的内部形成空腔。

14.根据权利要求1的处理,其中在第一基片的第一表面上布置互连,且通过以互连被至少部分覆盖的方式进行蒸镀向第一表面施加连结元件。

15.根据权利要求1的处理,其中互连横向或者垂直地延伸通过连结元件。

16.根据权利要求1的处理,其中连结元件在第一基片的第一表面上形成之后进行平面化。

17.根据权利要求1的处理,其中在第一基片的第一或第二表面上形成对准元件,该第二表面位于第一表面的相对侧。

18.根据权利要求1的处理,其中多个基片被连结形成堆叠。

19.一种复合元件,具有电、电子、半导体、机械和光学部件中的至少一个,且用根据权利要求1的处理制造,包括

第一基片,

连结元件,其位于第一基片的第一表面上,连结元件是用二元系材料、玻璃或者玻璃质材料制成的框,且连结元件通过以超过100nm/min的沉淀速度进行蒸镀而施加到第一基片的第一表面上,

第二基片,

该第一和第二基片通过连结元件相互连结。

20.根据权利要求19的复合元件,其中连结元件沉积在第一基片的第一表面上,并与第一基片相连结。

21.根据权利要求19或20的复合元件,其中在连结元件内的第一基片的第一表面上布置一个或多个支持元件。

22.根据权利要求19的复合元件,其包括多个嵌套的框作为连结元件。

23.根据权利要求19的复合元件,其中连结元件包括结构化的玻璃层。

24.根据权利要求19的复合元件,其中连结元件是结构化的,且该结构化是通过lift-off技术形成的结构化。

25.根据权利要求19的复合元件,其中连结元件和第二基片彼此被粘合地连结、焊接或者键合。

26.根据权利要求19的复合元件,其中连结元件和第二基片被连结,且该连结是通过阳极键合、熔化键合、溶胶-凝胶键合或者低温键合形成的结合。

27.根据权利要求19的复合元件,其中第一和第二基片分别包括第一和第二晶片,

在第一晶片的第一表面上布置有多个横向相邻的连结元件,且

连结元件连结于第二基片的表面。

28.根据权利要求19的复合元件,其中在第一和第二基片之间和框内部形成了空腔。

29.根据权利要求28的复合元件,其中空腔是密封的。

30.根据权利要求19的复合元件,其中在第一基片的第一表面上布置互连,且互连至少部分地被连结元件覆盖。

31.根据权利要求19的复合元件,其中互连横向或者垂直地延伸通过连结元件。

32.根据权利要求19的复合元件,其中连结元件的至少一个表面被平面化。

33.根据权利要求19的复合元件,其中在第一基片的第一或第二表面上布置对准元件,该第二表面位于第一表面的相对侧。

34.一种用于制造根据权利要求19的复合元件的中间产品,具有电、电子、半导体、机械和光学部件中的至少一个,包括

第一基片,

连结元件,其位于第一基片的第一表面上,该连结元件是用二元系材料、玻璃或者玻璃质材料形成的框,且连结元件通过以超过100nm/min的沉淀速度进行蒸镀而施加到第一基片的第一表面,且

该连结元件以如下方式设计,即第一基片能够通过连结元件连结于第二基片。

35.一种堆叠复合元件,包括多个根据权利要求19的复合元件,这些复合元件彼此互相连结。

36.一种框形式的结构的使用,该框结构由二元系材料、玻璃或玻璃质材料形成,用于连结两个基片,其根据权利要求1的处理通过蒸镀施加,用作两个基片之间的隔离物或者作为对准元件。

37.一种用于根据权利要求1来连结具有电或者光学部件的基片的处理,其中

提供第一和第二基片,

在第一步中,向第一基片的至少一个表面施加框,使用玻璃作为框的材料,且玻璃通过以超过100nm/min的沉淀速度进行蒸镀而施加,和

在随后的第二步中,第二基片的表面被连结或者键合于框,在第一和第二基片之间以及框的内部形成空腔。

38.一种复合元件,其在基片上具有电或者光学部件,其如权利要求19所述的那样,包括

第一和第二基片,

至少一个被施加到第一基片表面上的框,该框包括通过以超过100nm/min的沉淀速度进行蒸镀而施加的结构化玻璃层,和

连结区域,其中框的表面被连结或者键合到第二基片的表面,

空腔,其在框内的第一和第二基片之间形成。

39.一种用于连结至少两个基片的处理,所述基片具有电、半导体、机械和光学部件中的至少一个,包括如下步骤:

提供第一基片,

在第一基片的第一表面上,通过以超过100nm/min的沉淀速度来蒸镀玻璃层而形成连结元件,

提供第二基片,和

通过连结元件连结第一与第二基片,

多个嵌套的框被形成作为连结元件。

40.一种复合元件,具有电气、电子、半导体、机械和光学部件中的至少一个,所述复合元件是根据权利要求39的处理制造的,包括

第一基片,

连结元件,其通过以超过100nm/min的沉淀速度来蒸镀玻璃层而形成于第一基片的第一表面上,

第二基片,

该第一和第二基片通过连结元件连结,以及

被提供作为连结元件的多个嵌套的框。

Applications Claiming Priority (13)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE20205830.1 | 2002-04-15 | ||

| DE20205830 | 2002-04-15 | ||

| DE10222964A DE10222964B4 (de) | 2002-04-15 | 2002-05-23 | Verfahren zur Gehäusebildung bei elektronischen Bauteilen sowie so hermetisch verkapselte elektronische Bauteile |

| DE10222964.3 | 2002-05-23 | ||

| DE10222958A DE10222958B4 (de) | 2002-04-15 | 2002-05-23 | Verfahren zur Herstellung eines organischen elektro-optischen Elements und organisches elektro-optisches Element |

| DE10222609.1 | 2002-05-23 | ||

| DE10222958.9 | 2002-05-23 | ||

| DE10222609A DE10222609B4 (de) | 2002-04-15 | 2002-05-23 | Verfahren zur Herstellung strukturierter Schichten auf Substraten und verfahrensgemäß beschichtetes Substrat |

| DE10252787.3 | 2002-11-13 | ||

| DE10252787A DE10252787A1 (de) | 2002-04-15 | 2002-11-13 | Verfahren zur Herstellung eines Kopierschutzes für eine elektronische Schaltung |

| DE10301559.0 | 2003-01-16 | ||

| DE10301559A DE10301559A1 (de) | 2002-04-15 | 2003-01-16 | Verfahren zur Herstellung eines Erzeugnisses mit einer strukturierten Oberfläche |

| PCT/EP2003/003907 WO2003088347A2 (de) | 2002-04-15 | 2003-04-15 | Verfahren zum verbinden von substraten und verbundelement |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1647261A CN1647261A (zh) | 2005-07-27 |

| CN100359653C true CN100359653C (zh) | 2008-01-02 |

Family

ID=44243021

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB03808564XA Expired - Lifetime CN100359653C (zh) | 2002-04-15 | 2003-04-15 | 用于连结基片的处理和复合元件 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7396741B2 (zh) |

| EP (1) | EP1495491B1 (zh) |

| JP (1) | JP2005528782A (zh) |

| CN (1) | CN100359653C (zh) |

| AU (1) | AU2003227626A1 (zh) |

| CA (1) | CA2485022A1 (zh) |

| IL (1) | IL164301A0 (zh) |

| WO (1) | WO2003088347A2 (zh) |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2003237668A1 (en) | 2002-05-23 | 2003-12-12 | Schott Ag | Method for producing a component comprising a conductor structure that is suitable for use at high frequencies and corresponding component |

| DE10350038A1 (de) * | 2003-10-27 | 2005-05-25 | Robert Bosch Gmbh | Verfahren zum anodischen Bonden von Wafern und Vorrichtung |

| DE102004004289A1 (de) * | 2004-01-28 | 2005-08-25 | Infineon Technologies Ag | Integrierte Schaltungsanordnung |

| US7066661B2 (en) * | 2004-03-30 | 2006-06-27 | Stefano Therisod | Small footprint optical fiber transceiver |

| TWI231535B (en) * | 2004-05-26 | 2005-04-21 | Advanced Semiconductor Eng | Photoelectric device grinding process and device grinding process |

| KR100652375B1 (ko) * | 2004-06-29 | 2006-12-01 | 삼성전자주식회사 | 와이어 본딩 패키지를 포함하는 이미지 센서 모듈 구조물및 그 제조방법 |

| DE102006016373A1 (de) * | 2006-04-05 | 2007-10-11 | Merck Patent Gmbh | Großflächige OLED's mit homogener Lichtemission |

| US20080070340A1 (en) * | 2006-09-14 | 2008-03-20 | Nicholas Francis Borrelli | Image sensor using thin-film SOI |

| US20080067652A1 (en) * | 2006-09-18 | 2008-03-20 | Simpler Networks Inc. | Integrated mems packaging |

| US8030754B2 (en) * | 2007-01-31 | 2011-10-04 | Hewlett-Packard Development Company, L.P. | Chip cooling channels formed in wafer bonding gap |

| DE102007027811A1 (de) * | 2007-06-13 | 2008-12-24 | Carl Zeiss Smt Ag | Anwendung des LTB-Verfahrens zur Herstellung optischer Elemente |

| DE102007035788A1 (de) * | 2007-07-31 | 2009-02-05 | Robert Bosch Gmbh | Waferfügeverfahren, Waferverbund sowie Chip |

| WO2009110339A1 (ja) * | 2008-03-03 | 2009-09-11 | 日本電気株式会社 | デバイスパッケージ、電子モジュール、及び電子機器 |

| JP5493290B2 (ja) * | 2008-05-07 | 2014-05-14 | パナソニック株式会社 | 電子部品パッケージ |

| DE102008025202B4 (de) * | 2008-05-27 | 2014-11-06 | Epcos Ag | Hermetisch geschlossenes Gehäuse für elektronische Bauelemente und Herstellungsverfahren |

| FR2935537B1 (fr) * | 2008-08-28 | 2010-10-22 | Soitec Silicon On Insulator | Procede d'initiation d'adhesion moleculaire |

| JP5176146B2 (ja) * | 2008-10-08 | 2013-04-03 | 富士通株式会社 | マイクロ可動素子および光スイッチング装置 |

| JP5239722B2 (ja) | 2008-10-10 | 2013-07-17 | 富士通株式会社 | マイクロ可動素子および光スイッチング装置 |

| US8125042B2 (en) * | 2008-11-13 | 2012-02-28 | Samsung Electronics Co., Ltd. | Semiconductor package and method of manufacturing the same |

| US7936033B2 (en) * | 2008-12-29 | 2011-05-03 | Texas Instruments Incorporated | Micro-optical device packaging system |

| FR2943177B1 (fr) | 2009-03-12 | 2011-05-06 | Soitec Silicon On Insulator | Procede de fabrication d'une structure multicouche avec report de couche circuit |

| FR2947380B1 (fr) | 2009-06-26 | 2012-12-14 | Soitec Silicon Insulator Technologies | Procede de collage par adhesion moleculaire. |

| DE102009034532A1 (de) | 2009-07-23 | 2011-02-03 | Msg Lithoglas Ag | Verfahren zum Herstellen einer strukturierten Beschichtung auf einem Substrat, beschichtetes Substrat sowie Halbzeug mit einem beschichteten Substrat |

| CN102782862B (zh) * | 2010-02-26 | 2015-08-26 | 精材科技股份有限公司 | 芯片封装体及其制造方法 |

| DE102011005612A1 (de) * | 2011-03-16 | 2012-09-20 | Osram Opto Semiconductors Gmbh | Organisches Optoelektronisches Bauelement und Verfahren zur Herstellung eines Optoelektronischen Bauelements |

| WO2013031509A1 (en) * | 2011-08-26 | 2013-03-07 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device, electronic device, lighting device, and method for manufacturing the light-emitting device |

| CN102769091B (zh) * | 2012-05-25 | 2015-11-25 | 瑞声声学科技(深圳)有限公司 | Led封装中的陶瓷挡墙制造方法 |

| US9991463B2 (en) * | 2012-06-14 | 2018-06-05 | Universal Display Corporation | Electronic devices with improved shelf lives |

| TW201417250A (zh) * | 2012-07-17 | 2014-05-01 | 海特根微光學公司 | 光學模組,特別是光電模組,及其製造方法 |

| US9434145B2 (en) | 2012-12-07 | 2016-09-06 | Semrock, Inc. | Dichroic filter conformed to optical surface |

| US9741918B2 (en) | 2013-10-07 | 2017-08-22 | Hypres, Inc. | Method for increasing the integration level of superconducting electronics circuits, and a resulting circuit |

| US9105800B2 (en) * | 2013-12-09 | 2015-08-11 | Raytheon Company | Method of forming deposited patterns on a surface |

| US9698376B2 (en) * | 2014-10-24 | 2017-07-04 | Shenzhen China Star Optoelectronics Technology Co., Ltd | Packaging method and packaging structure of substrate |

| CN104362243B (zh) * | 2014-10-24 | 2017-11-03 | 深圳市华星光电技术有限公司 | 基板的封装方法及封装结构 |

| US10234695B2 (en) * | 2015-02-16 | 2019-03-19 | Apple Inc. | Low-temperature hermetic sealing for diffractive optical element stacks |

| US9771258B2 (en) | 2015-06-24 | 2017-09-26 | Raytheon Company | Wafer level MEMS package including dual seal ring |

| US20170219793A1 (en) * | 2016-01-28 | 2017-08-03 | AAC Technologies Pte. Ltd. | Sealed module with glue guiding features and method for making same |

| CN116282904A (zh) | 2016-09-13 | 2023-06-23 | Agc株式会社 | 高频器件用玻璃基板和高频器件用电路基板 |

| CN109103165B (zh) * | 2018-07-03 | 2019-12-10 | 中国电子科技集团公司第二十九研究所 | Ltcc基板三维堆叠结构及其气密封装方法 |

| CN110155934A (zh) | 2019-04-22 | 2019-08-23 | 武汉衍熙微器件有限公司 | 一种mems器件及其制作方法 |

| DE102019120844A1 (de) * | 2019-08-01 | 2021-02-04 | Horst Siedle Gmbh & Co. Kg | Verfahren zur Herstellung von abgedichteten Funktionselementen |

| DE102019129036A1 (de) * | 2019-10-28 | 2021-04-29 | Schott Ag | Verfahren zur Herstellung von Glasscheiben und verfahrensgemäß hergestellte Glasscheibe sowie deren Verwendung |

| FI20205075A1 (en) * | 2020-01-24 | 2021-07-25 | Teknologian Tutkimuskeskus Vtt Oy | Disc level housing for the device |

| DE102020111728B4 (de) | 2020-04-29 | 2022-06-23 | Schott Ag | Elektro-optisches Wandlerbauteil mit einem Abstandhalter, sowie Abstandhalter-Wafer zur Herstellung eines elektro-optischen Wandlerbauteils |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58172679A (ja) * | 1982-04-01 | 1983-10-11 | Fuji Photo Film Co Ltd | ホログラム作成方法 |

| EP0280905A2 (en) * | 1987-03-06 | 1988-09-07 | Hitachi, Ltd. | A method for manufacturing semiconductor absolute pressure sensor units |

| US5895233A (en) * | 1993-12-13 | 1999-04-20 | Honeywell Inc. | Integrated silicon vacuum micropackage for infrared devices |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4192433A (en) * | 1979-01-19 | 1980-03-11 | Semi-Alloys, Inc. | Hermetic sealing cover for a container for semiconductor devices |

| US4232814A (en) * | 1979-06-14 | 1980-11-11 | Semi-Alloys, Inc. | Method and apparatus for fabricating a sealing cover unit for a container for a semiconductor device |

| US4426768A (en) * | 1981-12-28 | 1984-01-24 | United Technologies Corporation | Ultra-thin microelectronic pressure sensors |

| US5343064A (en) * | 1988-03-18 | 1994-08-30 | Spangler Leland J | Fully integrated single-crystal silicon-on-insulator process, sensors and circuits |

| US5448444A (en) * | 1994-01-28 | 1995-09-05 | United Technologies Corporation | Capacitive pressure sensor having a reduced area dielectric spacer |

| US6969667B2 (en) * | 2002-04-01 | 2005-11-29 | Hewlett-Packard Development Company, L.P. | Electrical device and method of making |

| DE10222958B4 (de) | 2002-04-15 | 2007-08-16 | Schott Ag | Verfahren zur Herstellung eines organischen elektro-optischen Elements und organisches elektro-optisches Element |

| DE10222609B4 (de) | 2002-04-15 | 2008-07-10 | Schott Ag | Verfahren zur Herstellung strukturierter Schichten auf Substraten und verfahrensgemäß beschichtetes Substrat |

| DE10222964B4 (de) | 2002-04-15 | 2004-07-08 | Schott Glas | Verfahren zur Gehäusebildung bei elektronischen Bauteilen sowie so hermetisch verkapselte elektronische Bauteile |

-

2003

- 2003-04-15 AU AU2003227626A patent/AU2003227626A1/en not_active Abandoned

- 2003-04-15 CA CA002485022A patent/CA2485022A1/en not_active Abandoned

- 2003-04-15 CN CNB03808564XA patent/CN100359653C/zh not_active Expired - Lifetime

- 2003-04-15 JP JP2003585174A patent/JP2005528782A/ja not_active Withdrawn

- 2003-04-15 WO PCT/EP2003/003907 patent/WO2003088347A2/de active Application Filing

- 2003-04-15 US US10/511,557 patent/US7396741B2/en not_active Expired - Lifetime

- 2003-04-15 EP EP03725032.1A patent/EP1495491B1/de not_active Expired - Lifetime

-

2004

- 2004-09-27 IL IL16430104A patent/IL164301A0/xx unknown

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58172679A (ja) * | 1982-04-01 | 1983-10-11 | Fuji Photo Film Co Ltd | ホログラム作成方法 |

| EP0280905A2 (en) * | 1987-03-06 | 1988-09-07 | Hitachi, Ltd. | A method for manufacturing semiconductor absolute pressure sensor units |

| US5895233A (en) * | 1993-12-13 | 1999-04-20 | Honeywell Inc. | Integrated silicon vacuum micropackage for infrared devices |

Non-Patent Citations (1)

| Title |

|---|

| .WOO-BEOM CHOI ET AL.VACUUM MICROELECTRONICS CONFERENCE,1996。,Vol.IVMC’96 9TH No.7-12. 1996 * |

Also Published As

| Publication number | Publication date |

|---|---|

| AU2003227626A8 (en) | 2003-10-27 |

| WO2003088347A2 (de) | 2003-10-23 |

| WO2003088347A3 (de) | 2003-12-31 |

| CA2485022A1 (en) | 2003-10-23 |

| EP1495491A2 (de) | 2005-01-12 |

| US7396741B2 (en) | 2008-07-08 |

| JP2005528782A (ja) | 2005-09-22 |

| EP1495491B1 (de) | 2020-12-16 |

| AU2003227626A1 (en) | 2003-10-27 |

| CN1647261A (zh) | 2005-07-27 |

| IL164301A0 (en) | 2005-12-18 |

| US20060030074A1 (en) | 2006-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100359653C (zh) | 用于连结基片的处理和复合元件 | |

| US8324024B2 (en) | Method for production of packaged electronic components, and a packaged electronic component | |

| KR100934291B1 (ko) | 웨이퍼 패키징 환경에서의 ai/ge 본딩 제조 방법 및생산 제품 | |

| US7303645B2 (en) | Method and system for hermetically sealing packages for optics | |

| US7485956B2 (en) | Microelectronic package optionally having differing cover and device thermal expansivities | |

| US7164199B2 (en) | Device packages with low stress assembly process | |

| US7825029B2 (en) | Method for the production of structured layers on substrates | |

| US6448109B1 (en) | Wafer level method of capping multiple MEMS elements | |

| US7285478B2 (en) | Method for micro-electromechanical system package | |

| US7288464B2 (en) | MEMS packaging structure and methods | |

| US6465281B1 (en) | Method of manufacturing a semiconductor wafer level package | |

| WO2001020671A1 (en) | Semiconductor wafer level package | |

| WO2009038686A2 (en) | Hermetic wafer level cavity package | |

| KR100636414B1 (ko) | 기판 결합 방법 및 복합 부품 | |

| JP2023548674A (ja) | 電気デバイスへのアライメントされた光アクセスを有する層状基板構造 | |

| KR20240141791A (ko) | 에지 방출 레이저 다이오드용 반도체 패키지 | |

| WO2007059193A2 (en) | Low profile image sensor package |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CX01 | Expiry of patent term |

Granted publication date: 20080102 |

|

| CX01 | Expiry of patent term |