WO2022106943A1 - 半導体装置、表示装置、表示モジュール、及び電子機器 - Google Patents

半導体装置、表示装置、表示モジュール、及び電子機器 Download PDFInfo

- Publication number

- WO2022106943A1 WO2022106943A1 PCT/IB2021/060110 IB2021060110W WO2022106943A1 WO 2022106943 A1 WO2022106943 A1 WO 2022106943A1 IB 2021060110 W IB2021060110 W IB 2021060110W WO 2022106943 A1 WO2022106943 A1 WO 2022106943A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- insulating layer

- transistor

- semiconductor

- resin layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

- H10K59/1315—Interconnections, e.g. wiring lines or terminals comprising structures specially adapted for lowering the resistance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6733—Multi-gate TFTs

- H10D30/6734—Multi-gate TFTs having gate electrodes arranged on both top and bottom sides of the channel, e.g. dual-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/124—Insulating layers formed between TFT elements and OLED elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/043—Compensation electrodes or other additional electrodes in matrix displays related to distortions or compensation signals, e.g. for modifying TFT threshold voltage in column driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/351—Thickness

Definitions

- One aspect of the present invention relates to a semiconductor device and a method for manufacturing the same.

- One aspect of the present invention relates to a display device.

- one aspect of the present invention is not limited to the above technical fields.

- the technical fields of one aspect of the present invention disclosed in the present specification and the like include semiconductor devices, display devices, light emitting devices, power storage devices, storage devices, electronic devices, lighting devices, input devices, input / output devices, and driving methods thereof. , Or their manufacturing methods, can be mentioned as an example.

- Semiconductor devices refer to all devices that can function by utilizing semiconductor characteristics.

- Oxide semiconductors using metal oxides are attracting attention as semiconductor materials applicable to transistors used in display devices.

- a plurality of oxide semiconductor layers are laminated, and among the plurality of oxide semiconductor layers, the oxide semiconductor layer serving as a channel contains indium and gallium, and the ratio of indium is the ratio of gallium.

- a semiconductor device having an increased electric field effect mobility by making it larger than the above is disclosed.

- One aspect of the present invention is to provide a display device in which the parasitic capacitance of wiring is reduced.

- One aspect of the present invention is to provide a display device having both high resolution and high frame frequency.

- One aspect of the present invention is to provide a high-definition display device.

- One aspect of the present invention is to provide a highly reliable display device or semiconductor device.

- One aspect of the present invention is to provide a semiconductor device, a display device, a display module, an electronic device, or the like having a novel configuration.

- One aspect of the present invention is to provide a method for manufacturing the above-mentioned display device or semiconductor device with high yield.

- One aspect of the present invention is to alleviate at least one of the problems of the prior art.

- One aspect of the present invention is a semiconductor device having a first wiring, a second wiring, and a transistor.

- the semiconductor device has a first resin layer between the first wiring and the transistor.

- the semiconductor device has a first insulating layer between the first resin layer and the transistor.

- the semiconductor device has a second resin layer between the transistor and the second wiring.

- the semiconductor device has a second insulating layer between the second resin layer and the transistor.

- the first insulating layer and the second insulating layer have an inorganic insulating film containing nitrogen.

- the first resin layer and the second resin layer have a lower dielectric constant than the first insulating layer and the second insulating layer, respectively. Further, the thickness of the first resin layer and the second resin layer is 5 times or more and 100 times or less as thick as those of the first insulating layer and the second insulating layer, respectively.

- the first resin layer and the second resin layer contain the same material and have the same thickness.

- the thickness of the second resin layer is preferably 80% or more and 120% or less of the thickness of the first resin layer.

- the first resin layer and the second resin layer are formed by the same film forming method using the same material.

- the first insulating layer and the second insulating layer contain the same material and have the same thickness.

- the thickness of the second insulating layer is preferably 80% or more and 120% or less of the thickness of the first insulating layer.

- the first insulating layer and the second insulating layer are formed by the same film forming method using the same material.

- the transistor has a first gate electrode, a second gate electrode, a first gate insulating layer, a second gate insulating layer, and a semiconductor layer.

- the first gate insulating layer is located between the semiconductor layer and the first gate electrode.

- the second gate insulating layer is located between the semiconductor layer and the second gate electrode.

- the first gate electrode and the second gate electrode have an overlapping region via the semiconductor layer.

- the first gate electrode is electrically connected to the first wiring at the openings provided in the first insulating layer and the first resin layer.

- the second wiring is electrically connected to the semiconductor layer at the openings provided in the second resin layer and the second insulating layer.

- the transistor has a first electrode between the second resin layer and the second insulating layer. Further, it is preferable that the first electrode is electrically connected to a part of the semiconductor layer at the opening provided in the second insulating layer. Further, it is preferable that the second wiring is electrically connected to the first electrode at the opening provided in the second resin layer.

- the second gate electrode is electrically connected to the first gate electrode at the openings provided in the first gate insulating layer and the second gate insulating layer. ..

- the semiconductor layer contains either or both of indium and zinc and oxygen.

- the semiconductor layer contains indium, gallium, and zinc, and the semiconductor layer has an atomic number ratio of indium more than twice that of gallium and a zinc atomic number ratio of more than twice that of gallium. It is more preferable to have.

- the first resin layer and the second resin layer each contain acrylic or polyimide.

- one aspect of the present invention is a display device having any of the above semiconductor devices, a pixel electrode, a source drive circuit, and a gate drive circuit. Further, it is preferable that the display device has a third resin layer between the pixel electrode and the transistor. Further, it is preferable that the first wiring is electrically connected to the source drive circuit and the second wiring is electrically connected to the gate drive circuit.

- the pixel electrode is preferably an electrode of an organic EL element.

- one aspect of the present invention is a display module having any of the above display devices and a connector or an integrated circuit.

- one aspect of the present invention is an electronic device having the above-mentioned display module and at least one of an antenna, a battery, a housing, a camera, a speaker, a microphone, a touch sensor, and an operation button.

- a display device in which the parasitic capacitance of wiring is reduced.

- a display device having both high resolution and high frame frequency Alternatively, a high-definition display device can be provided.

- a highly reliable display device or semiconductor device can be provided.

- a semiconductor device a display device, a display module, an electronic device, or the like having a novel configuration.

- at least one of the problems of the prior art can be alleviated.

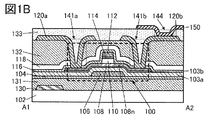

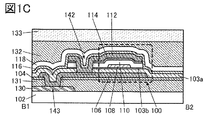

- 1A to 1C are diagrams showing a configuration example of a semiconductor device.

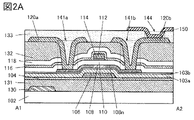

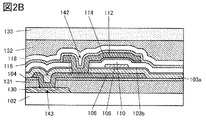

- 2A and 2B are diagrams showing a configuration example of a semiconductor device.

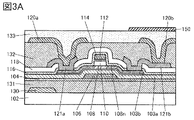

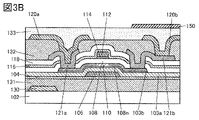

- 3A and 3B are diagrams showing a configuration example of a semiconductor device.

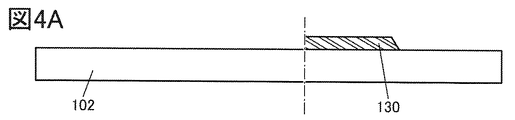

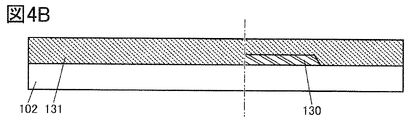

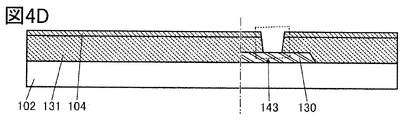

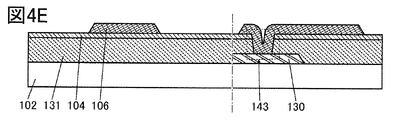

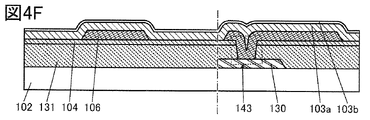

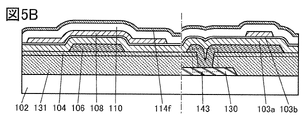

- 4A to 4F are diagrams illustrating an example of a method for manufacturing a semiconductor device.

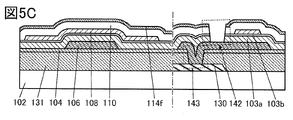

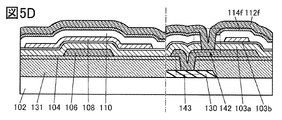

- 5A to 5D are diagrams illustrating an example of a method for manufacturing a semiconductor device.

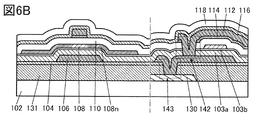

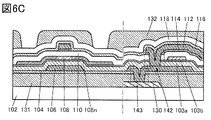

- 6A to 6C are diagrams illustrating an example of a method for manufacturing a semiconductor device.

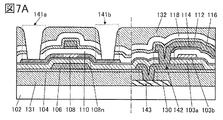

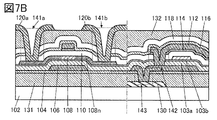

- 7A and 7B are diagrams illustrating an example of a method for manufacturing a semiconductor device.

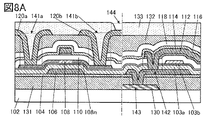

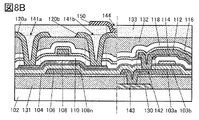

- 8A and 8B are diagrams illustrating an example of a method for manufacturing a semiconductor device.

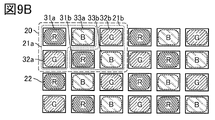

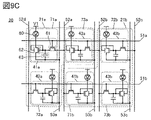

- 9A to 9C are diagrams showing a configuration example of the display device.

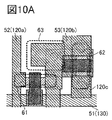

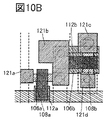

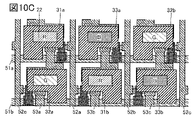

- FIGS. 10A to 10C are diagrams showing a configuration example of pixels.

- FIG. 11 is a diagram showing a configuration example of the display device.

- FIG. 12 is a diagram showing a configuration example of the display device.

- 13A to 13F are views showing a configuration example of an electronic device.

- 14A and 14B are diagrams showing a configuration example of a display module.

- 15A and 15B are diagrams showing a configuration example of an electronic device.

- 16A to 16E are diagrams showing a configuration example of an electronic device.

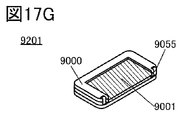

- 17A to 17G are diagrams showing a configuration example of an electronic device.

- 18A to 18D are diagrams showing a configuration example of an electronic device.

- a transistor is a kind of semiconductor element, and can realize a function of amplifying a current or a voltage and a switching operation for controlling conduction or non-conduction.

- the transistor in the present specification includes an IGFET (Insulated Gate Field Transistor) and a thin film transistor (TFT: Thin Film Transistor).

- source and drain functions may be interchanged when transistors with different polarities are used, or when the direction of current changes during circuit operation. Therefore, in the present specification, the terms “source” and “drain” may be used interchangeably.

- membrane and the term “layer” can be interchanged with each other.

- conductive layer or “insulating layer” may be interchangeable with the terms “conductive film” or “insulating film”.

- the display panel which is one aspect of the display device, has a function of displaying (outputting) an image or the like on the display surface. Therefore, the display panel is an aspect of the output device.

- a connector such as FPC (Flexible Printed Circuit) or TCP (Tape Carrier Package) is attached to the board of the display panel, or an IC is used on the board by a COG (Chip On Glass) method or the like.

- FPC Flexible Printed Circuit

- TCP Transmission Carrier Package

- COG Chip On Glass

- Embodiment 1 a semiconductor device according to one aspect of the present invention, a method for manufacturing the semiconductor device, a display device, and the like will be described.

- a transistor using an oxide semiconductor in the semiconductor layer on which the channel is formed will be described.

- FIG. 1A shows a schematic top view of a semiconductor device including the transistor 100. Further, FIG. 1B corresponds to a cross-sectional view of the alternate long and short dash line A1-A2 shown in FIG. 1A, and FIG. 1C corresponds to a cross-sectional view of the alternate long and short dash line B1-B2 shown in FIG. 1A. In FIG. 1A, a part of the components (gate insulating layer, etc.) is omitted. 1B is a cross-sectional view of the transistor 100 in the channel length direction, and FIG. 1C is a cross-sectional view including a cross section in the channel width direction.

- the transistor 100 is provided on the substrate 102 and has a conductive layer 106, an insulating layer 103a, an insulating layer 103b, a semiconductor layer 108, an insulating layer 110, a metal oxide layer 114, a conductive layer 112, and the like. Further, a resin layer 131 is provided between the transistor 100 and the substrate 102. A resin layer 132 is provided on the transistor 100. An insulating layer 104 is provided between the resin layer 131 and the transistor 100. An insulating layer 116 and an insulating layer 118 are laminated and provided between the transistor 100 and the resin layer 132.

- a part of the conductive layer 106 and a part of the conductive layer 112 each function as a gate electrode. Further, a part of the insulating layer 103a, a part of the insulating layer 103b, and a part of the insulating layer 110 each function as a gate insulating layer.

- a conductive layer 130 that functions as wiring is provided between the substrate 102 and the resin layer 131. Further, a conductive layer 120a and a conductive layer 120b are provided on the resin layer 132. At least one of the conductive layer 120a and the conductive layer 120b functions as wiring.

- the resin layer 133 is provided so as to cover the resin layer 132, the conductive layer 120a, and the conductive layer 120b. Further, a conductive layer 150 is provided on the resin layer 133.

- the conductive layer 150 can be used, for example, as a pixel electrode of a display element. Alternatively, the conductive layer 150 may be used as wiring.

- the conductive layer 150 is electrically connected to the conductive layer 120b at the opening 144 provided in the resin layer 133.

- the insulating layer 104 functions as a barrier membrane that prevents impurities such as water and hydrogen in the resin layer 131 from diffusing into the transistor 100.

- the insulating layer 116 also functions as a barrier membrane that prevents impurities such as water and hydrogen contained in the resin layer 132 from diffusing into the transistor 100.

- an inorganic insulating film in which water or hydrogen does not easily diffuse can be used.

- an insulating film containing a nitride such as silicon nitride, silicon nitride oxide, silicon nitride nitride, aluminum nitride, and aluminum nitride can be preferably used.

- silicon nitride since silicon nitride has a blocking property against either one or both of hydrogen and oxygen, it can prevent both the diffusion of hydrogen from the outside to the semiconductor layer 108 and the desorption of oxygen from the semiconductor layer 108 to the outside. It is possible to realize a highly reliable transistor.

- Organic resin can be used for the resin layer 131 and the resin layer 132.

- acrylic or polyimide it is preferable to use acrylic or polyimide.

- the material that can be used for the resin layer 131 is not limited to this, and a chemically or thermally stable material can be used.

- the resin layer 131 and the resin layer 132 preferably function as a flattening film.

- a film formed by a coating method such as a spin coating method or a slit coating method is preferable. Since the resin layer 131 functions as a flattening film, the influence of the step due to the conductive layer 130 located closer to the substrate 102 than the transistor 100 can be suppressed, the formed surface of the transistor 100 can be flattened, and the electrical characteristics of the transistor 100 can be improved. Variation can be reduced. Further, since the resin layer 132 functions as a flattening film, the influence of the step due to the transistor 100 can be suppressed, the formed surfaces of the conductive layer 120a and the conductive layer 120b can be flattened, and processing defects thereof can be reduced. Further, since the formed surface of the conductive layer 150 that can be used as a pixel electrode or the like can be flattened, it is possible to reduce variations in the electrical characteristics and optical characteristics of the display element that uses the conductive layer 150 as the pixel electrode.

- the resin layer 131 and the resin layer 132 each have a low dielectric constant. Specifically, it is preferable to use an organic insulating material having a lower dielectric constant than either or both of the insulating layer 104 and the insulating layer 116. In particular, it is preferable that the resin layer 131 and the resin layer 132 have a lower dielectric constant than both the insulating layer 104 and the insulating layer 116.

- the resin layer 131 and the resin layer 132 are each thickly formed.

- the resin layer 131 and the resin layer 132 are thicker than either or both of the insulating layer 104 and the insulating layer 116, respectively.

- the resin layer 131 and the resin layer 132 are thicker than both the insulating layer 104 and the insulating layer 116.

- the thickness of the resin layer 131 and the resin layer 132 is 5 times or more and 100 times or less, or 5 times or more and 50 times or less, or 5 times or more and 30 times or less, respectively, as thick as the insulating layer 104 or the insulating layer 116. Can be.

- the insulating layer 104 and the insulating layer 116 may have a thickness of 50 nm or more and 300 nm or less, and the resin layer 131 and the resin layer 132 may have a thickness of 500 nm or more and 20 ⁇ m or less, preferably 1 ⁇ m or more and 10 ⁇ m or less. can.

- FIG. 1B shows a cross section at the intersection of the conductive layer 130 and the conductive layer 120a shown in FIG. 1A.

- At least a resin layer 131 and a resin layer 132 are provided between the conductive layer 130 and the conductive layer 120a. Since the resin layer 131 and the resin layer 132 are layers having a low dielectric constant and formed thickly, the capacitance generated between them at the intersection of the conductive layer 130 and the conductive layer 120a should be extremely small. Can be done. This makes it possible to realize a display device that can be driven at a high resolution, a high definition, and a high frame rate.

- the resolution is full high definition (also called “2K resolution”, “2K1K”, or “2K”), ultra high definition (also called “4K resolution”, “4K2K”, or “4K”) or super high definition ("8K resolution”). , “8K4K”, or “8K”).

- the fineness is, for example, 400 ppi or more, or 500 ppi or more, preferably 1000 ppi or more, more preferably 2000 ppi or more, further 3000 ppi or more, and a high-definition display having a fineness of 10,000 ppi or less, 7500 ppi or less, or 6000 ppi or less.

- the device can be realized. It should be noted that even for a display device having a definition of less than 400 ppi, it is preferable because the parasitic capacitance can be reduced by applying the above configuration. For example, the above configuration can be suitably used for a large display device having a screen diagonal size of 50 inches or more, 60 inches or more, or 70 inches or more.

- the time constant of the wiring can be reduced, the time required for charging and discharging the wiring (for example, the writing time of the pixel) can be shortened, so that it is possible to drive at a high frame rate. For example, 60Hz drive, 120Hz drive, 180Hz drive, and even 240Hz drive can be expected.

- the resin layer 131 and the resin layer 132 contain the same material and have the same thickness.

- the thickness of the resin layer 132 is preferably 80% or more and 120% or less of the thickness of the resin layer 131.

- the resin layer 131 and the resin layer 132 are formed by the same film forming method using the same material.

- the stress can be made the same.

- the stress can be made similar between the upper and lower parts of the transistor 100, so that an extreme stress difference does not occur, and as a result, film peeling during the process can be suppressed.

- the stress applied to the transistor 100 from above and below can be made uniform, variations in the electrical characteristics of the transistor 100 can be reduced.

- the insulating layer 104 and the insulating layer 116 also contain the same material and have the same thickness.

- the thickness of the insulating layer 116 is preferably 80% or more and 120% or less of the thickness of the insulating layer 104.

- the insulating layer 104 and the insulating layer 116 are formed by the same film forming method using the same material. As a result, not only the film peeling during the process can be suppressed more effectively, but also the variation in the electrical characteristics of the transistor 100 can be reduced.

- the conductive layer 106 is provided on the insulating layer 104.

- the insulating layer 103a is provided so as to cover the conductive layer 106.

- the insulating layer 103b is provided on the insulating layer 103a.

- the island-shaped semiconductor layer 108 is provided on the insulating layer 103b and overlaps with a part of the conductive layer 106.

- the insulating layer 110, the metal oxide layer 114, and the conductive layer 112 are provided on the semiconductor layer 108 and the insulating layer 103b in this order, and have a portion that overlaps with the semiconductor layer 108 and the conductive layer 106.

- the insulating layer 116 is provided so as to cover the insulating layer 103a, the semiconductor layer 108, the insulating layer 110, the metal oxide layer 114, and the conductive layer 112.

- the insulating layer 118 is provided on the insulating layer 116.

- the semiconductor layer 108 has a region that overlaps with the conductive layer 112 and a pair of low resistance regions 108n that sandwich the region.

- the region of the semiconductor layer 108 that overlaps with the conductive layer 112 functions as a channel forming region of the transistor 100.

- the pair of low resistance regions 108n function as a source region and a drain region of the transistor 100.

- the insulating layer 103a and the insulating layer 103b are continuously formed by using a plasma CVD apparatus without being exposed to the atmosphere.

- an insulating film containing nitrogen such as a silicon nitride film, a silicon nitride film, an aluminum nitride film, and a hafnium nitride film can be used.

- the insulating layer 103b in contact with the semiconductor layer 108 is preferably a dense insulating film in which impurities such as water are not easily adsorbed on the surface thereof. Further, it is preferable to use an insulating film having as few defects as possible and reduced impurities such as water or hydrogen.

- Examples of the insulating layer 103b include a silicon oxide film, a silicon nitride film, a silicon nitride film, an aluminum oxide film, a hafnium oxide film, an yttrium oxide film, a zirconium oxide film, a gallium oxide film, a tantalum oxide film, and a magnesium oxide film.

- An insulating layer containing one or more of a lanthanum oxide film, a cerium oxide film, and a neodymium oxide film can be used. In particular, it is preferable to use a silicon oxide film or a silicon nitride film.

- the insulating layer 103b in contact with the semiconductor layer 108 preferably has an oxide insulating film. Further, it is more preferable that the insulating layer 103b has a region containing oxygen in excess of the stoichiometric composition. In other words, the insulating layer 103b has an insulating film capable of releasing oxygen. For example, forming the insulating layer 103b in an oxygen atmosphere, heat-treating the insulating layer 103b after film formation in an oxygen atmosphere, plasma treatment in an oxygen atmosphere after forming the insulating layer 110, etc.

- an oxide film for example, a metal oxide film to be the semiconductor layer 108

- oxygen can be supplied to the insulating layer 103b. ..

- an oxidizing gas for example, nitrous oxide, ozone, etc. may be used instead of or in addition to oxygen.

- the semiconductor layer 108 contains a metal oxide exhibiting semiconductor characteristics (hereinafter, also referred to as an oxide semiconductor).

- the semiconductor layer 108 preferably contains at least indium and oxygen. Since the semiconductor layer 108 contains an oxide of indium, the carrier mobility can be enhanced. For example, it is possible to realize a transistor capable of passing a larger current than when amorphous silicon is used.

- the region of the semiconductor layer 108 that overlaps the conductive layer 112 functions as a channel forming region. Further, the semiconductor layer 108 preferably has a pair of low resistance regions 108n with the channel forming region interposed therebetween.

- the low resistance region 108n is a region having a higher carrier concentration than the channel formation region, and functions as a source region and a drain region.

- the low resistance region 108n can also be said to be a region having a lower resistance, a region having a high carrier concentration, a region having a large amount of oxygen deficiency, a region having a high hydrogen concentration, or a region having a high impurity concentration than the channel forming region.

- the semiconductor layer 108 preferably contains at least a metal oxide containing indium and oxygen. Further, the semiconductor layer 108 may contain zinc in addition to these. Further, the semiconductor layer 108 may contain gallium.

- indium oxide indium zinc oxide (In-Zn oxide), indium gallium zinc oxide (also referred to as In-Ga-Zn oxide, IGZO) and the like can be typically used.

- indium tin oxide In—Sn oxide

- indium tin oxide containing silicon or the like can also be used.

- the composition of the semiconductor layer 108 greatly affects the electrical characteristics, reliability, and the like of the transistor 100. For example, by increasing the content of indium in the semiconductor layer 108, carrier mobility is improved, and a transistor having high field effect mobility can be realized.

- GBT Gate Bias Stress Test

- PBTS Positive Bias Temperature Stress

- the PBTS test and the NBTS test conducted in a state of being irradiated with light such as white LED light are called PBTIS (Positive Bias Temperature Illumination Stress) test and NBTIS (Negative Bias Temperature Test) Test, respectively.

- the composition of the semiconductor layer 108 preferably has a smaller gallium content than the indium content. This makes it possible to realize a highly reliable transistor.

- a metal oxide film in which the atomic number ratio of In is higher than the atomic number ratio of Ga is applied to the semiconductor layer 108.

- the semiconductor layer 108 is preferably a film formed by a sputtering method using a metal oxide target in which the atomic number ratio of the metal element is in the above range. At this time, the composition of the semiconductor layer 108 after the film formation may deviate from the composition of the metal oxide target.

- a metal oxide film containing no gallium may be applied to the semiconductor layer 108.

- the In—Zn oxide can be applied to the semiconductor layer 108.

- the electric field effect mobility of the transistor can be increased by increasing the atomic number ratio of In to the atomic number of the metal element contained in the metal oxide film.

- a highly crystalline metal oxide film is obtained, so that fluctuations in the electrical characteristics of the transistor are suppressed and reliability is improved.

- a metal oxide film containing no gallium and zinc such as indium oxide may be applied to the semiconductor layer 108.

- an oxide film such as indium oxide, indium zinc oxide, or indium tin oxide can be used for the semiconductor layer 108.

- M is aluminum, silicon, boron, yttrium, tin, copper, vanadium, beryllium, titanium, iron, nickel, germanium, zirconium, molybdenum

- M is preferably one or more selected from gallium, aluminum, yttrium, or tin.

- a crystalline metal oxide film for the semiconductor layer 108 It is preferable to use a crystalline metal oxide film for the semiconductor layer 108.

- a metal oxide film having a CAAC (c-axis aligned crystal) structure, a polycrystalline structure, a microcrystal structure, etc., which will be described later, can be used.

- CAAC c-axis aligned crystal

- the defect level density in the semiconductor layer 108 can be reduced, and a highly reliable semiconductor device can be realized.

- the low resistance region 108n of the semiconductor layer 108 is a region containing an impurity element.

- the impurity element include hydrogen, boron, carbon, nitrogen, fluorine, phosphorus, sulfur, arsenic, aluminum, and rare gas.

- the noble gas include helium, neon, argon, krypton, xenon and the like. In particular, it preferably contains boron or phosphorus. Further, it may contain two or more of these elements.

- the impurity concentration is 1 ⁇ 10 19 atoms / cm 3 or more, 1 ⁇ 10 23 atoms / cm 3 or less, preferably 5 ⁇ 10 19 atoms / cm 3 or more, and 5 ⁇ 10 22 atoms / cm 3

- the concentration of impurities contained in the low resistance region 108n is analyzed by, for example, an analysis method such as secondary ion mass spectrometry (SIMS: Secondary Ion Mass Spectrometry) or X-ray photoelectron spectroscopy (XPS: X-ray Photoelectron Spectroscopy).

- an analysis method such as secondary ion mass spectrometry (SIMS: Secondary Ion Mass Spectrometry) or X-ray photoelectron spectroscopy (XPS: X-ray Photoelectron Spectroscopy).

- SIMS Secondary Ion Mass Spectrometry

- XPS X-ray Photoelectron Spectroscopy

- the conductive layer 112, the metal oxide layer 114, and the insulating layer 110 are processed so that their upper surface shapes substantially match each other.

- the top surface shapes are substantially the same.

- the contours do not overlap, and the upper layer may be located inside the lower layer, or the upper layer may be located outside the lower layer. In this case as well, it is said that the top surface shapes are roughly the same.

- the description of the insulating layer 103b can be incorporated.

- the metal oxide layer 114 located between the insulating layer 110 and the conductive layer 112 functions as a barrier membrane for preventing oxygen contained in the insulating layer 110 from diffusing toward the conductive layer 112. Further, the metal oxide layer 114 also functions as a barrier membrane for preventing hydrogen or water contained in the conductive layer 112 from diffusing toward the insulating layer 110.

- the metal oxide layer 114 for example, it is preferable to use a material that is less permeable to oxygen and hydrogen than the insulating layer 110.

- the metal oxide layer 114 can prevent oxygen from diffusing from the insulating layer 110 to the conductive layer 112 even when a metal material such as aluminum or copper that easily absorbs oxygen is used for the conductive layer 112. .. Further, even when the conductive layer 112 contains hydrogen, it is possible to prevent hydrogen from diffusing from the conductive layer 112 to the semiconductor layer 108 via the insulating layer 110. As a result, the carrier density in the channel formation region of the semiconductor layer 108 can be made extremely low.

- the metal oxide layer 114 an insulating material or a conductive material can be used.

- the metal oxide layer 114 functions as a part of the gate insulating layer.

- the metal oxide layer 114 has conductivity, the metal oxide layer 114 functions as a part of the gate electrode.

- the metal oxide layer 114 it is preferable to use an insulating material having a higher dielectric constant than silicon oxide.

- an aluminum oxide film, a hafnium oxide film, a hafnium aluminate film, or the like because the driving voltage can be reduced.

- a conductive oxide such as indium oxide, indium tin oxide (ITO), or silicon-containing indium tin oxide (ITSO) can also be used.

- ITO indium tin oxide

- ITSO silicon-containing indium tin oxide

- conductive oxides containing indium are preferable because they have high conductivity.

- the metal oxide layer 114 it is preferable to use an oxide material containing one or more of the same elements as the semiconductor layer 108. In particular, it is preferable to use an oxide semiconductor material applicable to the semiconductor layer 108. At this time, it is preferable to apply the metal oxide film formed by using the same sputtering target as the semiconductor layer 108 as the metal oxide layer 114 because the apparatus can be shared.

- the metal oxide layer 114 is formed by using a sputtering device.

- oxygen can be suitably added to the insulating layer 110 or the semiconductor layer 108 by forming the oxide film in an atmosphere containing oxygen gas.

- the insulating layer 116 is provided in contact with the upper surface of the low resistance region 108n.

- the insulating layer 116 preferably has a function of lowering the resistance of the low resistance region 108n.

- an insulating film capable of supplying impurities into the low resistance region 108n by heating during or after the film formation of the insulating layer 116 can be used.

- an insulating film capable of causing oxygen deficiency in the low resistance region 108n can be used by heating the insulating layer 116 during or after the film formation.

- an insulating film capable of giving distortion to the low resistance region 108n can be used by heating the insulating layer 116 during or after the film formation.

- the insulating layer 116 an insulating film that functions as a supply source for supplying impurities to the low resistance region 108n can be used.

- the insulating layer 116 is preferably a film that releases hydrogen by heating.

- the insulating layer 116 is preferably a film formed by using a gas containing an impurity element such as a hydrogen element as the film forming gas used for film formation. Further, the lower the film formation temperature of the insulating layer 116, the more impurity elements can be effectively supplied to the semiconductor layer 108.

- the film formation temperature of the insulating layer 116 can be, for example, 200 ° C. or higher and 500 ° C. or lower, preferably 220 ° C. or higher and 450 ° C. or lower, and more preferably 230 ° C. or higher and 400 ° C. or lower.

- the insulating layer 116 under reduced pressure and heating it, it is possible to promote the desorption of oxygen from the region of the semiconductor layer 108 that becomes the low resistance region 108n.

- impurities such as hydrogen

- the carrier density in the low resistance region 108n is increased, and the resistance of the low resistance region 108n can be reduced more effectively.

- an insulating film containing a nitride such as silicon nitride, silicon nitride, silicon oxide, aluminum nitride, and aluminum nitride can be preferably used.

- silicon nitride has a blocking property against hydrogen or oxygen, it can prevent both the diffusion of hydrogen from the outside to the semiconductor layer and the desorption of oxygen from the semiconductor layer to the outside, and is a highly reliable transistor. Can be realized.

- an insulating film containing an oxide such as silicon oxide, aluminum oxide, or hafnium oxide can be used.

- the insulating layer 118 functions as a protective layer that protects the transistor 100.

- an inorganic insulating material such as an oxide or a nitride can be used.

- an inorganic insulating material such as silicon oxide, silicon nitride nitride, silicon nitride, silicon nitride oxide, aluminum oxide, aluminum nitride, aluminum nitride, hafnium oxide, and hafnium aluminate can be used.

- the stacking order of the insulating layer 116 and the insulating layer 118 may be changed.

- a part of the conductive layer 120a and the conductive layer 120b provided on the resin layer 132 is electrically connected to the low resistance region 108n of the transistor 100 and functions as a source electrode or a drain electrode.

- the conductive layer 120a and the conductive layer 120b are electrically connected to the low resistance region 108n via the openings 141a or 141b provided in the resin layer 132, the insulating layer 118, and the insulating layer 116, respectively.

- the conductive layer 112 is electrically connected to the conductive layer 106 at the openings 142 provided in the metal oxide layer 114, the insulating layer 110, the insulating layer 103b, and the insulating layer 103a. Further, the conductive layer 106 is electrically connected to the conductive layer 130 at the openings 143 provided in the insulating layer 104 and the resin layer 131.

- both of the pair of gate electrodes are electrically connected to the conductive layer 130 here, one of them may be electrically connected to the conductive layer 130.

- the conductive layer 130 and the conductive layer 112 are electrically connected without passing through the conductive layer 106, the conductive layer 130 and the conductive layer are connected via a relay electrode formed by processing the same conductive film as the conductive layer 106. It suffices to connect with 106 electrically.

- an opening may be formed from the metal oxide layer 114 to reach the upper surface of the conductive layer 130, and the conductive layer 112 and the conductive layer 130 may be directly connected to each other.

- a transistor having only one gate also referred to as a single gate transistor

- the transistor can be a so-called top gate type transistor having a gate above the semiconductor layer 108 on which the channel is formed.

- a single-gate transistor can be realized by forming the right end of the conductive layer 106 so as to be located between the opening 142 and the semiconductor layer 108.

- FIGS. 2A and 2B show an example in which a part of the configuration is different from that of the above configuration example 1.

- the configurations shown in FIGS. 2A and 2B are mainly different in that the shape of the insulating layer 110 is different.

- the insulating layer 110 is provided so as to cover the upper surface of the insulating layer 103b, the upper surface and the side surface of the semiconductor layer 108.

- the insulating layer 110 is provided in contact with the upper surface of the low resistance region 108n as well as the channel forming region of the semiconductor layer 108.

- the low resistance region 108n can be formed by forming the insulating layer 110, the metal oxide layer 114, and the conductive layer 112, and then supplying impurities or the like through the insulating layer 110 with the conductive layer 112 as a mask. ..

- the above-mentioned impurity element can be supplied to the semiconductor layer 108 via the insulating layer 110 by plasma treatment, plasma ion doping method, ion implantation method, or the like.

- the covering property of the insulating layer 116 in the vicinity of the end portion of the conductive layer 112 can be improved, so that the reliability and the manufacturing yield can be improved.

- FIG. 3A The configuration shown in FIG. 3A is mainly different from the above configuration example 1 in that it has a conductive layer 121a and a conductive layer 121b.

- the conductive layer 120a is electrically connected to the low resistance region 108n via the conductive layer 121a. Further, the conductive layer 120b is electrically connected to the low resistance region 108n via the conductive layer 121b. Therefore, the conductive layer 121a and the conductive layer 121b can also be referred to as relay wiring, respectively.

- the conductive layer 121a and the conductive layer 121b are provided between the insulating layer 118 and the resin layer 132.

- the conductive layer 121a and the conductive layer 121b are electrically connected to the low resistance region 108n at the openings provided in the insulating layer 118 and the insulating layer 116, respectively.

- the conductive layer 120a and the conductive layer 120b are electrically connected to the conductive layer 121a and the conductive layer 121b, respectively, at the openings provided in the resin layer 132.

- the conductive layer 121a and the conductive layer 121b that function as relay wiring between the insulating layer 118 and the resin layer 132 in this way, it is not necessary to form a deep contact hole, so that the production yield can be increased. Can be done.

- the resin layer 132 containing a resin and the insulating layer 118 and the insulating layer 116 containing an inorganic insulating film are opened in a series of steps, not only the restrictions on the processing conditions become stricter but also the bottom of the opening is opened. Problems such as the disappearance of the positioned semiconductor layer 108 or the increase in the opening diameter may occur.

- FIG. 3A shows an example in which the opening provided in the resin layer 132 and the opening provided in the insulating layer 118 and the insulating layer 116 overlap each other at the connection portion between the conductive layer 120a and the conductive layer 121a. ing. Further, like the connection portion between the conductive layer 120b and the conductive layer 121b, the above two openings may be staggered so as not to be overlapped with each other.

- FIG. 3B is an example in which the conductive layer 121a and the conductive layer 121b are applied to the configuration exemplified in the above configuration example 2.

- the conductive layer 121a and the conductive layer 121b are electrically connected to the low resistance region 108n at the openings provided in the insulating layer 118, the insulating layer 116, and the insulating layer 110, respectively.

- the thin films (insulating film, semiconductor film, conductive film, etc.) constituting the semiconductor device include a sputtering method, a chemical vapor deposition (CVD) method, a vacuum vapor deposition method, and a pulsed laser deposition (PLD: Pulsed Laser Deposition).

- CVD chemical vapor deposition

- ALD Atomic Layer Deposition

- CVD method examples include a plasma chemical vapor deposition (PECVD: Plasma Enhanced CVD) method and a thermal CVD method.

- PECVD plasma chemical vapor deposition

- thermal CVD there is an organometallic chemical vapor deposition (MOCVD: Metalorganic CVD) method.

- the thin films (insulating film, semiconductor film, conductive film, etc.) that make up the semiconductor device are spin coated, dip, spray coated, inkjet, dispense, screen printing, offset printing, doctor knife, slit coat, roll coat, curtain coat. , Can be formed by a method such as knife coating.

- a thin film constituting a semiconductor device when processing a thin film constituting a semiconductor device, it can be processed by using a photolithography method or the like.

- the thin film may be processed by a nanoimprint method, a sandblast method, a lift-off method, or the like.

- an island-shaped thin film may be directly formed by a film forming method using a shielding mask such as a metal mask.

- photolithography methods There are typically the following two methods as photolithography methods.

- One is a method of forming a resist mask on a thin film to be processed, processing the thin film by etching or the like, and removing the resist mask.

- the other is a method in which a photosensitive thin film is formed, and then exposed and developed to process the thin film into a desired shape.

- the light used for exposure for example, i-line (wavelength 365 nm), g-line (wavelength 436 nm), h-line (wavelength 405 nm), or a mixture of these can be used.

- ultraviolet rays, KrF laser light, ArF laser light, or the like can also be used.

- the exposure may be performed by the immersion exposure technique.

- extreme ultraviolet (EUV: Extreme Ultra-violet) light or X-rays may be used as the light used for exposure.

- an electron beam can be used instead of the light used for exposure. It is preferable to use extreme ultraviolet light, X-rays or an electron beam because extremely fine processing is possible.

- extreme ultraviolet light, X-rays or an electron beam because extremely fine processing is possible.

- a dry etching method, a wet etching method, a sandblasting method, etc. can be used for etching the thin film.

- 4A to 8B show side-by-side cross sections in the channel length direction and the channel width direction at each stage of the manufacturing process of the semiconductor device exemplified in the configuration example 2.

- a conductive film is formed on the substrate 102 and processed by etching to form a conductive layer 130 that functions as wiring (FIG. 4A).

- the resin layer 131 to be formed later functions as a flattening film and has extremely high coverage, the conductive layer 130 does not have to be tapered. Further, since the conductive layer 130 can be made thicker, it is possible to reduce the wiring resistance of the wiring to which the conductive layer 130 is applied.

- the wiring resistance can be reduced.

- a conductive film containing copper As the conductive film to be the conductive layer 106, the wiring resistance can be reduced.

- the insulating layer 103a suppresses the diffusion of copper toward the semiconductor layer 108, so that a highly reliable transistor can be realized.

- the resin layer 131 is a mixture of the resin precursor and the solvent by, for example, spin coating, dipping, spray coating, inkjet, dispensing, screen printing, offset printing, doctor knife, slit coating, roll coating, curtain coating, knife coating and the like.

- the material is formed on the support substrate. After that, by performing a heat treatment, the material can be cured while removing the solvent and the like to form the resin layer 131 containing the organic resin.

- polyimide As the organic resin that can be used for the resin layer 131, polyimide can be typically used. Polyimide is preferable because it has excellent heat resistance. In addition, acrylic, epoxy, polyamide, polyimideamide, siloxane, benzocyclobutene resin, phenol resin and the like can be used.

- polyimide when polyimide is used, a resin precursor that forms an imide bond by dehydration can be used. Alternatively, a material containing soluble polyimide may be used.

- the organic resin used for the resin layer 131 either photosensitive or non-photosensitive resin may be used.

- the photosensitive polyimide is a material preferably used for a flattening film or the like of a display panel, a forming device and a material can be shared. Therefore, no new device, material, or the like is required to realize the configuration of one aspect of the present invention.

- a photosensitive resin material and subjecting it to exposure and development treatment for example, an opening can be formed or an unnecessary portion can be removed.

- optimizing the exposure method and the exposure conditions it is possible to form an uneven shape on the surface. For example, a multiple exposure technique, an exposure technique using a halftone mask or a gray tone mask, or the like may be used.

- the insulating layer 104 is formed on the resin layer 131 (FIG. 4C).

- the insulating layer 104 can be formed by using a PECVD method, an ALD method, a sputtering method, or the like.

- opening 143 a resist mask is formed on the insulating layer 104, and a part of the insulating layer 104 is removed by etching to form an opening in the insulating layer 104. Subsequently, using the insulating layer 104 as a hard mask, an opening reaching the conductive layer 130 is formed in a part of the resin layer 131 to form an opening 143 (FIG. 4D).

- the diameter of the opening 143 can be reduced.

- the resin layer 131 is preferably etched by dry etching. For example, it can be etched by an ashing process using plasma.

- the opening 143 may be formed by using the following method. First, a photosensitive material is used for the resin layer 131, and exposure and development are performed to form the resin layer 131 having an opening overlapping with the conductive layer 130. Subsequently, after the insulating layer 104 is formed into a film, the opening portion 143 can be formed by removing the portion overlapping the opening of the resin layer 131 by etching. In this method, the step of etching the thick resin layer 131 can be omitted.

- conductive layer 106 is formed by covering the insulating layer 104 and the opening 143, and this is processed by etching to form a conductive layer 106 that functions as a gate electrode (FIG. 4E).

- the wiring resistance can be reduced.

- the insulating layer 103a and the insulating layer 103b can be formed by using a PECVD method, an ALD method, a sputtering method, or the like.

- the insulating layer 103a and the insulating layer 103b are laminated and formed.

- the insulating layer 103a and the insulating layer 103b are preferably formed by the PECVD method.

- a process of supplying oxygen to the insulating layer 103b may be performed.

- plasma treatment or heat treatment in an oxygen atmosphere can be performed.

- oxygen may be supplied to the insulating layer 103b by a plasma ion doping method, an ion implantation method, or the like.

- the metal oxide film is preferably formed by a sputtering method using a metal oxide target.

- the metal oxide film is preferably a dense film with as few defects as possible. Further, the metal oxide film is preferably a high-purity film in which impurities such as hydrogen and water are reduced as much as possible. In particular, it is preferable to use a metal oxide film having crystallinity.

- oxygen gas and an inert gas for example, helium gas, argon gas, xenon gas, etc.

- oxygen flow rate ratio the ratio of oxygen gas to the entire film formation gas

- a high-quality transistor can be realized.

- the lower the oxygen flow rate ratio the lower the crystallinity of the metal oxide film, and the transistor can be made with an increased on-current.

- the substrate temperature may be room temperature or higher and 250 ° C. or lower, preferably room temperature or higher and 200 ° C. or lower, and more preferably the substrate temperature is room temperature or higher and 140 ° C. or lower.

- productivity is high and it is preferable.

- the crystallinity can be lowered by forming a metal oxide film at a substrate temperature of room temperature or in a state where the substrate is not intentionally heated.

- At least one of the treatments for desorbing water, hydrogen, organic substances, etc. adsorbed on the surface of the insulating layer 103b and the treatment for supplying oxygen into the insulating layer 103b before forming the metal oxide film can be performed at a temperature of 70 ° C. or higher and 200 ° C. or lower in a reduced pressure atmosphere.

- plasma treatment may be performed in an atmosphere containing oxygen.

- oxygen may be supplied to the insulating layer 103b by plasma treatment in an atmosphere containing an oxidizing gas such as nitrous oxide ( N2O).

- oxygen can be supplied while suitably removing organic substances on the surface of the insulating layer 103b. After such treatment, it is preferable to continuously form a metal oxide film without exposing the surface of the insulating layer 103b to the atmosphere.

- the metal oxide film to be formed first is formed, and then the surface thereof is continuously formed without being exposed to the atmosphere. It is preferable to form the following metal oxide film.

- either one or both of the wet etching method and the dry etching method may be used.

- a part of the insulating layer 103b that does not overlap with the semiconductor layer 108 may be etched and thinned.

- the insulating layer 103b may disappear by etching and the surface of the insulating layer 103a may be exposed.

- heat treatment after forming the metal oxide film or processing the metal oxide film into the semiconductor layer 108.

- heat treatment hydrogen or water contained in or adsorbed on the surface of the metal oxide film or the semiconductor layer 108 can be removed. Further, the heat treatment may improve the film quality of the metal oxide film or the semiconductor layer 108 (for example, reduction of defects, improvement of crystallinity, etc.).

- oxygen can be supplied from the insulating layer 103b to the metal oxide film or the semiconductor layer 108 by heat treatment. At this time, it is more preferable to perform heat treatment before processing the semiconductor layer 108.

- the temperature of the heat treatment can be typically 150 ° C. or higher and lower than the strain point of the substrate, 200 ° C. or higher and 500 ° C. or lower, 250 ° C. or higher and 450 ° C. or lower, or 300 ° C. or higher and 450 ° C. or lower.

- the heat treatment can be performed in an atmosphere containing noble gas or nitrogen. Alternatively, after heating in the atmosphere, heating may be performed in an atmosphere containing oxygen. Alternatively, it may be heated in a dry air atmosphere. It is preferable that the atmosphere of the heat treatment does not contain hydrogen, water or the like as much as possible.

- an electric furnace, an RTA (Rapid Thermal Anneal) device, or the like can be used. By using the RTA device, the heat treatment time can be shortened.

- the heat treatment is unnecessary, it may not be performed. Further, the heat treatment is not performed here, and may be combined with the heat treatment performed in a later step. In addition, it may be possible to combine the heat treatment with a treatment under a high temperature (for example, a film forming step) in a later step.

- a high temperature for example, a film forming step

- Insulation Layer 110 [Formation of Insulation Layer 110] Subsequently, the insulating layer 103b and the semiconductor layer 108 are covered to form the insulating layer 110.

- the insulating layer 110 is preferably formed by the PECVD method.

- the plasma treatment it is preferable to perform plasma treatment on the surface of the semiconductor layer 108 before forming the insulating layer 110.

- impurities such as water adsorbed on the surface of the semiconductor layer 108 can be reduced. Therefore, impurities at the interface between the semiconductor layer 108 and the insulating layer 110 can be reduced, so that a highly reliable transistor can be realized.

- the plasma treatment can be performed in an atmosphere such as oxygen, ozone, nitrogen, nitrous oxide, or argon. Further, it is preferable that the plasma treatment and the film formation of the insulating layer 110 are continuously performed without being exposed to the atmosphere.

- heat treatment it is preferable to perform heat treatment after forming the insulating layer 110.

- heat treatment hydrogen or water contained in the insulating layer 110 or adsorbed on the surface can be removed.

- defects in the insulating layer 110 can be reduced.

- the heat treatment is unnecessary, it may not be performed. Further, the heat treatment is not performed here, and may be combined with the heat treatment performed in a later step. In addition, it may be possible to combine the heat treatment with a treatment under a high temperature (for example, a film forming step) in a later step.

- a high temperature for example, a film forming step

- the metal oxide film 114f is preferably formed in an atmosphere containing oxygen, for example. In particular, it is preferably formed by the sputtering method in an atmosphere containing oxygen. As a result, oxygen can be supplied to the insulating layer 110 when the metal oxide film 114f is formed. Oxygen may be supplied to the semiconductor layer 108 at the time of forming the metal oxide film 114f.

- the metal oxide film 114f is formed by a sputtering method using an oxide target containing a metal oxide similar to that of the semiconductor layer 108, the description of the semiconductor layer 108 can be incorporated.

- the metal oxide film may be formed by a reactive sputtering method using oxygen as the film forming gas and using a metal target.

- a metal target for example, an aluminum oxide film can be formed.

- the oxygen supplied into the layer 110 can be increased.

- the oxygen flow rate ratio or oxygen partial pressure is, for example, 50% or more and 100% or less, preferably 65% or more and 100% or less, more preferably 80% or more and 100% or less, and further preferably 90% or more and 100% or less.

- it is preferable that the oxygen flow rate ratio is 100% and the oxygen partial pressure in the film forming chamber is as close as possible to 100%.

- heat treatment oxygen contained in the insulating layer 110 can be supplied to the semiconductor layer 108.

- oxygen can be prevented from being desorbed from the insulating layer 110 to the outside, and a large amount of oxygen can be supplied to the semiconductor layer 108.

- oxygen deficiency in the semiconductor layer 108 can be reduced, and a highly reliable transistor can be realized.

- the heat treatment is unnecessary, it may not be performed. Further, the heat treatment is not performed here, and may be combined with the heat treatment performed in a later step. In addition, it may be possible to combine the heat treatment with a treatment under a high temperature (for example, a film forming step) in a later step.

- a high temperature for example, a film forming step

- the metal oxide film 114f may be removed after the film formation of the metal oxide film 114f or after the heat treatment.

- opening 142 [Formation of opening 142] Subsequently, by etching a part of the metal oxide film 114f, the insulating layer 110, the insulating layer 103b, and the insulating layer 103a, an opening 142 reaching the conductive layer 106 is formed (FIG. 5C). Thereby, the conductive layer 106 and the conductive layer 112 to be formed later can be electrically connected to each other through the opening 142.

- the conductive film 112f it is preferable to use a metal or alloy material having low resistance. Further, as the conductive film 112f, it is preferable to use a material that does not easily release hydrogen and that does not easily diffuse hydrogen. Further, it is preferable to use a material that is hard to oxidize as the conductive film 112f.

- the conductive film 112f is preferably formed by a sputtering method using a sputtering target containing a metal or an alloy.

- the conductive film 112f it is preferable to use a laminated film in which a conductive film that is difficult to oxidize and hydrogen is not easily diffused and a conductive film having low resistance are laminated.

- the conductive layer 112 and the metal oxide layer 114 are formed by etching a part of the conductive film 112f and the metal oxide film 114f. It is preferable that the conductive film 112f and the metal oxide film 114f are each processed using the same resist mask. Alternatively, the metal oxide film 114f may be etched by using the etched conductive layer 112 as a hard mask.

- the conductive layer 112 and the metal oxide layer 114 having substantially the same top surface shape can be formed.

- the semiconductor layer 108 and the insulating layer are formed when the conductive film 112f or the like is etched. It is possible to prevent 103b and the like from being etched and thinned.

- a process of supplying (also referred to as addition or injection) of the impurity element 140 to the semiconductor layer 108 via the insulating layer 110 is performed (FIG. 6A).

- the impurity element 140 is supplied in consideration of the material and thickness of the conductive layer 112 or the like as a mask so that the impurity element 140 is not supplied to the region overlapping the conductive layer 112 of the semiconductor layer 108 as much as possible. It is preferable to determine the conditions. As a result, it is possible to form a channel forming region in which the impurity concentration is sufficiently reduced in the region overlapping the conductive layer 112 of the semiconductor layer 108.

- a plasma ion doping method or an ion implantation method can be preferably used.

- the concentration profile in the depth direction can be controlled with high accuracy by the acceleration voltage of ions, the dose amount, and the like.

- Productivity can be increased by using the plasma ion doping method.

- the ion implantation method using mass separation the purity of the supplied impurity element can be increased.