WO2020058919A1 - 撮像装置、その作製方法および電子機器 - Google Patents

撮像装置、その作製方法および電子機器 Download PDFInfo

- Publication number

- WO2020058919A1 WO2020058919A1 PCT/IB2019/057958 IB2019057958W WO2020058919A1 WO 2020058919 A1 WO2020058919 A1 WO 2020058919A1 IB 2019057958 W IB2019057958 W IB 2019057958W WO 2020058919 A1 WO2020058919 A1 WO 2020058919A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- layer

- transistor

- photoelectric conversion

- imaging device

- crystal silicon

- Prior art date

Links

- 238000003384 imaging method Methods 0.000 title claims abstract description 101

- 238000000034 method Methods 0.000 title claims description 82

- 238000004519 manufacturing process Methods 0.000 title claims description 29

- 239000000758 substrate Substances 0.000 claims abstract description 81

- 238000006243 chemical reaction Methods 0.000 claims abstract description 70

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims abstract description 58

- 230000015572 biosynthetic process Effects 0.000 claims abstract description 28

- 229910044991 metal oxide Inorganic materials 0.000 claims abstract description 13

- 150000004706 metal oxides Chemical class 0.000 claims abstract description 13

- 230000031700 light absorption Effects 0.000 claims abstract description 9

- 230000003287 optical effect Effects 0.000 claims description 19

- 239000003990 capacitor Substances 0.000 claims description 17

- 229910052782 aluminium Inorganic materials 0.000 claims description 11

- 229910052733 gallium Inorganic materials 0.000 claims description 11

- 229910052738 indium Inorganic materials 0.000 claims description 9

- 229910052719 titanium Inorganic materials 0.000 claims description 8

- 229910052725 zinc Inorganic materials 0.000 claims description 8

- 229910052727 yttrium Inorganic materials 0.000 claims description 7

- 229910052684 Cerium Inorganic materials 0.000 claims description 6

- 229910052779 Neodymium Inorganic materials 0.000 claims description 6

- 229910052746 lanthanum Inorganic materials 0.000 claims description 6

- 229910052726 zirconium Inorganic materials 0.000 claims description 6

- 229910052732 germanium Inorganic materials 0.000 claims description 5

- 229910052718 tin Inorganic materials 0.000 claims description 5

- 238000001514 detection method Methods 0.000 abstract description 16

- 230000005540 biological transmission Effects 0.000 abstract description 5

- 239000010410 layer Substances 0.000 description 249

- 239000004065 semiconductor Substances 0.000 description 83

- 239000010408 film Substances 0.000 description 38

- 239000011701 zinc Substances 0.000 description 33

- 238000010586 diagram Methods 0.000 description 26

- 230000006870 function Effects 0.000 description 26

- 229910052751 metal Inorganic materials 0.000 description 24

- 239000002184 metal Substances 0.000 description 20

- 239000000463 material Substances 0.000 description 18

- 239000001257 hydrogen Substances 0.000 description 13

- 229910052739 hydrogen Inorganic materials 0.000 description 13

- 125000004429 atom Chemical group 0.000 description 12

- 239000013078 crystal Substances 0.000 description 12

- 229910052760 oxygen Inorganic materials 0.000 description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 11

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 10

- 239000001301 oxygen Substances 0.000 description 10

- 238000005498 polishing Methods 0.000 description 10

- 210000003462 vein Anatomy 0.000 description 9

- 239000004020 conductor Substances 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 7

- 238000000227 grinding Methods 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 239000000853 adhesive Substances 0.000 description 5

- 230000001070 adhesive effect Effects 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- 238000005304 joining Methods 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 238000005096 rolling process Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 4

- 239000002105 nanoparticle Substances 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 239000006059 cover glass Substances 0.000 description 3

- 230000002950 deficient Effects 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 238000007689 inspection Methods 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 230000007723 transport mechanism Effects 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 102000001554 Hemoglobins Human genes 0.000 description 2

- 108010054147 Hemoglobins Proteins 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 230000001276 controlling effect Effects 0.000 description 2

- 239000002019 doping agent Substances 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000003064 anti-oxidating effect Effects 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000000875 corresponding effect Effects 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000003745 diagnosis Methods 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000002524 electron diffraction data Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14649—Infrared imagers

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B5/00—Optical elements other than lenses

- G02B5/20—Filters

- G02B5/22—Absorbing filters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

- H01L27/14616—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor characterised by the channel of the transistor, e.g. channel having a doping gradient

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14627—Microlenses

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/20—Cameras or camera modules comprising electronic image sensors; Control thereof for generating image signals from infrared radiation only

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

Definitions

- One embodiment of the present invention relates to an imaging device.

- one embodiment of the present invention is not limited to the above technical field.

- the technical field of one embodiment of the present invention disclosed in this specification and the like relates to an object, a method, or a manufacturing method.

- one embodiment of the present invention relates to a process, a machine, a manufacturer, or a composition (composition of matter). Therefore, the technical field of one embodiment of the present invention disclosed in this specification more specifically includes a semiconductor device, a display device, a liquid crystal display device, a light-emitting device, a lighting device, a power storage device, a storage device, an imaging device,

- a driving method or a manufacturing method thereof can be given as an example.

- a semiconductor device in this specification and the like refers to any device that can function by utilizing semiconductor characteristics.

- a transistor and a semiconductor circuit are one embodiment of a semiconductor device.

- the storage device, the display device, the imaging device, and the electronic device sometimes include a semiconductor device.

- Patent Document 1 discloses an imaging device in which a transistor including an oxide semiconductor and having extremely low off-state current is used for a pixel circuit.

- the imaging device is used not only as a means for imaging visible light but also for various uses. For example, it is used for personal authentication, failure analysis, medical diagnosis, security use, and the like. In these applications, in addition to visible light, short-wavelength light such as X-rays, long-wavelength light such as infrared light, and the like are properly used depending on the application.

- One object of one embodiment of the present invention is to provide an imaging device suitable for detecting infrared light. Or. An object is to provide an imaging device suitable for biometric authentication. Alternatively, it is another object to provide an imaging device suitable for imaging a moving object. Another object is to provide a method for manufacturing the imaging device.

- Another object is to provide an imaging device with low power consumption. Another object is to provide a highly reliable imaging device. Another object is to provide a small-sized imaging device. Alternatively, it is another object to provide a novel imaging device. Another object is to provide an operation method of the imaging device. Another object is to provide a new semiconductor device or the like.

- One embodiment of the present invention relates to an imaging device including single crystal silicon in an imaging device and a metal oxide in a channel formation region of a transistor included in a circuit, and a method for manufacturing the imaging device.

- One embodiment of the present invention is a method for manufacturing an imaging device including a single-crystal silicon substrate and a support substrate, in which a conductivity type opposite to that of the single-crystal silicon substrate is provided on a first surface side of the single-crystal silicon substrate.

- a conductive region is provided to form a photoelectric conversion device; a transistor having a metal oxide in a channel formation region over the photoelectric conversion device and electrically connected to the photoelectric conversion device is formed; Forming an insulating layer, forming a second insulating layer on the supporting substrate, bonding the first insulating layer to the surface of the second insulating layer, and forming the first surface of the single crystal silicon substrate.

- This is a method for manufacturing an imaging device in which a surface opposite to the above is ground and polished to reduce the thickness of a light absorption layer of a photoelectric conversion device.

- Another embodiment of the present invention is a method for manufacturing an imaging device including a single-crystal silicon substrate and a support substrate, wherein a conductivity type of the single-crystal silicon substrate is set on a first surface side of the single-crystal silicon substrate.

- a region of the opposite conductivity type is provided to form a photoelectric conversion device; a first insulating layer and a first conductive layer electrically connected to the photoelectric conversion device are formed over the photoelectric conversion device;

- a transistor including an oxide in a channel formation region is formed, a second insulating layer and a second conductive layer electrically connected to the transistor are formed over the transistor, and a surface of the first insulating layer and a second insulating layer are formed.

- Imaging device that thins the light absorption layer of the device Which is a manufacturing method.

- a photoelectric conversion device may be formed by providing a region of the same conductivity type as the single crystal silicon substrate and having a higher carrier concentration than the single crystal silicon substrate on the polished surface side of the single crystal silicon substrate.

- a third insulating layer in contact with the photoelectric conversion device may be formed, and the optical filter layer may be formed so as to overlap with the photoelectric conversion device with the third insulating layer interposed therebetween.

- Another embodiment of the present invention is an imaging device in which a first layer, a second layer, a third layer, and a fourth layer are stacked in this order.

- a second layer, a third layer, and a fourth layer each have a region overlapping each other, the first layer has an optical filter layer, and the second layer is a single crystal silicon.

- the third layer has a device formation layer, the fourth layer has a support substrate, and the second layer has a photoelectric conversion device using single crystal silicon as a light absorption layer.

- the third layer includes a transistor having a metal oxide in a channel formation region, the photoelectric conversion device and the transistor are electrically connected, and the photoelectric conversion device receives light transmitted through the optical filter layer. It is.

- the device formation layer includes a first transistor, a second transistor, a third transistor, a fourth transistor, and a capacitor, and one electrode of the photoelectric conversion device is provided for the first transistor.

- the other of the source and the drain of the first transistor is electrically connected to one of the source and the drain, and the other of the source and the drain of the second transistor is electrically connected to the one of the source and the drain of the second transistor.

- One is electrically connected to one electrode of the capacitor, one electrode of the capacitor is electrically connected to the gate of the third transistor, and one of the source or the drain of the third transistor is connected to the fourth transistor.

- the transistor can be electrically connected to one of a source and a drain of the transistor.

- optical filter layer a layer that blocks visible light and transmits infrared light can be used.

- the metal oxide included in the channel formation region of the transistor may include In, Zn, and M (M is Al, Ti, Ga, Ge, Sn, Y, Zr, La, Ce, Nd, or Hf). preferable.

- an imaging device suitable for detecting infrared light can be provided.

- An imaging device suitable for biometric authentication can be provided.

- an imaging device suitable for imaging a moving object can be provided.

- a method for manufacturing the above imaging device can be provided.

- an imaging device with low power consumption can be provided.

- a highly reliable imaging device can be provided.

- a small imaging device can be provided.

- a novel imaging device can be provided.

- an operation method of the imaging device can be provided.

- a new semiconductor device or the like can be provided.

- FIG. 1 is a diagram illustrating an imaging device.

- 2A and 2B are diagrams illustrating a pixel circuit.

- FIG. 3A is a diagram illustrating a rolling shutter system.

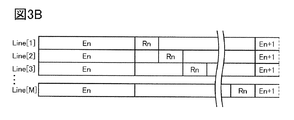

- FIG. 3B is a diagram illustrating the global shutter method.

- 4A and 4B are diagrams illustrating a method for manufacturing an imaging device.

- 5A to 5C are diagrams illustrating a method for manufacturing an imaging device.

- 6A and 6B are diagrams illustrating a method for manufacturing an imaging device.

- 7A to 7C are diagrams illustrating a method for manufacturing an imaging device.

- 8A and 8B are diagrams illustrating a method for manufacturing an imaging device.

- 9A to 9D are diagrams illustrating a method for manufacturing an imaging device.

- 10A to 10C are diagrams illustrating an imaging device.

- FIG. 11A and 11B are timing charts illustrating the operation of the pixel circuit.

- 12A and 12B are diagrams illustrating a pixel circuit.

- FIG. 13 is a block diagram illustrating an imaging device.

- 14A and 14B are diagrams illustrating a configuration of a pixel of the imaging device.

- 15A to 15D are diagrams illustrating a transistor.

- FIGS. 16A1 to 16A3 and FIGS. 16B1 to 16B3 are perspective views illustrating a package and a camera module accommodating an imaging device.

- 17A to 17C are diagrams illustrating electronic devices.

- 18A to 18C are diagrams illustrating electronic devices.

- the element may be configured by a plurality of elements unless there is a functional inconvenience.

- a plurality of transistors operating as switches may be connected in series or in parallel.

- the capacitor may be divided and arranged at a plurality of positions.

- one conductor may have a plurality of functions such as a wiring, an electrode, and a terminal in some cases, and in this specification, a plurality of names may be used for the same element.

- a plurality of names may be used for the same element.

- the elements may actually be connected via a plurality of conductors. In this document, such a configuration is also included in the category of direct connection.

- One embodiment of the present invention is an imaging device supporting infrared light. By converting the received infrared light into image data, it can be used for applications such as biometric authentication, failure analysis of industrial products, and non-defective product selection. In addition, by using a pixel circuit capable of capturing images in the global shutter mode, an image without distortion can be obtained even for a moving subject.

- FIG. 1 is a diagram illustrating an imaging device of one embodiment of the present invention.

- the imaging device has a layer 11, a layer 12, a layer 13, and a layer 14.

- Layer 11 has an optical filter layer.

- the optical filter layer for example, a layer that blocks visible light and transmits infrared light (hereinafter, an infrared light transmitting filter) can be used.

- an infrared light transmitting filter refers to a filter that mainly blocks light (mainly visible light) having a shorter wavelength than near infrared light. A clear infrared light image can be obtained by blocking visible light that is noise.

- the optical filter layer a layer that transmits light of another specific wavelength may be used, and an imaging device specialized in imaging using the light may be used.

- the layer 12 has a photoelectric conversion device (also referred to as a photoelectric conversion element).

- a photodiode can be used as the photoelectric conversion device.

- a photodiode capable of photoelectrically converting infrared light is used for imaging using infrared light.

- a pn junction photodiode using single crystal silicon for a photoelectric conversion portion a pin junction photodiode using polycrystalline silicon or microcrystalline silicon for a photoelectric conversion layer, or the like can be used.

- a material that can photoelectrically convert light in the infrared region such as a compound semiconductor, may be used.

- a pn junction photodiode using single crystal silicon is used as a photoelectric conversion device will be described.

- the light receiving surface is on the layer 11 side.

- the layer 13 has a device formation layer.

- the device formation layer has a transistor and the like which form a pixel circuit.

- a transistor including a metal oxide for a channel formation region (hereinafter, referred to as an OS transistor) is preferably used.

- the OS transistor has a characteristic of an extremely low off-state current and can hold data in a pixel circuit for a long time. Therefore, the OS transistor is suitable as a component of the pixel circuit.

- Layer 14 has a supporting substrate.

- a photodiode is formed by forming a region having a conductivity type opposite to that of the single crystal silicon substrate on the first surface side of the single crystal silicon substrate.

- the single crystal silicon substrate needs to have a thickness (for example, several hundred ⁇ m) that also functions as a support.

- the support substrate is a necessary element in the step of thinning (grinding and polishing). In addition, it becomes a support substrate of the completed imaging device.

- FIG. 2A is a circuit diagram illustrating an example of a pixel circuit including a photoelectric conversion device included in the layer 11 and a transistor included in a device formation layer of the layer 12, and the like.

- the pixel circuit can include the photoelectric conversion device 101, the transistor 103, the transistor 104, the transistor 105, the transistor 106, and the capacitor 108. Note that a structure without the capacitor 108 may be employed.

- One electrode (cathode) of the photoelectric conversion device 101 is electrically connected to one of a source and a drain of the transistor 103.

- the other of the source and the drain of the transistor 103 is electrically connected to one of the source and the drain of the transistor 104.

- One of a source and a drain of the transistor 104 is electrically connected to one electrode of the capacitor 108.

- One electrode of the capacitor 108 is electrically connected to the gate of the transistor 105.

- One of a source and a drain of the transistor 105 is electrically connected to one of a source and a drain of the transistor 106.

- a wiring connecting the other of the source and the drain of the transistor 103, one electrode of the capacitor 108, and the gate of the transistor 105 is referred to as a node FD.

- the node FD can function as a charge storage unit.

- the other electrode (anode) of the photoelectric conversion device 101 is electrically connected to the wiring 121.

- the gate of the transistor 103 is electrically connected to the wiring 127.

- the other of the source and the drain of the transistor 104 is electrically connected to the wiring 122.

- the other of the source and the drain of the transistor 105 is electrically connected to the wiring 123.

- the gate of the transistor 104 is electrically connected to the wiring 126.

- the gate of the transistor 106 is electrically connected to the wiring 128.

- the other electrode of the capacitor 108 is electrically connected to a reference potential line such as a GND wiring, for example.

- the other of the source and the drain of the transistor 106 is electrically connected to the wiring 129.

- the wirings 127, 126, and 128 can function as signal lines for controlling conduction of each transistor.

- the wiring 129 can function as an output line.

- the wirings 121, 122, and 123 can have a function as a power supply line.

- the cathode side of the photoelectric conversion device 101 is electrically connected to the transistor 103 and the node FD is reset to a high potential to operate. Is also a high potential).

- FIG. 2A illustrates a configuration in which the cathode of the photoelectric conversion device 101 is electrically connected to the node FD.

- the anode side of the photoelectric conversion device 101 is electrically connected to one of the source and the drain of the transistor 103. It may be configured to be connected.

- the node FD is reset to a low potential to operate, so that the wiring 122 has a low potential (a lower potential than the wiring 121).

- the transistor 103 has a function of controlling the potential of the node FD.

- the transistor 104 has a function of resetting the potential of the node FD.

- the transistor 105 functions as a source follower circuit and can output the potential of the node FD to the wiring 129 as image data.

- the transistor 106 has a function of selecting a pixel to output image data.

- An OS transistor is preferably used as the transistor 103 and the transistor 104.

- the OS transistor has a characteristic of extremely low off-state current. With the use of the OS transistors as the transistors 103 and 104, the period during which charge can be held at the node FD can be extremely long. Therefore, it is possible to apply a global shutter method in which charge accumulation operation is simultaneously performed in all pixels without complicating a circuit configuration and an operation method.

- FIG. 3A is a diagram schematically illustrating the operation method of the rolling shutter system

- FIG. 3B is a diagram schematically illustrating the global shutter system.

- En represents the exposure (accumulation operation) of the n-th column (n is a natural number)

- Rn represents the read operation of the n-th column.

- 3A and 3B show operations from the first row to the M-th row (M is a natural number).

- the rolling shutter method is an operation method of sequentially performing exposure and data reading, and is a method in which a reading period of a certain row and an exposure period of another row are overlapped. Since the reading operation is performed immediately after the exposure, imaging can be performed even with a circuit configuration in which the data retention period is relatively short. However, since an image of one frame is composed of data having no synchronization at the time of imaging, distortion occurs in imaging of a moving object.

- the global shutter method is an operation method in which exposure is performed simultaneously on all pixels, data is held in each pixel, and data is read out for each row. Therefore, an image without distortion can be obtained even when capturing a moving object.

- a rolling shutter method is often used because a data potential easily flows out of a charge storage portion.

- a transistor having a relatively high off-state current such as a transistor using Si in a channel formation region (hereinafter referred to as a Si transistor)

- Si transistor a transistor using Si in a channel formation region

- a rolling shutter method is often used because a data potential easily flows out of a charge storage portion.

- the OS transistor is used for the pixel circuit, the global shutter method can be easily realized because there is almost no outflow of the data potential from the charge storage portion. Note that the imaging device of one embodiment of the present invention can be operated by a rolling shutter method.

- an OS transistor may be used as the transistors 105 and 106. Further, an OS transistor and a Si transistor may be arbitrarily combined and applied. Further, all the transistors may be OS transistors or Si transistors. Examples of the Si transistor include a transistor including amorphous silicon, a transistor including crystalline silicon (typically, low-temperature polysilicon, single crystal silicon, and the like).

- a first method is a method in which a transistor or the like is formed over a photoelectric conversion device provided over a single crystal silicon substrate and a supporting substrate is attached.

- the photoelectric conversion device 101 is formed on the first surface side of the single crystal silicon substrate 21 (see FIG. 4A). Note that in the drawings for explaining the method for manufacturing the imaging device in this specification, a perspective view showing a part of the entire structure and a cross section of the part are shown. Further, the symbols of transistors and diodes shown in the drawings simply indicate device positions, and do not reflect electrical connections or circuit configurations.

- FIG. 4A illustrates a plurality of photoelectric conversion devices 101 corresponding to each of the plurality of pixels.

- the photoelectric conversion device 101 can be formed by joining a partial region of the single crystal silicon substrate 21 and a region 22 provided on the single crystal silicon substrate.

- the region 22 is a region having a conductivity type opposite to that of the single crystal silicon substrate 21.

- the conductivity type of single crystal silicon substrate 21 is p-type

- the conductivity type of region 22 is n-type. That is, the photoelectric conversion device 101 is a pn junction type photodiode.

- the region 22 can be formed by adding an n-type dopant (such as phosphorus or arsenic) to the first surface of the single crystal silicon substrate 21 by using a method such as ion doping or ion implantation.

- an n-type dopant such as phosphorus or arsenic

- a device formation layer 23 is formed on the photoelectric conversion device 101 (see FIG. 5A).

- the device formation layer 23 is provided with a plurality of insulating films as necessary, in addition to the transistors and capacitors included in the pixel circuit. Note that the transistor is electrically connected to the photoelectric conversion device 101.

- the insulating layer 24 is provided to flatten the unevenness on the surface (see FIG. 5B).

- the insulating layer 24 is not limited to a single layer, and may be a stacked layer of a plurality of layers.

- an inorganic film such as a silicon oxide film or an organic film such as an acrylic resin or polyimide can be used.

- at least the outermost surface is an inorganic film in order to join the inorganic films together.

- the surface may be flattened using CMP (chemical mechanical polishing) or the like as necessary.

- the insulating layer 26 is formed over the supporting substrate 25, the surface of the insulating layer 26 is brought into close contact with the surface of the insulating layer 24, and a bonding process is performed (see FIG. 5C).

- a hard material having high flatness such as a glass substrate, a ceramic substrate, a semiconductor substrate, or a metal substrate. It is preferable to use an inorganic film such as a silicon oxide film for the insulating layer 26, and at least the outermost surface of the insulating layer 24 and the outermost surface of the insulating layer 26 are preferably formed of the same material.

- the surface of the insulating layer 26 and the surface of the insulating layer 24 are made hydrophilic immediately before the bonding. By making the bonding surface hydrophilic, a strong adhesive force at the atomic level can be obtained. Further, heat treatment or pressure treatment may be performed as necessary.

- the surface opposite to the first surface of the single crystal silicon substrate 21 is ground and polished using the grinding and polishing tool 27 to make the single crystal silicon substrate 21 thinner (see FIG. 6A).

- a grinding device, a lapping device, a polishing device, a CMP device, or the like may be appropriately used as needed. Further, wet etching may be used in combination.

- the thickness of the single crystal silicon substrate 21 may be determined in consideration of the penetration length of light, the diffusion length, the thickness of a depletion layer, and the like. For example, when near-infrared light is to be imaged, the thickness is 3 ⁇ m or more and 100 ⁇ m or less, preferably 5 ⁇ m or more and 50 ⁇ m or less, and more preferably 10 ⁇ m or more and 25 ⁇ m or less.

- a region 28 having ap + conductivity type may be formed on the surface of the single-crystal silicon substrate 21 facing the first surface (FIG. 2). 6B).

- the region 28 is a region having a higher carrier concentration and a lower resistance than the single crystal silicon substrate 21, and functions as a carrier extraction electrode (common electrode) of the photoelectric conversion device 101. In the pixel circuit, it also functions as the wiring 121 or a part thereof. Note that a configuration in which the region 28 is not provided may be employed.

- a p-type dopant (boron, aluminum, or the like) is added to a surface of the single crystal silicon substrate 21 facing the first surface by a method such as ion doping, ion implantation, vapor phase diffusion, or solid phase diffusion. And can be formed.

- a method such as ion doping, ion implantation, vapor phase diffusion, or solid phase diffusion. And can be formed. The above is the first method.

- a second method is a method in which a photoelectric conversion device provided over a single crystal silicon substrate is bonded to a transistor or the like provided over a supporting substrate. Note that, in the following description, description overlapping with the first method will be omitted.

- the photoelectric conversion device 101 is formed as in the first method (see FIG. 4A). Then, the insulating layer 31 and the conductive layer 32 are formed over the photoelectric conversion device 101 (see FIG. 4B).

- the insulating layer 31 can be made of the same material as the insulating layer 26.

- the conductive layer 32 is a plug for electrically connecting the photoelectric conversion device 101 and the transistor, and one end is electrically connected to the photoelectric conversion device 101.

- the conductive layer 32 is provided with an opening in the insulating layer 31, the opening is filled with one of conductive materials such as titanium, tungsten, tantalum, and nitride thereof, or a plurality of the conductive materials. And by removing excess conductive material by CMP or the like.

- the conductive layer 32 is buried in the insulating layer 31, and the surface is a flat surface continuous with the surface of the insulating layer 31.

- the device formation layer 23 is formed on the support substrate 25 (see FIG. 7A).

- the device formation layer 23 is provided with a plurality of insulating films as necessary, in addition to the transistors and capacitors included in the pixel circuit.

- an insulating layer 33 and a conductive layer 34 are formed (see FIG. 7B).

- the insulating layer 33 can be made of the same material as the insulating layer 24.

- the conductive layer 34 is a plug for electrically connecting the photoelectric conversion device 101 and the transistor, and one end is electrically connected to the transistor.

- the conductive layer 34 is provided with an opening in the insulating layer 33, the opening is filled with one of conductive materials such as titanium, tungsten, tantalum, and nitride thereof, or a plurality of the conductive materials. And by removing excess conductive material by CMP or the like.

- the conductive layer 34 is buried in the insulating layer 33, and the surface is continuous with the surface of the insulating layer 33 and is flat.

- the surface of the insulating layer 31, the surface of the insulating layer 33, and the surfaces of the conductive layers 32 and 34 are brought into close contact with each other, and a bonding process is performed (see FIG. 7C).

- the surfaces of the insulating layer 31 and the insulating layer 33 be made hydrophilic and the surfaces of the conductive layer 32 and the conductive layer 34 be activated immediately before the bonding.

- the surface opposite to the first surface of the single crystal silicon substrate 21 is ground and polished using the grinding and polishing tool 27 to make the single crystal silicon substrate 21 thinner (see FIG. 8A).

- a region 28 having ap + conductivity type may be formed on the surface of the single-crystal silicon substrate 21 facing the first surface (FIG. 2). 8B). The above is the second method.

- the photoelectric conversion device 101 manufactured by the first method or the second method may be further processed. For example, as shown in FIGS. 9A to 9D, the region 28 of the photoelectric conversion device 101 and the region serving as the light absorption layer may be divided for each pixel.

- a groove for dividing the single crystal silicon substrate 21 including the region 28 for each pixel is provided (see FIG. 9A).

- an insulating layer 35 such as silicon oxide is provided over the groove and the region 28 (see FIG. 9B).

- an opening 36 reaching the region 28 is provided in the insulating layer 35 (see FIG. 9C).

- a conductive layer 37 having a property of transmitting light of a target wavelength is provided over the insulating layer 35 and the opening 36 (see FIG. 9D).

- the conductive layer 37 functions as a carrier extraction electrode (common electrode) of the photoelectric conversion device 101. In the pixel circuit, it also functions as the wiring 121 or a part thereof. Note that, as the conductive layer 37, a conductive organic film such as indium tin oxide, a conductive organic film, a metal mesh, a semiconductor film having the same conductivity type as the region 28, or the like can be used.

- the insulating layer 35 in the groove provided between the pixels, stray light entering from adjacent pixels can be suppressed, and a clearer image can be obtained.

- ⁇ Modification 2> Components may be further added to the configuration manufactured by the first method and the second method and the configuration shown as a modification.

- an insulating layer 38 can be provided over the region 28 as a protective layer.

- a silicon oxide film or the like having a property of transmitting light in a wide wavelength range can be used.

- a structure in which a silicon nitride film serving as a passivation film is stacked may be employed.

- a configuration in which a dielectric film such as hafnium oxide is stacked as the antireflection film may be adopted.

- a light-shielding layer 39 may be formed on the insulating layer 38.

- the light-shielding layer 30 has a function of suppressing light from entering from an oblique direction.

- a metal layer such as aluminum or tungsten can be used.

- a structure in which the metal layer and a dielectric film having a function as an anti-reflection film are stacked can be employed.

- a resin layer may be used instead of the metal layer.

- a structure in which an insulating layer 40 is provided as a planarization film over the insulating layer 38 and the light-blocking layer 39 can be employed.

- an organic resin film or the like can be used as the insulating layer 40.

- an optical filter layer 41 may be provided on the insulating layer 40.

- the optical filter layer 41 may be formed by selecting a material through which light is transmitted according to the purpose.

- an infrared light transmission filter can be used as the optical filter layer. By using the infrared light transmitting filter, an imaging device having sensitivity to only infrared light can be obtained.

- the infrared light transmitting filter for example, a layer formed by dispersing a material that transmits infrared light and absorbs visible light in a base material that transmits infrared light, such as glass or resin, can be used.

- the wavelength of the transmitted infrared light can be adjusted by appropriately selecting a material dispersed in the base material. For example, when the purpose is to image a vein used for biometric authentication or the like, a material that transmits at least near-infrared light that absorbs hemoglobin may be selected.

- a microlens array 42 may be provided so that light condensed by one lens is received by one pixel. By providing the microlens array 42, light can be efficiently received even in a configuration in which the light shielding layer 39 is provided.

- FIGS. 10A to 10C Note that a configuration in which any of the components illustrated in FIGS. 10A to 10C is omitted may be employed. Alternatively, a configuration in which other components are further provided may be employed.

- the transistor 104 is turned off and supply of a reset potential is cut off. Further, the potential of the node FD decreases in accordance with the operation of the photoelectric conversion device 101 (accumulation operation).

- the pixel circuit illustrated in FIG. 2B can be operated according to the timing chart in FIG. 11B. Note that “H” is always supplied to the wirings 121 and 123 and “L” is always supplied to the wiring 122. The basic operation is the same as that described in the timing chart of FIG. 11A.

- a transistor may have a back gate as illustrated in FIGS. 12A and 12B.

- FIG. 12A shows a configuration in which the back gate is electrically connected to the front gate, which has an effect of increasing the on-state current.

- FIG. 12B illustrates a structure in which the back gate is electrically connected to a wiring which can supply a constant potential, so that the threshold voltage of the transistor can be controlled.

- each transistor can perform an appropriate operation, such as a combination of FIGS. 12A and 12B, may be employed.

- the pixel circuit may include a transistor without a back gate.

- FIG. 13 is a block diagram illustrating an imaging device of one embodiment of the present invention.

- the imaging device includes a pixel array 51 including pixel circuits 50 of one embodiment of the present invention arranged in a matrix, a circuit 52 (row driver) having a function of selecting a row of the pixel array 51, and a pixel circuit 50.

- a circuit 53 having a function of reading data and a circuit 58 for supplying a power supply potential are provided.

- the circuit 53 includes a circuit 54 (column driver) having a function of selecting a column of the pixel array 51, a circuit 55 (CDS circuit) for performing correlated double sampling processing on output data of the pixel circuit 50, A circuit 56 (A / D conversion circuit or the like) having a function of converting analog data output from 55 into digital data can be provided.

- a circuit 54 column driver

- CDS circuit circuit 55

- a circuit 56 A / D conversion circuit or the like

- circuits 52 and 54 a shift register circuit or a decoder circuit can be used. Part or all of the circuits 52, 53, and 58 may be formed using OS transistors provided in the layer 13 illustrated in FIG. Alternatively, part of the circuits 52, 53, and 58 may be formed using Si transistors provided in the layer 12.

- FIG. 14A is a diagram illustrating an example of a cross section of a pixel that can be manufactured by the first method.

- FIG. 14B is a diagram illustrating an example of a cross section of a pixel that can be manufactured by the second method.

- the layer 12 includes, as the photoelectric conversion device 101, a pn junction including a region 22 having an n-type conductivity, a region having a p-type conductivity (single-crystal silicon substrate 21), and a region 28 having a p + -type conductivity.

- a type photodiode is provided.

- the layer 13 is provided with an OS transistor.

- 14A and 14B illustrate the transistors 103, 105, and 106 using the circuit configuration illustrated in FIG. 2A as an example.

- the layer 14 is provided with a support substrate 25 and the like.

- the layer 13 in FIG. 14A illustrates an example in which the insulating layer 24 is two layers of the insulating layer 63 and the insulating layer 64.

- the insulating layer 63 for example, an organic film such as an acrylic resin or a polyimide can be used.

- the insulating layer 64 an inorganic film such as a silicon oxide film can be used.

- the insulating layer 31 includes three layers of an insulating layer 63, an insulating layer 65, and an insulating layer 64.

- the insulating layer 65 has a function of preventing diffusion of hydrogen, and is provided between a region where an OS transistor is formed and a region where a Si device such as the photoelectric conversion device 101 is formed. Hydrogen in the insulating layer provided near the photoelectric conversion device 101 terminates dangling bonds of silicon. On the other hand, hydrogen in the insulating layer provided near the channel formation region of the transistors 102, 105, and 106 is one of the factors that generate carriers in the oxide semiconductor layer.

- the reliability of the Si device can be improved by confining hydrogen in one layer by the insulating layer 65. In addition, by suppressing diffusion of hydrogen from one layer to the other layer, reliability of the transistors 102, 105, and 106 can be improved.

- the insulating layer 65 for example, aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, hafnium oxynitride, yttria-stabilized zirconia (YSZ), or the like can be used.

- aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, hafnium oxynitride, yttria-stabilized zirconia (YSZ), or the like can be used.

- the insulating layer 65 may be provided at other positions as long as the above-described effects can be obtained.

- the insulating layers 63 and 65 may be interchanged.

- FIG. 15A shows details of the OS transistor.

- the OS transistor illustrated in FIG. 15A has a self-aligned structure in which an insulating layer is provided over a stack of an oxide semiconductor layer and a conductive layer, and a groove which reaches the semiconductor layer is provided to form a source electrode 205 and a drain electrode 206. is there.

- the OS transistor can include a channel formation region, a source region 203, and a drain region 204 formed in the oxide semiconductor layer 207, a gate electrode 201, and a gate insulating film 202. At least the gate insulating film 202 and the gate electrode 201 are provided in the groove.

- the groove may be further provided with an oxide semiconductor layer 208.

- the OS transistor may have a self-aligned structure in which a source region 203 and a drain region 204 are formed in a semiconductor layer using the gate electrode 201 as a mask.

- a non-self-aligned top-gate transistor including a region where the source electrode 205 or the drain electrode 206 and the gate electrode 201 overlap with each other may be used.

- the transistors 103, 105, and 106 have a structure including a back gate 535, a structure without a back gate may be employed.

- the back gate 535 may be electrically connected to a front gate of a transistor provided opposite to the transistor as illustrated in a cross-sectional view in the channel width direction of the transistor illustrated in FIG. 15D.

- FIG. 15D shows a cross section taken along line A1-A2 of the transistor in FIG. 15A, the same applies to transistors having other structures.

- a configuration in which a fixed potential different from that of the front gate may be supplied to the back gate 535 may be employed.

- a metal oxide having an energy gap of 2 eV or more, preferably 2.5 eV or more, more preferably 3 eV or more can be used.

- a typical example is an oxide semiconductor containing indium; for example, a CAAC-OS or a CAC-OS described later can be used.

- the CAAC-OS has stable atoms in its crystal and is suitable for a transistor or the like in which reliability is emphasized.

- the CAC-OS has high mobility characteristics, and thus is suitable for a transistor that drives at high speed or the like.

- the OS transistor has an extremely low off-current characteristic of several yA / ⁇ m (current value per 1 ⁇ m of channel width) because the energy gap of the semiconductor layer is large. Further, the OS transistor has characteristics different from those of the Si transistor, such as not generating impact ionization, avalanche breakdown, and a short-channel effect, and thus can form a highly reliable circuit with high withstand voltage. In addition, variation in electrical characteristics due to non-uniformity of crystallinity, which is a problem in the Si transistor, hardly occurs in the OS transistor.

- the semiconductor layer included in the OS transistor includes an In-M-Zn-based oxide including, for example, indium, zinc, and M (a metal such as aluminum, titanium, gallium, germanium, yttrium, zirconium, lanthanum, cerium, tin, neodymium, or hafnium). Can be obtained.

- the In-M-Zn-based oxide can be formed by, for example, a sputtering method, an ALD (Atomic layer deposition) method, a MOCVD (Metal organic chemical vapor deposition) method, or the like.

- the atomic ratio of metal elements in a sputtering target preferably satisfies In ⁇ M and Zn ⁇ M.

- each of the atomic ratios of the semiconductor layers to be formed includes a variation of ⁇ 40% of the atomic ratio of the metal element contained in the sputtering target.

- the semiconductor layer an oxide semiconductor with a low carrier density is used.

- the semiconductor layer has a carrier density of 1 ⁇ 10 17 / cm 3 or less, preferably 1 ⁇ 10 15 / cm 3 or less, further preferably 1 ⁇ 10 13 / cm 3 or less, more preferably 1 ⁇ 10 11 / cm 3. 3 or less, more preferably less than 1 ⁇ 10 10 / cm 3 , and an oxide semiconductor of 1 ⁇ 10 ⁇ 9 / cm 3 or more can be used.

- Such an oxide semiconductor is referred to as a high-purity intrinsic or substantially high-purity intrinsic oxide semiconductor. It can be said that the oxide semiconductor has a low density of defect states and has stable characteristics.

- the present invention is not limited thereto, and a transistor having an appropriate composition may be used in accordance with required semiconductor characteristics and electric characteristics (eg, field-effect mobility and threshold voltage) of the transistor.

- the carrier density and the impurity concentration of the semiconductor layer, the defect density, the atomic ratio between a metal element and oxygen, the interatomic distance, and the density be appropriate.

- the concentration of silicon or carbon (concentration obtained by secondary ion mass spectrometry) in the semiconductor layer is set to 2 ⁇ 10 18 atoms / cm 3 or less, preferably 2 ⁇ 10 17 atoms / cm 3 or less.

- an alkali metal and an alkaline earth metal may generate carriers when combined with an oxide semiconductor, which may increase off-state current of a transistor. Therefore, the concentration of alkali metal or alkaline earth metal in the semiconductor layer (concentration obtained by secondary ion mass spectrometry) is 1 ⁇ 10 18 atoms / cm 3 or less, preferably 2 ⁇ 10 16 atoms / cm 3 or less.

- the nitrogen concentration (concentration obtained by secondary ion mass spectrometry) in the semiconductor layer is preferably 5 ⁇ 10 18 atoms / cm 3 or less.

- the transistor when hydrogen is contained in the oxide semiconductor included in the semiconductor layer, oxygen reacts with oxygen bonded to a metal atom to become water, which may cause oxygen vacancies in the oxide semiconductor.

- oxygen vacancy When an oxygen vacancy is contained in a channel formation region in an oxide semiconductor, the transistor might have normally-on characteristics. Further, a defect in which hydrogen is contained in an oxygen vacancy functions as a donor, and an electron serving as a carrier may be generated. Further, in some cases, part of hydrogen is bonded to oxygen which is bonded to a metal atom to generate electrons serving as carriers. Therefore, a transistor including an oxide semiconductor containing a large amount of hydrogen is likely to have normally-on characteristics.

- a defect in which hydrogen is contained in oxygen vacancies can function as a donor of an oxide semiconductor.

- the hydrogen concentration obtained by secondary ion mass spectrometry is lower than 1 ⁇ 10 20 atoms / cm 3 , preferably 1 ⁇ 10 19 atoms / cm 3. It is less than 3 , more preferably less than 5 ⁇ 10 18 atoms / cm 3 , further preferably less than 1 ⁇ 10 18 atoms / cm 3 .

- an oxide semiconductor in which impurities such as hydrogen are sufficiently reduced is used for a channel formation region of a transistor, stable electric characteristics can be provided.

- An oxide semiconductor (metal oxide) is classified into a single crystal oxide semiconductor and another non-single-crystal oxide semiconductor.

- a non-single-crystal oxide semiconductor for example, CAAC-OS (C-Axis Aligned Crystalline Oxide Semiconductor), a polycrystalline oxide semiconductor, nc-OS (nanocrystalline oxide semiconductor), and a pseudo amorphous oxide semiconductor (a-like) OS: amorphous-like oxide semiconductor, an amorphous oxide semiconductor, or the like.

- CAAC-OS C-Axis Aligned Crystalline Oxide Semiconductor

- nc-OS nanocrystalline oxide semiconductor

- a pseudo amorphous oxide semiconductor a-like oxide semiconductor

- the amorphous structure has the highest density of defect states

- the CAAC-OS has the lowest density of defect states.

- An oxide semiconductor film having an amorphous structure has, for example, a disordered atomic arrangement and no crystalline component.

- an oxide film having an amorphous structure has, for example, a completely amorphous structure and no crystal part.

- the semiconductor layer is a mixed film including two or more of an amorphous structure region, a microcrystalline structure region, a polycrystalline structure region, a CAAC-OS region, and a single crystal structure region.

- the mixed film may have a single-layer structure or a stacked structure including any two or more of the above-described regions.

- a structure of a cloud-aligned composite (CAC) -OS which is one embodiment of a non-single-crystal semiconductor layer, is described below.

- the CAC-OS is one structure of a material in which an element included in an oxide semiconductor is unevenly distributed in a size of, for example, 0.5 nm or more and 10 nm or less, preferably 1 nm or more and 2 nm or less.

- one or more metal elements are unevenly distributed in an oxide semiconductor, and a region including the metal element has a size of 0.5 nm to 10 nm, preferably 1 nm to 2 nm, or a size in the vicinity thereof.

- the state mixed by is also referred to as a mosaic shape or a patch shape.

- the oxide semiconductor preferably contains at least indium. In particular, it preferably contains indium and zinc. In addition to them, aluminum, gallium, yttrium, copper, vanadium, beryllium, boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, or magnesium, etc. Or a plurality of types selected from the group consisting of:

- CAC-OS in an In-Ga-Zn oxide is an indium oxide (hereinafter referred to as InO).

- InO indium oxide

- X1 X1 is greater real than 0

- X2 Zn Y2 O Z2 X2, Y2, and Z2 is larger real than 0

- gallium An oxide hereinafter, referred to as GaO X3 (X3 is a real number larger than 0)

- Ga X4 Zn Y4 O Z4 X4, Y4, and Z4 are real numbers larger than 0)

- the material becomes mosaic by separate into, mosaic InO X1 or in X2 Zn Y2 O Z2, is a configuration in which uniformly distributed in the film (hereinafter Also referred to as a cloud-like

- the CAC-OS is a composite oxide semiconductor having a structure in which a region containing GaO X3 as a main component and a region containing In X2 Zn Y2 O Z2 or InO X1 as a main component are mixed.

- the atomic ratio of In to the element M in the first region is larger than the atomic ratio of In to the element M in the second region.

- the In concentration is higher than that of the region No. 2.

- IGZO is a common name and may refer to one compound of In, Ga, Zn, and O. Representative examples are represented by InGaO 3 (ZnO) m1 (m1 is a natural number), or In (1 + x0) Ga ( 1-x0) O 3 (ZnO) m0 (-1 ⁇ x0 ⁇ 1, m0 is an arbitrary number) Crystalline compounds may be mentioned.

- the above crystalline compound has a single crystal structure, a polycrystal structure, or a CAAC structure.

- the CAAC structure is a crystal structure in which a plurality of IGZO nanocrystals have a c-axis orientation and are connected without being oriented in the ab plane.

- CAC-OS relates to the material configuration of an oxide semiconductor.

- a CAC-OS is a material composition containing In, Ga, Zn, and O, a region which is observed as a nanoparticle mainly containing Ga as a part, and a nanoparticle mainly containing In as a part.

- a region observed in a shape means a configuration in which each region is randomly dispersed in a mosaic shape. Therefore, in the CAC-OS, the crystal structure is a secondary element.

- the CAC-OS does not include a stacked structure of two or more kinds of films having different compositions.