WO2019181558A1 - 光センサー回路、光センサー装置、および、表示装置 - Google Patents

光センサー回路、光センサー装置、および、表示装置 Download PDFInfo

- Publication number

- WO2019181558A1 WO2019181558A1 PCT/JP2019/009306 JP2019009306W WO2019181558A1 WO 2019181558 A1 WO2019181558 A1 WO 2019181558A1 JP 2019009306 W JP2019009306 W JP 2019009306W WO 2019181558 A1 WO2019181558 A1 WO 2019181558A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- switching transistor

- transistor

- gate

- light receiving

- period

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 84

- 230000003287 optical effect Effects 0.000 claims description 66

- 239000003990 capacitor Substances 0.000 claims description 27

- 238000010586 diagram Methods 0.000 description 19

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 230000004048 modification Effects 0.000 description 11

- 238000012986 modification Methods 0.000 description 11

- CNQCVBJFEGMYDW-UHFFFAOYSA-N lawrencium atom Chemical compound [Lr] CNQCVBJFEGMYDW-UHFFFAOYSA-N 0.000 description 10

- 239000010408 film Substances 0.000 description 9

- 239000004973 liquid crystal related substance Substances 0.000 description 8

- 239000000463 material Substances 0.000 description 8

- 230000000903 blocking effect Effects 0.000 description 6

- 239000000758 substrate Substances 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- 238000005513 bias potential Methods 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- 230000007704 transition Effects 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 230000000052 comparative effect Effects 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 239000004020 conductor Substances 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 101100410782 Arabidopsis thaliana PXG1 gene Proteins 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000001782 photodegradation Methods 0.000 description 2

- 101150115013 DSP1 gene Proteins 0.000 description 1

- 101150052726 DSP2 gene Proteins 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/12—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof structurally associated with, e.g. formed in or on a common substrate with, one or more electric light sources, e.g. electroluminescent light sources, and electrically or optically coupled thereto

- H01L31/125—Composite devices with photosensitive elements and electroluminescent elements within one single body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by potential barriers, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/112—Devices sensitive to infrared, visible or ultraviolet radiation characterised by field-effect operation, e.g. junction field-effect phototransistor

- H01L31/113—Devices sensitive to infrared, visible or ultraviolet radiation characterised by field-effect operation, e.g. junction field-effect phototransistor being of the conductor-insulator-semiconductor type, e.g. metal-insulator-semiconductor field-effect transistor

- H01L31/1136—Devices sensitive to infrared, visible or ultraviolet radiation characterised by field-effect operation, e.g. junction field-effect phototransistor being of the conductor-insulator-semiconductor type, e.g. metal-insulator-semiconductor field-effect transistor the device being a metal-insulator-semiconductor field-effect transistor

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1601—Constructional details related to the housing of computer displays, e.g. of CRT monitors, of flat displays

- G06F1/1605—Multimedia displays, e.g. with integrated or attached speakers, cameras, microphones

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/042—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by opto-electronic means

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by potential barriers, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/1016—Devices sensitive to infrared, visible or ultraviolet radiation comprising transparent or semitransparent devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

Definitions

- the present invention relates to an optical sensor circuit, and is particularly applicable to an optical sensor circuit, an optical sensor device, and a display device using an oxide semiconductor transistor.

- Patent Document 1 JP 2011-243950 A (Patent Document 1) and JP 2009-182194 A (Patent Document 2) have been proposed as an optical sensing circuit or an optical sensor element using an oxide semiconductor transistor.

- An oxide semiconductor transistor has a deterioration mode called optical negative bias deterioration in which a threshold voltage greatly fluctuates when a negative bias is applied while irradiating light.

- optical negative bias deterioration in which a threshold voltage greatly fluctuates when a negative bias is applied while irradiating light.

- the oxide semiconductor transistor is irradiated with light, the drain current decreases very slowly even if the light irradiation is stopped. Therefore, there is a problem that it is difficult to use an oxide semiconductor transistor for an optical sensor element.

- An object of the present invention is to provide an optical sensor circuit using an oxide semiconductor transistor capable of performing a stable operation.

- the optical sensor circuit includes a light receiving transistor, a first switching transistor, a second switching transistor, and a capacitive element.

- the light receiving transistor includes a gate connected to the first wiring, a source connected to the second wiring, and a drain.

- the first switching transistor includes a gate connected to a third wiring, a source connected to a fourth wiring, and a drain connected to the drain of the light receiving transistor.

- the capacitive element includes a first terminal connected to the drain of the light receiving transistor and a second terminal connected to the source of the first switching transistor.

- the second switching transistor includes a gate connected to a gate line, a source connected to a signal line, and a drain connected to the first terminal of the capacitor.

- Each of the light receiving transistor, the first switching transistor, and the second switching transistor includes an oxide semiconductor layer as a channel layer.

- the photosensor device includes the plurality of gate lines, the plurality of signal lines, and the plurality of gate lines and the plurality of signal lines so that one photosensor circuit is connected to one gate line and one signal line.

- Each of the plurality of photosensor circuits includes a light receiving transistor, a first switching transistor, a second switching transistor, and a capacitive element.

- the light receiving transistor includes a gate connected to the first wiring, a source connected to the second wiring, and a drain.

- the first switching transistor includes a gate connected to a third wiring, a source connected to a fourth wiring, and a drain connected to the drain of the light receiving transistor.

- the capacitive element has a first terminal connected to the drain of the light receiving transistor and a second terminal connected to the source of the first switching transistor.

- the second switching transistor includes a gate connected to a corresponding gate line, a source connected to a corresponding signal line, and a drain connected to the first terminal of the capacitive element.

- Each of the light receiving transistor, the first switching transistor, and the second switching transistor includes an oxide semiconductor layer as a channel layer.

- the display device has a display panel having a display area.

- the display area includes display pixels and a photosensor circuit.

- the photosensor circuit includes a light receiving transistor, a first switching transistor, a second switching transistor, and a capacitive element.

- the light receiving transistor includes a gate connected to the first wiring, a source connected to the second wiring, and a drain.

- the first switching transistor includes a gate connected to a third wiring, a source connected to a fourth wiring, and a drain connected to the drain of the light receiving transistor.

- the capacitive element includes a first terminal connected to the drain of the light receiving transistor and a second terminal connected to the source of the first switching transistor.

- the second switching transistor includes a gate connected to a gate line, a source connected to a signal line, and a drain connected to the first terminal of the capacitor.

- Each of the light receiving transistor, the first switching transistor, and the second switching transistor includes an oxide semiconductor layer as a channel layer.

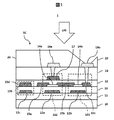

- FIG. 2 is a cross-sectional view schematically illustrating an exemplary structure of the light receiving transistor in FIG. 1.

- FIG. 2 is a cross-sectional view schematically illustrating an exemplary structure of the switching transistor of FIG. 1. It is a figure which shows the characteristic of the drain current of the light reception transistor when there is no light irradiation. It is a figure which shows the characteristic of the drain current of a light reception transistor in case there exists light irradiation.

- It is a circuit diagram explaining the example of an example structure of the optical sensor circuit which concerns on an Example. It is a block diagram which shows the example whole structure of the optical sensor apparatus which concerns on an Example.

- FIG. 12 is a diagram exemplarily showing a gate bias potential (Vg) of a gate electrode of an oxide semiconductor transistor when a reset pulse is applied in FIG. 12 is a diagram exemplarily showing a drain bias potential (Vd) of a drain electrode of an oxide semiconductor transistor when a reset pulse is applied in FIG. 11 is a plan view conceptually showing a display device according to application example 1.

- Vg gate bias potential

- Vd drain bias potential

- FIG. 12 is a plan view conceptually showing a display device according to application example 2.

- FIG. It is a top view which shows notionally the display apparatus which concerns on a modification.

- FIG. 1 is a cross-sectional view schematically illustrating an exemplary structure of an oxide semiconductor transistor used in the photosensor device according to the example.

- FIG. 2 is a cross-sectional view schematically illustrating an exemplary structure of the light receiving transistor 101 of FIG.

- FIG. 3 is a cross-sectional view schematically illustrating an exemplary structure of the switching transistor 102 of FIG.

- the optical sensor device 1 includes a plurality of optical sensor circuits SC.

- one light receiving transistor 101, one switching transistor 102, and capacitive element 103 that are used in each photosensor circuit SC are illustrated. Both the light receiving transistor 101 and the switching transistor 102 are configured using oxide semiconductor transistors.

- the light receiving transistor 101 includes a gate electrode 12b, an oxide semiconductor layer 14b, a drain electrode 15b, and a source electrode 15c. That is, the light receiving transistor 101 is a lower gate structure in which the gate electrode 12b is provided below the oxide semiconductor layer 14b, that is, a bottom gate type three-terminal (gate, source, and drain) element. It has a bottom gate / top contact structure (called an inverted stagger structure).

- the switching transistor 102 includes a gate electrode 12a, an oxide semiconductor 14a, a source electrode 15a and a drain electrode 15b, and a back gate electrode 17. That is, the switching transistor 102 is a bottom-gate type four-terminal (gate, source, drain, and back gate) element, and has a configuration in which the back gate electrode 17 is provided in an inverted staggered structure.

- the switching transistor 102 may be a dual gate drive that drives the gate electrode 12 a and the back gate electrode 17.

- the switching transistor 102 may have a configuration in which the back gate electrode 17 is connected to the source electrode 15a.

- the switching transistor 102 is not limited to the bottom gate type configuration, and may have a top gate type configuration.

- the upper gate structure is a structure in which the gate electrode 12a is provided above the oxide semiconductor 14a.

- the capacitive element 103 includes a gate electrode 12c, a source or drain electrode 15d, and a gate insulating film 13.

- the capacitor 103 is not limited to this structure, and can include the gate electrode 12c, the oxide semiconductor layer provided simultaneously with the oxide semiconductor layers 14a and 14b, and the gate insulating film 13. Further, the capacitor 103 can be constituted by the source or drain electrode 15 d, a metal layer provided simultaneously with the back gate electrode 17, and the insulating layer 16.

- the oxide semiconductor layers 14a and 14b constitute channel layers (active layers) of the oxide semiconductor transistors (101 and 102), and the material thereof can include an oxide semiconductor material such as a ZnO-based material.

- the ZnO-based material may include, for example, ZnO, or at least one material selected from Hf, Y, Ta, Zr, Ti, Cu, Ni, Cr, In, Ga, Al, Sn, and Mg Can also include a mixture or compound containing ZnO.

- such a ZnO-based material can include ZnO, TaZnO, InZnO (IZO), and GaInZnO (Gallium Indium Zinc Oxide; GIZO).

- Such an oxide semiconductor transistor can be used as the light receiving transistor 101 because the threshold voltage and the drain current change depending on the amount of incident light LIG.

- the switching transistor 102 does not need to change the threshold voltage and the drain current depending on the amount of incident light LIG. Therefore, as shown in FIGS. 1 and 3, a gate is provided below the oxide semiconductor layer 14a.

- An electrode 12a is provided, and a back gate electrode 17 is provided above the oxide semiconductor layer 14a.

- the oxide semiconductor layer 14a of the switching transistor 102 is configured not to be irradiated with the incident light LIG. That is, the back gate electrode 17 has a function of blocking or blocking incident light LIG to the oxide semiconductor layer 14a.

- the optical sensor device 1 includes a substrate 10, an insulating layer 11 provided entirely on the substrate 10, and gate electrodes 12 a, 12 b, 12 c partially provided on the insulating layer 11. And the insulating layer 11 and the gate insulating film 13 provided on the gate electrodes 12a, 12b, and 12c so as to cover the side surfaces and the upper surface of the gate electrodes 12a, 12b, and 12c.

- the optical sensor device 1 further includes oxide semiconductor layers 14a and 14b partially provided on the gate insulating film 13, and source and drain electrodes provided so as to cover both sides of the oxide semiconductor layers 14a and 14b.

- the optical sensor device 1 further includes a back gate electrode 17 partially provided on the transparent insulating layer 16 so as to cover the oxide semiconductor layer 14a, and the entire back gate electrode 17 and the transparent insulating layer 16.

- a transparent insulating layer 20 as a protective film provided so as to cover the whole.

- the wiring layer 19a is connected to the back gate electrode 17 via a via electrode

- the wiring layer 19b is connected to the source electrode 15c via a via electrode.

- the substrate 10 can use a general substrate material such as glass, silicon, or a resin substrate.

- the insulating layer 11, the gate insulating film 13, the transparent insulating layer 16, the transparent insulating layer 18, and the transparent insulating layer 20 can be made of a silicon oxide film material.

- the insulating layer 11, the gate insulating film 13, the transparent insulating layer 16, the transparent insulating layer 18, and the transparent insulating layer 20 can be formed by a CVD method.

- the gate electrodes 12a, 12b, 12c, the source and drain electrodes 15a, 15b, 15c, 15d, the back gate electrode 17, and the wiring layers 19a, 19b can use a conductive metal or a conductive metal oxide.

- the oxide semiconductor layers 14a and 14b can be formed by a sputtering method.

- the gate electrodes 12a, 12b, and 12c, and the source and drain electrodes 15a, 15b, 15c, and 15d are transparent such as ITO. It can be made of a conductive material.

- the back gate electrode 17 irradiates the oxide semiconductor layer 14a with the incident light LIG.

- the back gate electrode 17 is preferably made of an opaque conductive material because it has a role of shielding or blocking light.

- the gate electrode 12c blocks or blocks the irradiation of the incident light LIG to the oxide semiconductor layer 14a. Since it has a blocking function, the gate electrode 12c is preferably made of an opaque conductive material.

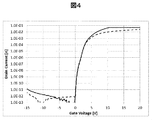

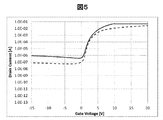

- FIG. 4 is a diagram showing the drain current characteristics of the light receiving transistor 101 when there is no light irradiation.

- FIG. 5 is a diagram showing the drain current characteristics of the light receiving transistor 101 when there is light irradiation. 4 and FIG. 5, the vertical axis indicates the drain current value of the light receiving transistor 101, and the horizontal axis indicates the gate voltage of the light receiving transistor 101. The characteristic indicated by the dotted line indicates the case where the drain voltage is 1V, and the characteristic indicated by the solid line indicates the case where the drain voltage is 10V.

- the drain current is The value is very small, such as below the lower limit of measurement.

- the drain current increases significantly as compared with FIG.

- the value of the drain current of the light receiving transistor 101 in an off state (herein also referred to as an off current) is set as shown in FIGS. It can be used to determine the presence or absence of light irradiation.

- an off current the value of the drain current of the light receiving transistor 101 in an off state

- the signal ratio of the off-current of the light receiving transistor 101 in the presence or absence of light irradiation is large, it is possible to detect the presence or absence of light irradiation in a stable operation.

- the oxide semiconductor transistor has a deterioration mode called optical negative bias deterioration in which the threshold voltage greatly fluctuates when a negative bias is applied while irradiating light.

- optical negative bias deterioration in which the threshold voltage greatly fluctuates when a negative bias is applied while irradiating light.

- the trade-off that the photodegradation is accelerated when the photosensitivity is increased is a problem.

- the light-receiving transistor 101 since the off-state current of an oxide semiconductor transistor is very low, the light-receiving transistor 101 has a three-terminal structure, and the light-receiving transistor 101 is operated in an off region, so that a sufficient signal ratio of off-state current with and without light irradiation is obtained be able to.

- the light irradiation amount between the two elements 101 and 102 can be controlled. Thereby, it is possible to detect the presence or absence of light irradiation with a stable operation.

- the photodegradation of the oxide semiconductor transistor moves the threshold value in the negative direction. Therefore, when the oxide semiconductor transistor is turned off, the negative potential applied to the gate electrode is increased, thereby affecting the negative fluctuation of the threshold value. It is possible to make it difficult to receive.

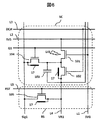

- FIG. 6 is a circuit diagram illustrating an exemplary configuration example of the optical sensor circuit according to the embodiment.

- the optical sensor circuit SC includes a light receiving transistor 101 that is a light receiving element, a switching transistor 102, a switching transistor 104, and a capacitive element 103.

- a reset circuit RS connected to the photosensor circuit SC is depicted.

- the reset circuit RS includes a switching transistor 105.

- each of the switching transistors 104 and 105 is formed of an oxide semiconductor transistor having a back gate electrode 17, similarly to the switching transistor 102 described with reference to FIGS. 1 and 3.

- each of the switching transistors 102, 104, and 105 has a configuration in which the back gate electrode 17 is connected to the source electrode.

- the switching transistor 102 may be referred to as a first switching transistor, the switching transistor 104 as a second switching transistor, and the switching transistor 105 as a third switching transistor.

- the light receiving transistor 101 is connected to the gate connected to the wiring (first wiring) L1 to which the first gate control signal SVG is supplied and the wiring (second wiring) L2 to the wiring to which the first source control signal SVS is supplied.

- the switching transistor 102 is connected to a gate connected to the wiring (third wiring) L3 to which the second gate control signal DCH is supplied and to a wiring (fourth wiring) L4 to which the second source control signal VR1 is supplied.

- Capacitance element 103 has a first terminal connected to the drain of light-receiving transistor 101 and a second terminal connected to the source of switching transistor 102.

- the switching transistor 104 has a gate connected to the gate line G1, a source connected to the signal line Sig1, and a drain connected to the first terminal of the capacitor 103.

- the capacitor element 103 has a function of storing charges according to the amount of light irradiated when the light receiving transistor 101 is irradiated with the incident light LIG.

- the charge stored in the capacitor 103 is read out to the signal line Sig1 through the source / drain path of the switching transistor 104 which is turned on when the gate line G1 is set to the selection level.

- the reset circuit RS has a switching transistor 105.

- the switching transistor 105 is connected to the gate connected to the wiring (fifth wiring) L5 to which the reset signal RST is supplied, the source connected to the wiring L4 to which the second source control signal VR1 is supplied, and the signal line Sig1. Drain.

- the wiring L4 to which the second source control signal VR1 is supplied is connected to the second terminal of the capacitor 103 of each photosensor circuit SC when a plurality of photosensor circuits SC are provided.

- FIG. 7 is a block diagram illustrating an exemplary overall configuration of the optical sensor device according to the embodiment.

- FIG. 7 shows a plurality of wirings other than the light receiving transistor 101, the switching transistors 102 and 104, the capacitor 103, the gate line G, and the signal line S shown in FIG. L1-L4) are not described.

- the photosensor device 1 is provided on, for example, a rectangular photosensor panel LPNL.

- An array unit ARR is provided on the photosensor panel LPNL, and the array unit ARR includes a plurality of photosensor circuits (SC11, SC12,...) Arranged in a matrix such as m rows and n columns, for example. , SCmn).

- m gate lines G (G1, G2, G3,..., Gm) are provided, and n signal lines S (Sig1, Sig2, Sig3,. ., Sign).

- Photosensor circuits SC11, SC12, SC13,. . . , SC1n is connected to the gate line G1

- the optical sensor circuits SC21, SC22, SC23,. . . , SC2n is connected to the gate line G2

- the optical sensor circuits SC31, SC32, SC33,. . . , SC3n is connected to a gate line G3.

- a plurality of photosensor circuits arranged in corresponding rows are connected to the other gate lines.

- the optical sensor circuits SC11, SC21, SC31,. . . , SCm1 is connected to the signal line Sig1

- the optical sensor circuits SC12, SC22, SC32,. . . , SCm2 is connected to the signal line Sig2

- the optical sensor circuits SC13, SC23, SC33,. . . , SCm3 is connected to a signal line Sig3.

- a plurality of photosensor circuits arranged in corresponding columns are connected to the other signal lines.

- the plurality of photosensor circuits are connected to the plurality of gate lines and the plurality of signal lines so that one photosensor circuit is connected to one gate line and one signal line. Is done.

- a reset circuit RS1, RS2, RS3,. . . RSn there are a plurality of reset circuits RS1, RS2, RS3,. . . RSn), a reset control circuit RSTL, a gate line driving circuit GD, and a reading circuit RA.

- a plurality of reset circuits (RS1, RS2, RS3,..., RSn) are provided corresponding to each column.

- the reset circuit RS1 is connected to the signal line Sig1

- the reset circuit RS2 is connected to the signal line Sig2

- the reset circuit RS3 is connected to the signal line Sig3.

- other reset circuits are connected to corresponding signal lines.

- a reset signal RST output from the reset control circuit RSTL is also input to the plurality of reset circuits (RS1, RS2, RS3,..., RSn) via a wiring.

- the gate line driving circuit GD is connected to m gate lines G (G1, G2, G3,..., Gm), for example, m gate lines G (G1, G2, G3,..., Gm). ) Has a function of setting a desired one gate line to a selection level.

- Read circuit RA is connected to n signal lines S (Sig1, Sig2, Sig3, ..., Sign). For example, in the read operation, when the gate line driving circuit GD sets one gate line to the selection level, a plurality of photosensor circuits connected to the gate line set to the selection level are selected. Then, the charges stored in the capacitive elements in the selected plurality of photosensor circuits are input as read data to the read circuit RA via the n signal lines.

- the read circuit RA can have an analog-digital conversion circuit function for converting an analog signal into a digital signal, for example. Thereby, an analog signal such as the amount of electric charge read from the capacitive element of the photosensor circuit can be converted into a digital signal and transmitted to, for example, a host device.

- a control circuit SVGL that generates the first gate control signal SVG and a control circuit SVSL that generates the first source control signal SVS are also provided in the area around the area where the array unit ARR is provided.

- a control circuit DCHL for generating the second gate control signal DCH and a control circuit VR1L for generating the second source control signal VR1 are provided.

- FIG. 8 is a timing diagram illustrating an operation example of the optical sensor device 1 according to the embodiment.

- the timing diagram of FIG. 8 shows one sensor sequence.

- One sensor sequence includes a sensor reset period SRP, a capacity reset period CRP, an exposure period EXP, and a readout period RAP.

- Such a sensor sequence is performed, for example, continuously or a predetermined number of times in a desired period to perform touch detection or fingerprint detection.

- the sensor reset period SRP is a period in which the optical response of the light receiving transistor 101 is canceled by returning a reset current to the light receiving transistor 101 by the switching transistor 105 and is returned to the initial state.

- the photocurrent is instantaneously reset by making the bias of the gate electrode of the light receiving transistor 101 positive.

- the capacitance reset period CRP is a period in which the charge stored in the capacitor 103 is changed to a constant potential by the switching transistor 102 before the exposure period EXP.

- the exposure period EXP is a period in which the light receiving transistor 101 functions as a light receiving element and charges are stored in the capacitor 103 according to the amount of light irradiated by the incident light LIG. In the exposure period EXP, sufficient signal strength is ensured by making the bias of the gate electrode of the light receiving transistor 101 negative.

- the readout period RAP is a period in which a signal proportional to the amount of light irradiated by the incident light LIG is read from the charge newly stored in the capacitive element 103 by turning on the switching transistor 104 after the exposure period EXP. is there.

- the light intensity of the light irradiation of the incident light LIG on the light receiving transistor 101 can be quantitatively detected.

- the period t1 indicates a preparation period that is performed before the sensor reset period SRP.

- the first gate control signal SVG is set to a high level such as 10V

- the reset signal RST is set to a high level such as 10V.

- the second gate control signal DCH is set to a low level such as -5V

- the first source control signal SVS is set to a low level such as -1V

- the second source control signal VR1 is set to a high level such as 0V.

- All the gate electrodes G1-Gm are set to a low level (non-selection level) such as ⁇ 5V. In this state, the light receiving transistor 101 and the switching transistor 105 are on.

- the sensor reset period SRP After the period t1, the sensor reset period SRP is started.

- the sensor reset period SRP has a plurality of periods t2.

- a period t2 indicates a period in which each of the gate electrodes (G1-Gm) is sequentially shifted from a non-selection level such as ⁇ 5V to a selection level such as 10V and then transitions to a non-selection level. .

- the gate electrode G1 is set to the selection level, the optical response of the light receiving transistor 101 in each photosensor circuit (SC11, SC12,..., SC1n) in the first row connected to the gate electrode G1 is canceled, Returns to the initial state.

- the gate electrode G2 When the gate electrode G2 is set to the selection level, the optical response of the light receiving transistor 101 in each photosensor circuit (SC21, SC22,..., SC2n) in the second row connected to the gate electrode G2 is canceled, Returns to the initial state.

- a similar operation sequentially sets the other gate electrodes (G3-Gm) to the selection level, whereby the light receiving transistors 101 in all the optical sensor circuits of the sensor array ARR are returned to the initial state. Specifically, the switching transistor 105, the switching transistor 104, and the light receiving transistor 101 are turned on.

- the reset current is supplied from the wiring to which the second source control signal VR1 is supplied to the source / drain path of the switching transistor 105, the signal line (Sig1-Sign), the source / drain path of the switching transistor 104, and the light receiving transistor 101. Flows through the source / drain path to the wiring to which the first source control signal SVS is supplied.

- the period t3 indicates the period when the selection operation of all the gate electrodes (G3-Gm) is completed.

- the period t4 is provided after the period t3 and indicates a preparation period that is performed before the capacity reset period CRP.

- the first gate control signal SVG is changed from a high level such as 10V to a low level such as ⁇ 5V.

- the period t5 indicates a capacity reset period CRP provided after the period t4.

- the second gate control signal DCH is changed from a low level such as -5V to a high level such as 10V

- the second source control signal VR1 is changed from a high level such as 0V to a low level such as -1V.

- the first source control signal SVS is changed from a low level such as ⁇ 1V to a high level such as 5V.

- the switching transistor 102 is turned on, and the electric charge stored in the capacitor 103 is discharged or charged to change to a constant potential. To do.

- the exposure period EXP is provided after the period t5.

- the second gate control signal DCH is changed from a high level such as 10V to a low level such as -5V

- the second source control signal VR1 is changed from a low level such as -1V to a high level such as 0V.

- the light receiving transistor 101, the switching transistor 102, and the switching transistor 104 in all the optical sensor circuits are in an off state.

- each light receiving transistor 101 in the photosensor circuit (SC11, SC12,..., SCnm) functions as a light receiving element and is irradiated with the incident light LIG. Electric charge is stored in each capacitor 103 according to the amount of light.

- the end of the exposure period EXP is determined by transitioning the reset signal RST from a high level such as 10V to a low level such as ⁇ 5V. That is, the exposure period EXP can be determined by the time between the transition of the second gate control signal DCH to the low level and the transition of the reset signal RST to the low level. Therefore, the exposure period EXP can be varied by controlling this time.

- the period t6 is a preparation period before the reading period RAP.

- the reset signal RST is set to a low level.

- Read period RAP is started after period t6.

- the read period RAP has a plurality of periods t7.

- a period t7 indicates a period in which each of the gate electrodes (G1-Gm) is sequentially shifted from a non-selection level such as ⁇ 5V to a selection level such as 10V, and then transitions to a non-selection level. .

- the gate electrode G1 is set to the selection level, the charge newly stored in each capacitor 103 in each photosensor circuit (SC11, SC12,..., SC1n) connected to the gate electrode G1 in the first row.

- the switching transistor 104 is turned on, the signal is read out to the signal lines Sig1-Sign and input to the readout circuit RA.

- the readout circuit RA By sequentially setting all the gate electrodes (G2-Gm) to the selection level, the charges of all the capacitive elements 103 of all the optical sensor circuits (SC11, SC12,..., SCmn) in the array part ARR are read out by the readout circuit RA. Is input.

- the period t8 is provided after the end of the reading period RAP. After the period t8, the reset signal RST transitions from the low level to the high level, so that the state of each signal is set to the state before the start of the period t1.

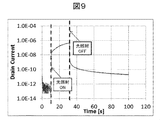

- FIG. 9 is a characteristic diagram for explaining the characteristics of the photocurrent of the oxide semiconductor transistor according to the comparative example.

- the vertical axis indicates the drain current

- the horizontal axis indicates time (seconds: S).

- FIG. 9 shows changes in drain current (photocurrent) when a simple two-terminal or oxide semiconductor transistor to which no reset bias is applied is irradiated with light for 10 to 30 seconds on the horizontal axis. .

- light irradiation ON when light irradiation ON), the drain current of the oxide semiconductor transistor increases.

- light irradiation is stopped (non-light irradiation OFF)

- the drain current of the oxide semiconductor transistor is increased.

- the drain current decreases very slowly. Note that the drain current (photocurrent) increased by the light irradiation does not easily decrease even after the light irradiation is stopped, and has a characteristic that it remains higher than the original current value before the light irradiation for one hour or longer.

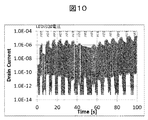

- FIG. 10 is a diagram for explaining the photocurrent of the oxide semiconductor transistor according to the comparative example.

- the vertical axis represents the drain current

- the horizontal axis represents time (second: S).

- the voltage applied to the LED element employed as the light emitting element is shown on the upper side of FIG. That is, FIG. 10 shows the drain current (photocurrent) of an oxide semiconductor transistor when a simple two-terminal or oxide semiconductor transistor to which no reset bias is applied is irradiated with light while changing the light emission amount of the LED element. Changes are shown.

- a simple two-terminal or oxide semiconductor transistor to which no reset bias is applied has a very slow light relaxation, so that a stable signal intensity cannot be obtained, and a quantitative optical sensor. It can be seen that it is difficult to form an element using an oxide semiconductor transistor.

- FIG. 11 is a diagram for explaining the photocurrent of the oxide semiconductor transistor according to the example.

- the vertical axis represents the drain current

- the horizontal axis represents time (seconds: S).

- the voltage applied to the LED element is shown as in FIG. 10. 11 illustrates a case where a three-terminal oxide semiconductor transistor 101 is used as an oxide semiconductor transistor, and a positive voltage is applied as a reset pulse to the gate terminal G1 of the oxide semiconductor transistor 101 at the start of sensing or at the end of sensing. A change in drain current (photocurrent) of the oxide semiconductor transistor 101 is shown. As understood from FIG.

- the refresh period can be significantly reduced to, for example, 100 msec or less. Therefore, a stable signal intensity can be obtained, and it becomes possible to form a quantitative photosensor element with an oxide semiconductor transistor.

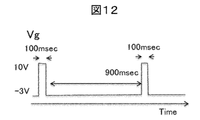

- FIG. 12 is a diagram exemplarily showing the gate bias potential (Vg) of the gate electrode of the oxide semiconductor transistor 101 when the reset pulse of FIG. 11 is applied.

- Vg gate bias potential

- a positive potential which is set to a high level (10 V) can be applied to the gate electrode of the oxide semiconductor transistor 101 as a reset pulse, for example, for a period of 100 msec.

- the interval between the reset pulses is illustratively 900 msec.

- the high-level period of the reset pulse in FIG. 12 can be regarded as one period t2 in the sensor reset period SRP shown in FIG.

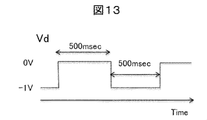

- FIG. 13 is a diagram exemplarily showing the drain bias potential (Vd) of the drain electrode of the oxide semiconductor transistor 101 when the reset pulse of FIG. 11 is applied.

- the drain electrode of the oxide semiconductor transistor 101 is set to a high level (0 V) for a period such as 500 msec, and is then set to a low level ( ⁇ 1 V) for a period such as 500 msec.

- the period in which the bias potential (Vd) in FIG. 13 is at the low level ( ⁇ 1V) can be regarded as the capacitance reset period CRP (period t5) shown in FIG.

- the light receiving transistor 101 is an oxide semiconductor element having three terminals (gate, source, and drain) using the oxide semiconductor layer 14b as a channel layer (active layer). Since the light receiving transistor 101 has a three-terminal structure, as shown in FIGS. 4 and 5, it is possible to use the value of the drain current (off current) in the off state of the light receiving transistor 101 to determine the presence or absence of light irradiation. I can do it. By utilizing the fact that the signal ratio of the off-state current of the light receiving transistor 101 in the presence or absence of light irradiation is large, it is possible to detect the presence or absence of light irradiation in a stable operation.

- the switching transistor 102 (104, 105) is an oxide semiconductor element having four terminals (gate, source, drain, and back gate) using the oxide semiconductor layer 14a as a channel layer (active layer).

- the oxide semiconductor layer 14a of the switching transistor 102 is configured not to be irradiated with the incident light LIG.

- the back gate electrode 17 has a function of blocking or blocking incident light LIG to the oxide semiconductor layer 14a.

- the switching transistor 102 (104, 105) may be a dual gate drive for driving the gate electrode 12a and the back gate electrode 17.

- the switching transistor 102 (104, 105) may have a configuration in which the back gate electrode 17 is connected to the source electrode 15a.

- the switching transistor 102 (104, 105) is not limited to the bottom gate type structure, and may have a top gate type structure.

- the optical sensor circuit includes a light receiving transistor 101, switching transistors 102 and 104, and a capacitive element 103.

- the light receiving transistor 101 has a gate connected to a wiring to which the first gate control signal SVG is supplied, a source connected to a wiring to which the first source control signal SVS is supplied, and a drain.

- the switching transistor 102 is connected to the gate connected to the wiring to which the second gate control signal DCH is supplied, the source connected to the wiring to which the second source control signal VR1 is supplied, and the drain of the light receiving transistor 101. And a drain.

- Capacitance element 103 has a first terminal connected to the drain of light-receiving transistor 101 and a second terminal connected to the source of switching transistor 102.

- the switching transistor 104 has a gate connected to the gate line G1, a source connected to the signal line Sig1, and a drain connected to the first terminal of the capacitor 103.

- the charge stored in the capacitor 103 is read out to the signal line Sig1 through the source / drain path of the switching transistor 104 which is turned on when the gate line G1 is set to the selection level.

- the reset circuit RS is connected to the photosensor circuit.

- the reset circuit RS includes a switching transistor 105.

- the switching transistor 105 has a gate connected to the wiring to which the reset signal RST is supplied, a source connected to the wiring to which the second source control signal VR1 is supplied, and a drain connected to the signal line Sig1. .

- one sensor sequence includes a sensor reset period SRP, a capacitance reset period CRP, an exposure period EXP, and a readout period RAP.

- the sensor reset period SRP is a period in which the optical response of the light receiving transistor 101 is canceled by returning a reset current to the light receiving transistor 101 by the switching transistor 105 and is returned to the initial state.

- the capacitance reset period CRP is a period in which the charge stored in the capacitor 103 is changed (initialized) to a constant potential by the switching transistor 102 before the exposure period EXP.

- the exposure period EXP is a period in which the light receiving transistor 101 functions as a light receiving element, and charges are stored in the capacitive element 103 according to the amount of light irradiated by the incident light LIG.

- the readout period RAP is a period in which a signal proportional to the amount of light irradiated by the incident light LIG is read from the charge newly stored in the capacitive element 103 by turning on the switching transistor 104 after the exposure period EXP. is there.

- the optical sensor device 1 capable of performing stable operation can be provided.

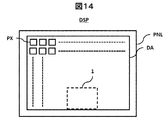

- FIG. 14 is a plan view conceptually showing the display device according to the application example 1.

- FIG. The display device DSP according to the application example 1 illustrates a configuration example when the optical sensor device 1 according to the embodiment is used as a fingerprint sensor.

- the optical sensor device 1 is attached to a desired region on the display panel PNL of the display device DSP.

- This area is, for example, the area of the display panel PNL assigned to the fingerprint detection area.

- the display panel PNL has a display area DA, and the display area DA has a plurality of display pixels PX arranged in a matrix.

- the display panel PNL can be a liquid crystal display panel, for example. In this case, a liquid crystal display pixel can be used for each of the plurality of display pixels PX.

- FIG. 15 is a plan view conceptually showing a display device according to application example 2.

- FIG. The display device DSP1 according to the application example 2 illustrates a configuration example in the case where the optical sensor device 1 of the embodiment is used as a touch sensor.

- the optical sensor device 1 is attached to the display area DA of the display panel PNL of the display device DSP.

- the display panel PNL includes a display area DA

- the display area DA includes a plurality of display pixels PX arranged in a matrix.

- the optical sensor device 1 of the application example 2 is not limited to a touch sensor, and can also be used as a fingerprint sensor.

- FIG. 16 is a plan view conceptually showing a display device according to a modification. 14 and 15 show a configuration example in which the optical sensor device 1 of the embodiment is bonded to the display area DA of the display panel PNL.

- the display device DSP2 according to the modification both the display pixel PX and the photosensor circuit SC are provided in the display area DA of the display panel PNL.

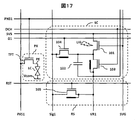

- FIG. 17 is a circuit diagram showing a configuration example of the display pixel PX and the photosensor circuit SC that can be employed in the display device according to the modification.

- FIG. 17 exemplarily shows a configuration in which the photosensor circuit SC of FIG. 6 and the display pixel PX are combined.

- the configuration of the photosensor circuit SC is the same as that shown in FIG.

- the display pixel PX includes one thin film transistor TFT as a switching element.

- the thin film transistor TFT has a gate connected to a pixel gate line PXG1 that is a scanning line, one source / drain connected to a pixel source line S1 that is a signal line, and the other source / drain connected to a pixel electrode PE.

- the display pixel PX is provided with a common electrode Vcom that applies a common potential Vcom to all the display pixels PX, and a liquid crystal layer LC is provided between the pixel electrode PE and the common electrode Vcom.

- the thin film transistor TFT is turned on / off based on a drive signal supplied via the pixel gate line PXG1, and a pixel voltage is applied to the pixel electrode PE based on a display signal supplied from the pixel source line S1 when the thin film transistor TFT is on.

- the liquid crystal layer LC is driven by the electric field between the pixel electrode PE and the common electrode Vcom.

- FIG. 17 shows a configuration in which one photosensor circuit SC is provided for one display pixel PX, but is not limited thereto.

- One photosensor circuit SC may be provided for a plurality of display pixels PX.

- one photosensor circuit SC may be provided for five display pixels PX.

- a liquid crystal display device is disclosed as an example of a display device.

- the liquid crystal display device can be used for various devices such as a smartphone, a tablet terminal, a mobile phone terminal, a personal computer, a television receiver, an in-vehicle device, a game machine, a digital camera, and a video camera.

- main structures disclosed in the application examples and the modification examples include a self-luminous display device (OLED) having an organic electroluminescence display element and the like, an electronic paper display device having an electrophoretic element and the like, MEMS (Micro

- OLED self-luminous display device

- MEMS Micro

- the present invention can also be applied to a display device applying Electro (Mechanical Systems) or a display device applying electrochromism.

- the light-receiving transistor 101 using an oxide semiconductor layer has a very low off-current, and therefore can keep a very low off-current without light irradiation. Therefore, the exposure time (exposure period EXP) and readout time (readout period RAP) can be freely changed according to the purpose and irradiation light (global shutter). For example, when an OLED or liquid crystal display device is combined, the optical sensor device 1 can be driven or the optical sensor device 1 can be operated independently between display operations of the OLED or liquid crystal display device. . In the case where the reading time (reading period RAP) is shortened, a polycrystalline low-temperature polysilicon (LTPS) thin film transistor (TFT) can be used for the reading transistor 104 and the reset transistor 105.

- LTPS polycrystalline low-temperature polysilicon

- TFT thin film transistor

- Various inventions can be formed by appropriately combining a plurality of constituent elements disclosed in the above embodiment. For example, some components may be deleted from all the components shown in the embodiment. Furthermore, you may combine suitably the component covering different embodiment.

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Power Engineering (AREA)

- General Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Electromagnetism (AREA)

- Chemical & Material Sciences (AREA)

- Human Computer Interaction (AREA)

- Nonlinear Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Multimedia (AREA)

- Composite Materials (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Thin Film Transistor (AREA)

- Light Receiving Elements (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Liquid Crystal (AREA)

Abstract

本開示の課題は、安定した動作を行うことが可能な、酸化物半導体トランジスタを用いた光センサー回路を提供することにある。光センサー回路は、受光トランジスタと、第1スイッチングトランジスタと、第2スイッチングトランジスタと、容量素子と、を含む。受光トランジスタは、第1配線に接続されたゲートと、第2配線に接続されたソースと、ドレインと、を含む。第1スイッチングトランジスタは、第3配線に接続されたゲートと、第4配線に接続されたソースと、受光トランジスタのドレインに接続されたドレインと、を有する。容量素子は、受光トランジスタのドレインに接続された第1端子と、第1スイッチングトランジスタのソースに接続された第2端子と、を含む。第2スイッチングトランジスタは、ゲート線に接続されたゲートと、信号線に接続されたソースと、容量素子の第1端子に接続されたドレインと、を含む。受光トランジスタ、第1スイッチングトランジスタ、および、第2スイッチングトランジスタのおのおのは、チャンネル層として酸化物半導体層を含む。

Description

本発明は光センサー回路に関し、特に、酸化物半導体トランジスタを用いた光センサー回路、光センサー装置および表示装置に適用可能である。

酸化物半導体トランジスタを用いた光センシング回路や光センサー素子として、特開2011-243950号公報(特許文献1)や、特開2009-182194号(特許文献2)が提案されている。

酸化物半導体トランジスタは、光照射をしながら負バイアスが印加されると閾値電圧が大きく変動する光負バイアス劣化という劣化モードがある。また、酸化物半導体トランジスタに光照射した場合、光の照射を止めても、ドレイン電流の減少が極めて遅いという特性を有する。そのため、酸化物半導体トランジスタを光センサー素子に用いることは難しいという課題がある。

本発明の目的は、安定した動作を行うことが可能な、酸化物半導体トランジスタを用いた光センサー回路を提供することにある。

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

本発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

すなわち、光センサー回路は、受光トランジスタと、第1スイッチングトランジスタと、第2スイッチングトランジスタと、容量素子と、を含む。前記受光トランジスタは、第1配線に接続されたゲートと、第2配線に接続されたソースと、ドレインと、を含む。前記第1スイッチングトランジスタは、第3配線に接続されたゲートと、第4配線に接続されたソースと、前記受光トランジスタの前記ドレインに接続されたドレインと、を含む。前記容量素子は、前記受光トランジスタの前記ドレインに接続された第1端子と、前記第1スイッチングトランジスタの前記ソースに接続された第2端子と、を含む。前記第2スイッチングトランジスタは、ゲート線に接続されたゲートと、信号線に接続されたソースと、前記容量素子の前記第1端子に接続されたドレインと、を含む。前記受光トランジスタ、第1スイッチングトランジスタ、および、前記第2スイッチングトランジスタのおのおのは、チャンネル層として酸化物半導体層を含む。

また、光センサー装置は、複数のゲート線と、複数の信号線と、1つの光センサー回路が1つのゲート線と1つの信号線とに接続されるように、前記複数のゲート線と前記複数の信号線とに接続された複数の光センサー回路と、を含む。前記複数の光センサー回路のおのおのは、受光トランジスタと、第1スイッチングトランジスタと、第2スイッチングトランジスタと、容量素子と、を含む。前記受光トランジスタは、第1配線に接続されたゲートと、第2配線に接続されたソースと、ドレインと、を含む。前記第1スイッチングトランジスタは、第3配線に接続されたゲートと、第4配線に接続されたソースと、前記受光トランジスタの前記ドレインに接続されたドレインと、を含む。前記容量素子は、前記受光トランジスタの前記ドレインに接続された第1端子と、前記第1スイッチングトランジスタの前記ソースに接続された第2端子と、を有する。前記第2スイッチングトランジスタは、対応するゲート線に接続されたゲートと、対応する信号線に接続されたソースと、前記容量素子の前記第1端子に接続されたドレインと、を含む。前記受光トランジスタ、第1スイッチングトランジスタ、および、前記第2スイッチングトランジスタのおのおのは、チャンネル層として酸化物半導体層を含む。

また、表示装置は、表示領域を有する表示パネルを有する。前記表示領域は、表示画素と、光センサー回路と、を含む。前記光センサー回路は、受光トランジスタと、第1スイッチングトランジスタと、第2スイッチングトランジスタと、容量素子と、を含む。前記受光トランジスタは、第1配線に接続されたゲートと、第2配線に接続されたソースと、ドレインと、を含む。前記第1スイッチングトランジスタは、第3配線に接続されたゲートと、第4配線に接続されたソースと、前記受光トランジスタの前記ドレインに接続されたドレインと、を含む。前記容量素子は、前記受光トランジスタの前記ドレインに接続された第1端子と、前記第1スイッチングトランジスタの前記ソースに接続された第2端子と、を含む。前記第2スイッチングトランジスタは、ゲート線に接続されたゲートと、信号線に接続されたソースと、前記容量素子の前記第1端子に接続されたドレインと、を含む。前記受光トランジスタ、第1スイッチングトランジスタ、および、前記第2スイッチングトランジスタのおのおのは、チャンネル層として酸化物半導体層を含む。

以下に、本発明の各実施の形態について、図面を参照しつつ説明する。

なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。

また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

(光センサー素子の素子構造)

図1は、実施例に係る光センサー装置に用いられる酸化物半導体トランジスタの例示的な構造を概略的に説明する断面図である。図2は、図1の受光トランジスタ101の例示的な構造を概略的に説明する断面図である。図3は、図1のスイッチングトランジスタ102の例示的な構造を概略的に説明する断面図である。

図1は、実施例に係る光センサー装置に用いられる酸化物半導体トランジスタの例示的な構造を概略的に説明する断面図である。図2は、図1の受光トランジスタ101の例示的な構造を概略的に説明する断面図である。図3は、図1のスイッチングトランジスタ102の例示的な構造を概略的に説明する断面図である。

実施例に係る光センサー装置1は、複数の光センサー回路SCを含む。図1には、各光センサー回路SCに利用される1つの受光トランジスタ101と、1つのスイッチングトランジスタ102と、容量素子103と、が例示的に描かれる。受光トランジスタ101およびスイッチングトランジスタ102は、共に、酸化物半導体トランジスタを利用して構成される。

受光トランジスタ101は、図1および図2に示されるように、ゲート電極12bと、酸化物半導体層14bと、ドレイン電極15bと、ソース電極15cと、を含む。すなわち、受光トランジスタ101は、酸化物半導体層14bの下部にゲート電極12bが設けられた下部ゲート構造、すなわち、ボトムゲート型の3端子(ゲート、ソース、および、ドレイン)の素子とされており、ボトムゲート・トップコンタクト構造(逆スタガ構造という)を有する。

スイッチングトランジスタ102は、図1および図3に示されるように、ゲート電極12aと、酸化物半導体14aと、ソース電極15aおよびドレイン電極15b、および、バックゲート電極17と、を含む。すなわち、スイッチングトランジスタ102は、ボトムゲート型の4端子(ゲート、ソース、ドレイン、および、バックゲート)の素子とされており、逆スタガ構造にバックゲート電極17を設けた構成を有する。例えば、スイッチングトランジスタ102は、ゲート電極12aとバックゲート電極17とを駆動するデュアルゲート駆動としても良い。また、スイッチングトランジスタ102は、バックゲート電極17をソース電極15aに接続した構成でも良い。スイッチングトランジスタ102は、ボトムゲート型の構成に限定されるものではなく、上部ゲート型構造の構成でもよい。なお、上部ゲート型構造とは、酸化物半導体14aの上方に、ゲート電極12aを設けた構成である。

容量素子103は、ゲート電極12cと、ソースまたはドレイン電極15dと、ゲート絶縁膜13とにより構成される。容量素子103は、この構成に限らず、ゲート電極12cと、酸化物半導体層14a、14bと同時に設けられた酸化物半導体層と、ゲート絶縁膜13とで構成することができる。また、容量素子103は、ソースまたはドレイン電極15dと、バックゲート電極17と同時に設けられた金属層と、絶縁層16で構成することができる。

酸化物半導体層14a、14bは、酸化物半導体トランジスタ(101、102)のチャンネル層(活性層)を構成しており、その材料は、ZnO系の材料などの酸化物半導体材料を含むことができる。ZnO系の材料は、例えば、ZnOを含むことができ、または、Hf、Y、Ta、Zr、Ti、Cu、Ni、Cr、In、Ga、Al、Sn及びMgから選択された少なくとも一つの材料がZnOに含まれている混合物または化合物を含むこともできる。例えば、かかるZnO系の材料は、ZnO、TaZnO、InZnO(IZO)やGaInZnO(Gallium Indium Zinc Oxide;GIZO)を含むことができる。

このような酸化物半導体トランジスタは、入射光LIGの光量によってしきい電圧及びドレイン電流が変わる特性があるため、受光トランジスタ101として利用することが可能である。なお、スイッチングトランジスタ102においては、入射光LIGの光量によってしきい電圧及びドレイン電流が変わる特性は不要であるため、図1および図3に示されるように、酸化物半導体層14aの下方にはゲート電極12aが設けられ、また、酸化物半導体層14aの上方にはがバックゲート電極17が設けられる。これにより、スイッチングトランジスタ102の酸化物半導体層14aには、入射光LIGが照射されない様な構成にされている。つまり、バックゲート電極17は、酸化物半導体層14aへの入射光LIGを遮光ないし阻止する機能を有する。

図1を参照すれば、光センサー装置1は、基板10と、基板10上に全体的に設けられた絶縁層11と、絶縁層11上に部分的に設けられたゲート電極12a、12b、12cと、ゲート電極12a、12b、12cの側面および上面を覆うように、絶縁層11及びゲート電極12a、12b、12c上に設けられたゲート絶縁膜13と、を有する。光センサー装置1は、さらに、ゲート絶縁膜13上に部分的に設けられた酸化物半導体層14a、14bと、酸化物半導体層14a、14bの両側を覆うように設けられたソース電極およびドレイン電極15a、15b、15c、15dと、ソース電極およびドレイン電極15a、15b、15c、15d及び酸化物半導体層14a、14bを全体的に覆うように設けられた透明絶縁層16と、を有する。光センサー装置1は、さらに、透明絶縁層16上に、酸化物半導体層14aを覆う様に部分的に設けられたバックゲート電極17と、バックゲート電極17上と透明絶縁層16上とを全体的に覆うように設けられた平坦化膜としての透明絶縁層18と、透明絶縁層18上に部分的に設けられた配線層19a、19bと、配線層19a、19b上と透明絶縁層18上とを全体的に覆うように設けられた保護膜としての透明絶縁層20と、を有する。なお、配線層19aはバックゲート電極17にビア電極を介し接続され、配線層19bはソース電極15cにビア電極を介し接続されている。

基板10は、ガラス、シリコン、樹脂基板などの一般的な基板材料を使用できる。絶縁層11、ゲート絶縁膜13、透明絶縁層16、透明絶縁層18、透明絶縁層20は、シリコン酸化膜の材料を使用できる。絶縁層11、ゲート絶縁膜13、透明絶縁層16、透明絶縁層18、透明絶縁層20は、CVD法により成膜することが出来る。ゲート電極12a、12b、12c、ソース電極およびドレイン電極15a、15b、15c、15d、バックゲート電極17、配線層19a、19bは、導電性金属または導電性金属酸化物を使用できる。酸化物半導体層14a、14bは、スパッタリング法により、成膜することが可能である。

たとえば、光センサー装置1がディスプレイパネル上に付着される光タッチパネルまたは指紋センサーに使われる場合、ゲート電極12a、12b、12c、ソース電極およびドレイン電極15a、15b、15c、15dは、ITO等の透明導電性材料で構成できる。ただし、図1に示される様に、光センサー装置1の上面から入射光LIGが照射されるような上面照射方式の場合、バックゲート電極17は酸化物半導体層14aへの入射光LIGの照射を遮光または阻止する役割を有するため、バックゲート電極17は不透明な導電性材料で構成するのが良い。一方、光センサー装置1の裏面、すなわち、基板10側から、入射光LIGが照射されるような裏面照射方式の場合、ゲート電極12cは酸化物半導体層14aへの入射光LIGの照射を遮光または阻止する役割を有するため、ゲート電極12cは不透明な導電性材料で構成するのが良い。

図4は、光照射の無い場合の受光トランジスタ101のドレイン電流の特性を示す図である。図5は、光照射の有る場合の受光トランジスタ101のドレイン電流の特性を示す図である。図4および図5において、縦軸は受光トランジスタ101のドレイン電流の値を示し、横軸は受光トランジスタ101のゲート電圧を示している。また、点線で示される特性は、ドレイン電圧が1Vの場合を示し、実線で示される特性は、ドレイン電圧が10Vの場合を示している。

図4から理解されるように、光照射の無い場合において、受光トランジスタ101のゲート電位が閾値以下の領域、すなわち、受光トランジスタ101がオフ状態(非導通)とされるオフ領域では、ドレイン電流は測定下限以下の様な極めて小さい値となっている。これに対し、図5から理解されるように、光照射の有る場合において、受光トランジスタ101のゲート電位が閾値以下の領域、すなわち、受光トランジスタ101がオフ状態(非導通)とされるオフ領域では、ドレイン電流は、図4と比較して、大幅に上昇する。

本発明の受光トランジスタ101は、前述の様に3端子構造であるので、図4および図5に示されるように、受光トランジスタ101のオフ状態のドレイン電流(ここではオフ電流ともいう)の値を光照射の有無の判定に利用することが出来る。これは、光照射の有無における受光トランジスタ101のオフ電流の信号比が大きいことを利用することで、光照射の有無の検出を安定した動作で行うことが可能である。

前述の様に、酸化物半導体トランジスタは、光照射をしながら負バイアスが印加されると閾値電圧が大きく変動する光負バイアス劣化という劣化モードがある。特に、光感度を上げると、光劣化が加速してしまうというトレードオフは問題となっている。一方、酸化物半導体トランジスタはオフ電流が非常に低いため、受光トランジスタ101を3端子構造とし、受光トランジスタ101をオフ領域で動作させることで、光照射の有無におけるオフ電流の信号比を十分にとることができる。

また、受光トランジスタ101とスイッチングトランジスタ102とのゲート位置およびバックゲート電極を変えることにより、二つの素子101、102の間の光照射量が制御可能である。これにより、光照射の有無の検出を安定した動作で行うことが可能である。

また、酸化物半導体トランジスタの光劣化は、閾値を負方向に動かすため、酸化物半導体トランジスタのオフ時にゲート電極へ印加される負電位を大きくとることで、閾値のマイナス変動に対しても影響を受けにくくすることが可能である。

次に、図1-図3で説明された受光トランジスタ101、スイッチングトランジスタ102および容量素子103を利用した光センサー回路の例示的な回路構成例を説明する。

(光センサー回路の回路構成)

図6は、実施例に係る光センサー回路の例示的な構成例を説明する回路図である。

図6は、実施例に係る光センサー回路の例示的な構成例を説明する回路図である。

光センサー回路SCは、受光素子である受光トランジスタ101と、スイッチングトランジスタ102、スイッチングトランジスタ104と、容量素子103と、を含む。また、図6には、光センサー回路SCに接続されたリセット回路RSが描かれる。リセット回路RSは、スイッチングトランジスタ105を含む。

ここで、スイッチングトランジスタ104、105のおのおのは、図1や図3で説明されたスイッチングトランジスタ102と同様に、バックゲート電極17を有する酸化物半導体トランジスタで構成される。図6において、スイッチングトランジスタ102、104、105のおのおは、そのバックゲート電極17がそのソース電極に接続された構成を有する。スイッチングトランジスタ102は第1スイッチングトランジスタと、スイッチングトランジスタ104は第2スイッチングトランジスタと、スイッチングトランジスタ105は第3スイッチングトランジスタと、言う事がある。

受光トランジスタ101は、第1ゲート制御信号SVGが供給される配線(第1配線)L1に接続されたゲートと、第1ソース制御信号SVSが供給される配線に接続(第2配線)L2されたソースと、ドレインと、を有する。スイッチングトランジスタ102は、第2ゲート制御信号DCHが供給される配線(第3配線)L3に接続されたゲートと、第2ソース制御信号VR1が供給される配線(第4配線)L4に接続されたソースと、受光トランジスタ101のドレインに接続されたドレインと、を有する。容量素子103は、受光トランジスタ101のドレインに接続された第1端子と、スイッチングトランジスタ102のソースに接続された第2端子と、を有する。スイッチングトランジスタ104は、ゲート線G1に接続されたゲートと、信号線Sig1に接続されたソースと、容量素子103の第1端子に接続されたドレインと、を有する。

容量素子103は、入射光LIGが受光トランジスタ101へ照射された時、照射された光量に応じた電荷を蓄える機能を有する。容量素子103に蓄えられた電荷は、ゲート線G1が選択レベルとされることで、オン状態とされたスイッチングトランジスタ104のソース・ドレイン経路を介して、信号線Sig1へ読み出される。

リセット回路RSは、スイッチングトランジスタ105を有する。スイッチングトランジスタ105は、リセット信号RSTが供給される配線(第5配線)L5に接続されたゲートと、第2ソース制御信号VR1が供給される配線L4に接続されたソースと、信号線Sig1に接続されたドレインと、を有する。なお、第2ソース制御信号VR1が供給される配線L4は、複数の光センサー回路SCが設けられた場合、各光センサー回路SCの容量素子103の第2端子に接続される。

次に、図6で説明された光センサー回路SCおよびリセット回路RSを複数含む光センサー装置1の例示的な全体構成を説明する。

(光センサー装置の全体構成)

図7は、実施例に係る光センサー装置の例示的な全体構成を示すブロック図である。なお、図面の複雑さを避けるため、図7には、図6に示される受光トランジスタ101、スイッチングトランジスタ102、104、容量素子103、および、ゲート線G、信号線S、以外の複数の配線(L1-L4)は、記載されていない。

(光センサー装置の全体構成)

図7は、実施例に係る光センサー装置の例示的な全体構成を示すブロック図である。なお、図面の複雑さを避けるため、図7には、図6に示される受光トランジスタ101、スイッチングトランジスタ102、104、容量素子103、および、ゲート線G、信号線S、以外の複数の配線(L1-L4)は、記載されていない。

光センサー装置1は、例えば、矩形形状の光センサーパネルLPNLの上に設けられる。光センサーパネルLPNL上には、アレイ部ARRが設けられており、アレイ部ARRには、例えば、m行n列の様な行列状に配置された複数の光センサー回路(SC11、SC12、...、SCmn)が設けられる。

m行に対応して、m本のゲート線G(G1、G2、G3、...、Gm)が設けられ、n列に対応してn本の信号線S(Sig1、Sig2、Sig3、...、Sign)が設けられる。

1行目に配置された光センサー回路SC11、SC12、SC13、...、SC1nには、ゲート線G1が接続され、2行目に配置された光センサー回路SC21、SC22、SC23、...、SC2nには、ゲート線G2が接続され、3行目に配置された光センサー回路SC31、SC32、SC33、...、SC3nには、ゲート線G3が接続される。同様にして、他のゲート線には、対応する行に配置された複数の光センサー回路が接続される。

一方、1列目に配置された光センサー回路SC11、SC21、SC31、...、SCm1には、信号線Sig1が接続され、2列目に配置された光センサー回路SC12、SC22、SC32、...、SCm2には、信号線Sig2が接続され、3列目に配置された光センサー回路SC13、SC23、SC33、...、SCm3には、信号線Sig3が接続される。同様にして、他の信号線には、対応する列に配置された複数の光センサー回路が接続される。

以上の様にして、複数の光センサー回路は、1つの光センサー回路が1本のゲート線と1本の信号線とに接続される様に、複数のゲート線と複数の信号線とに接続される。

光センサーパネルLPNL上において、アレイ部ARRの設けられた領域の周辺の領域には、複数のリセット回路RS1、RS2、RS3、...、RSn)と、リセット制御回路RSTLと、ゲート線駆動回路GDと、読み出し回路RAと、が設けられる。

複数のリセット回路(RS1、RS2、RS3、...、RSn)は、各列に対応して設けられる。リセット回路RS1は信号線Sig1に接続され、リセット回路RS2は信号線Sig2に接続され、リセット回路RS3は信号線Sig3に接続される。同様にして、他のリセット回路は、対応する信号線に接続される。複数のリセット回路(RS1、RS2、RS3、...、RSn)には、また、リセット制御回路RSTLから出力されるリセット信号RSTが配線を介して入力される。

ゲート線駆動回路GDは、m本のゲート線G(G1、G2、G3、...、Gm)に接続され、例えば、m本のゲート線G(G1、G2、G3、...、Gm)の内の所望の1本のゲート線を選択レベルとする機能を有する。

読み出し回路RAは、n本の信号線S(Sig1、Sig2、Sig3、...、Sign)に接続される。例えば、読み出し動作において、ゲート線駆動回路GDが1本のゲート線を選択レベルとした場合、選択レベルとされたゲート線に接続される複数の光センサー回路が選択される。そして、選択された複数の光センサー回路内の容量素子に蓄えられた電荷が、読み出しデータとして、n本の信号線を介して、読み出し回路RAへ入力されることになる。読み出し回路RAは、例えば、アナログ信号をデジタル信号へ変換するアナログデジタル変換回路機能を有することが出来る。これにより、光センサー回路の容量素子から読み出された電荷の量の様なアナログ信号を、デジタル信号へ変換して、例えば、ホスト装置へ送信することが出来る。

光センサーパネルLPNL上において、アレイ部ARRの設けられた領域の周辺の領域には、また、第1ゲート制御信号SVGを生成する制御回路SVGLと、第1ソース制御信号SVSを生成する制御回路SVSLと、第2ゲート制御信号DCHを生成する制御回路DCHLと、第2ソース制御信号VR1を生成する制御回路VR1Lと、が設けられる。

次に、図7で説明された光センサー装置1の動作を説明する。

(光センサー装置の駆動方法)

図8は、実施例に係る光センサー装置1の動作例を説明するタイミング図である。図8のタイミング図は、1回のセンサーシーケンスを示している。1回のセンサーシーケンスは、センサーリセット期間SRPと、容量リセット期間CRPと、露光期間EXPと、読み出し期間RAPと、を含む。このようなセンサーシーケンスが、例えば、連続的に、または、所望の期間に所定回数行われて、タッチ検出または指紋検出が行われる。

図8は、実施例に係る光センサー装置1の動作例を説明するタイミング図である。図8のタイミング図は、1回のセンサーシーケンスを示している。1回のセンサーシーケンスは、センサーリセット期間SRPと、容量リセット期間CRPと、露光期間EXPと、読み出し期間RAPと、を含む。このようなセンサーシーケンスが、例えば、連続的に、または、所望の期間に所定回数行われて、タッチ検出または指紋検出が行われる。

センサーリセット期間SRPは、スイッチングトランジスタ105により、受光トランジスタ101にリセット電流を流すことで、受光トランジスタ101の光応答をキャンセルさせ、初期状態に戻す期間である。センサーリセット期間SRPにおいて、受光トランジスタ101のゲート電極のバイアスをプラスにすることで、瞬間的に光電流をリセットさせる。

容量リセット期間CRPは、露光期間EXPの前において、容量素子103に蓄えられた電荷を、スイッチングトランジスタ102により、一定の電位に変化させる期間である。

露光期間EXPは、受光トランジスタ101を受光素子として機能させ、入射光LIGにより照射された光量に応じて、容量素子103に電荷を蓄える期間である。露光期間EXPには、受光トランジスタ101のゲート電極のバイアスをマイナスにすることで十分な信号強度を確保する。

読み出し期間RAPは、露光期間EXPの後に、スイッチングトランジスタ104をオン状態とすることにより、容量素子103に新たに蓄えられた電荷から、入射光LIGにより照射された光量に比例する信号を読み出す期間である。

以上により、受光トランジスタ101に対する入射光LIGの光照射の光強度を、定量的に検出することが可能になる。

図8を参照して、1回のセンサーシーケンスを説明する。

期間t1は、センサーリセット期間SRPの前に行われる準備期間を示している。期間t1において、第1ゲート制御信号SVGは10Vの様なハイレベルとされ、リセット信号RSTは10Vの様なハイレベルとされる。また、第2ゲート制御信号DCHは-5Vの様なロウレベルとされ、第1ソース制御信号SVSは-1Vの様なロウレベルにされ、第2ソース制御信号VR1は0Vの様なハイレベルにされ、すべてのゲート電極G1-Gmは-5Vの様なロウレベル(非選択レベル)にされる。この状態では、受光トランジスタ101とスイッチングトランジスタ105が、オン状態となっている。

期間t1の後、センサーリセット期間SRPが開始される。センサーリセット期間SRPは、複数の期間t2を有している。期間t2は、ゲート電極(G1-Gm)のおのおのが、順次、-5Vの様な非選択レベルから10Vの様な選択レベルへ遷移され、その後、非選択レベルへ遷移される期間を示している。ゲート電極G1が選択レベルとされると、ゲート電極G1に接続された1行目の各光センサー回路(SC11、SC12、...、SC1n)内の受光トランジスタ101の光応答がキャンセルされて、初期状態に戻される。ゲート電極G2が選択レベルとされると、ゲート電極G2に接続された2行目の各光センサー回路(SC21、SC22、...、SC2n)内の受光トランジスタ101の光応答がキャンセルされて、初期状態に戻される。同様な動作が、他のゲート電極(G3-Gm)を順次選択レベルとすることで、センサーアレイARRの全ての光センサー回路内の受光トランジスタ101が初期状態に戻される。具体的には、スイッチングトランジスタ105、スイッチングトランジスタ104、および受光トランジスタ101がオン状態されている。したがって、リセット電流は、第2ソース制御信号VR1の供給される配線から、スイッチングトランジスタ105のソース・ドレイン経路、信号線(Sig1-Sign)、スイッチングトランジスタ104のソース・ドレイン経路、および、受光トランジスタ101のソース・ドレイン経路を介して、第1ソース制御信号SVSの供給される配線へ流れる。

期間t3は、すべてのゲート電極(G3-Gm)の選択動作が終了した期間を示している。

期間t4は、期間t3の後に設けられており、容量リセット期間CRPの前に行われる準備期間を示している。期間t4において、第1ゲート制御信号SVGは、10Vの様なハイレベルから-5Vの様なロウレベルとされる。

期間t5は、期間t4の後に設けられた容量リセット期間CRPを示している。期間t5において、第2ゲート制御信号DCHは-5Vの様なロウレベルから10Vの様なハイレベルにされ、第2ソース制御信号VR1は0Vの様なハイレベルから-1Vの様なロウレベルにされる。また、第1ソース制御信号SVSは-1Vの様なロウレベルから5Vの様なハイレベルにされる。これにより、各光センサー回路(SC11、SC12、...、SCnm)において、スイッチングトランジスタ102がオン状態にされ、容量素子103に蓄えられた電荷が、放電または充電されて、一定の電位に変化する。

露光期間EXPは、期間t5の後に設けられる。露光期間EXPは、第2ゲート制御信号DCHを10Vの様なハイレベルから-5Vの様なロウレベルへ遷移させ、また、第2ソース制御信号VR1を-1Vの様なロウレベルから0Vの様なハイレベルへ遷移させることにより開始される。この時、すべての光センサー回路(SC11、SC12、...、SCnm)内の受光トランジスタ101、スイッチングトランジスタ102、スイッチングトランジスタ104は、オフ状態とされている。この状態で、アレイ部ARRに入射光LIGが照射されると、光センサー回路(SC11、SC12、...、SCnm)内の各受光トランジスタ101は受光素子として機能し、入射光LIGにより照射された光量に応じて、各容量素子103に電荷が蓄えられることになる。露光期間EXPの終了は、リセット信号RSTを10Vの様なハイレベルから-5Vの様なロウレベルへ遷移させることによって決定される。すなわち、露光期間EXPは、第2ゲート制御信号DCHのロウレベルへの遷移とリセット信号RSTのロウレベルへの遷移の間の時間で決めることが出来る。したがって、露光期間EXPは、この時間を制御することで、露光期間EXPの期間を可変に出来る。

期間t6は、読み出し期間RAPの前の準備期間である。期間t6において、リセット信号RSTがロウレベルにされる。

期間t6の後、読み出し期間RAPが開始される。読み出し期間RAPは、複数の期間t7を有している。期間t7は、ゲート電極(G1-Gm)のおのおのが、順次、-5Vの様な非選択レベルから10Vの様な選択レベルへ遷移され、その後、非選択レベルへ遷移される期間を示している。ゲート電極G1が選択レベルとされると、ゲート電極G1に接続された1行目の各光センサー回路(SC11、SC12、...、SC1n)内の各容量素子103に新たに蓄えられた電荷がスイッチングトランジスタ104をオン状態とすることにより、信号線Sig1-Signに読み出されて、読み出し回路RAへ入力される。すべてのゲート電極(G2-Gm)が順次選択レベルとされることで、アレイ部ARR内の全光センサー回路(SC11、SC12、...、SCmn)の全容量素子103の電荷が読み出し回路RAへ入力される。

期間t8は、読み出し期間RAPの終了後、に設けられる。期間t8の後、リセット信号RSTがロウレベルからハイレベルへ遷移することで、期間t1の開始前の状態に、各信号の状態が設定される。