WO2015178215A1 - データ処理装置、及び、データ処理方法 - Google Patents

データ処理装置、及び、データ処理方法 Download PDFInfo

- Publication number

- WO2015178215A1 WO2015178215A1 PCT/JP2015/063253 JP2015063253W WO2015178215A1 WO 2015178215 A1 WO2015178215 A1 WO 2015178215A1 JP 2015063253 W JP2015063253 W JP 2015063253W WO 2015178215 A1 WO2015178215 A1 WO 2015178215A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- ldpc code

- check matrix

- bits

- code

- bit

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2792—Interleaver wherein interleaving is performed jointly with another technique such as puncturing, multiplexing or routing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/033—Theoretical methods to calculate these checking codes

- H03M13/036—Heuristic code construction methods, i.e. code construction or code search based on using trial-and-error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1105—Decoding

- H03M13/1131—Scheduling of bit node or check node processing

- H03M13/1137—Partly parallel processing, i.e. sub-blocks or sub-groups of nodes being processed in parallel

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

- H03M13/1165—QC-LDPC codes as defined for the digital video broadcasting [DVB] specifications, e.g. DVB-Satellite [DVB-S2]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

- H03M13/255—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM] with Low Density Parity Check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

- H03M13/271—Row-column interleaver with permutations, e.g. block interleaving with inter-row, inter-column, intra-row or intra-column permutations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2778—Interleaver using block-wise interleaving, e.g. the interleaving matrix is sub-divided into sub-matrices and the permutation is performed in blocks of sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/29—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes combining two or more codes or code structures, e.g. product codes, generalised product codes, concatenated codes, inner and outer codes

- H03M13/2906—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes combining two or more codes or code structures, e.g. product codes, generalised product codes, concatenated codes, inner and outer codes using block codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/35—Unequal or adaptive error protection, e.g. by providing a different level of protection according to significance of source information or by adapting the coding according to the change of transmission channel characteristics

- H03M13/356—Unequal error protection [UEP]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0041—Arrangements at the transmitter end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0071—Use of interleaving

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/118—Parity check matrix structured for simplifying encoding, e.g. by having a triangular or an approximate triangular structure

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/13—Linear codes

- H03M13/15—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes

- H03M13/151—Cyclic codes, i.e. cyclic shifts of codewords produce other codewords, e.g. codes defined by a generator polynomial, Bose-Chaudhuri-Hocquenghem [BCH] codes using error location or error correction polynomials

- H03M13/152—Bose-Chaudhuri-Hocquenghem [BCH] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

- H03M13/2707—Simple row-column interleaver, i.e. pure block interleaving

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/61—Aspects and characteristics of methods and arrangements for error correction or error detection, not provided for otherwise

- H03M13/615—Use of computational or mathematical techniques

- H03M13/616—Matrix operations, especially for generator matrices or check matrices, e.g. column or row permutations

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6522—Intended application, e.g. transmission or communication standard

- H03M13/6552—DVB-T2

Definitions

- the present technology relates to a data processing device and a data processing method, and in particular, a data processing device and a data processing method that can ensure good communication quality, for example, in data transmission using an LDPC code. About.

- LDPC Low Density Parity Check

- DVB Digital Video Broadcasting

- DVB-T.2 DVB-C.2

- ATSC Advanced Television Systems Committee

- LDPC codes have been found to have performance close to the Shannon limit as the code length is increased, as is the case with turbo codes and the like.

- the LDPC code has the property that the minimum distance is proportional to the code length, its characteristic is that the block error probability characteristic is good, and furthermore, the so-called error floor phenomenon observed in the decoding characteristic such as turbo code is observed.

- An advantage is that it hardly occurs.

- DVB-S.2 ETSI EN 302 307 V1.2.1 (2009-08)

- the LDPC code is used as a symbol of quadrature modulation (digital modulation) such as QPSK (Quadrature Phase Shift Keying), and the symbol is used as a signal point for quadrature modulation. Mapped and sent.

- quadrature modulation digital modulation

- QPSK Quadrature Phase Shift Keying

- the present technology has been made in view of such a situation, and is intended to ensure good communication quality in data transmission using an LDPC code.

- the first data processing apparatus / method of the present technology includes an encoding unit / step for performing LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 10/15.

- the sequence of 44 is represented by bit groups 17, 2, 30, 12, 7, 25, 27, 3, 15, 14, 4, 26, 34, 31, 13, 22, 0, 39, 23, 24, 21, 6 , 38, 5, 19, 42, 11 , 32, 28, 40, 20, 18, 36, 9, 41, 10, 33, 37, 1, 16, 8, 43, 29, 35, 44

- the LDPC code includes information bits and parity bits

- the check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is , Represented by a parity check matrix initial value table

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix portion every 360 columns, 352 747 894 1437 1688 1807 1883 21

- LDPC coding is performed based on a parity check matrix of an LDPC code having a code length N of 16200 bits and a coding rate r of 10/15.

- Group-wise interleaving is performed in which bits are interleaved in bit group units.

- the LDPC code is mapped to any one of 256 signal points determined by the modulation method in units of 8 bits.

- an i + 1-th bit group from the beginning of the LDPC code is set as a bit group i, and the bit groups 0 to 44 of the 16200-bit LDPC code are arranged in bit groups 17, 2, 30, 12, 7, 25, 27, 3, 15, 14, 4, 26, 34, 31, 13, 22, 0, 39, 23, 24, 21, 6, 38, 5, 19, 42, 11, 32, 28, 40, 20, 18, 36, 9, 41, 10, 33, 37, 1, 16, 8, 43, 29, 35, 44 Are interleaved.

- the LDPC code includes information bits and parity bits

- the parity check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is a parity check matrix initial value.

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix part for every 360 columns, 352 747 894 1437 1688 1807 1883 2119 2159 3321 3400 3543 3588 3770 3821 4384 4470 4884 5012 5036 5084 5101 5271 5281 5353 505 915 1156 1269 1518 1650 2153 2256 2344 2465 2509 2867 2875 3007 3254 3519 3687 4331 4439 4532 4940 5011 5076 5113 5367 268 346 650 919 1260 4389 4653 4721 4838 5054 5157 5162 5275 5362 220 236 828 1590 1792 3259 3647 4276 4281 4325 4963 4974 5003 5037 381 737 1099 1409 2364 2955 3228 3341 3473 3985 4257 4730 5173 5242 88 771 1640 1737 1803 2408 2575 2974 3167 3464 3780 4501 4901 5047 749 1502 2201 3189 2873 3245 34

- a second data processing device / method of the present technology includes an encoding unit that performs LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 10/15, Group-wise interleaving unit that performs group-wise interleaving for interleaving LDPC codes in 360-bit bit group units, and mapping the LDPC codes to any one of 256 signal points defined by modulation schemes in 8-bit units

- the i + 1-th bit group from the head of the LDPC code is defined as bit group i

- the bit groups 0 to 44 of the 16200-bit LDPC code are arranged in bits.

- the LDPC code includes information bits and parity bits

- the check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is , Represented by a parity check matrix initial value table

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix portion every 360 columns, 352 747 894 1437 1688 1807 1883 2119 2159 3321 3400 3543 3588 3770 3821 4384 4470 4884 5012 5036 5084 5101 5271 5281 5353 505 915 1156 1269 1518 1650 2153 2256 2344 2465 2509 2867 2875 3007 3254 3519 3687 4331 4439 4532 4940 5011 5076 5113 53

- an encoding unit that performs LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 10/15, and the LDPC code

- a group-wise interleaving unit that performs group-wise interleaving for interleaving in units of 360-bit bit groups, and mapping that maps the LDPC code to any one of 256 signal points determined by a modulation scheme in units of 8 bits

- the i + 1-th bit group from the head of the LDPC code is defined as a bit group i

- the bit group 0 to 44 of the 16200-bit LDPC code is arranged as a bit group 17 , 2, 30, 12, 7, 25, 27, 3, 15, 14, 4, 26, 34, 31, 13, 22, 0, 39, 23, 24, 21, 6, 38, 5, 19, 42 , 11, 32, 28, 40, 20, 18, 36, 9, 41, 10 33,37,1,16,8,43,29,35,44

- the group-wise interleaving unit that performs group-

- a third data processing apparatus / method of the present technology includes an encoding unit / step that performs LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 12/15.

- the sequence of 44 is represented by bit groups 28, 21, 10, 15, 8, 22, 26, 2, 14, 1, 27, 3, 39, 20, 34, 25, 12, 6, 7, 40, 30, 29.

- the LDPC code includes information bits and parity bits

- the check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is , Represented by a parity check matrix initial value table

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix portion every 360 columns, 3 394 1014 1214 1361 1477 1534 1660 1856 2745 2987 2991 3124 3155 59 136 528 781 803 928 1293 1489 1944 2041 2200 2613 2690 2847 155 245 311 621 1114 1269 1281 1783 1995 2047 2672 2803 2885 3014 79 870 974 1326 1449 1531 2077 2317 2467 2627 2811 3083 3101 3132 4 582 660 902 1048 1482 1697 1744 1928

- LDPC coding is performed based on a parity check matrix of an LDPC code having a code length N of 16200 bits and a coding rate r of 12/15.

- Group-wise interleaving is performed in which bits are interleaved in bit group units.

- the LDPC code is mapped to any one of 256 signal points determined by the modulation method in units of 8 bits.

- an i + 1-th bit group from the head of the LDPC code is a bit group i

- the bit groups 0 to 44 of the 16200-bit LDPC code are arranged in bit groups 28, 21, 10, 15, 8, 22, 26, 2, 14, 1, 27, 3, 39, 20, 34, 25, 12, 6, 7, 40, 30, 29, 38, 16, 43, 33, 4, 35, 9, 32, 5, 36, 0, 41, 37, 18, 17, 13, 24, 42, 31, 23, 19, 11, 44 Are interleaved.

- the LDPC code includes information bits and parity bits

- the parity check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is a parity check matrix initial value.

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix part for every 360 columns, 3 394 1014 1214 1361 1477 1534 1660 1856 2745 2987 2991 3124 3155 59 136 528 781 803 928 1293 1489 1944 2041 2200 2613 2690 2847 155 245 311 621 1114 1269 1281 1783 1995 2047 2672 2803 2885 3014 79 870 974 1326 1449 1531 2077 2317 2467 2627 2811 3083 3101 3132 4 582 660 902 1048 1482 1697 1744 1928 2628 2699 2728 3045 3104 175 395 429 1027 1061 1068 1154 1168 1175 2147 2359 2376 2613 2682 1388 2241 3118 3148 143 506 2067 3148 1594 2217 2705 398 988 2551 1149 2588 2654 678 2844 3115 1508 1547 1954 1199 1267 1710 2589 3163 3207 1 2583 2974

- a fourth data processing device / method of the present technology includes: an encoding unit that performs LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 12/15; Group-wise interleaving unit that performs group-wise interleaving for interleaving LDPC codes in 360-bit bit group units, and mapping the LDPC codes to any one of 256 signal points defined by modulation schemes in 8-bit units In the group-wise interleave, the i + 1-th bit group from the head of the LDPC code is defined as bit group i, and the bit groups 0 to 44 of the 16200-bit LDPC code are arranged in bits.

- the LDPC code includes information bits and parity bits

- the check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is , Represented by a parity check matrix initial value table

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix portion every 360 columns, 3 394 1014 1214 1361 1477 1534 1660 1856 2745 2987 2991 3124 3155 59 136 528 781 803 928 1293 1489 1944 2041 2200 2613 2690 2847 155 245 311 621 1114 1269 1281 1783 1995 2047 2672 2803 2885 3014 79 870 974 1326 1449 1531 2077 2317 2467 2627 28

- an encoding unit that performs LDPC encoding based on a parity check matrix of an LDPC code having a code length N of 16200 bits and an encoding rate r of 12/15, and the LDPC code

- a group-wise interleaving unit that performs group-wise interleaving for interleaving in units of 360-bit bit groups, and mapping that maps the LDPC code to any one of 256 signal points determined by a modulation scheme in units of 8 bits

- the i + 1-th bit group from the head of the LDPC code is defined as a bit group i

- the bit group 0 to 44 of the 16200-bit LDPC code is arranged as a bit group 28.

- the LDPC code includes information bits and parity bits

- the check matrix includes an information matrix portion corresponding to the information bits and a parity matrix portion corresponding to the parity bits

- the information matrix portion is , Represented by a parity check matrix initial value table

- the parity check matrix initial value table is a table that represents the position of one element of the information matrix portion every 360 columns, 3 394 1014 1214 1361 1477 1534 1660 1856 2745 2987 2991 3124 3155 59 136 528 781 803 928 1293 1489 1944 2041 2200 2613 2690 2847 155 245 311 621 1114 1269 1281 1783 1995 2047 2672 2803 2885 3014 79 870 974 1326 1449 1531 2077 2317 2467 2627 2811

- the data processing apparatus may be an independent apparatus or an internal block constituting one apparatus.

- FIG. 3 is a block diagram illustrating a configuration example of a transmission device 11.

- FIG. 3 is a block diagram illustrating a configuration example of a bit interleaver 116.

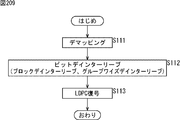

- FIG. 12 is a flowchart illustrating an example of processing performed by a bit interleaver 116 and a mapper 117.

- 3 is a block diagram illustrating a configuration example of an LDPC encoder 115.

- FIG. 5 is a flowchart illustrating an example of processing of an LDPC encoder 115.

- Fig. 38 is a diagram illustrating an example of a parity check matrix initial value table with the code rate 1/4 and the code length 16200. It is a figure explaining the method of calculating

- FIG. It is a figure which shows the example of a check matrix initial value table. It is a figure which shows the example of the Tanner graph of the ensemble of a degree sequence that column weight is 3 and row weight is 6.

- FIG. It is a figure which shows the example of the Tanner graph of a multi-edge type ensemble. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure explaining a check matrix. It is a figure which shows the example of the constellation in case a modulation system is 16QAM.

- the symbol y of 1024QAM a diagram showing the relationship between the complex numbers real part Re (z q) as the coordinates of a signal point z q corresponding 1D NUC symbol y and imaginary part Im (z q), respectively. It is a figure which shows the example of the coordinate of the signal point of 1D

- the symbol y of 4096QAM a diagram showing the relationship between the complex numbers real part Re (z q) as the coordinates of a signal point z q corresponding 1D NUC symbol y and imaginary part Im (z q), respectively. It is a figure which shows the other example of the constellation in case a modulation system is 16QAM.

- FIG. 3 is a block diagram illustrating a configuration example of a block interleaver 25.

- FIG. It is a figure which shows the example of the column number C of parts 1 and 2 and part column length R1 and R2 with respect to the combination of code length N and a modulation system. It is a figure explaining the block interleaving performed with the block interleaver 25.

- FIG. It is a figure explaining the groupwise interleaving performed in the groupwise interleaver 24.

- FIG. It is a figure which shows the 1st example of GW pattern with respect to the LDPC code whose code length N is 64k bit. It is a figure which shows the 2nd example of GW pattern with respect to the LDPC code whose code length N is 64k bit.

- FIG. 10 is a flowchart illustrating an example of processing performed by a demapper 164, a bit deinterleaver 165, and an LDPC decoder 166. It is a figure which shows the example of the check matrix of a LDPC code.

- FIG. 3 is a block diagram illustrating a configuration example of an LDPC decoder 166.

- FIG. 3 is a block diagram illustrating a configuration example of a block deinterleaver 54.

- FIG. It is a block diagram which shows the other structural example of the bit deinterleaver 165.

- FIG. It is a block diagram which shows the 1st structural example of the receiving system which can apply the receiving device.

- FIG. 18 is a block diagram illustrating a configuration example of an embodiment of a computer to which the present technology is applied.

- LDPC code is a linear code and does not necessarily need to be binary, but here it will be described as being binary.

- LDPC code is characterized by the fact that the parity check matrix that defines the LDPC code is sparse.

- a sparse matrix is a matrix in which the number of “1” s in the matrix is very small (a matrix in which most elements are 0).

- FIG. 1 is a diagram illustrating an example of a parity check matrix H of an LDPC code.

- the weight of each column (column weight) (the number of “1”) (weight) is “3”, and the weight of each row (row weight) is “6”. .

- a generator matrix G is generated based on the check matrix H, and the generator matrix G is multiplied by binary information bits to generate a codeword (LDPC code). ) Is generated.

- the generator matrix G is a K ⁇ N matrix

- the encoding device multiplies the generator matrix G by a bit string (vector u) of information bits made up of K bits to generate a code made up of N bits.

- the code word (LDPC code) generated by this encoding device is received on the receiving side via a predetermined communication path.

- LDPC code decoding is an algorithm proposed by Gallager called probabilistic decoding (Probabilistic Decoding), consisting of variable nodes (also called message nodes) and check nodes (check nodes). This can be done by a message passing algorithm based on belief propagation on a so-called Tanner graph.

- the variable node and the check node are also simply referred to as nodes as appropriate.

- FIG. 2 is a flowchart showing a procedure for decoding an LDPC code.

- a real value (reception LLR) expressing the “0” likelihood of the value of the i-th code bit of the LDPC code (1 codeword) received on the receiving side as a log likelihood ratio as appropriate. ) Is also referred to as a received value u 0i . Further, a message output from the check node is u j and a message output from the variable node is v i .

- step S11 the LDPC code is received, the message (check node message) u j is initialized to “0”, and the counter of the iterative process is used.

- the variable k taking the integer of is initialized to “0”, and the process proceeds to step S12.

- step S12 a message (variable node message) v i is obtained by performing the calculation (variable node calculation) shown in Expression (1) based on the received value u 0i obtained by receiving the LDPC code.

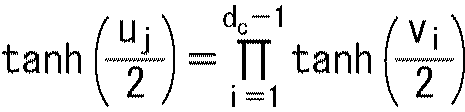

- the message u j is obtained by performing the calculation (check node calculation) shown in Expression (2).

- Equation (1) and Equation (2) can be arbitrarily selected to indicate the number of “1” s in the vertical direction (column) and horizontal direction (row) of the parity check matrix H, respectively.

- variable node calculation of Expression (1) the message input from the edge (line connecting the variable node and the check node) to which the message is to be output, respectively.

- the computation range is 1 to d v -1 or 1 to d c -1.

- the check node calculation of equation (2) actually creates a table of function R (v 1 , v 2 ) shown in equation (3) defined by one output for two inputs v 1 and v 2 in advance. In addition, this is performed by using it continuously (recursively) as shown in Equation (4).

- step S12 the variable k is further incremented by “1”, and the process proceeds to step S13.

- step S13 it is determined whether or not the variable k is larger than a predetermined iterative decoding count C. If it is determined in step S13 that the variable k is not greater than C, the process returns to step S12, and thereafter the same processing is repeated.

- step S13 determines whether the variable k is larger than C. If it is determined in step S13 that the variable k is larger than C, the process proceeds to step S14, and a message v i as a decoding result to be finally output is obtained by performing the calculation shown in equation (5). And the LDPC code decoding process ends.

- equation (5) is performed using messages u j from all branches connected to the variable node.

- FIG. 3 is a diagram illustrating an example of a parity check matrix H of a (3, 6) LDPC code (coding rate 1/2, code length 12).

- the column weight is 3 and the row weight is 6, as in FIG.

- FIG. 4 is a diagram showing a Tanner graph of the check matrix H in FIG.

- a plus “+” represents a check node

- Check nodes and variable nodes correspond to the rows and columns of the parity check matrix H, respectively.

- the connection between the check node and the variable node is an edge, and corresponds to “1” of the check matrix element.

- FIG. 5 is a diagram showing variable node calculation performed in the variable node.

- the message v i corresponding to the branch to be calculated is the variable node of the formula (1) using the messages u 1 and u 2 from the remaining branches connected to the variable node and the received value u 0i. It is obtained by calculation. Messages corresponding to other branches are obtained in the same manner.

- FIG. 6 is a diagram showing a check node calculation performed in the check node.

- Equation (6) can be transformed into Equation (7).

- the message u j corresponding to the branch to be calculated is the messages v 1 , v 2 , v 3 , v 4 , v from the remaining branches connected to the check node. It is obtained by the check node calculation of Equation (7) using 5 . Messages corresponding to other branches are obtained in the same manner.

- ⁇ (x) and ⁇ ⁇ 1 (x) are mounted on hardware, they may be mounted using a LUT (Look Up Table), but both are the same LUT.

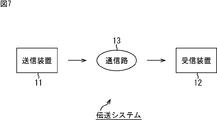

- FIG. 7 shows a transmission system to which the present technology is applied (a system is a logical collection of a plurality of devices, regardless of whether or not each component device is in the same housing). It is a figure which shows the structural example of embodiment.

- the transmission system includes a transmission device 11 and a reception device 12.

- the transmission device 11 transmits (broadcasts) (transmits) a television broadcast program, for example. That is, the transmission device 11 encodes target data to be transmitted, such as image data and audio data as a program, into an LDPC code, for example, a satellite line, a terrestrial wave, a cable (wired line), or the like. It transmits via the communication path 13.

- target data to be transmitted such as image data and audio data as a program

- an LDPC code for example, a satellite line, a terrestrial wave, a cable (wired line), or the like. It transmits via the communication path 13.

- the receiving device 12 receives the LDPC code transmitted from the transmitting device 11 via the communication path 13, decodes it into the target data, and outputs it.

- the LDPC code used in the transmission system of FIG. 7 exhibits extremely high capability in an AWGN (Additive White Gaussian Noise) channel.

- AWGN Additional White Gaussian Noise

- a burst error or erasure may occur in the communication path 13.

- D / U Desired to Undesired Ratio

- Desired main path power

- a burst error may occur due to the state of the wiring from the receiving unit (not shown) such as an antenna that receives a signal from the transmitting device 11 to the receiving device 12 on the receiving device 12 side or the instability of the power supply of the receiving device 12. May occur.

- the code bit of the LDPC code (the received value u 0i ) Since the variable node calculation of Expression (1) involving addition is performed, if an error occurs in the sign bit used for the variable node calculation, the accuracy of the required message is reduced.

- the check node performs the check node calculation of Expression (7) using the message obtained by the variable node connected to the check node, so that a plurality of connected variable nodes ( When the number of check nodes in which the error (including erasure) of the code bits of the LDPC code corresponding to) simultaneously increases, the decoding performance deteriorates.

- the check node sends a message with an equal probability of a probability of 0 and a probability of 1 to all the variable nodes. return.

- a check node that returns an equiprobable message does not contribute to one decoding process (one set of variable node calculation and check node calculation), and as a result, requires a large number of repetitions of the decoding process. As a result, the decoding performance deteriorates, and the power consumption of the receiving apparatus 12 that decodes the LDPC code increases.

- FIG. 8 is a block diagram illustrating a configuration example of the transmission device 11 of FIG.

- one or more input streams (Input Streams) as target data are supplied to a Mode Adaptation / Multiplexer 111.

- the mode adaptation / multiplexer 111 performs processing such as mode selection and multiplexing of one or more input streams supplied thereto as necessary, and supplies the resulting data to a padder 112. .

- the padder 112 performs necessary zero padding (Null insertion) on the data from the mode adaptation / multiplexer 111 and supplies the resulting data to the BB scrambler 113.

- the BB scrambler 113 subjects the data from the padder 112 to BB scramble (Base-Band Scrambling), and supplies the resulting data to a BCH encoder (BCH encoder) 114.

- BCH encoder BCH encoder

- the BCH encoder 114 BCH-encodes the data from the BB scrambler 113, and supplies the resulting data to an LDPC encoder 115 as LDPC target data that is an LDPC encoding target.

- the LDPC encoder 115 performs LDPC coding on the LDPC target data from the BCH encoder 114, for example, according to a parity check matrix that is a portion corresponding to the parity bit of the LDPC code, and a parity matrix having a dual (diagonal) structure. To output an LDPC code having LDPC target data as information bits.

- the LDPC encoder 115 sets the LDPC target data to the LDPC (corresponding to the check matrix) defined in a predetermined standard such as DVB-S.2, DVB-T.2, or DVB-C.2. Code, LDPC encoding to be used in ATSC 3.0 (corresponding to the parity check matrix) and the like, and LDPC code obtained as a result is output.

- the LDPC code defined in the DVB-T.2 standard and the LDPC code to be adopted in ATSC 3.0 are IRA (Irregular Repeat Accumulate) codes

- the parity matrix in the parity check matrix of the LDPC code is It has a staircase structure. The parity matrix and the staircase structure will be described later.

- IRA codes for example, “Irregular Repeat-Accumulate Codes,” H. Jin, A. Khandekar, and R. J. McEliece, in Proceedings of 2nd International Symposium on Turbo codes and Related Topics-8 , Sept. 2000.

- the LDPC code output from the LDPC encoder 115 is supplied to a bit interleaver 116.

- the bit interleaver 116 performs bit interleaving described later on the LDPC code from the LDPC encoder 115 and supplies the LDPC code after the bit interleaving to the mapper 117.

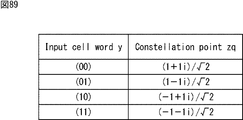

- the mapper 117 maps the LDPC code from the bit interleaver 116 to a signal point representing one symbol of orthogonal modulation in units of one or more code bits (symbol unit) of the LDPC code and performs orthogonal modulation (multiple modulation). Value modulation).

- the mapper 117 converts the LDPC code from the bit interleaver 116 into an IQ plane (IQ constellation) defined by an I axis representing an I component in phase with the carrier and a Q axis representing a Q component orthogonal to the carrier.

- the quadrature modulation is performed by mapping to signal points determined by the modulation method for performing the quadrature modulation of the LDPC code.

- the mapper 117 uses the bit interleaver 116. Are mapped to signal points representing symbols out of 2 m signal points in symbol units.

- a modulation method of orthogonal modulation performed by the mapper 117 for example, a modulation method defined in the DVB-T.2 standard, a modulation method to be adopted in ATSC 3.0, other modulation methods, For example, BPSK (Binary Phase Shift Keying), QPSK (Quadrature Phase Shift Keying), 8PSK (Phase-Shift Keying), 16APSK (Amplitude Phase Shift Keying), 32APSK, 16QAM (Quadrature Amplitude Modulation), 16QAM, 64QAM , 256QAM, 1024QAM, 4096QAM, 4PAM (Pulse Amplitude Modulation), etc.

- BPSK Binary Phase Shift Keying

- QPSK Quadadrature Phase Shift Keying

- 8PSK Phase-Shift Keying

- 16APSK Amplitude Phase Shift Keying

- 32APSK 16QAM (Quadrature Amplitude Modulation)

- 16QAM 64QAM

- Data obtained by processing in the mapper 117 (mapping result obtained by mapping symbols to signal points) is supplied to a time interleaver 118.

- the time interleaver 118 performs time interleaving (interleaving in the time direction) on the data from the mapper 117 in units of symbols, and the resulting data is converted into SISO / MISO encoders (SISO / MISO (Single / Input / Single / Output / Multiple). Input Single Output) encoder) 119.

- SISO / MISO encoders SISO / MISO encoders

- the SISO / MISO encoder 119 performs space-time coding on the data from the time interleaver 118 and supplies it to a frequency interleaver 120.

- the frequency interleaver 120 performs frequency interleaving (interleaving in the frequency direction) on a symbol-by-symbol basis for the data from the SISO / MISO encoder 119 and supplies the data to a frame builder / resource allocation unit (Frame Builder & Resource Allocation) 131.

- a frame builder / resource allocation unit Fre Builder & Resource Allocation

- the BCH encoder 121 is supplied with control data (signalling) for transmission control such as BB signaling (Base Band Signaling) (BB Header).

- BB signaling Basic Band Signaling

- the BCH encoder 121 performs BCH encoding on the control data supplied thereto in the same manner as the BCH encoder 114, and supplies the resulting data to the LDPC encoder 122.

- the LDPC encoder 122 performs LDPC encoding on the data from the BCH encoder 121 as LDPC target data in the same manner as the LDPC encoder 115, and supplies the resulting LDPC code to the mapper 123.

- the mapper 123 maps the LDPC code from the LDPC encoder 122 to a signal point that represents one symbol of orthogonal modulation in units of one or more code bits (symbol unit) of the LDPC code. Then, quadrature modulation is performed, and data obtained as a result is supplied to the frequency interleaver 124.

- the frequency interleaver 124 performs frequency interleaving on the data from the mapper 123 in units of symbols and supplies the data to the frame builder / resource allocation unit 131.

- the frame builder / resource allocation unit 131 inserts pilot symbols at necessary positions of the data (symbols) from the frequency interleavers 120 and 124, and from the resulting data (symbols), a predetermined number

- a frame composed of a number of symbols for example, a PL (Physical Layer) frame, a T2 frame, a C2 frame, etc.

- OFDM generation OFDM generation

- the OFDM generation unit 132 generates an OFDM signal corresponding to the frame from the frame from the frame builder / resource allocation unit 131, and transmits the OFDM signal via the communication path 13 (FIG. 7).

- the transmission apparatus 11 is configured without providing some of the blocks illustrated in FIG. 8 such as the time interleaver 118, the SISO / MISO encoder 119, the frequency interleaver 120, and the frequency interleaver 124, for example. Can do.

- FIG. 9 is a block diagram illustrating a configuration example of the bit interleaver 116 of FIG.

- the bit interleaver 116 has a function of interleaving data, and includes a parity interleaver 23, a group-wise interleaver 24, and a block interleaver 25.

- the parity interleaver 23 performs parity interleaving for interleaving the parity bits of the LDPC code from the LDPC encoder 115 to the positions of other parity bits, and supplies the LDPC code after the parity interleaving to the group-wise interleaver 24.

- the groupwise interleaver 24 performs groupwise interleaving on the LDPC code from the parity interleaver 23, and supplies the LDPC code after the groupwise interleaving to the block interleaver 25.

- an LDPC code for one code is partitioned from the beginning into 360-bit units equal to a unit size P described later, and the one-part 360 bits are used as a bit group to generate a parity interleaver 23.

- bit group units are interleaved in bit group units.

- the error rate can be improved compared to when not performing groupwise interleaving, and as a result, good communication quality can be ensured in data transmission.

- the block interleaver 25 performs block interleaving for demultiplexing the LDPC code from the group-wise interleaver 24, so that, for example, an LDPC code for one code is converted into an m-bit symbol that is a unit of mapping. And supplied to the mapper 117 (FIG. 8).

- a column as a storage area for storing a predetermined number of bits in the column (vertical) direction is equal to the number m of symbol bits in the row (horizontal) direction.

- LDPC codes from the group-wise interleaver 24 are written in the column direction and read out in the row direction, for example, so that an LDPC code for one code is converted into an m-bit symbol.

- FIG. 10 is a diagram illustrating an example of a parity check matrix H used for LDPC encoding by the LDPC encoder 115 of FIG.

- LDGM Low-Density Generation Matrix

- the number of information bits and the number of parity bits in the code bits of one LDPC code are referred to as an information length K and a parity length M, respectively, and one (1

- the information length K and the parity length M for an LDPC code having a certain code length N are determined by the coding rate.

- the parity check matrix H is a matrix in which rows ⁇ columns are M ⁇ N (a matrix having M rows and N columns). Then, the information matrix H A, becomes the matrix of M ⁇ K, the parity matrix H T is a matrix of M ⁇ M.

- Figure 11 is a diagram showing an example of a parity matrix H T of the parity check matrix H used in LDPC encoding by the LDPC encoder 115 of FIG.

- Parity matrix H T of the parity check matrix H used in LDPC encoding by the LDPC encoder 115 is, for example, becomes similar to the parity matrix H T of the parity check matrix H of an LDPC code prescribed in standards such as DVB-T.2 ing.

- DVB-T.2 like parity matrix H T of the parity check matrix H of an LDPC code of which is specified in the Standard, as shown in FIG. 11, first element is, so to speak a matrix of step structure arranged stepwise (lower bidiagonal matrix).

- the row weight of the parity matrix H T is 1 for the first row and 2 for all the remaining rows.

- the column weight is 1 for the last column and 2 for all the remaining columns.

- LDPC codes of the check matrix H the parity matrix H T has a staircase structure can be using the check matrix H, readily produced.

- an LDPC code (one codeword), together represented by a row vector c, and column vector obtained by transposing the row vector is represented as c T. Further, in the row vector c which is an LDPC code, the information bit portion is represented by the row vector A, and the parity bit portion is represented by the row vector T.

- FIG. 12 is a diagram for explaining a parity check matrix H of an LDPC code defined in a standard such as DVB-T.2.

- the column weight is X, and for the subsequent K3 column, the column weight is 3, and then For the M-1 column, the column weight is 2, and for the last column, the column weight is 1.

- KX + K3 + M-1 + 1 is equal to the code length N.

- FIG. 13 is a diagram showing the number of columns KX, K3, and M, and the column weight X for each coding rate r of the LDPC code defined in the DVB-T.2 standard and the like.

- Standards such as DVB-T.2 specify LDPC codes with code length N of 64800 bits and 16200 bits.

- LDPC code having a code length N of 64,800 bits 11 coding rates (nominal rates) 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3 / 4, 4/5, 5/6, 8/9, and 9/10 are defined, and for an LDPC code having a code length N of 16200 bits, 10 coding rates 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, and 8/9 are specified.

- the code length N of 64800 bits is also referred to as 64k bits

- the code length N of 16200 bits is also referred to as 16k bits.

- the error rate tends to be lower for code bits corresponding to columns having a larger column weight of the check matrix H.

- the column weight on the head side (left side) tends to be large.

- the LDPC code corresponding to H the first code bit tends to be more resistant to errors (tolerant to errors), and the last code bit tends to be weaker to errors.

- parity interleaving by the parity interleaver 23 in FIG. 9 will be described with reference to FIGS.

- FIG. 14 is a diagram illustrating an example of (part of) a Tanner graph of a parity check matrix of an LDPC code.

- variable nodes corresponding code bits

- all the check nodes are connected to the check node.

- a message having a probability that the value is 0 and the probability that the value is 1 is returned to the variable node. For this reason, if a plurality of variable nodes connected to the same check node simultaneously become erasures or the like, the decoding performance deteriorates.

- an LDPC code output from the LDPC encoder 115 of FIG. 8 for example, similarly to the LDPC code prescribed in standards such as DVB-T.2, an IRA code, the parity matrix H T of the parity check matrix H As shown in FIG. 11, it has a staircase structure.

- FIG. 15 is a diagram illustrating an example of a parity matrix H T having a staircase structure and a Tanner graph corresponding to the parity matrix H T as illustrated in FIG.

- FIG. 15A shows an example of a parity matrix H T having a staircase structure

- FIG. 15B shows a Tanner graph corresponding to the parity matrix H T of A in FIG.

- parity matrix H T has a staircase structure, in each row (except the first row) first element is adjacent. Therefore, in the Tanner graph of the parity matrix H T, the value of the parity matrix H T corresponding to the columns of two adjacent elements are set to 1, the two variable nodes adjacent, connected to the same check node Yes.

- the parity interleaver 23 (FIG. 9) performs parity interleaving for interleaving the parity bits of the LDPC code from the LDPC encoder 115 to the positions of other parity bits in order to prevent the above-described degradation in decoding performance. .

- Figure 16 is a diagram illustrating a parity matrix H T of the parity check matrix H corresponding to the LDPC code after parity interleave to the parity interleaver 23 of FIG. 9 is performed.

- the information matrix H A of the parity check matrix H corresponding to the LDPC code output from the LDPC encoder 115 is the same as the information matrix of the parity check matrix H corresponding to the LDPC code defined in the standard such as DVB-T.2. In addition, it has a cyclic structure.

- a cyclic structure is a structure in which a column matches a cyclic shift of another column.For example, for each P column, the position of 1 in each row of the P column is the first of the P column.

- a structure in which the column is cyclically shifted in the column direction by a predetermined value such as a value proportional to the value q obtained by dividing the parity length M is also included.

- the P row in the cyclic structure is referred to as a unit size as appropriate.

- the unit size P is defined as 360 which is one of the divisors of the parity length M except 1 and M.

- the parity interleaver 23 sets the information length to K, sets x to an integer between 0 and less than P, and sets y to an integer between 0 and less than q.

- the K + qx + y + 1-th code bit is interleaved at the position of the K + Py + x + 1-th code bit.

- the K + qx + y + 1-th code bit and the K + Py + x + 1-th code bit are both the K + 1-th code bit and the subsequent parity bits, and are therefore parity bits. According to interleaving, the position of the parity bit of the LDPC code is moved.

- variable nodes connected to the same check node are separated by unit size P, that is, 360 bits here, so the burst length is less than 360 bits.

- unit size P that is, 360 bits here

- the LDPC code after parity interleaving that interleaves the K + qx + y + 1-th code bit at the position of the K + Py + x + 1-th code bit is K + qx + of the original parity check matrix H.

- the pseudo cyclic structure means a structure in which a part except for a part has a cyclic structure.

- the parity check matrix obtained by performing column replacement equivalent to parity interleaving on the parity check matrix of the LDPC code specified in the DVB-T.2 standard, etc. is 360 rows ⁇

- the 360-column part (shift matrix described later) there is only one element of 1 (it is an element of 0). In that respect, it is not a (perfect) cyclic structure, but a pseudo cyclic structure. ing.

- the conversion parity check matrix for the LDPC code parity check matrix output from the LDPC encoder 115 has, for example, a pseudo cyclic structure, similar to the conversion parity check matrix for the LDPC code parity check matrix stipulated in a standard such as DVB-T.2. ing.

- the conversion check matrix in FIG. 16 replaces rows so that the conversion check matrix is configured with a configuration matrix described later. (Row replacement) is also applied to the matrix.

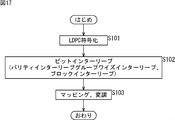

- FIG. 17 is a flowchart for explaining processing performed by the LDPC encoder 115, the bit interleaver 116, and the mapper 117 of FIG.

- the LDPC encoder 115 waits for the LDPC target data to be supplied from the BCH encoder 114, encodes the LDPC target data into an LDPC code in step S101, and supplies the LDPC code to the bit interleaver 116. The process proceeds to step S102.

- step S102 the bit interleaver 116 performs bit interleaving on the LDPC code from the LDPC encoder 115, supplies a symbol obtained by the bit interleaving to the mapper 117, and the process proceeds to step S103.

- the parity interleaver 23 performs parity interleaving for the LDPC code from the LDPC encoder 115, and converts the LDPC code after the parity interleaving to the group-wise interleave. Supplied to Lever 24.

- the groupwise interleaver 24 performs groupwise interleaving on the LDPC code from the parity interleaver 23 and supplies it to the block interleaver 25.

- the block interleaver 25 performs block interleaving on the LDPC code after group-wise interleaving by the group-wise interleaver 24, and supplies the m-bit symbol obtained as a result to the mapper 117.

- step S103 the mapper 117 maps the symbol from the block interleaver 25 to one of 2 m signal points determined by the orthogonal modulation method performed by the mapper 117, and performs quadrature modulation. Data is supplied to the time interleaver 118.

- the parity interleaver 23 that is a block that performs parity interleaving and the group-wise interleaver 24 that is a block that performs group-wise interleaving are configured separately.

- the parity interleaver 23 and the group-wise interleaver 24 can be configured integrally.

- both parity interleaving and group-wise interleaving can be performed by writing and reading code bits to and from the memory, and an address (write address) for writing code bits is an address for reading code bits. It can be represented by a matrix to be converted into (read address).

- parity interleaving is performed by converting the sign bit using those matrices, and further, A result of group-wise interleaving the LDPC code after parity interleaving can be obtained.

- the block interleaver 25 can also be configured integrally.

- the block interleaving performed by the block interleaver 25 can also be represented by a matrix that converts the write address of the memory storing the LDPC code into the read address.

- FIG. 18 is a block diagram illustrating a configuration example of the LDPC encoder 115 of FIG.

- LDPC encoder 122 of FIG. 8 is similarly configured.

- N LDPC codes 64800 bits and 16200 bits are defined.

- LDPC codes having a code length N of 64,800 bits eleven coding rates 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4 / 5, 5/6, 8/9, and 9/10 are defined, and for LDPC codes with a code length N of 16200 bits, 10 coding rates 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, and 8/9 are defined (FIGS. 12 and 13).

- the LDPC encoder 115 performs encoding (error correction coding) using an LDPC code having a code length N of 64,800 bits or 16200 bits for each code length N and each code rate. This can be performed according to the prepared check matrix H.

- the LDPC encoder 115 includes an encoding processing unit 601 and a storage unit 602.

- the encoding processing unit 601 includes an encoding rate setting unit 611, an initial value table reading unit 612, a parity check matrix generation unit 613, an information bit reading unit 614, an encoded parity calculation unit 615, and a control unit 616, and an LDPC encoder

- the LDPC encoding of the LDPC target data supplied to 115 is performed, and the resulting LDPC code is supplied to the bit interleaver 116 (FIG. 8).

- the coding rate setting unit 611 sets the code length N and coding rate of the LDPC code in accordance with, for example, an operator's operation.

- the initial value table reading unit 612 reads a parity check matrix initial value table, which will be described later, corresponding to the code length N and the coding rate set by the coding rate setting unit 611 from the storage unit 602.

- the parity check matrix H is generated by arranging one element of the information matrix HA corresponding to the length N-parity length M) in the column direction at a period of every 360 columns (unit size P), and stored in the storage unit 602.

- the information bit reading unit 614 reads (extracts) information bits for the information length K from the LDPC target data supplied to the LDPC encoder 115.

- the encoded parity calculation unit 615 reads the parity check matrix H generated by the parity check matrix generation unit 613 from the storage unit 602, and uses the parity check matrix H to calculate a parity bit for the information bits read by the information bit reading unit 614, A codeword (LDPC code) is generated by calculating based on the formula.

- LDPC code LDPC code

- the control unit 616 controls each block constituting the encoding processing unit 601.

- the storage unit 602 stores, for example, a plurality of parity check matrix initial value tables corresponding to a plurality of coding rates and the like shown in FIGS. 12 and 13 for code lengths N such as 64800 bits and 16200 bits, respectively. Has been.

- the storage unit 602 temporarily stores data necessary for the processing of the encoding processing unit 601.

- FIG. 19 is a flowchart for explaining an example of processing of the LDPC encoder 115 of FIG.

- step S201 the coding rate setting unit 611 determines (sets) a code length N and a coding rate r for performing LDPC coding.

- step S202 the initial value table reading unit 612 reads, from the storage unit 602, a predetermined parity check matrix initial value table corresponding to the code length N and the coding rate r determined by the coding rate setting unit 611. .

- the parity check matrix generation unit 613 uses the parity check matrix initial value table read from the storage unit 602 by the initial value table reading unit 612, and the code length N and the coding rate determined by the coding rate setting unit 611.

- the parity check matrix H of the LDPC code of r is obtained (generated), supplied to the storage unit 602 and stored.

- step S205 the encoded parity calculation unit 615 sequentially calculates the parity bits of the codeword c satisfying Expression (8) using the information bits from the information bit reading unit 614 and the check matrix H.

- c represents a row vector as a code word (LDPC code), and c T represents transposition of the row vector c.

- the information bit portion is represented by the row vector A and the parity bit portion is represented by the row vector T.

- step S206 the control unit 616 determines whether or not to end LDPC encoding. If it is determined in step S206 that the LDPC encoding is not terminated, that is, for example, if there is still LDPC target data to be LDPC encoded, the process returns to step S201 (or step S204). The processing from S201 (or step S204) to S206 is repeated.

- step S206 If it is determined in step S206 that the LDPC encoding is to be ended, that is, for example, if there is no LDPC target data to be LDPC encoded, the LDPC encoder 115 ends the processing.

- a parity check matrix initial value table corresponding to each code length N and each coding rate r is prepared, and the LDPC encoder 115 has a predetermined code length N and a predetermined coding rate r.

- LDPC encoding is performed using a parity check matrix H generated from a parity check matrix initial value table corresponding to the predetermined code length N and the predetermined coding rate r.

- the parity check matrix initial value table includes an information matrix H A corresponding to the code length N of the LDPC code (LDPC code defined by the parity check matrix H) and the information length K of the parity check matrix H (FIG. 10). ) Is a table representing the position of one element for each 360 columns (unit size P), and is created in advance for each check matrix H of each code length N and each coding rate r.

- the parity check matrix initial value table represents at least the position of one element of the information matrix HA for every 360 columns (unit size P).

- parity check matrix H specified by DVB-T.2 etc. in which the parity matrix H T (all of them) has a staircase structure, and the parity matrix H proposed by CRC / ETRI are included in the parity check matrix H.

- a parity check matrix in which a part of T has a staircase structure and the remaining part is a diagonal matrix (unit matrix).

- the parity matrix H T is an expression scheme of the parity check matrix initial value table representative of the parity check matrix having a staircase structure, known as DVB scheme, CRC / ETRI Inc. proposed A representation method of a parity check matrix initial value table representing a parity check matrix to be performed is also referred to as an ETRI method.

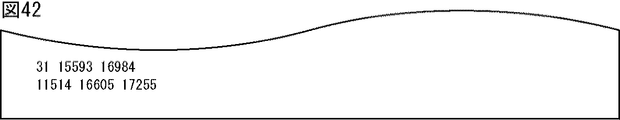

- FIG. 20 is a diagram illustrating an example of a DVB check matrix initial value table.

- FIG. 20 shows that the code length N is 16200 bits and the coding rate (coding rate in the notation of DVB-T.2) r is 1/4 as defined in the DVB-T.2 standard.

- the parity check matrix initial value table for the parity check matrix H is shown.

- the parity check matrix generator 613 obtains the parity check matrix H as follows using the DVB parity check matrix initial value table.

- FIG. 21 is a diagram for explaining a method of obtaining a parity check matrix H from a DVB parity check matrix initial value table.

- FIG. 21 shows a parity check matrix initial value table for a parity check matrix H prescribed in the DVB-T.2 standard and having a code length N of 16200 bits and a coding rate r of 2/3.

- the DVB parity check matrix initial value table has 360 columns (unit size P) of the position of the entire element of the information matrix HA corresponding to the information length K corresponding to the code length N and coding rate r of the LDPC code. ) In the i-th row, the row number of the 1 element of the 1 + 360 ⁇ (i ⁇ 1) column of the parity check matrix H (the row number of the first row of the parity check matrix H is 0). Row number) are arranged by the number of column weights of the 1 + 360 ⁇ (i ⁇ 1) th column.

- the parity matrix H T (FIG. 10) corresponding to the parity length M of the DVB parity check matrix H is determined in a staircase structure as shown in FIG. If the information matrix H A (FIG. 10) corresponding to the length K can be obtained, the check matrix H can be obtained.

- the number of rows k + 1 in the DVB parity check matrix initial value table differs depending on the information length K.

- Equation (9) The relationship of Equation (9) is established between the information length K and the number k + 1 of rows in the parity check matrix initial value table.

- 360 in equation (9) is the unit size P described in FIG.

- the column weights of the parity check matrix H obtained from the parity check matrix initial value table of FIG. 21 are 13 from the first column to the 1 + 360 ⁇ (3-1) ⁇ 1 column, and 1 + 360 ⁇ (3-1) It is 3 from the column to the Kth column.

- the first row of the parity check matrix initial value table in FIG. 21 is 0,2084,1613,1548,1286,1460,3196,4297,2481,3369,3451,4620,2622, which is the parity check matrix H

- the row number is 0,2084,1613,1548,1286,1460,3196,4297,2481,3369,3451,4620,2622

- the element of the row is 1 (and other elements) Is 0).

- the second row of the parity check matrix initial value table in FIG. 21 is 1,122,1516,3448,2880,1407,1847,3799,3529,373,971,4358,3108, which is 361 of the parity check matrix H.

- the row number is 1,122,1516,3448,2880,1407,1847,3799,3529,373,971,4358,3108 and the element is 1 ing.

- the parity check matrix initial value table represents the position of one element of the information matrix HA of the parity check matrix H for every 360 columns.

- the numerical value of the i-th row (i-th from the top) and j-th column (j-th from the left) of the parity check matrix initial value table is represented as h i, j and j items in the w-th column of the parity check matrix H. If the row number of the first element is represented as H wj , the row number H of the first element in the w column, which is a column other than the 1 + 360 ⁇ (i ⁇ 1) column of the parity check matrix H wj can be obtained by Expression (10).

- mod (x, y) means the remainder of dividing x by y.

- the parity check matrix generation unit 613 (FIG. 18) specifies the row number of the 1 element in the 1 + 360 ⁇ (i ⁇ 1) column of the parity check matrix H by using the parity check matrix initial value table.

- the parity check matrix generation unit 613 calculates the row number H wj of the first element of the w-th column other than the 1 + 360 ⁇ (i ⁇ 1) -th column of the parity check matrix H by the formula ( 10) to generate a parity check matrix H in which the element of the row number obtained as described above is 1.

- FIG. 22 is a diagram showing the structure of an ETRI check matrix.

- the ETRI check matrix consists of A matrix, B matrix, C matrix, D matrix, and Z matrix.

- the B matrix is a matrix with a staircase structure adjacent to the right of the A matrix, with g rows and g columns.

- the C matrix is a matrix adjacent to the N-K-g rows and K + g columns below the A matrix and the B matrix.

- the D matrix is an N-K-g row N-K-g column unit matrix adjacent to the right of the C matrix.

- the Z matrix is a zero matrix (0 matrix) adjacent to the right of the B matrix with g rows and N-K-g columns.

- ETRI check matrix composed of the A matrix, D matrix, and Z matrix as described above

- a part of the A matrix and the C matrix constitutes an information matrix

- the B matrix and the C matrix constitute a parity matrix.

- the B matrix is a staircase matrix and the D matrix is a unit matrix

- a part of the parity matrix of the ETRI check matrix (part of the B matrix) has a staircase structure, and the rest

- the part (D matrix part) is a diagonal matrix (unit matrix).

- the A matrix and the C matrix have a cyclic structure for every 360 columns (unit size P), similar to the information matrix of the DVB check matrix, and the ETRI check matrix initial value table includes the A matrix and the C matrix. Represents the position of one element of every 360 columns.

- the initial check matrix of the ETRI system that represents the position of one element of the A matrix and the C matrix every 360 columns It can be said that the value table represents at least the position of one element of the information matrix for every 360 columns.

- FIG. 23 is a diagram illustrating an example of an ETRI check matrix initial value table.

- FIG. 23 shows an example of a parity check matrix initial value table for a parity check matrix having a code length N of 50 bits and an encoding rate r of 1/2.

- the ETRI parity check matrix initial value table is a table that represents the position of one element of the A matrix and the C matrix for each unit size P.

- the number of the column weight of the 1 + P ⁇ (i-1) column is the row number of the first element in the column (the row number where the first row number in the parity check matrix is 0). Just lined up.

- the unit size P is assumed to be 5, for example.

- the performance of the LDPC code changes, when determining the check matrix is adjusted to a predetermined value.

- M 2 takes a value MM 1 obtained by subtracting M 1 from the parity length M.

- the parity check matrix initial value table in FIG. 23 three numerical values are arranged in the first and second rows, and one numerical value is arranged in the third to fifth rows.

- the column weights of the parity check matrix obtained from the parity check matrix initial value table in FIG. 23 are 3 from the first column to the 1 + 5 ⁇ (2-1) ⁇ 1 column, and 1 + 5 ⁇ ( 2-1) It is 1 from the fifth column to the fifth column.

- the first row of the parity check matrix initial value table of FIG. 23 is 2,6,18. This is because the elements of the rows whose row numbers are 2,6,18 in the first column of the parity check matrix. Is 1 (and other elements are 0).

- the A matrix is a matrix of 15 rows and 25 columns (g rows and K columns), and the C matrix is a matrix of 10 rows and 40 columns (NKg rows and K + g columns).

- the row numbers 0 to 14 are rows of the A matrix, and the row numbers 15 to 24 of the parity check matrix are the rows of the C matrix.

- rows # 2, # 6, and # 18 are rows of the A matrix

- rows # 18 is the C matrix row.

- rows # 2, # 10 of rows # 2, # 10, # 19 are rows of the A matrix.

- Line # 19 is a C matrix row.

- row # 22 is a row of the C matrix.

- the 2 + 5 ⁇ (i-1) column is cyclically shifted downward by Q 1 ).

- the 2 + 5 ⁇ (i-1) column is cyclically shifted downward by Q 2 ).

- FIG. 24 is a diagram showing an A matrix generated from the parity check matrix initial value table of FIG.

- FIG. 25 is a diagram showing parity interleaving of the B matrix.

- FIG. 25 shows the A matrix and the B matrix after parity interleaving of the B matrix.

- FIG. 26 is a diagram showing a C matrix generated from the parity check matrix initial value table of FIG.

- the element in row # 15 of the column is 1.

- the parity check matrix generation unit 613 (FIG. 18) generates a C matrix using the parity check matrix initial value table, and places the C matrix below the A matrix and the B matrix (after parity interleaving).

- check matrix generation unit 613 arranges the Z matrix to the right of the B matrix and arranges the D matrix to the right of the C matrix to generate the check matrix shown in FIG.

- FIG. 27 is a diagram showing parity interleaving of the D matrix.

- FIG. 27 shows the parity check matrix after parity interleaving of the D matrix for the parity check matrix in FIG.

- the LDPC encoder 115 (the encoded parity calculation unit 615 (FIG. 18)) performs LDPC encoding (LDPC code generation) using, for example, the parity check matrix of FIG.

- the LDPC code generated using the parity check matrix of FIG. 27 is an LDPC code subjected to parity interleaving. Therefore, the LDPC code generated using the parity check matrix of FIG. It is not necessary to perform parity interleaving in the leaver 23 (FIG. 9).

- FIG. 28 shows parity for returning parity interleaving to the B matrix, a part of the C matrix (part of the C matrix arranged below the B matrix), and the D matrix of the parity check matrix of FIG. It is a figure which shows the test matrix which performed column permutation (column

- the LDPC encoder 115 can perform LDPC encoding (generation of an LDPC code) using the parity check matrix of FIG.

- FIG. 29 is a diagram illustrating a conversion parity check matrix obtained by performing row permutation on the parity check matrix of FIG.

- the conversion parity check matrix is a P ⁇ P unit matrix, a quasi-unit matrix in which one or more of the unit matrices become 0, a shift matrix obtained by cyclically shifting the unit matrix or the quasi-unit matrix, It is a matrix represented by a combination of a sum matrix that is a sum of two or more of a unit matrix, a quasi-unit matrix, or a shift matrix, and a P ⁇ P 0 matrix.

- ATSC3.0 a standard for terrestrial digital television broadcasting

- a new LDPC code (hereinafter also referred to as a new LDPC code) that can be used in ATSC 3.0 and other data transmission will be described.

- the unit size P is 360, which is the same as DVB-T.2 etc., and adopts the DVPC LDPC code and ETRI LDPC code corresponding to the check matrix of cyclic structure Can do.

- the LDPC encoder 115 (FIGS. 8 and 18) has a code length N of 16k bits or 64k bits and a coding rate r of 5/15, 6, 15, 7/15, 8/15, 9 as follows. LDPC to the new LDPC code using the parity check matrix obtained from the parity check matrix initial value table of the new LDPC code of / 15, 10/15, 11/15, 12/15, or 13/15 Encoding can be performed.

- a check matrix initial value table of the new LDPC code is stored in the storage unit 602 of the LDPC encoder 115 (FIG. 8).