WO2012017648A1 - Plasma display panel driving method and plasma display apparatus - Google Patents

Plasma display panel driving method and plasma display apparatus Download PDFInfo

- Publication number

- WO2012017648A1 WO2012017648A1 PCT/JP2011/004389 JP2011004389W WO2012017648A1 WO 2012017648 A1 WO2012017648 A1 WO 2012017648A1 JP 2011004389 W JP2011004389 W JP 2011004389W WO 2012017648 A1 WO2012017648 A1 WO 2012017648A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- voltage

- discharge

- electrode

- sustain

- gradation value

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/28—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels

- G09G3/288—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels

- G09G3/291—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels controlling the gas discharge to control a cell condition, e.g. by means of specific pulse shapes

- G09G3/293—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels controlling the gas discharge to control a cell condition, e.g. by means of specific pulse shapes for address discharge

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/28—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels

- G09G3/288—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels

- G09G3/291—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels controlling the gas discharge to control a cell condition, e.g. by means of specific pulse shapes

- G09G3/294—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels controlling the gas discharge to control a cell condition, e.g. by means of specific pulse shapes for lighting or sustain discharge

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0238—Improving the black level

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/041—Temperature compensation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2044—Display of intermediate tones using dithering

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/28—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels

- G09G3/288—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using luminous gas-discharge panels, e.g. plasma panels using AC panels

- G09G3/296—Driving circuits for producing the waveforms applied to the driving electrodes

- G09G3/2965—Driving circuits for producing the waveforms applied to the driving electrodes using inductors for energy recovery

Definitions

- the present invention relates to an AC surface discharge type plasma display panel driving method and a plasma display apparatus.

- a typical plasma display panel (hereinafter abbreviated as “panel”) as a display device has a large number of discharge cells formed between a front substrate and a rear substrate arranged to face each other.

- a plurality of pairs of display electrodes composed of a pair of scan electrodes and sustain electrodes are formed on the front glass substrate in parallel with each other.

- a dielectric layer and a protective layer are formed so as to cover the display electrode pairs.

- the back substrate has a plurality of parallel data electrodes formed on the glass substrate on the back side, a dielectric layer is formed so as to cover the data electrodes, and a plurality of barrier ribs are formed thereon in parallel with the data electrodes. ing. And the fluorescent substance layer is formed in the surface of a dielectric material layer, and the side surface of a partition.

- the front substrate and the rear substrate are arranged opposite to each other and sealed so that the display electrode pair and the data electrode are three-dimensionally crossed.

- a discharge gas containing xenon at a partial pressure ratio of 5% is sealed, and a discharge cell is formed in a portion where the display electrode pair and the data electrode face each other.

- ultraviolet rays are generated by gas discharge in each discharge cell, and the phosphors of each color of red (R), green (G) and blue (B) are excited and emitted by the ultraviolet rays. Display an image.

- the subfield method is generally used as a method for driving the panel.

- one field is divided into a plurality of subfields, and light emission and non-light emission of each discharge cell are controlled in each subfield.

- gradation display is performed by controlling the number of times of light emission generated in one field.

- Each subfield has an initialization period, an address period, and a sustain period.

- an initialization waveform is applied to each scan electrode, and an initialization operation is performed to generate an initialization discharge in each discharge cell.

- wall charges necessary for the subsequent address operation are formed, and priming particles (excited particles for generating the discharge) for generating the address discharge stably are generated.

- Initializing operation includes forced initializing operation that generates initializing discharge in each discharge cell regardless of the operation of the previous subfield, and initializing discharge is generated only in the discharge cell that has generated address discharge in the immediately preceding subfield. There is a selective initialization operation to do.

- an address discharge is selectively generated in the discharge cells according to the image to be displayed, and an address operation is performed to form wall charges in the discharge cells.

- scan pulses are sequentially applied to the scan electrodes, and address pulses are selectively applied to the data electrodes based on the image signal to be displayed. Thereby, an address discharge is generated between the scan electrode and the data electrode of the discharge cell to emit light, and a wall charge is formed in the discharge cell.

- the sustain pulses of the number based on the luminance weight determined for each subfield are alternately applied to the display electrode pairs composed of the scan electrodes and the sustain electrodes, and the sustain discharge is generated in the discharge cells that have generated the address discharge.

- the sustaining operation for causing the phosphor layer of the discharge cell to emit light is performed (hereinafter, the discharge cell is caused to emit light by the sustain discharge is also referred to as “lighting” and the light emission is not referred to as “non-lighting”).

- each discharge cell is made to emit light with the luminance according to the luminance weight.

- the light emission of the phosphor layer due to the sustain discharge is light emission related to gradation display, and the other light emission is light emission not related to gradation display.

- each discharge cell of the panel is caused to emit light with a luminance corresponding to the gradation value of the image signal, and an image is displayed in the image display area of the panel.

- One of the important factors in improving the image display quality on the panel is the improvement in contrast.

- light emission not related to gradation display is reduced as much as possible, the luminance when displaying the lowest gradation (black gradation value “0”) is reduced, and the contrast ratio is improved.

- a driving method is disclosed.

- the forced initialization operation is performed using a gradually changing ramp waveform voltage.

- the forced initializing operation is performed in the initializing period of one subfield, and the selective initializing operation is performed in the initializing period of the other subfield. In this way, the number of times of forced initialization operation is set to once per field.

- black luminance The luminance of the black display area where no sustain discharge occurs (hereinafter abbreviated as “black luminance”) varies depending on light emission not related to image display, for example, light emission caused by initialization discharge.

- light emission in the black display region is only weak light emission when the initialization operation is performed on all the discharge cells. Thereby, it is possible to reduce the black luminance and display an image with high contrast (see, for example, Patent Document 1).

- the number of forced initialization operations per unit time (for example, 1 second) can be reduced and the black luminance can be further decreased as compared with the driving method described in Patent Document 1. it can.

- the wall charge necessary for generating the address discharge in the subsequent address period is accumulated in the discharge cell, and the discharge delay time is shortened to surely generate the address discharge.

- the discharge delay time is the time required from when the voltage applied to the discharge cell exceeds the discharge start voltage until the actual discharge occurs. The longer the discharge delay time, the more unstable the generation of discharge.

- the address discharge operation becomes unstable due to a long discharge delay time of the address discharge, or a malfunction such as no address discharge occurs, resulting in normal image display. become unable.

- the present invention is a panel driving method for driving a panel having a plurality of discharge cells each having a scan electrode, a sustain electrode, and a data electrode.

- a single field is formed by using a plurality of subfields each having an address period, a sustain period, and an erase period.

- a scan pulse is applied to the scan electrode and an address pulse is applied to the data electrode. This is applied to selectively generate an address discharge in the discharge cell, and in the sustain period, sustain pulses of the number corresponding to the luminance weight are alternately applied to the scan electrode and the sustain electrode to maintain the address discharge in the discharge cell.

- a ramp waveform voltage is applied to the scan electrode, and an erasing discharge is selectively generated only in the discharge cells in which the address discharge is generated in the immediately preceding address period.

- the voltage obtained by subtracting the voltage applied to the data electrode from the low-voltage side voltage of the sustain pulse applied to the scan electrode during the sustain period is defined as the first voltage, and the data is obtained from the high-voltage side voltage of the sustain pulse applied to the scan electrode during the sustain period

- the voltage obtained by subtracting the voltage applied to the electrode is the second voltage

- the voltage obtained by subtracting the low voltage side voltage of the write pulse applied to the data electrode from the low voltage side voltage of the scan pulse applied to the scan electrode in the write period is the third voltage.

- the voltage applied to each electrode is set so that the voltage obtained by subtracting the third voltage from the first voltage is equal to or higher than the discharge start voltage of the discharge using the data electrode as an anode and the scan electrode as a cathode.

- a voltage obtained by subtracting the third voltage from the second voltage is a discharge start voltage of discharge using the data electrode as an anode and the scan electrode as a cathode, and the data electrode as a cathode and the scan electrode as an anode.

- the discharge start voltage of the discharge to the sum following sets the voltage applied to the electrodes.

- the input image signal is amplified at a predetermined amplification factor and an image is displayed on the panel. At this time, an input image signal less than a predetermined size is amplified with an amplification factor equal to or higher than an amplification factor for an input image signal having a predetermined size or more.

- the panel driving method of the present invention it is desirable to increase the amplification factor as the input image signal becomes smaller for an input image signal less than a predetermined size.

- the predetermined size may be a size in which only the subfield having the smallest luminance weight in one field emits light and the other subfields do not emit light.

- the temperature of the panel is detected and the detected temperature is compared with a preset temperature threshold value.

- the detected temperature is You may enlarge the amplification factor regarding the input image signal below a predetermined magnitude

- the cumulative operation time of the panel is measured and the measured cumulative operation time is compared with a preset cumulative time threshold value.

- the amplification factor relating to an input image signal having a size less than a predetermined magnitude may be larger than when the cumulative operation time is less than the cumulative time threshold.

- the present invention is a plasma display device including a panel including a plurality of discharge cells each having a scan electrode, a sustain electrode, and a data electrode, and a drive circuit that drives the panel and displays an image on the panel.

- the drive circuit forms a single field using a plurality of subfields having an address period, a sustain period, and an erase period, and applies a scan pulse to the scan electrode and an address pulse to the data electrode in the address period. Then, an address discharge is selectively generated in the discharge cell, and in the sustain period, a sustain pulse of the number corresponding to the luminance weight is alternately applied to the scan electrode and the sustain electrode to sustain the discharge cell in which the address discharge is generated.

- an erasing discharge is selectively generated only in the discharge cells in which the ramp waveform voltage is applied to the scan electrodes and the address discharge is generated in the immediately preceding address period. Then, the drive circuit sets the voltage obtained by subtracting the voltage applied to the data electrode from the low-voltage side voltage of the sustain pulse applied to the scan electrode during the sustain period as the first voltage, and sets the high voltage of the sustain pulse applied to the scan electrode during the sustain period.

- the voltage obtained by subtracting the voltage applied to the data electrode from the side voltage is the second voltage, and the voltage obtained by subtracting the low voltage side voltage of the write pulse applied to the data electrode from the low voltage side voltage of the scan pulse applied to the scan electrode in the write period Is applied to each electrode so that the voltage obtained by subtracting the third voltage from the first voltage is equal to or higher than the discharge start voltage of the discharge having the data electrode as the anode and the scan electrode as the cathode.

- the voltage obtained by subtracting the third voltage from the second voltage is the discharge start voltage of the discharge using the data electrode as the anode and the scan electrode as the cathode and the data electrode as the cathode.

- Electrodes to set the voltage applied to each electrode so that the following sum of the discharge start voltage of the discharge of the anode. Then, the drive circuit amplifies the input image signal with a predetermined amplification factor and displays an image on the panel. At this time, an input image signal less than a predetermined size is amplified with an amplification factor equal to or higher than an amplification factor for an input image signal having a predetermined size or more.

- the drive circuit increases the amplification factor as the input image signal becomes smaller for the input image signal less than a predetermined size.

- the drive circuit includes a temperature detection circuit that detects the temperature of the panel, compares the temperature detected by the temperature detection circuit with a preset temperature threshold value, and the detected temperature is the temperature.

- the amplification factor related to the input image signal less than the predetermined magnitude may be set larger than when the detected temperature is equal to or higher than the temperature threshold value.

- the drive circuit includes a cumulative operation time measurement circuit that measures the cumulative operation time of the panel, and a cumulative time threshold value that is preset with the cumulative operation time measured by the cumulative operation time measurement circuit.

- the cumulative operation time is equal to or greater than the cumulative time threshold

- the amplification factor for the input image signal less than the predetermined magnitude may be larger than when the cumulative operation time is less than the cumulative time threshold.

- FIG. 1 is an exploded perspective view showing a structure of a panel used in a plasma display device according to an embodiment of the present invention.

- FIG. 2 is an electrode array diagram of a panel used in the plasma display device according to one embodiment of the present invention.

- FIG. 3 is a diagram schematically showing a drive voltage waveform applied to each electrode of the panel used in the plasma display device according to one embodiment of the present invention.

- FIG. 4 is a waveform diagram schematically showing voltage waveforms applied to scan electrodes and data electrodes in one subfield in one embodiment of the present invention.

- FIG. 5 is a diagram illustrating an example of a method for simply measuring the discharge start voltage.

- FIG. 1 is an exploded perspective view showing a structure of a panel used in a plasma display device according to an embodiment of the present invention.

- FIG. 2 is an electrode array diagram of a panel used in the plasma display device according to one embodiment of the present invention.

- FIG. 3 is a diagram schematically showing a drive voltage waveform applied to each electrode of the

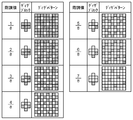

- FIG. 6A is a diagram schematically showing an example of a dither pattern used for dither processing in the plasma display apparatus according to one embodiment of the present invention.

- FIG. 6B is a diagram schematically showing another example of a dither pattern used for dither processing in the plasma display apparatus according to one embodiment of the present invention.

- FIG. 6C is a diagram schematically showing still another example of the dither pattern used for the dither processing in the plasma display device in accordance with the exemplary embodiment of the present invention.

- FIG. 7 is a circuit block diagram of the plasma display device according to one embodiment of the present invention.

- FIG. 8 is a diagram schematically showing an operation in the low luminance amplifier circuit of the plasma display device in accordance with the exemplary embodiment of the present invention.

- FIG. 10A is a diagram showing an example of the amplification factor for the input signal in the first correction in the embodiment of the present invention.

- FIG. 10B is a diagram showing an example of the amplification factor for the input signal in the second correction according to the embodiment of the present invention.

- FIG. 10C is a diagram showing an example of the amplification factor for the input signal in the third correction according to the embodiment of the present invention.

- FIG. 10D is a diagram showing an example of the amplification factor for the input signal in the fourth correction in the embodiment of the present invention.

- FIG. 11 shows the temperature detected by the temperature detection circuit and the accumulated operation time measured by the accumulated operation time measurement circuit and the first correction, the second correction, the third correction, It is a figure which shows the relationship with correction

- FIG. 12 is a circuit diagram schematically showing a configuration of a scan electrode driving circuit of the plasma display device in accordance with the exemplary embodiment of the present invention.

- FIG. 13 is a circuit diagram schematically showing a configuration of a sustain electrode driving circuit of the plasma display device in accordance with the exemplary embodiment of the present invention.

- FIG. 14 is a circuit diagram schematically showing a configuration of a data electrode driving circuit of the plasma display device in accordance with the exemplary embodiment of the present invention.

- FIG. 1 is an exploded perspective view showing the structure of panel 10 used in the plasma display device according to one embodiment of the present invention.

- a plurality of display electrode pairs 24 each including a scanning electrode 22 and a sustaining electrode 23 are formed on a glass front substrate 21.

- a dielectric layer 25 is formed so as to cover the scan electrode 22 and the sustain electrode 23, and a protective layer 26 is formed on the dielectric layer 25.

- This protective layer 26 is made of a material using magnesium oxide (MgO) having high electron emission performance and excellent durability in order to easily generate discharge by lowering the discharge start voltage in the discharge cell.

- MgO magnesium oxide

- a plurality of data electrodes 32 are formed on the rear substrate 31, a dielectric layer 33 is formed so as to cover the data electrodes 32, and a grid-like partition wall 34 is formed thereon.

- a phosphor layer 35R that emits red (R)

- a phosphor layer 35G that emits green (G)

- a phosphor layer 35B that emits blue (B).

- the phosphor layer 35R, the phosphor layer 35G, and the phosphor layer 35B are collectively referred to as a phosphor layer 35.

- the red phosphor for example, a phosphor mainly composed of (Y, Gd) BO 3 : Eu is used, and as the green phosphor, for example, Zn 2 SiO 4 : Mn is mainly composed.

- a phosphor mainly composed of BaMgAl 10 O 17 : Eu is used as the blue phosphor.

- the phosphor forming the phosphor layer 35 is not limited to the above-described phosphor.

- the front substrate 21 and the rear substrate 31 are arranged to face each other so that the display electrode pair 24 and the data electrode 32 intersect with each other with a minute discharge space interposed therebetween. And the outer peripheral part is sealed with sealing materials, such as glass frit. Then, for example, a mixed gas of neon and xenon is sealed in the discharge space inside as a discharge gas.

- the discharge space is partitioned into a plurality of sections by partition walls 34, and discharge cells are formed at the intersections between the display electrode pairs 24 and the data electrodes 32.

- discharge is generated in these discharge cells, and the phosphor layer 35 of the discharge cells emits light (lights the discharge cells), thereby displaying a color image on the panel 10.

- One pixel is composed of three discharge cells that emit blue (B) light.

- the structure of the panel 10 is not limited to that described above.

- the rear substrate 31 may include a stripe-shaped partition wall.

- FIG. 2 is an electrode array diagram of panel 10 used in the plasma display device according to one embodiment of the present invention.

- the panel 10 includes n scan electrodes SC1 to SCn (scan electrode 22 in FIG. 1) extended in the horizontal direction (row direction) and n sustain electrodes SU1 to SUn (sustain electrodes in FIG. 1). 23) are arranged, and m data electrodes D1 to Dm (data electrodes 32 in FIG. 1) extending in the vertical direction (column direction) are arranged.

- a green phosphor is applied as a phosphor layer 35G to a discharge cell having a blue color

- a blue phosphor is applied as a phosphor layer 35B to a discharge cell having a data electrode Dp + 2.

- the plasma display device in the present embodiment drives the panel 10 by the subfield method.

- the subfield method one field is divided into a plurality of subfields on the time axis, and a luminance weight is set for each subfield. Therefore, each field has a plurality of subfields.

- An image is displayed on the panel 10 by controlling light emission / non-light emission of each discharge cell for each subfield.

- the luminance weight represents a ratio of the luminance magnitudes displayed in each subfield, and the number of sustain pulses corresponding to the luminance weight is generated in the sustain period in each subfield. Therefore, for example, the subfield with the luminance weight “8” emits light with a luminance about eight times that of the subfield with the luminance weight “1”, and emits light with about four times the luminance of the subfield with the luminance weight “2”. Therefore, by selectively causing each subfield to emit light in a combination corresponding to an image signal, various gradations can be displayed on the panel 10 and an image can be displayed.

- each subfield has a write period, a sustain period, and an erase period.

- the forced initialization operation is not performed.

- the forced initializing operation is an initializing operation that forcibly generates an initializing discharge in a discharge cell regardless of whether or not there has been a discharge so far.

- a scan pulse is applied to the scan electrode 22 and an address pulse (data pulse) is selectively applied to the data electrode 32 to perform an address operation that selectively generates an address discharge in the discharge cells to emit light.

- an address pulse data pulse

- wall charges for generating a sustain discharge in the subsequent sustain period are formed in the discharge cell.

- the number of sustain pulses obtained by multiplying the luminance weight of each subfield by a predetermined proportional constant is alternately applied to the scan electrode 22 and the sustain electrode 23.

- This proportionality constant is the luminance magnification.

- the sustain pulse is applied to the scan electrode 22 and the sustain electrode 23 four times in the sustain period of the subfield having the luminance weight “2”. Therefore, the number of sustain pulses generated in the sustain period is 8.

- a sustain discharge is generated in the discharge cell that has generated the address discharge in the immediately preceding address period, and the discharge cell emits light.

- the operation of applying the sustain pulse to the discharge cell and emitting the discharge is the sustain operation.

- a subfield in which the sustain period is omitted may be provided in order to keep the emission luminance low.

- an erasing discharge is generated only in the discharge cells that have generated the address discharge in the address period of the subfield to which the erasing period belongs. Therefore, this erasing discharge is selectively generated only in the discharge cells that have generated the address discharge.

- this erasing discharge is generated, wall charges formed by the address discharge or the subsequent sustain discharge are erased, and wall charges necessary for the address discharge in the subsequent subfield are formed on each electrode.

- these operations are also referred to as “erase operations”.

- one field is divided into 10 subfields (SF1, SF2,..., SF10), and each subfield is (1, 2, 3, 6, 11, 18, 30). , 44, 60, 80).

- the number of subfields and the luminance weight of each subfield are not limited to the above values.

- the structure which switches the structure of a subfield based on an image signal etc. may be sufficient.

- FIG. 3 is a diagram schematically showing drive voltage waveforms applied to the respective electrodes of panel 10 used in the plasma display device according to one embodiment of the present invention.

- FIG. 3 shows scan electrode SC1 that performs the address operation first in the address period, scan electrode SCn that performs the address operation last in the address period, sustain electrode SU1 to sustain electrode SUn, and data electrode D1 to data electrode Dm.

- the drive voltage waveform to be applied is shown.

- Scan electrode SCi, sustain electrode SUi, and data electrode Dk in the following represent electrodes selected based on image data (data indicating light emission / non-light emission for each subfield) from among the electrodes.

- FIG. 3 mainly shows drive voltage waveforms in three subfields, that is, subfield SF1, subfield SF2, and subfield SF3.

- voltage 0 (V) is applied to data electrode D1 to data electrode Dm

- voltage Ve is applied to sustain electrode SU1 to sustain electrode SUn

- scan electrode SC1 to scan electrode SCn are applied to scan electrode SC1.

- a voltage Vc is applied.

- a scan pulse having a negative voltage Va is applied to the scan electrode SC1 in the first row where the address operation is first performed.

- an address pulse of a positive voltage Vd is applied to the data electrode Dk corresponding to the discharge cell that should emit light in the first row of the data electrodes D1 to Dm.

- the voltage difference at the intersection between the data electrode Dk of the discharge cell to which the address pulse of the voltage Vd is applied and the scan electrode SC1 is the difference between the externally applied voltage (voltage Vd ⁇ voltage Va) and the wall voltage on the data electrode Dk and the scan electrode.

- the difference from the wall voltage on SC1 is added.

- the voltage difference between data electrode Dk and scan electrode SC1 exceeds discharge start voltage VFds, and a discharge is generated between data electrode Dk and scan electrode SC1.

- the voltage difference between sustain electrode SU1 and scan electrode SC1 is the difference between the externally applied voltages (voltage Ve ⁇ voltage Va), and sustain electrode SU1.

- the difference between the upper wall voltage and the wall voltage on the scan electrode SC1 is added.

- the sustain electrode SU1 and the scan electrode SC1 are not easily discharged but are likely to be discharged. Can do.

- a discharge is generated between the sustain electrode SU1 and the scan electrode SC1 in a region intersecting the data electrode Dk, induced by a discharge generated between the data electrode Dk and the scan electrode SC1.

- address discharge is generated in the discharge cells (discharge cells to emit light) to which the scan pulse and address pulse are simultaneously applied.

- positive wall voltage is accumulated on scan electrode SC1

- negative wall voltage is accumulated on sustain electrode SU1

- negative wall voltage is also accumulated on data electrode Dk. Is done.

- the wall voltage on the electrode represents a voltage generated by wall charges accumulated on the dielectric layer 25 covering the electrode, the protective layer 26, the phosphor layer 35, and the like.

- a scan pulse is applied to the scan electrode SC2 in the second row, and an address pulse is applied to the data electrode Dk corresponding to the discharge cell to emit light in the second row.

- an address discharge is generated between data electrode Dk and scan electrode SC2 and between sustain electrode SU2 and scan electrode SC2, a positive wall voltage is accumulated on scan electrode SC2, and a negative voltage is applied on sustain electrode SU2. And a negative wall voltage is also accumulated on the data electrode Dk.

- the voltage at the intersection between the data electrode Dh and the scan electrode SC2 to which no address pulse is applied does not exceed the discharge start voltage VFds, no address discharge occurs. In this way, an address operation is performed in which an address discharge is generated in the discharge cells that should emit light in the second row, and a wall voltage is accumulated on each electrode.

- the same addressing operation is performed by scanning electrode SC3 in the third row, scanning electrode SC4 in the fourth row,..., Scanning electrode SC (n ⁇ 1) in the (n ⁇ 1) th row, scanning in the nth row.

- the process is sequentially performed from the discharge cell in the third row to the discharge cell in the nth row in the order of the electrode SCn, and the address period of the subfield SF1 is completed.

- the first voltage V1, the second voltage V2, and the third voltage V3 are defined as follows.

- FIG. 4 is a waveform diagram schematically showing voltage waveforms applied to scan electrode 22 and data electrode 32 in one subfield in one embodiment of the present invention.

- a voltage obtained by subtracting the voltage 0 (V)) is defined as a third voltage V3.

- the discharge start voltage VFds is the discharge start voltage in the address period in which the data electrode Dj is the anode and the scan electrode SCi is the cathode

- the discharge start voltage is the discharge start voltage in the sustain period in which the data electrode Dj is the cathode and the scan electrode SCi is the anode.

- the voltage is VFsd.

- the discharge with the data electrode Dj as the anode and the scan electrode SCi as the cathode is a discharge in which the electric field in the discharge cell when the discharge occurs is a high potential side on the data electrode Dj side and a low potential side on the scan electrode SCi side. It is.

- the discharge with the data electrode Dj as the cathode and the scan electrode SCi as the anode is a discharge in which the electric field in the discharge cell when the discharge occurs is a low potential side on the data electrode Dj side and a high potential side on the scan electrode SCi side. is there.

- the protective layer 26 of magnesium oxide having high electron emission performance is formed on the front substrate 21 with the scan electrode SCi, the discharge start voltage VFds is lower than the discharge start voltage VFsd.

- the voltage Va of the scan pulse applied to the scan electrode SCi is set so as to satisfy the following two conditions (condition 1) and (condition 2).

- a voltage obtained by subtracting the third voltage V3 from the second voltage V2 is a discharge start voltage VFds of discharge using the data electrode Dj as an anode and the scan electrode SCi as a cathode.

- the discharge start voltage VFsd of the discharge having the data electrode Dj as the cathode and the scan electrode SCi as the anode is, (V2 ⁇ V3) ⁇ (VFds + VFsd) It is.

- the voltage difference between the scan electrode SCi and the sustain electrode SUi causes the voltage Vs of the sustain pulse to be the wall voltage on the scan electrode SCi and the wall voltage on the sustain electrode SUi. The difference between and is added.

- the voltage difference between scan electrode SCi and sustain electrode SUi exceeds discharge start voltage VFss, and a sustain discharge is generated between scan electrode SCi and sustain electrode SUi.

- the fluorescent substance layer 35 light-emits with the ultraviolet-ray which generate

- negative wall voltage is accumulated on scan electrode SCi

- positive wall voltage is accumulated on sustain electrode SUi.

- a positive wall voltage is also accumulated on the data electrode Dk.

- sustain pulses of the number obtained by multiplying the luminance weight by a predetermined luminance magnification are alternately applied to scan electrode SC1 through scan electrode SCn and sustain electrode SU1 through sustain electrode SUn.

- the sustain discharge is continuously generated in the discharge cells in which the address discharge is generated in the address period.

- voltage 0 (V) is gradually increased from voltage 0 (V) to voltage Vr while voltage 0 (V) is applied to sustain electrode SU1 through sustain electrode SUn and data electrode D1 through data electrode Dm.

- An upward ramp waveform voltage is applied to scan electrode SC1 through scan electrode SCn.

- the charged particles generated by the erasing discharge are accumulated as wall charges on the sustain electrode SUi and the scan electrode SCi so as to alleviate the voltage difference between the sustain electrode SUi and the scan electrode SCi.

- the wall voltage on scan electrode SCi and sustain electrode SUi is weakened while the positive wall voltage on data electrode Dk remains. That is, unnecessary wall charges in the discharge cells are erased by the erase discharge.

- the voltage Vr is set to the same voltage value as the voltage Vs, but the voltage Vr may be a voltage value different from the voltage Vs.

- the voltage Vr is desirably set to an optimum voltage value according to the characteristics of the panel 10 and the specifications of the plasma display device.

- voltage Ve is applied to sustain electrode SU1 through sustain electrode SUn, and voltage 0 (V) is applied to data electrode D1 through data electrode Dm. Then, a downward ramp waveform voltage that gently falls from voltage 0 (V) to voltage Vi is applied to scan electrode SC1 through scan electrode SCn.

- the voltage Vi is set to be equal to or slightly higher than the voltage Va of the scanning pulse.

- This weak discharge discharges an excessive portion of the wall voltage on the scan electrode SCi, the wall voltage on the sustain electrode SUi, and the wall voltage on the data electrode Dk, and the wall voltage in the discharge cell

- the wall voltage is adjusted to a suitable level.

- erasing that selectively generates erasing discharges in the discharge cells that generated the sustaining discharge in the immediately preceding sustaining period (in the subfield in which the sustaining period is omitted, the discharge cell in which the addressing discharge occurred) Perform the action.

- an erasing discharge is generated only in the discharge cells in which the address discharge is generated in the address period of the subfield to which the erasing period belongs, and in the discharge cells in which the address discharge is not generated. Erase discharge does not occur. Accordingly, in a discharge cell displaying black (gradation value “0”) that does not generate a sustain discharge, neither an initializing discharge, an address discharge, a sustain discharge, nor an erasing discharge is generated. There is no light emission.

- each voltage value is desirably set optimally based on the discharge characteristics of panel 10 and the specifications of the plasma display device.

- the subfield configuration described above is merely an example in the present embodiment, and the present invention is not limited to this subfield configuration. It is desirable to optimally set the number of subfields constituting one field and the luminance weight of each subfield according to the characteristics of the panel and the specifications of the plasma display device.

- the wall voltage on each electrode is shown assuming a reference potential of wall voltage 0 (V) inside the discharge cell space.

- V wall voltage

- the discharge start voltage VFds and the discharge start voltage VFsd of the panel 10 used in the present embodiment are measured by the method described later, and their values are as follows.

- the discharge start voltage varies depending on the phosphor.

- the inventor of the present application measured the panel 10, and in the discharge cell coated with the red phosphor, the discharge start voltage VFds between the “data electrode 32 and the scan electrode 22” was 200 ⁇ 10 (V), and the discharge start voltage was The VFsd was 320 ⁇ 10 (V).

- the discharge start voltage VFds between “data electrode 32 and scan electrode 22” is 220 ⁇ 10 (V), and the discharge start voltage VFsd is 350 ⁇ 10 (V). there were.

- the discharge start voltage VFds between the “data electrode 32 and the scan electrode 22” is 200 ⁇ 10 (V), and the discharge start voltage VFsd is 330 ⁇ 10 (V). there were.

- the discharge start voltage VFss between the “scan electrode 22 and the sustain electrode 23” is 250 ⁇ 10 (V) in the discharge cell coated with the red phosphor and the discharge cell coated with the blue phosphor. It was 280 ⁇ 10 (V) in the discharge cell coated with the phosphor.

- the low-voltage side voltage of the sustain pulse is the voltage 0 (V)

- the voltage applied to the data electrode 32 during the sustain period is the voltage 0 (V)

- the first voltage V1 is the voltage 0. (V).

- the third voltage V3 is the voltage Va ( ⁇ 280 (V)).

- the discharge start voltage VFds is larger in the discharge cell coated with the green phosphor than the other discharge cells, and its maximum value is the voltage 230 (V) in consideration of variation.

- (Condition 1) is (first voltage V1 ⁇ third voltage V3) ⁇ VFds.

- (Maximum value of VFds) 230 (V) It is. That is, (First voltage V1 ⁇ third voltage V3)> (maximum value of VFds)

- (condition 1) is satisfied in all discharge cells.

- the second voltage V2 is the voltage Vs (200 (V)).

- the discharge start voltage VFsd is smaller in the discharge cell coated with the red phosphor than the other discharge cells, and its minimum value is the voltage 310 (V) in consideration of variation.

- the discharge start voltage VFds is smaller in discharge cells coated with red and blue phosphors than other discharge cells, and its minimum value is a voltage 190 (V) in consideration of variation. Therefore, the minimum value of the sum of the discharge start voltage VFsd and the discharge start voltage VFds is the voltage 500 (V).

- a voltage not lower than the voltage Va which is the low voltage side voltage of the scan pulse and not higher than the voltage Vs which is the high voltage side voltage of the sustain pulse is applied to the scan electrode 22.

- a voltage lower than the voltage Va that is the low-voltage side voltage of the scan pulse or a voltage that exceeds the voltage Vs that is the high-voltage side voltage of the sustain pulse is not applied to the scan electrode 22. Therefore, the discharge cells that did not generate the address discharge do not emit light.

- of the voltage Va which is the low-voltage side voltage of the scan pulse is the high-voltage side voltage of the sustain pulse. Is larger than the absolute value

- the drive voltage waveform applied to each electrode, in particular, the voltage Va of the scan pulse is set so as to satisfy (Condition 1) and (Condition 2).

- an erasing discharge is selectively generated only in the discharge cells that have generated the address discharge in the address period of the subfield to which the erasing period belongs.

- the voltage obtained by subtracting the third voltage V3 from the first voltage V1 is equal to or higher than the discharge start voltage VFds (Condition 1), and the second voltage V2 to the third voltage.

- the voltage obtained by subtracting V3 does not exceed the sum of the discharge start voltage VFds and the discharge start voltage VFsd (condition 2).

- address discharge is generated in the discharge cells that should generate address discharge, and address discharge is not generated in discharge cells that should not generate address discharge, even if forced initialization is not performed. Can do. That is, the write operation can be performed stably. The reason is considered as follows.

- the forced initialization operation is not performed in this embodiment. Therefore, in the discharge cell displaying black (gradation value “0”), neither an initializing discharge, an addressing discharge, a sustaining discharge, nor an erasing discharge is generated. Therefore, it is difficult to appropriately control the wall voltage, and the wall voltage of the discharge cell displaying black tends to be unstable.

- the wall voltage is slowly accumulated on the electrodes so as to alleviate the potential difference between the electrodes by the voltages applied to the scan electrodes SCi, the sustain electrodes SUi, and the data electrodes Dj. It will be done.

- the neglected wall voltage when the sustain pulse is alternately applied to the scan electrode SCi and the sustain electrode SUi is It is a voltage between the high voltage and the low voltage.

- the drive voltage waveform other than the sustain pulse is also applied to the discharge cell, it is considered that the neglected wall voltage of each discharge cell is substantially close to the low voltage of the sustain pulse.

- the neglected wall voltage is greatly affected by the charging characteristics of the phosphor applied inside the discharge cell.

- the charging characteristics of the phosphor are +20 ( ⁇ C / g) for the red phosphor, ⁇ 30 ( ⁇ C / g) for the green phosphor, and +10 ( ⁇ C) for the blue phosphor. / G).

- the leaving wall voltage of the discharge cell coated with the green phosphor is lower than that of the discharge cell coated with the red or blue phosphor. .

- the wall voltage is gradually accumulated on the data electrode Dh of the discharge cell displaying black without generating the address discharge, generally toward the low-voltage side voltage of the sustain pulse or the neglected wall voltage higher than that.

- the voltage Va of the scan pulse in the present embodiment is a voltage satisfying (Condition 1). Therefore, a positive wall voltage sufficient to generate the address discharge is accumulated on the data electrode Dh, and the address discharge can be generated in the discharge cells without performing any forced initialization operation.

- the wall voltage of the discharge cell displaying black gradually approaches the left wall voltage.

- a dark current current that flows in a state where no discharge occurs

- the voltage Va of the scan pulse in the address period is particularly (Condition 1).

- the wall voltage necessary for the address discharge can be accumulated in the discharge cell without performing the forced initialization operation before the address period.

- a dark current that plays the role of priming particles for stably generating the address discharge can be generated in the discharge cell.

- each voltage must be set so that the voltage between the “data electrode 32 and the scan electrode 22” becomes equal to or lower than the discharge start voltage VFsd when the sustain pulse voltage Vs is applied. I must. This condition is (Condition 2).

- the drive voltage waveform is set so as to satisfy (Condition 1) and (Condition 2) in all the discharge cells. Therefore, the address discharge can be stably generated even if the forced initialization operation is omitted. As a result, it is possible to display an image without causing light emission not related to gradation display.

- an erase discharge is generated only in the discharge cells in which the address discharge is generated in the address period of the subfield to which the erase period belongs, and the discharge in which the address discharge is not generated. Erase discharge does not occur in the cell. Accordingly, in a discharge cell displaying black (gradation value “0”) that does not generate a sustain discharge, neither an initializing discharge, an address discharge, a sustain discharge, nor an erasing discharge is generated. There is no light emission.

- a stable writing operation can be performed without performing a forced initialization operation, black luminance can be suppressed, and an image with high contrast can be displayed on the panel 10.

- the slope of the rising ramp waveform voltage applied to scan electrode SC1 through scan electrode SCn in the erasing period is 10 (V / ⁇ sec), and the slope of the falling ramp waveform voltage is ⁇ 1.5 (V / ⁇ sec).

- this numerical value is only one example when generating an up-slope waveform voltage and a down-slope waveform voltage, and the present invention does not limit the slope of the up-slope waveform voltage and the down-slope waveform voltage to these values. Absent.

- a weak erasing discharge is repeatedly generated a plurality of times during the erasing period without using the forced initialization operation, and a weak erasing discharge is repeatedly generated several times. Since the wall voltage can be accumulated in the discharge cell and the priming particles can be generated, the address discharge can be stably generated in the subsequent address period.

- discharge start voltage VFsd the discharge start voltage VFds

- the wall voltage can be easily measured, for example, by the method described below.

- FIG. 5 is a diagram showing an example of a method for simply measuring the discharge start voltage.

- the wall charge is erased. Specifically, as shown in the wall charge erasing period of FIG. 5, a pulse voltage Vers sufficiently higher than the expected discharge start voltage is alternately applied between the electrodes to be measured, for example, the data electrode 32 and the scan electrode 22. Apply to.

- a pulsed voltage Vmsr lower than the expected discharge start voltage is applied to one electrode (for example, the data electrode 32). Then, light emission due to the discharge at that time is detected by using a light detection sensor such as a photomultiplier.

- the minimum value of the absolute value of the voltage Vmsr when light emission is observed in the measurement period is the discharge start voltage.

- the discharge start voltage VFds of the discharge with the data electrode 32 as the anode and the scan electrode 22 as the cathode can be measured. Further, when the voltage Vmsr applied in the measurement period is a negative voltage, the discharge start voltage VFsd of the discharge having the data electrode 32 as a cathode and the scan electrode 22 as an anode can be measured.

- the discharge start voltage is known, the voltage at which discharge starts is measured for the discharge cell in which the wall voltage is accumulated, and the wall voltage can be known as the difference between the voltage value and the discharge start voltage measured in advance. .

- the discharge start voltage VFsd, the discharge start voltage VFds, and the wall voltage can be obtained from IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-24, NO. 7, JULY, 1977 “Measurement of a Plasma in the AC Plasma Display panel Usage RF Capacitance and Microwave Techniques”, etc.

- an image is displayed on panel 10 using a subfield method.

- the subfield method one field is composed of a plurality of subfields whose luminance weights are determined in advance, and a subfield that emits light is selected according to the magnitude of the gradation value to be displayed.

- the address operation is not performed in all the subfields from the subfield SF1 to the subfield SF10.

- the sustain discharge never occurs in the discharge cell, and the gradation value “0” having the lowest luminance is displayed.

- the address operation is performed only in the subfield SF1 that is the subfield having the luminance weight “1”, and the address operation is not performed in the other subfields.

- the number of sustain discharges corresponding to the luminance weight “1” is generated in the discharge cell, and light emission with brightness corresponding to the gradation value “1” is generated, and the gradation value “1” is displayed.

- the write operation is performed, and the write operation is not performed in the other subfields.

- the number of sustain discharges corresponding to the luminance weight “9” is generated in the discharge cell, and the light emission having the brightness corresponding to the gradation value “9” is generated to display the gradation value “9”.

- each subfield generates a sustain pulse as many times as the luminance weight and emits light according to the gradation value to be displayed. Select. By doing so, each discharge cell generates sustain discharges the number of times corresponding to the gradation value to be displayed, causes the discharge cell to emit light with the luminance corresponding to the gradation value, and displays an image on the panel 10. .

- the gradation value that can be displayed on the panel 10 does not continuously change from the minimum gradation value to the maximum gradation value.

- the gradation values that can be displayed on the panel 10 change discretely, and the amount of change is additive.

- the minimum value when increasing the gradation value is the gradation value “1”

- the gradation value that can be displayed on the panel 10 is from the minimum value to the maximum value of the gradation value.

- Gradation value “1” such as gradation value “0”, gradation value “1”, gradation value “2”,..., Gradation value “255”. Increase by increments.

- the brightness perceived by humans changes logarithmically with changes in luminance, as is generally known. Therefore, for example, when the gradation value is changed from the minimum value to the maximum value that can be displayed on the panel 10, the gradation value is changed at equal intervals (for example, the gradation value). Despite being changed by “1”, a person observing the change in the brightness of the panel 10 does not perceive that the brightness is changing at equal intervals. For humans observing changes in the brightness of the panel 10, the brightness changes more greatly when the gradation value is small than when the gradation value is large. Perceived as.

- the gradation display capability (ability to display an image smoothly) when displaying a dark image is reduced.

- an intermediate gradation value can be displayed in a pseudo manner by performing dither processing or error diffusion processing on the image signal, and the gradation value that can be displayed on the panel 10. Has increased. Thereby, the gradation display capability in the plasma display device is improved, and a smoother image can be displayed.

- the gradation value “0” is black, and is a gradation value that does not emit light (emission by sustain discharge) in all subfields.

- the gradation value “1” is a gradation value in which only the subfield with the smallest luminance weight (for example, subfield SF1) emits light and the other subfields do not emit light. Therefore, the gradation value between the gradation value “0” and the gradation value “1” cannot be displayed on the panel 10 without performing the dither process (or error diffusion process).

- the gradation value “0” is based on a predetermined dither pattern.

- the dither processing is performed by arranging the discharge cells displaying "" and the discharge cells displaying the gradation value "1".

- black wrinkles represent discharge cells that display a gradation value “0”, and white wrinkles represent discharge cells that display a gradation value “1”.

- FIG. 6A is a diagram schematically showing an example of a dither pattern used for dither processing in the plasma display device according to one embodiment of the present invention.

- FIG. 6A shows an example of a dither pattern when the minimum value of the intermediate gradation value is the gradation value “1/2”.

- the dither block which is the minimum block constituting the dither pattern, is composed of two discharge cells.

- the discharge cell displaying the gradation value “0” and the discharge cell displaying the gradation value “1” are adjacent to each other.

- the discharge cells are not actually adjacent.

- a discharge cell displaying a gradation value “0” and a discharge cell displaying a gradation value “1” for a blue discharge cell are based on a dither pattern.

- a dither pattern Arrange. The same applies to the gradation values of other colors, and the same applies to the other dither patterns shown below.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 1: 1.

- a dither pattern (checkered dither pattern) is generated in which discharge cells displaying the gradation value “0” and discharge cells displaying the gradation value “1” are arranged in a checkered pattern at a ratio of 1: 1.

- the gradation value “1/2” can be displayed on the panel 10 in a pseudo manner.

- FIG. 6B is a diagram schematically showing another example of a dither pattern used for dither processing in the plasma display device according to one embodiment of the present invention.

- the minimum value of the intermediate gradation value is the gradation value “1/4”, the gradation value “1/4”, the gradation value “2/4”, and the gradation value “3/4”.

- An example of a dither pattern when each gradation value is displayed on the panel 10 is shown.

- the dither block which is the smallest block constituting the dither pattern, is composed of four discharge cells.

- the discharge cell displaying the gradation value “0” and the gradation value “1” are displayed.

- the discharge cells to be displayed are generated at a ratio of 3: 1.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 3: 1 can be generated.

- the tone value “1/4” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 2: 2.

- a dither pattern (checkered dither pattern) is generated in which discharge cells displaying gradation value “0” and discharge cells displaying gradation value “1” are arranged in a checkered pattern at a ratio of 2: 2.

- the gradation value “2/4” can be displayed on the panel 10 in a pseudo manner.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 1: 3.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 1: 3 can be generated.

- the tone value “3/4” can be displayed on the panel 10.

- FIG. 6C is a diagram schematically showing still another example of the dither pattern used for the dither process in the plasma display device according to the embodiment of the present invention.

- the minimum value of the intermediate gradation value is the gradation value “1/8”, the gradation value “1/8”, the gradation value “2/8”, the gradation value “3/8”,

- the dither pattern for displaying the gradation value “4/8”, gradation value “5/8”, gradation value “6/8”, gradation value “7/8” on the panel 10 An example is shown.

- the dither block which is the minimum block constituting the dither pattern, is composed of eight discharge cells. However, in this case, the discharge cells are not arranged in 2 rows and 4 columns or 4 rows and 2 columns, but the discharge cells are arranged in a “+” shape to form a dither block.

- the discharge cell displaying the gradation value “0” and the gradation value “1” are displayed.

- the discharge cells to be displayed are generated at a ratio of 7: 1.

- a dither pattern can be generated in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 7: 1.

- the tone value “1/8” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 6: 2.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 6: 2 can be generated.

- the tone value “2/8” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 5: 3.

- a dither pattern can be generated in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 5: 3.

- the tone value “3/8” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 4: 4.

- a dither pattern (checkered dither pattern) is generated in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged in a checkered pattern at a ratio of 4: 4.

- the pseudo gradation value “4/8” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 3: 5.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 3: 5 can be generated.

- the tone value “5/8” can be displayed on the panel 10.

- discharge cells displaying the gradation value “0” and discharge cells displaying the gradation value “1” are generated at a ratio of 2: 6.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 2: 6 can be generated.

- the tone value “6/8” can be displayed on the panel 10.

- the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are generated at a ratio of 1: 7.

- a dither pattern in which the discharge cells displaying the gradation value “0” and the discharge cells displaying the gradation value “1” are arranged at a ratio of 1: 7 can be generated.

- the tone value “7/8” can be displayed on the panel 10.

- the gradation value “a” and the gradation value “b” are equally divided into N, and (N ⁇ 1) intermediate gradations between the gradation value “a” and the gradation value “b”.

- the dither block is composed of N discharge cells.

- the discharge cells may be arranged so that the dither block has a square shape.

- the discharge cells are arranged so as to have a non-rectangular shape. May be. Note that a is an integer greater than or equal to “0”, b is an integer greater than or equal to “1”, and N is an integer greater than or equal to “2”.

- n is an integer of 1 or more and less than N.

- the dither block is composed of four discharge cells.

- the gradation value “5” is displayed in one discharge cell of the dither block, and the remaining three

- the gradation value “6” is displayed in the discharge cell.

- the dither block is generated so that no gap is generated in the area of the panel 10 where the gradation value “5.25” is displayed and no overlap occurs. In this way, the gradation value “5.25” can be displayed on the panel 10 in a pseudo manner.

- FIG. 7 is a circuit block diagram of the plasma display device 40 in one embodiment of the present invention.

- the plasma display apparatus 40 uses a panel 10 having a plurality of discharge cells each having a scan electrode 22, a sustain electrode 23, and a data electrode 32, and a single field using a plurality of subfields having an address period, a sustain period, and an erase period. And a drive circuit that generates the drive voltage waveform shown in FIGS. 3 and 4 and applies it to each electrode of the panel 10 to drive the panel 10.

- the drive circuit is necessary for the image signal processing circuit 41, the data electrode drive circuit 42, the scan electrode drive circuit 43, the sustain electrode drive circuit 44, the timing generation circuit 45, the temperature detection circuit 96, the cumulative operation time measurement circuit 98, and each circuit block.

- a power supply circuit (not shown) for supplying a proper power supply is provided.

- the temperature detection circuit 96 includes a temperature sensor 97 made of a generally known element such as a thermocouple used for detecting the temperature, and detects the temperature of the panel 10. Then, the temperature of the panel 10 detected by the temperature sensor 97 is compared with a plurality of predetermined temperature thresholds to determine what the temperature of the panel 10 is, and the result is subjected to image signal processing. Output to the circuit 41. Specifically, the temperature threshold is set to 5 ° C., 10 ° C., 20 ° C., and the panel temperature is lower than 5 ° C., 5 ° C. or higher, lower than 10 ° C. And a signal indicating the result is output to the image signal processing circuit 41 (low luminance amplification circuit 46).

- a temperature threshold is set to 5 ° C., 10 ° C., 20 ° C.

- the panel temperature is lower than 5 ° C., 5 ° C. or higher, lower than 10 ° C.

- a signal indicating the result is output to the image

- the accumulated operation time measuring circuit 98 has a generally known timer 99 having an integration function in which a numerical value increases by a certain amount per unit time during an energization period of the panel 10 (during the operation period of the panel 10).

- the measurement time is accumulated without being reset. That is, even when the power of the plasma display device 40 is turned off, the measurement time is not reset and the measurement time immediately before the power is turned off is held in the timer 99, and the plasma display device 40 is turned on again.

- the operation time of the plasma display device 40 is measured by the timer 99 following the measurement time up to the previous time.

- the accumulated operation time measuring circuit 98 can measure the accumulated operation time (accumulated operation time) of the plasma display device 40 after the plasma display device 40 starts the operation for the first time. That is, the cumulative operation time measuring circuit 98 measures the cumulative operation time of the panel 10.

- the cumulative operation time measuring circuit 98 compares the cumulative operation time of the panel 10 measured by the timer 99 with a plurality of predetermined cumulative time thresholds to determine whether or not the cumulative operation time of the panel 10 has exceeded a predetermined time.

- a signal representing the result of the determination is output to the image signal processing circuit 41.

- 500 hours, 1000 hours, and 2000 hours are set as the cumulative time threshold, and the cumulative operation time is less than 500 hours, 500 hours or more and less than 1000 hours, 1000 hours or more and less than 2000 hours, or 2000 hours. Whether it is the above or not is determined, and a signal indicating the result is output to the image signal processing circuit 41 (low luminance amplification circuit 46).

- each of the above-described threshold values is merely an example in the present embodiment, and the present invention is not limited to the above-described numerical values.

- Each threshold value is desirably set to an optimum value based on the characteristics of the panel 10 and the specifications of the plasma display device 40.

- the image signal processing circuit 41 includes a low luminance amplification circuit 46, a dither processing circuit 47, and a subfield conversion circuit 48.

- the low luminance amplifying circuit 46 converts each of the input image signals of the red primary color signal sigR, the green primary color signal sigG, and the blue primary color signal sigB (hereinafter simply referred to as “image signal”) of the image signal. Amplification is performed at an amplification factor corresponding to the magnitude and the temperature detected by the temperature detection circuit 96 and the cumulative operation time measured by the cumulative operation time measurement circuit 98. Although details will be described later, in this embodiment, the amplification factor is non-linear, and the low luminance amplifier circuit 46 outputs an image signal having a signal level (signal magnitude) less than the gradation value “1”.

- Amplification is performed with an amplification factor larger than the amplification factor of an image signal equal to or higher than the signal level corresponding to the gradation value “1”.

- an image signal having a signal level corresponding to the gradation value “1” is simply referred to as an “image signal having a gradation value“ 1 ””.

- the discharge cell displaying the gradation value “1” only the subfield with the smallest luminance weight (for example, subfield SF1) emits light, and the other subfields do not emit light.