SINGLE CHIP VLSI IMPLEMENTATION OF A DIGITAL RECEIVER EMPLOYING ORTHOGONAL FREQUENCY DIVISION MULTIPLEXING

This invention relates to receivers of electromagnetic signals employing multicarπer modulation More particularly this invention relates to a digital receiver which is implemented on a single VLSI chip for receiving transmissions employing orthogonal frequency division multiplexing, and which is suitable for the reception of digital video broadcasts Coded orthogonal frequency division multiplexing ("COFDM") has been proposed for digital audio and digital video broadcasting, both of which require efficient use of limited bandwidth, and a method of transmission which is reliable in the face of several effects For example the impulse response of a typical channel can be modeled as the sum of a plurality of Dirac pulses having different delays Each pulse is subject to a multiplication factor, in which the amplitude generally follows a Rayleigh law Such a pulse train can extend over several microseconds, making unencoded transmission at high bit rates unreliable In addition to random noise, impulse noise, and fading, other major difficulties in digital terrestrial transmissions at high data rates include multipath propagation, and adjacent channel interference, where the nearby frequencies have highly correlated signal variations COFDM is particularly suitable for these applications In practical COFDM arrangements, relatively small amounts of data are modulated onto each of a large number of carriers that are closely spaced in frequency The duration of a data symbol is increased in the same ratio as the number of carriers or subchannels, so that inter-symbol interference is markedly reduced Multiplexing according to COFDM is illustrated in Figs 1 and 2, wherein the spectrum of a single COFDM carrier or subchannel is indicated by line 2 A set of carrier frequencies is indicated by the superimposed waveforms in Fig 2, where orthogonality conditions are satisfied In general two real-valued functions are orthogonal if

"ψp(t) ψq(t) dt = K (1)

where K is a constant, and K = 0 if p ≠ q, K ≠O if p = q Practical encoding and decoding of signals according to COFDM relies heavily on the fast Fourier transform ("FFT"), as can be appreciated from the following equations The signal of a carrier c is given by ω + φc(t)] se(t) = An(t) e Jlu,e, τ ψeiυj (2)

where Ac is the data at time t, ωc is the frequency of the carrier, and φc is the phase. N carriers in the COFDM signal is given by

s.(t) = (1/N) ∑ An(t)eJ [ω"t +φ»(t)l (3) n = 0

ωn = ω0 + nΔω (4)

Sampling over one symbol period, then

Ac(t)^An (6)

With a sampling frequency of 1/T, the resulting signal is represented by

ss( = ( 1 /Λ/) ∑ An(t)e "+n^)kT+*"] (7) n = 0

Sampling over the period of one data symbol T = NT, with ω0 = 0,

N - 1 ss(kT) = ( 1 /N) ∑ Ane )Φne j(nΔω)kτ (8) n -= 0 which compares with the general form of the inverse discrete Fourier transform:

N - 1 g (kT) = (1 /N) ∑ G(n/(kT))e ,πn (k/N) (9) n = 0

In the above equations r\n^n is the input signal in the sampled frequency domain, and ss(kT) is the time domain representation. It is known that increasing the size of the FFT provides longer symbol durations and improves ruggedness of the system as regards echoes which exceed the length of the guard interval. However computational complexity increases according to Nlog2N, and is a practical limitation.

In the presence of intersymbol interference caused by the transmission channel, orthogonality between the signals is not maintained. One approach to this problem has been to deliberately sacrifice some of the emitted energy by preceding each symbol in the time domain by an interval which exceeds the memory of the channel, and any multipath delay. The "guard interval" so chosen is large enough to absorb any intersymbol interference, and is established by preceding each symbol by a replication of a portion of itself. The replication is typically a cyclic extension of the terminal portion

of the symbol. Referring to Fig. 3, a data symbol 4 has an active interval 6 which contains all the data transmitted in the symbol. The terminal portion 8 of the active interval 6 is repeated at the beginning of the symbol as the guard interval 10. The COFDM signal is represented by the solid line 12. It is possible to cyclically repeat the initial portion of the active interval 6 at the end of the symbol.

Transmission of COFDM data can be accomplished according to the known general scheme shown in Fig. 4. A serial data stream 14 is converted to a series of parallel streams 16 in a serial-to-parallel converter 18. Each of the parallel streams 16 is grouped into x bits each to form a complex number, where x determines the signal constellation of its associated parallel stream. After outer coding and interleaving in block 20 pilot carriers are inserted via a signal mapper 22 for use in synchronization and channel estimation in the receiver. The pilot carriers are typically of two types. Continual pilot carriers are transmitted in the same location in each symbol, with the same phase and amplitude. In the receiver, these are utilized for phase noise cancellation, automatic frequency control, and time/sampling synchronization. Scattered pilot carriers are distributed throughout the symbol, and their location typically changes from symbol to symbol. They are primarily useful in channel estimation. Next the complex numbers are modulated at baseband by the inverse fast fourier transform ("IFFT") in block 24. A guard interval is then inserted at block 26. The discrete symbols are then converted to analog, typically low-pass filtered, and then upconverted to radiofrequency in block 28. The signal is then transmitted through a channel 30 and received in a receiver 32. As is well known in the art, the receiver applies an inverse of the transmission process to obtain the transmitted information. In particular an FFT is applied to demodulate the signal. A modern application of COFDM has been proposed in the European Telecommunications Standard ETS 300 744 (March 1997), which specifies the framing structure, channel coding, and modulation for digital terrestrial television. The specification was designed to accommodate digital terrestrial television within the existing spectrum allocation for analog transmissions, yet provide adequate protection against high levels of co-channel interference and adjacent channel interference. A flexible guard interval is specified, so that the system can support diverse network configurations, while maintaining high spectral efficiency, and sufficient protection against co-channel interference and adjacent channel interference from existing PAL/SECAM services. The noted European Telecommunications Standard defines two modes of operation. A "2K mode", suitable for single transmitter operation and for small single frequency networks with limited transmitterdistances. An "8K mode" can be used for either single transmitter operation or for large single frequency networks. Various levels of quadrature amplitude

modulation ("QAM") are supported, as are different inner code rates, in order to balance bit rate against ruggedness. The system is intended to accommodate a transport layer according to the Moving Picture Experts Group ("MPEG"), and is directly compatible with M P E G - 2 c o d e d TV s i g n a l s ( I S O / I E C 1 38 1 8 ) . In the noted European Telecommunications Standard data carriers in a COFDM frame can be either quadrature phase shift keyed ("QPSK"), 16-QAM, 64-QAM, non- uniform 16-QAM, or non-uniform 64-QAM using Gray mapping.

An important problem in the reception of COFDM transmission is difficulty in maintaining synchronization due to phase noise and jitter which arise from upconversion prior to transmission, downconversion in the receiver, and the front end oscillator in the tuner, which is typically a voltage controlled oscillator. Except for provision of pilot carriers to aid in synchronization during demodulation, these issues are not specifically addressed in the noted European Telecommunications Standard, but are left for the implementer to solve. Basically phase disturbances are of two types. First, noisy components which disturb neighbor carriers in a multicarrier system are called the "foreign noise contribution" ("FNC"). Second, a noisy component which disturbs its own carrier is referred to as the "own noise contribution".

Referring to Fig. 5, the position of ideal constellation samples are indicated by "x" symbols 34. The effect of foreign noise contribution is stochastic, resulting in Gaussianlike noise. Samples perturbed in this manner are indicated on Fig. 5 as circles 36. The effects of the own noise contribution is a common rotation of all constellation points, indicated as a displacement between each "x" symbol 34 and its associated circle 36. This is referred to as the "common phase error", which notably changes from symbol to symbol, and must therefore be recalculated each symbol period Ts. The common phase error may also be interpreted as a mean phase deviation during the symbol period Ts.

In order for the receiver 32 to process the data symbols in a practical system, a mathematical operation is performed on the complex signal representing each data symbol. Generally this is an FFT. For valid results to be obtained, a particular form of timing synchronization is required in order to align the FFT interval with the received data symbol.

It is therefore a primary object of the invention to provide a highly integrated, low cost apparatus for the reception of digital broadcasts, such as terrestrial digital video broadcasts, which is implemented on a single VLSI chip. It is another object of the invention to provide an improved method and apparatus for synchronizing a received data symbol with an FFT window in signals transmitted according to COFDM.

It is yet another object of the invention to improve the stability of digital multicarrier receivers in respect of channel estimation

It is still another object of the invention to improve the automatic frequency control circuitry employed in multicarrier digital receivers It is a further object of the invention to improve the automatic sampling rate control circuitry employed in multicarrier digital receivers

The invention provides a digital receiverfor multicarπersignals that are transmitted by orthogonal frequency division multiplexing The multicarrier signal carries a stream of data symbols having an active interval, and a guard interval in which the guard interval is a replication of a portion of the active interval In the receiver an analog to digital converter is coupled to a front end amplifier An l/Q demodulator is provided for recovering in phase and quadrature components from data sampled by the analog to digital converter, and an automatic gam control circuit is coupled to the analog to digital converter In a low pass filter circuit accepting I and Q data from the l/Q demodulator, the I and Q data are decimated and provided to a resampling circuit An interpolator in the resampling circuit accepts the decimated I and Q data at a first rate and outputs resampled I and Q data at a second rate An FFT window synchronization circuit is coupled to the resampling circuit for locating a boundary of the guard interval A realtime pipelined FFT processor is operationally associated with the FFT window synchronization circuit Each stage of the FFT processor has a complex coefficient multiplier, and an associated memory with a lookup table defined therein for multiplicands being multiplied in the complex coefficient multiplier Each multiplicand in the lookup table is unique in value A monitor circuit responsive to the FFT window synchronization circuit detects a predetermined indication that a boundary between an active symbol and a guard interval has been located

According to an aspect of the invention the FFT window synchronization circuit has a first delay element accepting currently arriving resampled I and Q data, and outputting delayed resampled I and Q data A subtracter produces a signal representative of the difference between the currently arriving resampled I and Q data and the delayed resampled I and Q data In a first circuit the subtracter output signal is converted to a signal having a unipolar magnitude, which is preferably the absolute value of the signal provided by the subtracter A second delay element stores the output signal of the first circuit, and a third delay element receives the delayed output of the second delay element In a second circuit a statistical relationship is calculated between data stored in the second delay element and data stored in the third delay element The output of the FFT window synchronization circuit is representative of the statistical relationship

Preferably the statistical relationship is the F ratio. The FFT processor is capable of operation in a 2K mode and in an 8K mode.

The FFT processor has an address generatorfor the memory of each stage, which accepts a signal representing the order dependency of a currently required multiplicand, and generates an address of the memory wherein the currently required multiplicand is stored. In a further aspect of the invention each multiplicand is stored in the lookup table in order of its respective order dependency for multiplication by the complex coefficient multiplier, so that the order dependencies of the multiplicands define an incrementation sequence. The address generator has an accumulator for storing a previous address that was generated thereby, a circuit for calculating an incrementation value of the currently required multiplicand responsive to the incrementation sequence, and an adder for adding the incrementation value to the previous address.

In another aspect of the invention there are a plurality of incrementation sequences. The multiplicands are stored in row order, wherein in a first row a first incrementation sequence is 0, in a second row a second incrementation sequence is 1 , in a third row first and second break points B1 , B2 of a third incrementation sequence are respectively determined by the relationships

N -1

B1 M = 4NB1 M "∑ 4n n =0

B2

' ,N Σ 4" n =0 and in a fourth row a third break point B3 of a third incrementation sequence is determined by the relationship

B3M = 2 x 4N + 2 wherein MN represents the memory of an Nth stage of the FFT processor.

The receiver provides channel estimation and correction circuitry. Pilot location circuitry receives a transformed digital signal representing a frame from the FFT processor, and identifies the position of pilot carriers therein. The pilot carriers are spaced apart in a carrier spectrum of the transformed digital signal at intervals K and have predetermined magnitudes. The pilot location circuitry has a first circuit for computing an order of carriers in the transformed digital signal, positions of said carriers being calculated modulo K. There are K accumulators coupled to the second circuit for accumulating magnitudes of the carriers in the transformed digital signal, the accumulated magnitudes defining a set. A correlation circuit is provided for correlating

K sets of accumulated magnitude values with the predetermined magnitudes In the correlation a first member having a position calculated modulo K in of each of the K sets is uniquely offset from a start position of the frame

According to another aspect of the invention the pilot location circuitry also has a bit reversal circuit for reversing the bit order of the transformed digital signal

According to yet another aspect of the invention amplitudes are used to represent the magnitudes of the carriers Preferably the magnitudes of the carriers and the predetermined magnitudes are absolute values

In a further aspect of the invention the correlation circuitry also has a peak tracking circuit for determining the spacing between a first peak and a second peak of the K sets of accumulated magnitudes, wherein the first peak is the maximum magnitude, and the second peak is the second highest magnitude

The channel estimation and correction circuitry also has an interpolating filter for estimating the channel response between the pilot carriers, and a multiplication circuit for multiplying data carriers output by the FFT processor with a correction coefficient produced by the interpolating filter

The channel estimation and correction circuitry also has a phase extraction circuit accepting a data stream of phase-uncorrected I and Q data from the FFT processor, and producing a signal representative of the phase angle of the uncorrected data The phase extraction circuit includes an accumulator for the phase angles of succeeding phase-uncorrected I and Q data

According to an aspect of the invention the channel estimation and correction circuitry includes an automatic frequency control circuit coupled to the phase extraction circuit, in which a memory stores the accumulated common phase error of a first symbol carried in the phase-uncorrected I and Q data An accumulator is coupled to the memory and accumulates differences between the common phase error of a plurality of pilot carriers in a second symbol and the common phase error of corresponding pilot carriers in the first symbol The output of the accumulator is filtered, and coupled to the l/Q demodulator According to another aspect of the invention the coupled output of the accumulator of the automatic frequency control circuit is enabled in the l/Q demodulator only during reception of a guard interval therein

According to yet another aspect of the invention the channel estimation and correction circuitry also has an automatic sampling rate control circuit coupled to the phase extraction circuit, in which a memory stores the individual accumulated phase errors of pilot carriers in a first symbol carried in the phase-uncorrected I and Q data

An accumulator is coupled to the memory and accumulates differences between the

phase errors of individual pilot carriers in a second symbol and phase errors of corresponding pilot carriers in the first symbol to define a plurality of accumulated intersymbol carrier phase error differentials. A phase slope is defined by a difference between a first accumulated intersymbol carrier phase differential and a second accumulated intersymbol carrier phase differential. The output of the accumulator is filtered and coupled to the l/Q demodulator.

According to one aspect of the invention the sampling rate control circuit stores a plurality of accumulated intersymbol carrier phase error differentials and computes a line of best fit therebetween. According to another aspect of the invention the coupled output signal of the accumulator of the automatic sampling rate control circuit is enabled in the resampling circuit only during reception of a guard interval therein.

According to an aspect of the invention a common memory for storing output of the phase extraction circuit is coupled to the automatic frequency control circuit and to the automatic sampling rate control circuit.

According to another aspect of the invention the phase extraction circuit also has a pipelined circuit for iteratively computing the arctangent of an angle of rotation according to the series

X Y Λ V Λ V Λ i i tan W = * ~ — + — + — - ■ • •, x 1

3 5 7 9 wherein x is a ratio of the phase-uncorrected I and Q data.

The pipelined circuit includes a constant coefficient multiplier, and a multiplexerfor selecting one of a plurality of constant coefficients of the series. An output of the multiplexer is connected to an input of the constant coefficient multiplier.

According to still another aspect of the invention the pipelined circuit has a multiplier, a first memory for storing the quantity x2, wherein the first memory is coupled to a first input of the multiplier, and has a second memory for holding an output of the multiplier. A feedback connection is provided between the second memory and a second input of the multiplier. The pipelined circuit also has a third memory for storing the value of the series. Under direction of a control circuit coupled to the third memory, the pipeline circuit computes N terms of the series, and also computes N+1 terms of the series. An averaging circuit is also coupled to the third memory and computes the average of N terms and N+1 terms of the series. Data transmitted in a pilot carrier of the multicarrier signal is BCH encoded according to a code generator polynomial h(x). A demodulator operative on the BCH encoded data is provided, which includes an iterative pipelined BCH decoding circuit.

The BCH decoding circuit is circuit coupled to the demodulator It forms a Galois Field of the polynomial, and calculates a plurality of syndromes therewith The BCH decoding circuit includes a plurality of storage registers, each storing a respective one of the syndromes, and a plurality of feedback shift registers, each accepting data from a respective one of the storage registers The BCH decoding circuit has a plurality of Galois field multipliers Each of the multipliers is connected in a feedback loop across a respective one of the feedback shift registers and multiplies the output of its associated feedback shift register by an alpha value of the Galois Field An output Galois field multiplier multiplies the outputs of two of the feedback shift registers A logical network forms an error detection circuit connected to the feedback shift registers and to the output Galois field multiplier The output of the error detection circuit indicates an error in a current bit of data, and a feedback line is enabled by the error detection logic and connected to the storage registers Using the feedback line, the data output by the feedback shift registers are written back into the storage registers for use in a second iteration

According to an aspect of the invention the output Galois field multiplier has a first register initially storing a first multiplicand A, a constant coefficient multiplier connected to the first register for multiplication by a value α An output of the constant coefficient multiplier is connected to the first register to define a first feedback loop, whereby in a kth cycle of clocked operation the first register contains a Galois field product Aαk A second register is provided for storing a second multiplicand B An AND gate is connected to the second register and to the output of the constant coefficient multiplier An adder has a first input connected to an output of the AND gate An accumulator is connected to a second input of the adder, and the Galois field product AB is output by the adder

The invention provides a method for the estimation of a frequency response of a channel It is performed by receiving from a channel an analog multicarrier signal that has a plurality of data carriers and scattered pilot carriers The scattered pilot carriers are spaced apart at an interval N and are transmitted at a power that differs from the transmitted power of the data carriers The analog multicarrier signal is converted to a digital representationthereof A Fouπertransform is performed on the digital representation of the multicarrier signal to generate a transformed digital signal The bit order of the transformed digital signal is reversed to generate a bit-order reversed signal Magnitudes of the carriers in the bit-order reversed signal are cyclically accumulated in N accumulators, amd the accumulated magnitudes are correlated with the power of the scattered pilot carriers Responsive to the correlation, a synchronizing signal is

generated that identifies a carrier position of the multicarrier signal, preferably an active carrier.

According to another aspect of the invention the step of accumulating magnitudes is performed by adding absolute values of a real component of the bit-order reversed signal to respective absolute values of imaginary components thereof to generate sums, and respectively storing the sums in the N accumulators.

According to yet another aspect of the invention the step of correlating the accumulated magnitudes also is performed by identifying a first accumulator having the highest of the N values stored therein, which represents a first carrier position, and by identifying a second accumulator which has the second highest of the N values stored therein, which represents a second carrier position. The interval between the first carrier position and the second carrier position is then determined.

To validate the consistency of the carrier position identification, the position of a carrier of a first symbol in the bit-order reversed signal is compared with a position of a corresponding carrier of a second symbol therein.

Preferably interpolation is performed between pilot carriers to determine correction factors for respective intermediate data carriers disposed therebetween, and respectively adjusting magnitudes of the intermediate data carriers according to the correction factors. According to an aspect of the invention a mean phase difference is determined between corresponding pilot carriers of successive symbols of the transformed digital signal. A first control signal representing the mean phase difference, is provided to control the frequency of reception of the multicarrier signal. The first control signal is enabled only during reception of a guard interval. Preferably a line of best fit is determined for the inter-symbol phase differences of multiple carriers to define a phase slope.

For a better understanding of these and other objects of the present invention, reference is made to the detailed description of the invention, by way of example, which is to be read in conjunction with the following drawings, wherein: Fig. 1 illustrates the spectrum of a COFDM subchannel;

Fig. 2 shows a frequency spectrum for multiple carriers in a COFDM signal; Fig. 3 is a diagram of a signal according to COFDM and shows a data symbol format;

Fig. 4 is a block diagram illustrating an FFT based COFDM system; Fig. 5 illustrates certain perturbations in a COFDM signal constellation;

Fig. 6 is a flow diagram of a method of timing synchronization according to a preferred embodiment of the invention;

Fig 7 is a plot of an F ratio test performed on several data symbols for coarse timing synchronization,

Fig 8 is a plot of an incomplete beta function for different degrees of freedom,

Fig 9 is a plot helpful in understanding a test of statistical significance according to the invention,

Fig 10 is an electrical schematic of a synchronization circuit according to an alternate embodiment of the invention,

Fig 11 is an electrical schematic of a synchronization circuit according to another alternate embodiment of the invention, Fig 12 is a block diagram of a single-chip embodiment of a digital receiver in accordance with the invention,

Fig 13 is a block diagram illustrating the front end of the digital receiver shown in Fig 12 in further detail,

Fig 14 is a block diagram illustrating the FFT circuitry, channel estimation and correction circuitry of the digital receiver shown in Fig 12,

Fig 15 is a block diagram illustrating another portion of the digital receiver shown in Fig 12,

Fig 16 is a more detailed block diagram of the channel estimation and correction circuitry shown in Fig 14, Fig 17 is a schematic of the automatic gam control circuitry of the digital receiver shown in Fig 12,

Fig 18 is a schematic of the l/Q demodulator of the digital receiver shown in Fig 12,

Fig 19 illustrates in greater detail a low pass filter shown in Fig 13, Fig 20 shows the response of the low pass filter shown in Fig 19,

Fig 21 shows the resampling circuitry of the digital receiver shown in Fig 12,

Fig 22 illustrates a portion of an interpolator in the resampling circuitry of Fig 21 ,

Fig 23 is a more detailed block diagram of the FFT window circuitry shown in Fig 14, Fig 24 is a schematic of a butterfly unit in the FFT calculation circuitry shown in

Fig 14,

Figs 25 and 26 are schematics of butterfly units in accordance with the prior art,

Fig 27 is a schematic of a radix 22 + 2 FFT processor in accordance with the invention, Fig 28 is 32 point flow graph of the FFT processor shown in Fig 27,

Fig 29 is a schematic of a configurable 2K 8K radix 22+2 single path, delay feedback pipelined FFT processor in accordance with the invention,

Fig 30 is a detailed schematic of a complex multiplier used in the circuitry shown in Fig 29,

Fig 31 is a detailed schematic of an alternateembodimentof a complex multipliers used in the circuitry shown in Fig 29, Fig 32 is another diagram illustrating the organization of the twiddle factors for each of the multipliers in the circuitry shown in Fig 29,

Fig 33 illustratesthe organization of the twiddle factors for each of the multipliers in the circuitry shown in Fig 29,

Fig 34 is a schematic of address generator used in the circuitry shown in Fig 29, Fig 35 is a schematic of a generalization of the address generator shown in Fig

34,

Fig 36 is a flow chart illustrating the process of pilot location conducted by the channel estimation and correction circuitry shown in Fig 16,

Fig 37 is a flow chart of an embodiment of the pilot localization procedure according to the invention

Fig 38 is a more detailed block diagram of the tps sequence block of the circuitry shown in Fig 14,

Fig 39 is a schematic of a BCH decoder used in the tps processing circuitry shown

Fig 40 is a more detailed schematic of a Galois field multiplier shown in Fig 39,

Fig 41 is a block diagram genencally illustrating the automatic sampling control and automatic frequency control loops of the digital receiver shown in Fig 12,

Fig 42 is a more detailed block diagram of the automatic sampling control and automatic frequency control loops shown in Fig 41 Fig 43 is a more detailed block diagram of the phase extract block of the circuitry shown in Fig 42,

Fig 44 is a schematic of the circuitry employed to calculate an arctangent in the block diagram shown in Fig 43,

Fig 45 is a plot of the square error at different values of α of the Taylor expansion to 32 terms,

Fig 46 is a plot of the square error at different values of α of the Taylor expansion to 31 terms,

Fig 47 is a plot of the square error at different values of α of the average of the Taylor expansion to 31 and 32 terms, Fig 48 is a plot of the phase differences of pilot carriers with a line of best fit shown,

Fig. 49 is a more detailed block diagram an alternate embodiment of the automatic sampling control and automatic frequency control loops shown in Fig. 41 ;

Fig. 50 illustrates a coded constellation format used in the demapping circuitry of Fig. 15; Fig. 51 illustratesthe conversion of l,Q data to binary data value using the format shown in Fig. 50;

Fig. 52 is a more detailed block diagram of the symbol deinterleaving circuitry shown in Fig. 15;

Fig. 53 is a more detailed block diagram of the bit deinterleaving circuitry shown in Fig. 15;

Fig. 54 illustratesthe conversion from a coded constellation format to a 24 bit soft l/Q format by the bit deinterleaving circuitry shown in Fig. 53;

Fig. 55 is a more detailed block diagram of the microprocessor interface of the receiver shown in Fig. 12; Fig. 56 is a more detailed block diagram of the system controller of the receiver shown in Fig. 12; and

Fig. 57 is a state diagram relating to channel acquisition in the system controller of the receiver shown in Fig. 56. Alignment of The FFT Window Referring again to Figs. 3 and 4, according to the invention a statistical method is applied to COFDM signals to find the end of the guard interval 10. This method is explained with reference to the above noted European Telecommunications Standard, but is applicable to many forms of frequency division multiplexing having prefixed or postfixed guard intervals. It allows the receiver 32 to find the end of the guard interval given only the received sampled complex signal ( solid line 12) and the size of the active interval 6 . The method relies on the fact that the guard interval 10 is a copy of the last part of the data symbol 4. In the receiver 32, due to echoes and noise from the channel and errors in the local oscillator, the guard interval 10 and the last part of the data symbol 4 will differ. If the errors introduced are random then a statistical method can be applied. According to the invention, the received complex signal is sampled at a rate which is nearly identical to that used in the transmitter. A difference signal is found for a pair of received samples which are separated by a period of time which is as close as possible to the active interval 6. This period should be equal to the size of the fast fourier transform ("FFT") being applied (i.e. 2048 or 8192 samples). Let

' msize I (14)

where S, is the difference signal; s, and §_msae are the current and previous complex input samples of which the modulus is taken. That is, the subscript "i" indexes a linear time sequence of input values. Assuming that the input signal is random, then S, is also random. Within the guard interval s, and s^^wM be similar, although not identical, due to the effects ofthe channel. S, will be therefore a random signal with a small dispersion. As used herein the term "dispersion" means generally the spread of values, and is not restricted to a particular mathematical definition, in general the active part of one symbol is not related to the active part of the next symbol. Outside of the guard interval S, will be random with a much larger dispersion. In order to find the end of the guard interval, the dispersion of the difference signal S, is monitored to look for a significant increase which will occur at the boundary of the guard interval 10 and the active interval 6. The inventors have also observed that a large decrease in dispersion is seen at the start of the guard interval 10.

According to a preferred embodiment of the invention samples of the input signal are stored over an interval which includes at least one symbol period Ts. The dispersion of the difference signal S, is calculated over a block of samples. The block is moved back in time over a number of samples, n, and the dispersion is recalculated. These two blocks are referred to herein as "comparison blocks". The ratio of a current dispersion in a first comparison block to the dispersion in a previous comparison block is found. Then, the F ratio significance test is used to find significant differences in the dispersions of the two comparison blocks. The F ratio is defined as

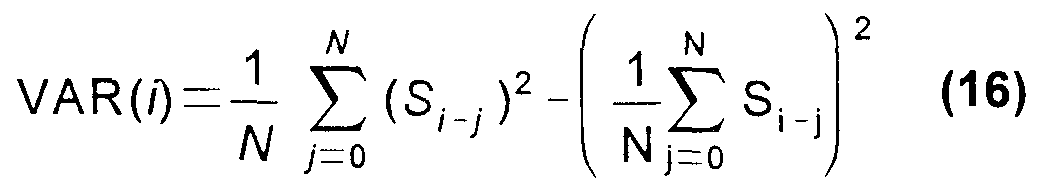

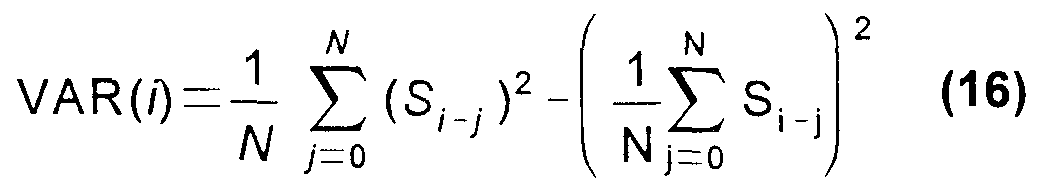

where n is a positive integer, i indexes the input samples, and VAR(i) is the variance of a block of values of length N samples. Variance can be defined as

While the F ratio significance test is used in the preferred embodiment, other functions of the two dispersion values which give a signal relating to the change in dispersion could be used. There are many such functions. An advantage of the F ratio is that for a random input signal it has a known probability distribution, allowing convenient statistical analysis for purposes of performance analysis and system design. Also the F ratio intrinsically normalizes the signal, making the result independent of the signal level.

The method is disclosed with reference to Fig. 6, in which a first member of a sample pair in a current evaluation block is measured at step 38. A delay of one active interval 6 ( Fig. 3) is experienced in step 40. This may be accomplished with a digital delay such as a FIFO, or equivalently by buffering samples for an active interval in a memory and accessing appropriate cells of the memory. A second member of the sample pair is measured in step 42, and the difference between the first and second member is determined and stored in step 44. The end of the current block is tested at decision step 46. The size of the evaluation block should not exceed the length of a guard interval, and may be considerably smaller. In the event the end of the current block has not yet been reached, another sample is acquired at step 48, and control returns to step 38.

If the end of the current block has been reached, the dispersion of the current block is measured in step 50, and is treated as one of two comparison blocks of data. A test is made at decision step 52 to determine if a group of two comparison blocks have been evaluated. If this test is negative, then another block of data is acquired in step 54, after which control returns to step 38. The other block of data need not be contiguous with the block just completed.

In the event the test at decision step 52 is positive, the F ratio is computed for the group of two comparison blocks at step 56. The results obtained in step 56 are submitted to peak detection in step 60. Peak detection optionally includes statistical tests of significance, as is explained hereinbelow.

If peaks are detected, then the boundary of a guard interval is established in step 62 for purposes of synchronization of the FFT window which is necessary for further signal reconstruction. If peaks are not detected, the above process is repeated with a block of samples taken from another portion of the data stream. Example 1 :

Referring now to Fig. 7 a complex signal was generated according to the above noted European Telecommunicationsstandard using a random number generator, and transmitted across a Ricean channel model together with added white Gaussian noise (SNR = 3.7). Data symbols were then analyzed according to the above described method. The results 6 data symbols are shown in Fig. 7, wherein the F ratio is plotted for convenience of presentation on a logarithmic axis as line 64, because the spikes 66, 68, at the beginning and end of the guard intervals respectively, are very large.

Although it is quite evident from Figure 7 that the ends of the guard intervals are easy to find using any of several well known peak detectors, it is possible to apply a statistical test to more accurately answer the question: do the two blocks of samples have the same dispersion? This is the null hypothesis, H0, i.e. the dispersion is the

same and the observed spike in F is due to random fluctuations only If H0 has very low probability it can be rejected, which would correspond to detection of the start or end of the guard interval From the way the COFDM symbol is constructed H0 is expected to be true for comparison blocks lying entirely within the guard interval or within the active interval, but false when the comparison blocks straddle a boundary at the start or end of the guard interval If comparison blocks of random samples are drawn from the same population then the probability of F is given by

where l() is the incomplete Beta function, v 2

(18) v2 T v,F and v1 and v2 are the number of degrees of freedom with which the first and second dispersions are estimated In this example v1 = v2 = (N-1 ) if n >= N The shape of the function is shown in Fig 8 From a statistical point of view n should be sufficiently large so that the two blocks do not overlap, i e n >= N If the blocks do overlap, then the calculation of the second dispersion will use samples used for the calculation of the first dispersion This effectively reduces the number of degrees of freedom and hence the significance of the result It has been determined that setting n=N works well

The function Q() in equation (13) actually gives the one-tailed probability H0 could be rejected if F is either very large or very small, and so the two-tailed test is required Actually the two tails are identical, so for a two-tailed test the probability is double that given in equation (13) However, this results in values of probability greater than one for F<1 The prooabihty, p, is therefore calculated as follows

P =2/ (γ' γ) <19>

and then if (p > 1), p = 2 - p This probability reflects the viability of H0 Thus if p is small, H0 can be rejected and it can be stated, with a specified degree of certainty, that the comparison blocks come from sample populations with different dispersion The noted European Telecommunications Standard specification states that the block size, N, should be 32 for a correlation algorithm N={32,64} have been successfully tried The probability functions obtained are shown in Fig 9 using these values for N In the preferred embodiment p <= 0 05 has been set for the rejection of H0

A precise implementationwould be to calculate F, then x, then the incomplete Beta function, then p and then apply the threshold test. This algorithm would be very difficult to realize in hardware since the Beta function is very complicated. In the preferred embodiment it is much simpler, and gives the same results, to set the acceptance threshold and N parameter, and thus define an upper and lower limit for F. It is then only necessary to calculate F and compare it with the limits. In order to simply find the end of the guard interval it may be safely assumed that F>1. Only the upper limit on F is needed. To calculate the limits on F accurately, a suitable root-finding method, such as Newton-Raphson may be utilized. Typical values are given in Table 1.

Table 1

This method has been successfully tested using the specified channel model with additive white Gaussian noise (SNR=3.7).

The formula for dispersion given in Equation (12) would require a multiplier for implementation in silicon. The calculation of F is a division in which the (N-1 ) normalisation constants cancel out as long as the two blocks have the same size. Accurate multiplication and division can be expensive in silicon. In the preferred embodiment simplifications have been implemented which give less accurate, but still viable, values for F. S, can be assumed to have zero mean so it is not necessary to calculate the mean from the block of samples. This also increases the number of degrees of freedom from (N-1) to N. Instead of calculating variance using the standard

sum of squares formula, the dispersion can be estimated by the mean absolute deviation. The formula for VAR(i) becomes

The (1/N) factor divides out in the calculation of F if the two blocks have the same size. But there still remains the division of the two dispersions and the squaring required. These can be tackled using logarithms to the base 2. Substituting from Equation (16) into Equation (11) gives

Taking logs to the base 2 gives

log F = 2(log sa - log sb) = y (22)

It is then only necessary to calculate y and compare it with the logarithm to the base 2 of the F upper limit. The comparison can be made by subtracting the log of the limit from 2(log2sa-iog2sb) and comparing with zero. The factor of 2 can be absorbed into the limit.

Calculation of the logs to base two is relatively straightforward in hardware if the numbers are stored as fixed point fractions. The fractions can be split into an exponent and a fractional mantissa: x = A2B. Taking log base 2 gives logx = logA + B. Since A is fractional it is practical to find its logarithm using a lookup table. The exponent B can be found from the position of the MSB (since sa and sb will both be positive numbers).

The calculation can thus be reduced to require only addition and subtraction arithmetic operations. The limit should also be recalculated using v1=v2=N if using this method. In practice, the significance level may be set empirically for a particular application, preferably p = 0.05.

It will be appreciated by those skilled in the art that various measures of dispersion may be utilized without departing from the spirit of the invention, for example the

standard deviation, skew, various moments, histograms, and other calculations known in the art.

In a first alternate embodiment of the invention, the above described method is employed using either the real or the imaginary parts of the signal instead of the modulus. This embodiment achieves economy in hardware.

In a second alternate embodiment of the invention, the n parameter of equation (11) has been optimized. At the end of the guard interval, the two blocks straddle more of the transition to the active interval, giving a well-defined increase in the dispersion. Using any value n>2 has the drawback that several successive points will give significant increases as the later block travels up to the boundary. This small problem is easily overcome by introducing a dead period after detection of the boundary. That is, once a spike has been detected a set of samples equal to the size of the FFT window is accepted before further attempts are made to locate another spike. The dead period has the added benefit of not introducing false spikes. When using larger values of n the spikes 66, 68 ( Fig. 7) increase, whilst the H0 noisy F signal remain much the same. Example 2:

The maximum F-spike height as a function of n has been measured systematically together with the background variation in F. The results are shown in Table 2.

Table 2

Table 2 was developed using the first 5 frames of the signal analyzed in Fig. 7. The statistics in columns (2) and (3) of Table 2 were made by excluding any points where F>=3.0 to exclude spikes from the calculations. The spikes would otherwise affect the values of mean and standard deviation even though they are from a different statistical population.

The results indicate that the background variation in F, Fs d , was affected by n, increasing asymptotically to a value of approximately 0 28 It is likely that this is the effect of overlapping blocks For example, for N=64 and n<64, the blocks over which the dispersions are calculated will contain some of the same values and therefore be correlated To test this theory Fs d was evaluated for n>N, and the results are shown in Table 3

Table 3

The dependence becomes linear at n >= N/2 If F is calculated every n samples rather than every sample, then this dependence may be reduced However, this creates a risk for small guard intervals of not having the first block wholly within the guard interval and the second wholly within the active interval

A third alternateembodimentof the invention is disclosed with reference to Fig 10 which schematically illustrates a timing synchronization circuit 70 The circuit accepts a complex input signal 72, and includes a circuit module 74 which develops the modulus of its input, which is taken from node 83 The circuit module 74 insures that the value being subsequently processed is an unsigned number The input to the circuit module 74 is a difference signal which is developed by a subtracter 75 which takes as inputs the input signal 72 and a delayed version of the input signal 72 which has been processed through a delay circuit 79, preferably realized as a FIFO 77 of length L, where L is the size of the FFT window As explained above, it is also possible to operate this circuit where the input signal 72 is real, imaginary, or complex, or even the modulus of a complex number In the case where the input signal 72 is real, or imaginary, the circuit module 74 can be modified, and can be any known circuit that removes the sign of the output of the subtracter 75, or

sets the sign so that the outputs accumulate monotonically, i e the circuit has a unipolar output The output of the circuit module 74 is ultimately clocked into a digital delay, which is preferably implemented as a FIFO 78 When the FIFO 78 is full, a signal SIG1 80 is asserted and the output of the FIFO 78

becomes available, as indicated by the AND gate 82 An adder/subtracter circuit 84 is also connected to the node 76, and its output is stored in a register 86 A delayed version of the output of the adder/subtractercircuit 84 is taken from the register 86 and fed back as a second input to the adder/subtractercircuit 84 on line 88 In the event the signal SIG1 80 has been asserted, a version of the output of the circuit module 74, delayed by a first predetermined interval N, where N is the number of samples in the comparison blocks, is subtracted from the signal on node 76

The signal on line 88 is an index into a lookup table, preferably implemented as a read-only-memory ("ROM"), and shown as ROM 90 The address of the ROM 90 contains the logarithm to the base 2 of the magnitude of the signal on line 88, which then appears at node 92 The node 92 is connected to a subtracter 94, and to a delay circuit, shown as FIFO 98, which is used to develop the denommatorof the middle term of equation (17)

The subtracter 94 produces a signal which is compared against the log2 of a predetermined threshold value FUM,T in a comparison circuit 106, shown for simplicity as an adder 108 connected to a comparator 110 The output signal SYNC 112 is asserted when the boundary of a guard interval has been located

Although not implemented in the presently preferred embodiment, It is also possible to configure the size of the FIFO 77 dynamically, so that the size of the interval being evaluated can be adjusted according to operating conditions This may conveniently be done by storing the values on the node 92 in a RAM 114 for computation of their dispersion

In a fourth alternate embodimentof the invention explained with reference to Fig 11 , components similar to those of the embodiment shown in Fig 10 have the same reference numerals A timing synchronization circuit 1 16 is similar to the timing synchronization circuit 70, except now the delay circuit 79 is realized as the FIFO 77, and another FIFO 100, one of which is selected by a multiplexer 102 Both of the FIFOs 77, 100 provide the same delay, however the capacities of the two are different The FIFO 100 provides for storage of samples taken in an interval equal to the size of the FFT window, and is normally selected in a first mode of operation, for example during channel acquisition, when it is necessary to evaluate an entire symbol in order to locate a boundary of a guard interval in the noted European Telecommunications standard, up to 8K of data storage is required, with commensurate resource requirements During subsequent operation, the approximate location of the guard interval boundaries will be known from the history of the previous symbols In a second mode of operation, It is therefore only necessary to evaluate a much smaller interval in order to verify the exact location of the guard interval boundary The number of samples used in the computation

of the dispersion can be kept to a small number, preferably 32 or 64, and the much smaller FIFO 77 accordingly selected to hold the computed values The resources saved thereby can be utilized for other functions in the demodulator, and memory utilized by the larger FIFO 100 may also be reallocated for other purposes A control block 81 optionally advances the evaluation interval relative to symbol boundaries in the data stream in successive symbols, and can also be used to delay for the dead period Eventually the moving evaluation interval straddles the boundary of the current symbol's guard interval, and synchronization is then determined The size of the evaluation interval is chosen to minimize the use of memory, yet to be large enough to achieve statistical significance in the evaluation interval The size of the evaluation interval, and the FIFO 77 may be statically or dynamically configured Single Chip Implementation of a COFDM Demodulator Overview

Referring initially to Fig 12, there is shown a high level block diagram of a multicarrier digital receiver 126 in accordance with the invention The embodiment described hereinbelow conforms to the ETS 300 744 telecommunicationsstandard (2K mode), but can be adapted by those skilled in the art to operate with other standards without departing from the spirit of the invention A radio frequency signal is received from a channel such as an antenna 128, into a tuner 130 which is conventional, and preferably has first and second intermediate frequency amplifiers The output of the second intermediate frequency amplifier (not shown), is conducted on line 132 to an analog to digital converter 134 The digitized output of the analog to digital converter 134 is provided to block 136 in which l/Q demodulation, FFT, channel estimation and correction, inner and outer deinterleaving, and forward error correction are conducted Carrier and timing recovery are performed in block 136 entirely in the digital domain, and the only feedback to the tuner 130 is the automatic gain control ("AGC") signal which is provided on line 138 A steady 20 MHz clock on line 140 is provided for use as a sampling clock for the external analog to digital converter 134 A host microprocessor interface 142 can be either parallel or serial The system has been arranged to operate with a minimum of host processor support In particular channel acquisition can be achieved without any host processor intervention

The functions performed within the block 136 are grouped for convenience of presentation into a front end (Fig 13), FFT and channel correction group (Fig 14), and a back end (Fig 15) As shown in Fig 13, l/Q samples at are received by an IQ demodulator 144 from the analog to digital converter 134 (Fig 12) on a bus 146 at a rate of 20 megasamples per second An AGC circuit 148 also takes its input from the bus 146 A frequency rate

control loop is implemented using a numerically controlled oscillator 150, which receives frequency error signals on line 152, and frequency error update information on line 154. Frequency and sampling rate control are achieved in the frequency domain, based on the pilot carrier information. The frequency error signals, which are derived from the pilot carriers, and the frequency error update information will both be disclosed in further detail shortly. The I and Q data output from the IQ demodulator 144 are both passed through identical low pass filters 156, decimated to 10 megasamples per second, and provided to a sine interpolator 158. Sample rate control is achieved using a numerically controlled oscillator 160 which receives sample rate control information derived from the pilot signals on line 162, and receives sample error update timing information on line 164.

As shown in Fig. 14, acquisition and control of the FFT window are performed in block 166, which receives signals from the sine interpolator 158 (Fig. 13). The FFT computations are performed in FFT calculation circuitry 168. Channel estimation and correction are performed in channel estimation and correction block 170, and involves localization of the pilot carriers, as will be described below in greater detail. The tps information obtained during pilot localization is processed in tps sequence extract block 172. Uncorrected pilot carriers are provided by the circuitry of channel estimation and correction block 170 to correction circuitry 174, which develops sampling rate error and frequency error signals that are fed back to the numerically controlled oscillators 150, 160 (Fig. 13).

Referring to Fig. 15, corrected I and Q data output from channel estimation and correction block 170 are provided to demapping circuitry 176. The current constellation and hierarchical constellation parameters, derived from the tps data, are also input on lines 178, 180. The resulting symbols are deinterleaved in symbol deinterleaver 182, utilizing a 1512 x 13 memory store. One bit of each cell in the memory store is used to flag carriers having insufficient signal strength for reliable channel correction. Bit deinterleaver 184 then provides deinterleaved I and Q data to a Viterbi Decoder 186, which discards the flagged carriers, so that unreliable carriers do not influence traceback metrics. A Forney deinterleaver 188 accepts the output of the Viterbi Decoder 186 and is coupled to a Reed-Solomon decoder 190. The forward error correction provided by the Viterbi and Reed-Solomon decoders is relied upon to recover lost data in the case of flagged carriers.

Referring to Fig. 16, in the presently preferred embodiment a mean value is calculated in block 192 for uncorrected carriers with reference to the previous symbol. Data carriers whose interpolated channel response falls below some fraction, preferably 0.2, of this mean will be marked with a bad_carrier flag 194. The bad_carrier flag 194

is carried through the demapping circuitry 176, symbol deinterleaver 182, and bit deinterleaver 184, to the Viterbi Decoder 186 where it is used to discard data relating to the unreliable carriers The parameters used to set the bad_carrιer flag 194 can be varied by the microprocessor interface 142 An output interface 196 produces an output which can be an MPEG-2 transport stream The symbol deinterleaver 182, and the bit deinterleaver 184 are conventional The Viterbi decoder 186, Forney deinterleaver 188, Reed-Solomon decoder 190, and the output interface 196 are conventional They can be the components disclosed in copending Application No 638,273, entitled "An Error Detection and Correction System for a Stream of Encoded Data", filed April 26, 1996, Application No 480,976, entitled "Signal Processing System", filed June 7, 1995, and Application No 481 ,107, entitled "Signal Processing Apparatus and Method", filed June 7, 1995, all of which are commonly assigned herewith, and are incorporated herein by reference The operation of the multicarrier digital receiver 126 (Fig 12) is controlled by a system controller 198 Optionally the hierarchical constellation parameters can be programmed to speed up channel acquisition, rather than derived from the tps data

The input and output signals and the register map of the multicarrier digital receiver 126 are described in tables 4, and 5 respectively Automatic Gain Control The purpose of the AGC circuit 148 (Fig 3)ιs to generate a control signal to vary the gain of the COFDM input signal to the device before it is analog-to-digital converted As shown in greater detail in Fig 17 a Sigma-Delta modulator 200 is used to provide a signal which can be used as a gain control to a tuner once it has been low-pass filtered by an external R-C network The magnitude of the control voltage signal 202 is given by control_voltage = control_voltage - error (23) where error = K ( |data| - mean) (24)

where K is a constant (normally K«1 ) which determines the gam in the AGC control loop The mean value can be determined from the statistics of Gaussian noise, which is a close approximation to the properties of the COFDM input signal, where the input data is scaled to +/-1 The control voltage signal 202 is set back to its initial value when the signal resync 204 is set low, indicating a channel change or some other event requiring resynchronization

The input and output signals and the registers for the microprocessorinterface 142 of the AGC circuit 148 are described in tables 6, 7, and 8 respectively

IQ Demodulator

The function of the IQ demodulator 144 (Fig 13) is to recover m-phase and quadrature components of the received sampled data It is shown in further detail in Fig 18 The numerically controlled oscillator 150 generates m-phase and quadrature sinusoids at a rate of (32/7) MHz, which are multiplied with data samples in multipliers 206 The address generator 208 advances the phase linearly The frequency error input 210 increments or decrements the phase advance value The samples are multiplied with the sinusoids in the multipliers 206usιng 10 bit x 10 bit multiply operations In one embodiment the IQ demodulator 144 is operated at 20 MHZ and then retimed to 40MHz in retiming block 212 In a preferred embodiment the IQ demodulator 144 is operated at 40MHz, in which case the retiming block 212 is omitted

Sinusoids are generated by the address generator 208 on lines 214, 216 The phase value is employed as an address into a lookup table ROM 218 Only quarter cycles are stored in the lookup table ROM 218 to save area Full cycles can be generated from the stored quarter cycles by manipulating the data from the ROM 218 and inverting the data in the case of negative cycles Two values are read from the lookup table ROM 218 for every input sample - a cosine and a sine, which differ in phase by 90 degrees The input and output signals of the IQ demodulator 144 are described in tables 9 and 10 respectively Low Pass Filter

The purpose of the low pass filters 156 (Fig 13) is to remove aliased frequencies after IQ demodulation - frequencies above the 32/7 MHz second IF are suppressed by 40dB I and Q data are filtered separately The output data is decimated to 10 megasamples per second ("Msps") because the filter removes any frequencies above 1/4 of the original 20 Msps sampling rate The filter is constructed with approximately 60 taps which are symmetrical about the center allowing the filter structure to be optimized to reduce the number of multipliers 220 Fig 19 is a block diagram of one of the low pass filters 156, the other being identical Fig 19 shows a representative symmetrical tap 222, and a center tap 224 The required filter response of the low pass filters 156 is shown in Fig 20

The input and output signals of the low pass filters 156 are described in tables 11 and 12 respectively Resampling

Referring to Fig 13, the purpose of resampling is to reduce the 10 Msps data stream output from the low pass filters 156 down to a rate of (64/7) Msps, which is the

nominal sample rate of the terrestrial digital video broadcasting ("DVB-T") modulator at the transmitter.

Resampling is accomplished in the sine interpolator 158, and the numerically controlled oscillator 160. The latter generates a nominal 64/7 MHZ signal. The resampling circuitry is shown in further detail in Fig. 21. The numerically controlled oscillator 160 generates a valid pulse on line 226 and a signal 228 representing the interpolation distance for each 40MHz clock cycle in which a 64/7MHz sample should be produced. The interpolation distance is used to select the appropriate set of interpolating filter coefficients which are stored in coefficient ROMs 230. It should be noted that only the sine interpolatorfor I data is illustrated in Fig. 21. The structures for Q data are identical.

Fig. 22 illustratesthe generation of the interpolation distance and the valid pulse. Nominally Ts = 1/10 Msps, and T = 1/ (64/7) Msps. The sine interpolation circuit disclosed in our noted Application No. 08/638,273 is suitable, with appropriate adjustment of the operating frequencies.

The input and output signals of the sine interpolator 158 and the numerically controlled oscillator 160 are described in tables 13 and 14 respectively. FFT Window

As has been explained in detail above, the function of the FFT Window function is to locate the "active interval" of the COFDM symbol, as distinct from the "guard interval". This function is referred to herein for convenience as "FFT Window". In this embodiment the active interval contains the time domain representation of the 2048 carriers which will be recovered by the FFT itself.

The FFT window operates in two modes; Acquisition and Tracking. In Acquisition mode the entire incoming sample stream is searched for the guard interval/active interval boundary. This is indicated when the F-ratio reaches a peak, as discussed above. Once this boundary has been located, window timing is triggered and the incoming sample stream is searched again for the next guard interval/active interval boundary. When this has been located the length ofthe guard interval is known and the expected position of the next guard/active boundary can be predicted. The FFT window function then switches to tracking mode.

This embodiment is similar to the fourth alternate embodiment discussed above in respect of the tracking mode. In tracking mode only a small section of the incoming sample stream around the point where the guard/active boundary is expected to be is searched. The position of the active interval drifts slightly in response to IF frequency and sampling rate offsets in the front-end before the FFT is calculated. This drift is

tracked and FFT window timing corrected, the corrections being inserted only during the guard interval

It will be appreciated by those skilled in the art that in a practical single chip implementation as is disclosed herein, memory is an expensive resource in terms of chip area, and therefore must be minimized Referring to Fig 23, during Acquisition mode the FFT calculation process is not active so hardware can be shared between the FFT Window and the FFT calculation, most notably a 1024x22 RAM 232 used as a FIFO by the FFT Window, and selected for receipt of FFT data on line 234 by a multiplexer 236 Once in Tracking mode the FFT calculation process is active so that other control loops to recover sampling rate and frequency which depend on FFT data (e g pilots in the COFDM symbol) can initialize Therefore tracking mode requires a dedicated tracking FIFO 238, which is selected by a multiplexer 240

The input and output signals, and signals relating to the microprocessor interface 142 of the FFT Window circuitry shown in Fig 23 are described in tables 15, 16, and 17 respectively

In one embodiment a threshold level, set from statistical considerations, is applied to the F-ratio signal (see Fig 7) to detect the negative and positive spikes which occur at the start and end of the guard interval respectively The distance between the spikes is used to estimate the guard interval size Repeated detection of the positive spikes is used to confirm correct synchronization However with this method under noisy conditions the F-ratio signal becomes noisy and the spikes are not always reliably detectable

In another embodiment peak detection is used to find the spikes in the F-ratios It has been found that a fixed threshold is reliable only at or exceeding about a carπer- to-noise ("C/N") ratio of 12 dB Peak detection is generally more sensitive and more specific, with generally reliable operation generally at 6 - 7 dB The maxima should occur at the end of the guard interval The difference in time between the two maxima is checked against the possible guard interval sizes With an allowance for noise, the difference in time indicates the most likely guard interval size and the maxima themselves provide a good indication of the start of the active part of the symbol

Preferably this process is iterated for several symbols to confirm detection, and is expected to improve performance when the C/N ratio is low

The data stream is passed to accumulators 242, 244, each holding 64 moduli Conversion to logarithms and subtraction of the logarithms is performed in block 246 The peaks are detected in peak detector block 248 Averaging of the symbol peaks is performed in block 250

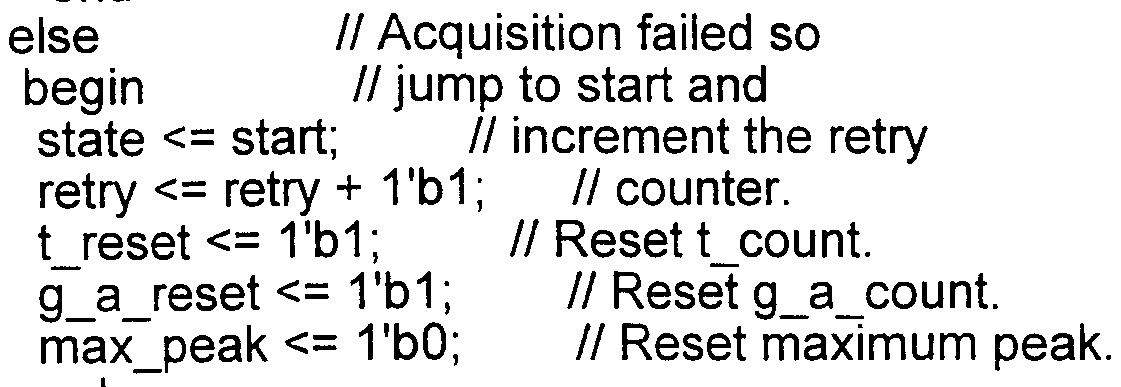

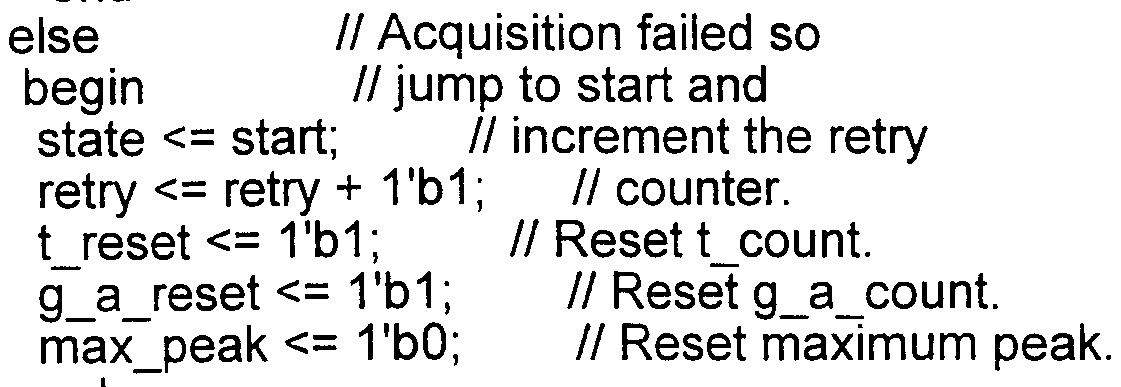

In noisy conditions, the maxima may be due to noise giving possibly inaccurate indications of the guard interval length and the start of the active symbol The general strategy to cope with this is to perform a limited number of retries

Currently, calculation of the F-ratio is done "on the fly" i e only once at each point The variance estimates are calculated from 64 values only Under noisy conditions, the variance estimates become very noisy and the spikes can become obscured In an optional variation this problem is solved by obtaining more values for the variance estimate, by storing the variance estimate during acquisition for each of the possible T+Gmax points in the storage block 256 The variance estimates themselves may be formed by accumulating variances for each point, and then filtering in time over a number of symbols A moving average filter or an infinite impulse response ("MR") filter is suitable A moving run of symbols, preferably between 16 and 32, are integrated in block 252, which increases the reliability of peak detection under noisy conditions The storage block 256 holding the integrated F-ratio values is searched to find the maximum value This is of length T+Gmax, where Gmax is the maximum guard interval size, T/4 Preferably the memory for storage block 256 is dynamically allocated, depending on whether acquisition mode or tracking mode is operative Any unused memory is released to other processes Similarly in tracking mode the integrated data stream is stored in tracking integration buffer 254 This method has been tested with up to 4 symbols, without an MR filter, and it has been found that the spikes can be recovered However this approach does require increased memory FFT Processor

The discrete Fourier transform ("DFT") has the well known formula

L 1

1 x(k) = Σ x(n)W nk k = 0,1 , ,N -1 (25) n 0 where N = the number of points in the DFT, x(k) = the kth output in the frequency domain, x(n) = the nth input in the time domain and

W nk = e J(2πnk/L) (26)

W is also known as a "twiddle factor" For N > 1000 the DFT imposes a heavy computational burden and becomes impractical Instead the continuous Fourier transform is used, given by

t +00 x(t) = f x(t)e "jωtdt (27) t - -oc

The continuous Fourier transform, when computed according to the well known FFT algorithm, breaks the original N-point sequence into two shorter sequences In the present invention the FFT is implemented using the basic butterfly unit 258 as shown in Fig 24 The outputs C and D represent equations of the form C = A + B, and D = (A - B)Wk The butterfly unit 258 exploits the fact that the powers of W are really just complex additions or subtractions

A real-time FFT processor, realized as the FFT calculation circuitry 168 (Fig 14) is a key component in the implementation of the multicarrier digital receiver 126 (Fig 12) Known 8K pipeline FFT chips have been implemented with 1 5M transistors, requiring an area of 100 mm2 in 0 5μ technology, based on the architecture of Bi and Jones Even using a memory implementation with 3-transιstor digital delay line techniques, over 1 M transistors are needed This has been further reduced with alternative architecture to 0 6M, as reported in the document A New Approach to Pipeline FFT Processor Shousheng He and Mats Torkelson, Teracom Svensk RundRadio DTTV-SA 180, TM 1547 This document proposes a hardware-oriented radιx-22 algorithm having radιx-4 multiplicative complexity However the requirements of the FFT computation in the present invention require the implementation of a radix 22+2 FFT processor

Referring to Fig 25 and Fig 26 the butterfly structures BF2I 260 and BF2II 262 known from the noted Torkelson publication, are shown The butterfly structure BF2II 262 differs from the butterfly structure BF2I 260 in that it has logic 264 and has a crossover 266 for crossing the real and imaginary inputs to facilitate multiplication by -j

Fig 27 illustratesthe retimed architecture of a radix 22 + 2 FFT processor 268 in accordance with the invention, which is fully pipelined, and comprises a plurality of stages, stage-0 270 through stage-6 272 Except for stage-0 270, the stages each comprise one butterfly structure BF2I 260 and one butterfly structure BF2H 262, and storage RAMS 274, 276 associated therewith stage-0 270 only has a single butterfly structure BF2I 260 This architecture performs a straight-forward 32-poιnt FFT stage-6 272 has control logic associated therewith, including demultiplexer 278 and multiplexer 280, allowing stage-6 272 to be bypassed, thus providing a 2K implementation of the FFT Counters 282 configure the butterfly structures BF2I 260 and BF2II 262 to select one of the two possible diagonal computations, during which data is being simultaneously written to and read from the storage RAMS 274, 276

Fig 28 illustrates a 32 point flow graph of the FFT processor 268 using radix 22+2 pipeline architecture Computations are performed using eight 4-poιnt FFTs and four 8- point FFTs These are decomposed in turn into two 4-poιnt FFTs and four 2-poιnt FFTs Fig 29 illustrates the retimed architecture of a configurable 2K/8K radix 22+2 single path, delay feedback pipelined FFT processor 284, in which like elements in Fig 27 are given the same reference numerals The stages have a plurality of pipeline registers 286 which are required for proper timing of the butterfly structures BF2I 260 and BF2II 262 in the various stages As can be seen, the addition of each pipelined stage multiplies the range of the FFT by a factor of 4 There are 6 complex multipliers 288, 290, 292, 294, 296, 298 which operate in parallel This processor computes one pair of l/Q data points every four fast clock cycles, which is equivalentto the sample rate clock Using 0 35μm technology the worst case throughput is 140μs for the 2K mode of operation, and 550μs for the 8K mode, exceeding the requirements of the ETS 300 744 telecommunicationsstandard Data enters the pipeline from the left side of Fig 29, and emerges on the right The intermediate storage requirements are 2K/8K for I data and 2K/8K for Q data, and is mode dependent In practice the radιx-4 stage is implemented as a cascade of two adapted radιx-2 stages that exploit the radιx-4 algorithms to reduce the number of required complex multipliers

Fig 30 is a schematic of one embodiment of the multipliers 288, 290, 292, 294, 296, 298 for performing the complex multiplication C = A x B, where A is data, and B is a coefficient Because the FFT processor 284 has 6 complex multipliers, each requiring 3 hardware multipliers 300, a total of 18 hardware multipliers 300 would be required It is preferable to use the embodiment of Fig 31 in which some ofthe hardware multipliers 300 are replaced by multiplexers 302, 304 Turning again to Fig 29 there are a plurality of RAMS 306, 308, 310, 312, 314,

316 which are preferably realized as ROMs and contain lookup tables containing complex coefficients comprising cosines for the multipliers 288, 290, 292, 294, 296, 298 respectively It has been discovered that by addressing the RAMS 306, 308, 310, 312, 314, 316 according to a particular addressing scheme, the size of these RAMS can be markedly reduced The tradeoff between the complexity of the addressing circuitry and the reduction in RAM size becomes favorable beginning at stage-3318 Referring again to Fig 28 there are two columns 320, 322 Column 320 holds values W2 - W14, followed by W1 - W7, and then W3 - W21 These coefficients are stored in the RAM 308, required by the particular multiplier 290 Column 322 contains values W8, W4, W12, which repeat 3 times Note turtherthat between the values W8, W4, and W4, W12 are connections 324, 326 to the preceding butterfly unit located in column 328 In practice the connections 324, 326 are implemented as multiplications by W° In moving from multiplier to

multiplier toward the left in Fig. 29, the lookup table space is multiplied by a power of 4 at each stage. In Fig. 32 table 330, the lookup table for multiplier M3 contains 512 entries. It can be deduced by extrapolation that multiplier M5 must contain 8192 twiddle factors, and corresponds to the size of the FFT being performed by the FFT processor 284 (Fig. 29).

Before examining the look-up table space in more detail it is helpful to considerthe plurality of horizontal lines 332. Moving downward from the top of Fig. 28, the line beginning at x(3) extends to W8, which is the first twiddle factor required, and is at the third effective step in the flow diagram. Figs. 33 and 32 show the organization of the twiddle factors for each of the multipliers, wherein the terminology Mk represents the multiplier associated with the kth stage. Thus table 334 relates to multiplier M0. The notation for the W values (twiddle factors) is shown in box 336. The subscript "B" at the bottom right represents a time stamp, that is an order dependency in which the twiddle factors are required by the pipeline. The superscript "A" represents the address of the twiddle factor in its lookup table. The superscript "N" is the index of the twiddle factor.

Thus in table 334 it may be seen that W° is required at time 0, W1 at time 1 , and

W° is again required at time 2. Further inspection of the other tables in Figs. 33, 32 reveals that half of the entries in each table are redundant. The storage requirementfor the lookup tables can be decreased by 50% by eliminating redundant entries. This has been accomplished by organizing the W values in ascending order by index, so that the values can be stored in memory in ascending order. Thus in the case of table 338 the index values range from 0 to 21 , with gaps at 11 , 13, 16, 17, 19, and 20.

The procedure for organizing the lookup table and the addressing scheme for accessing the twiddle factors is explained with reference to table 338, but is applicable to the other tables in Fig. 33. (1) Each row is assigned a line number as illustrated. (2) Each twiddle factor is assigned an order dependency which is noted in the lower right of its respective cell in table 338. (3) It is assumed that table 338 in its reduced form will contain only unique twiddle factors in ascending order by index within the memory address space. Consequently each twiddle factor is assigned a memory address as shown in the upper left of its respective cell.

During address generation, for line 3 of table 338 the address is simply held at 0. For line 1 the address is incremented by 1 to the end of the line. However lines 0 and 2 contain non-trivial address sequences. For line 0, looking at table 340, which contains 64 values, it will be observed that the address sequence changes according to the intervals 2,2,2,2, and then later 1 , 1 ,2, 1 , 1 ,2... For line 2, the address first increments by 3, then by 2, and finally by 1. The locations at which the address increments change are

referred to herein as the "break-points". These values ofthe break points range between 0, corresponding to the first point in line 2, to the last position in the line.

By inspection it can be seen that the occurrence of the first break point changes from table to table following the recurrence relationship B1MN = 4B1MH I (28) with the initial condition

B M0 = 1 (29) where MN is the multiplier of the Nth stage of the FFT processor 284.

Expanding the recurrence relationship gives:

B1MN = («4B1Mo-1)x4-1)x4-1) ... (30)

B1, 4NB1 ιN-3 i N-2

(31)

Similarly the second break point B2 for line 2 is determined from the recurrence relation

B2MN = 4B2MN_ + 1 (33) with the initial condition

B2M0 = 1 (34) or

B2MN = (((4B2Mo + 1)x4+1)x4+1) ... {35)

B2MN = ∑4Π (36) n=0