RU2433503C1 - Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров - Google Patents

Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров Download PDFInfo

- Publication number

- RU2433503C1 RU2433503C1 RU2010129098/28A RU2010129098A RU2433503C1 RU 2433503 C1 RU2433503 C1 RU 2433503C1 RU 2010129098/28 A RU2010129098/28 A RU 2010129098/28A RU 2010129098 A RU2010129098 A RU 2010129098A RU 2433503 C1 RU2433503 C1 RU 2433503C1

- Authority

- RU

- Russia

- Prior art keywords

- mos

- indium

- substrate

- sources

- multiplexers

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 13

- 229910052738 indium Inorganic materials 0.000 claims abstract description 26

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims abstract description 24

- 239000000758 substrate Substances 0.000 claims abstract description 18

- 239000013078 crystal Substances 0.000 claims abstract description 10

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 6

- 239000010703 silicon Substances 0.000 claims abstract description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 3

- 230000007547 defect Effects 0.000 claims description 12

- 230000001681 protective effect Effects 0.000 claims description 3

- 238000001514 detection method Methods 0.000 claims description 2

- 230000015572 biosynthetic process Effects 0.000 claims 1

- 239000011248 coating agent Substances 0.000 abstract 1

- 238000000576 coating method Methods 0.000 abstract 1

- 230000005611 electricity Effects 0.000 abstract 1

- 230000008030 elimination Effects 0.000 abstract 1

- 238000003379 elimination reaction Methods 0.000 abstract 1

- 239000000126 substance Substances 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 2

- 238000003032 molecular docking Methods 0.000 description 2

- 238000012544 monitoring process Methods 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 239000011148 porous material Substances 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

Images

Landscapes

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

Abstract

Изобретение относится к технологии изготовления и способам тестирования МОП мультиплексоров. Сущность изобретения: в способе обнаружения скрытых дефектов кремниевых МОП мультиплексоров на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке, наносят слой индия, формируют область индия, которая закорачивает все истоки МОП транзисторов на подложку в каждом кристалле. При этом область индия, которая закорачивает все истоки МОП транзисторов на подложку, выполняют в виде полос, расположенных только над истоками МОП транзисторов. Затем проводят контроль годных кристаллов с обнаружением скрытых дефектов и проводят формирование In столбиков. Способ позволяет увеличить надежность метода обнаружения скрытых дефектов кремниевых МОП мультиплексоров за счет исключения прямых закороток стоковых областей на подложку. 4 ил.

Description

Изобретение относится к технологии изготовления и способам тестирования МОП мультиплексоров.

В настоящее время широко используется способ изготовления гибридных ИК матричных фотоприемных устройств (МФПУ) методом перевернутого монтажа фоточувствительных элементов с МОП мультиплексором при помощи индиевых столбиков. После стыковки часто обнаруживаются электрические дефекты МОП мультиплексора, определить которые без специальных мер тестирования до стыковки невозможно, например электрическое короткое замыкание между входными контактами и выходными шинами МОП мультиплексора (исток - шина стока ключевого МОП транзистора) в ячейке матрицы считывания фотосигнала.

Известно, что для выявления упомянутого выше дефекта используется сплошной слой In толщиной не менее толщины окисного слоя, закорачивающий все истоки МОП транзисторов слоем индия на подложку [RU, патент на изобретение №2388110 С1]. Путь тока при этом: стоковая шина-дефект-исток-слой индия-подложка.

Указанный метод обнаружения дефектов имеет следующие недостатки: наличие слоя индия над металлизированными шинами стоков может приводить к их закоротке на подложку слоем индия напрямую через дефект (пору) в защитном окисле над стоком, миную область истока, что можно назвать «ложной тревогой», так как в рабочей структуре слоя индия над стоковыми шинами нет. Путь тока в этом случае: стоковая шина-дефект-слой индия-подложка.

Задачей изобретения является увеличение надежности (достоверности) метода обнаружения скрытых дефектов кремниевых МОП мультиплексоров за счет исключения прямых закороток стоковых областей на подложку путем формирования в каждом кристалле МОП мультиплексора слоя индия в виде полос только над истоками МОП транзисторов.

Технический результат достигается тем, что:

- на металлизированные площадки истоков, вскрытые в окисле, наносят слой индия толщиной, равной необходимой высоте In столбика;

- при помощи фотолитографической обработки формируют в каждом кристалле область индия в виде полос, которые располагаются только над истоками МОП транзисторов и закорачивают их на подложку;

- контролируют функционирование мультиплексоров и фиксируют наличие дефектов, в том числе и электрические закоротки исток-сток, которые не проявлялись при контроле функционирования без индия;

- далее методом фотолитографии формируют индиевые столбики высотой, равной толщине напыленной пленки индия.

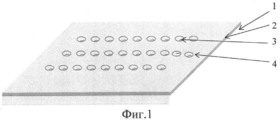

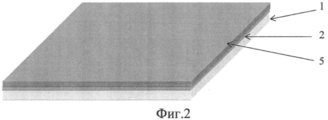

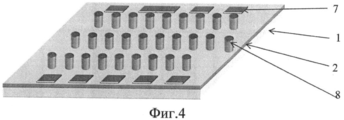

Последовательность технологической цепочки предлагаемого способа иллюстрируется на фиг.1-4, где:

1 - годный кристалл МОП мультиплексора, являющийся частью пластины;

2 - слой защитного окисла;

3 - контактные окна к металлизированным площадкам истоков МОП транзисторов;

4 - контактное окно к подложке;

5 - слой индия;

6 - область индия в виде полос, сформированная только над истоками МОП транзисторов мультиплексора и закорачивающая их на подложку;

7 - контактные площадки для контроля функционирования МОП мультиплексора;

8 - индиевые столбики.

Способ обнаружения скрытых дефектов МОП мультиплексоров осуществляется в следующей последовательности:

- на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке (фиг.1);

- напыляют слой индия толщиной, равной необходимой высоте In столбиков (фиг.2);

- проводят фотолитографическую обработку по слою индия для получения области индия в виде полос, расположенных только над истоками МОП транзисторов, которая закорачивает все истоки МОП транзисторов на подложку (фиг.3);

- проводят контроль функционирования годных МОП мультиплексоров с выявлением скрытых дефектов - закороток исток-сток;

- проводят фотолитографическую обработку по слою индия для формирования столбиков, режут пластину на кристаллы, осуществляют травление индия для формирования столбиков (фиг.4).

Предлагаемый способ обнаружения дефектов гармонично вписывается в технологию изготовления МОП мультиплексоров.

Изготовлены экспериментальные образцы кремниевых МОП мультиплексоров с проведением тестирования на предмет обнаружения скрытых дефектов методом закорачивания истоков МОП транзисторов на подложку слоем индия с рельефом 3…4 мкм и с последующей фотолитографией для получения однородных столбиков высотой 9…10 мкм.

Claims (1)

- Способ обнаружения скрытых дефектов кремниевых МОП мультиплексоров, заключающийся в том, что на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке, наносят слой индия, формируют область индия, которая закорачивает все истоки МОП транзисторов на подложку в каждом кристалле, проводят контроль годных кристаллов с обнаружением скрытых дефектов, проводят формирование In столбиков, отличающийся тем, что область индия, которая закорачивает все истоки МОП транзисторов на подложку выполняют в виде полос, расположенных только над истоками МОП транзисторов.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010129098/28A RU2433503C1 (ru) | 2010-07-13 | 2010-07-13 | Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010129098/28A RU2433503C1 (ru) | 2010-07-13 | 2010-07-13 | Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU2433503C1 true RU2433503C1 (ru) | 2011-11-10 |

Family

ID=44997363

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2010129098/28A RU2433503C1 (ru) | 2010-07-13 | 2010-07-13 | Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU2433503C1 (ru) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2523752C1 (ru) * | 2013-04-01 | 2014-07-20 | Российская Федерация, От Имени Которой Выступает Министерство Промышленности И Торговли Российской Федерации | Способ обнаружения скрытых дефектов матричных бис считывания |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2005308C1 (ru) * | 1991-01-09 | 1993-12-30 | Московский Инженерно-Физический Институт | Способ ускоренных испытаний МОП-интегральных микросхем на пластине |

| RU2073254C1 (ru) * | 1993-06-25 | 1997-02-10 | Московский Инженерно-Физический Институт | Способ контроля моп полупроводниковых приборов и интегральных схем на пластинах |

| US6275059B1 (en) * | 1997-04-04 | 2001-08-14 | University Of Florida | Method for testing and diagnosing MOS transistors |

| RU2388110C1 (ru) * | 2009-02-19 | 2010-04-27 | Федеральное государственное унитарное предприятие "НПО "ОРИОН" | Способ обнаружения скрытых дефектов матричных или линейных моп мультиплексоров |

-

2010

- 2010-07-13 RU RU2010129098/28A patent/RU2433503C1/ru active IP Right Revival

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2005308C1 (ru) * | 1991-01-09 | 1993-12-30 | Московский Инженерно-Физический Институт | Способ ускоренных испытаний МОП-интегральных микросхем на пластине |

| RU2073254C1 (ru) * | 1993-06-25 | 1997-02-10 | Московский Инженерно-Физический Институт | Способ контроля моп полупроводниковых приборов и интегральных схем на пластинах |

| US6275059B1 (en) * | 1997-04-04 | 2001-08-14 | University Of Florida | Method for testing and diagnosing MOS transistors |

| RU2388110C1 (ru) * | 2009-02-19 | 2010-04-27 | Федеральное государственное унитарное предприятие "НПО "ОРИОН" | Способ обнаружения скрытых дефектов матричных или линейных моп мультиплексоров |

Non-Patent Citations (1)

| Title |

|---|

| Low-Bias CTIA Multiplexer for 1024 Element InGaAs Line Sensors. Walter F. Kosonocky at all. SPIE, v.2226, 1994, p.152. * |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2523752C1 (ru) * | 2013-04-01 | 2014-07-20 | Российская Федерация, От Имени Которой Выступает Министерство Промышленности И Торговли Российской Федерации | Способ обнаружения скрытых дефектов матричных бис считывания |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20100055809A1 (en) | Process of fabricating a workpiece using a test mask | |

| CN102629613B (zh) | 一种x射线传感器的制作方法 | |

| CN103618499B (zh) | 一种太阳能电池片pid测试装置及测试方法 | |

| KR20160143800A (ko) | 어레이 기판 및 그 제조 방법, x-선 평판 검출기 및 카메라 시스템 | |

| CN102664184A (zh) | 一种x射线检测装置的阵列基板及其制造方法 | |

| US9515118B2 (en) | Radiation detecting panel | |

| EP2856135B1 (fr) | Capteur isfet avec dispositif de controle integre | |

| KR101428115B1 (ko) | 박막 트랜지스터 어레이를 위한 전기 바이어스 스트레스를 사용한 어레이 시험 방법 | |

| JP5923972B2 (ja) | 光電変換装置の製造方法および当該光電変換装置を用いた撮像装置の製造方法 | |

| US20130306873A1 (en) | Radiation detecting panel | |

| RU2415493C1 (ru) | Способ обнаружения скрытых дефектов матричного или линейного кремниевого моп мультиплексора | |

| RU2433503C1 (ru) | Способ обнаружения скрытых дефектов кремниевых моп мультиплексоров | |

| RU2388110C1 (ru) | Способ обнаружения скрытых дефектов матричных или линейных моп мультиплексоров | |

| US9588237B2 (en) | Digital X-ray detector and method for manufacturing the X-ray detector | |

| RU2474918C1 (ru) | Способ обнаружения скрытых электрических дефектов матричных или линейных кремниевых моп мультиплексоров | |

| US20110180716A1 (en) | Radiation detection element | |

| US20210272859A1 (en) | Array substrate and fabrication method thereof, and display device | |

| CN115565903B (zh) | 一种封装过程中电性检测方法 | |

| EP2810058A1 (en) | Radiation detecting panel | |

| KR20150067830A (ko) | 엑스레이 검출기의 어레이 기판 및 그의 제조 방법 | |

| TW506013B (en) | Etching method and apparatus for semiconductor device | |

| US20150177319A1 (en) | Integrated circuits with copper hillock-detecting structures and methods for detecting copper hillocks using the same | |

| CN107170765B (zh) | 一种探测基板及其制备方法、x射线探测器 | |

| CN110854092A (zh) | 共享接触孔及其刻蚀缺陷检测方法 | |

| WO2014081694A1 (en) | Detecting defects within photovoltaic modules |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| MM4A | The patent is invalid due to non-payment of fees |

Effective date: 20140714 |

|

| NF4A | Reinstatement of patent |

Effective date: 20160910 |