RU102403U1 - INFORMATION STORAGE DEVICE - Google Patents

INFORMATION STORAGE DEVICE Download PDFInfo

- Publication number

- RU102403U1 RU102403U1 RU2010128076/08U RU2010128076U RU102403U1 RU 102403 U1 RU102403 U1 RU 102403U1 RU 2010128076/08 U RU2010128076/08 U RU 2010128076/08U RU 2010128076 U RU2010128076 U RU 2010128076U RU 102403 U1 RU102403 U1 RU 102403U1

- Authority

- RU

- Russia

- Prior art keywords

- inputs

- input

- block

- elements

- information

- Prior art date

Links

Landscapes

- Error Detection And Correction (AREA)

Abstract

Устройство хранения информации, содержащее узел памяти, входной блок кодирования, формирующий значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов х1, х2, х3, у1, у2, у3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕у1⊕у2; r2=х2⊕х3⊕у2⊕у3, выходной блок кодирования, формирующий значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов х1C, х2C, х3C, у1C, у2C, у3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1С⊕х2С⊕у1С⊕у2С; r2П=х2C⊕х3C⊕у2C⊕у3C, блок выявления ошибки, первый блок элементов И, элемент И, первый блок элементов ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, отличающееся тем, что дополнительно содержит второй блок элементов ИЛИ, второй блок элементов, третий блок элементов И, причем вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к первым входам второго блока элементов ИЛИ, вторые входы которого подключены к выходам второго блока элементов И, а выходы подключены к входам блока кодирования, выходы которого подключены к шестым входам узла памяти и к первым входам блока выявления ошибки, вход синхронизации подключен к седьмому входу узла памяти и к первым входам п� An information storage device comprising a memory unit, an input coding unit, generating control bit values r1 and r2 by adding modulo 2 information symbols x1, x2, x3, y1, y2, y3 to the inputs of the input coding unit, in accordance with the rule: r1 = x1⊕x2⊕u1⊕u2; r2 = х2⊕х3⊕у2⊕у3, the output coding unit, which forms the values of the test check bits r1П, r2П by adding modulo 2 information symbols х1C, х2C, х3C, у1C, у2C, у3C, received at the inputs of the output encoding unit and received at reading information from the information outputs of the memory node in accordance with the rule: r1P = x1C⊕x2C⊕u1C⊕u2C; r2P = х2C⊕х3C⊕у2C⊕у3C, error detection block, first block of AND elements, AND element, first block of OR elements, device zeroing input, write input, read input, address inputs, information inputs, synchronization input, information outputs, signal output when an error occurs, characterized in that it further comprises a second block of OR elements, a second block of elements, a third block of AND elements, and the input to the zero state, write input, read input, address inputs are connected respectively to the first , to the second, third and fourth inputs of the memory node, the information inputs are connected to the fifth inputs of the memory node and to the first inputs of the second block of OR elements, the second inputs of which are connected to the outputs of the second block of AND elements, and the outputs are connected to the inputs of the coding block, the outputs of which are connected to sixth inputs of the memory node and to the first inputs of the error detection unit, the synchronization input is connected to the seventh input of the memory node and to the first inputs of

Description

Устройство хранения информации повышенной достоверности функционирования относится к вычислительной технике и может быть использовано для повышения достоверности функционирования работы, устройств хранения и передачи информации.An information storage device with increased reliability of operation relates to computer technology and can be used to increase the reliability of the operation of information storage and transmission devices.

Известно устройство памяти с контролем на четность [1], содержащее узел памяти, входной блок формирования дополнительного разряда проверки на четность, выходной блок формирования дополнительного разряда проверки на четность, элемент неравнозначности, информационные входы устройства подключены к узлу памяти и к входам входного блока формирования дополнительного разряда проверки на четность, выходы узла памяти являются информационными выходами устройства и подключены к входам выходного блока формирования дополнительного разряда проверки на четность, выход которого подключен к первому входу элемента неравнозначности, второй вход элемента неравнозначности соединен с выходом входного блок формирования дополнительного разряда проверки на четность, и с его выхода снимается сигнал при возникновении ошибки.A memory device with a parity check [1] is known, comprising a memory node, an input unit for generating an additional parity check bit, an output unit for generating an additional parity check bit, an ambiguity element, information inputs of the device are connected to the memory node and to the inputs of the input additional generating unit parity check, the outputs of the memory node are the information outputs of the device and are connected to the inputs of the output block of the formation of an additional discharge A parity check, the output of which is connected to the first input of the disambiguation element, the second input of the disambiguation element is connected to the output of the input unit for generating an additional parity check digit, and a signal is removed from its output when an error occurs.

Недостатком устройства является низкая достоверность функционирования устройства, так как обнаруживаются только одиночные (нечетные) ошибки, т.е. обнаруживается 50% возможных ошибок.The disadvantage of this device is the low reliability of the device, since only single (odd) errors are detected, i.e. 50% of possible errors are detected.

Наиболее близким по техническому решению является устройство хранения и передачи информации с обнаружением двойных ошибок [2], содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к входам входного блока кодирования, выходы которого подключены к шестым входам узла памяти, вход синхронизации подключен к седьмому входу узла памяти и к первым входам блока элементов И и элемента И, первые выходы узла памяти подключены к входам выходного блока кодирования и к вторым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока выявления ошибки, к вторым входам которого подключены вторые выходы узла памяти, а выходы подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала при возникновении ошибки.The closest in technical solution is a device for storing and transmitting information with the detection of double errors [2], containing a memory node, an input coding unit, an output coding unit, an error detection unit, a block of AND elements, an AND element, an OR element, an input to set the device to zero status, write input, read input, address inputs, information inputs, synchronization input, information outputs, signal output in case of an error, zero input, write input, read input, address inputs are connected to the first, second, third and fourth inputs of the memory node, respectively, information inputs are connected to the fifth inputs of the memory node and to the inputs of the input coding block, the outputs of which are connected to the sixth inputs of the memory node, the synchronization input is connected to the seventh input of the memory node and the first inputs of the block of elements And and the element And, the first outputs of the memory node are connected to the inputs of the output coding block and to the second inputs of the block of elements And, the outputs of the output coding block are connected to the first inputs of the detection block Errors, to second inputs of which are connected the second output of the storage unit, and outputs connected to inputs of the OR gate, an output of OR connected to the second input of the AND gate, the outputs of the block elements and data outputs are device yield and the element is the output signal when an error occurs.

Недостатком устройства является большая аппаратурная избыточность, так как используются два блока кодирования: входной блок кодирования и выходной блок кодирования информации.The disadvantage of this device is a large hardware redundancy, since two coding units are used: an input coding unit and an output information coding unit.

Целью полезной модели является сокращение аппаратурных затрат за счет использования одного блока кодирования, выполняющего кодирование входной и выходной информации.The purpose of the utility model is to reduce hardware costs by using a single coding unit that encodes input and output information.

Поставленная цель достигается тем, что устройство, содержащее узел памяти, блок кодирования, блок выявления ошибки, первый блок элементов И, элемент И, первый блок элементов ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала при возникновении ошибки, дополнительно содержит второй блок элементов ИЛИ, второй блок элементов, третий блок элементов И, причем вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к первым входам второго блока элементов ИЛИ, вторые входы которого подключены к выходам второго блока элементов И, а выходы подключены к входам блока кодирования, выходы которого подключены к шестым входам узла памяти и к первым входам блока выявления ошибки, вход синхронизации подключен к седьмому входу узла памяти и к первым входам первого блока элементов И и к первому входу элемента И, первые выходы узла памяти подключены к вторым входам первого блока элементов И и к первым входам второго блока элементов И, второй вход которого подключен к входу считывания, вторые выходы узла памяти подключены к вторым входам блока выявления ошибки, выходы которого подключены к входам первого блока элементов ИЛИ, выход которого подключен к второму входу элемента И, выходы первого блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала при возникновении ошибки.This goal is achieved in that the device containing the memory node, the coding unit, the error detection unit, the first block of AND elements, the AND element, the first block of OR elements, the input of setting the device to zero, write input, read input, address inputs, information inputs , the synchronization input, information outputs, the signal output when an error occurs, further comprises a second block of OR elements, a second block of elements, a third block of AND elements, and the input is in the zero state, the write input, the read input I, the address inputs, are connected respectively to the first, second, third and fourth inputs of the memory node, the information inputs are connected to the fifth inputs of the memory node and to the first inputs of the second block of OR elements, the second inputs of which are connected to the outputs of the second block of AND elements, and the outputs are connected to the inputs of the coding block, the outputs of which are connected to the sixth inputs of the memory node and to the first inputs of the error detection block, the synchronization input is connected to the seventh input of the memory node and to the first inputs of the first block of AND elements and to the first input to the And element, the first outputs of the memory node are connected to the second inputs of the first block of And elements and to the first inputs of the second block of And elements, the second input of which is connected to the read input, the second outputs of the memory node are connected to the second inputs of the error detection unit, the outputs of which are connected to the inputs the first block of OR elements, the output of which is connected to the second input of the AND element, the outputs of the first block of AND elements are information outputs of the device, the output of the AND element is the signal output when an error occurs.

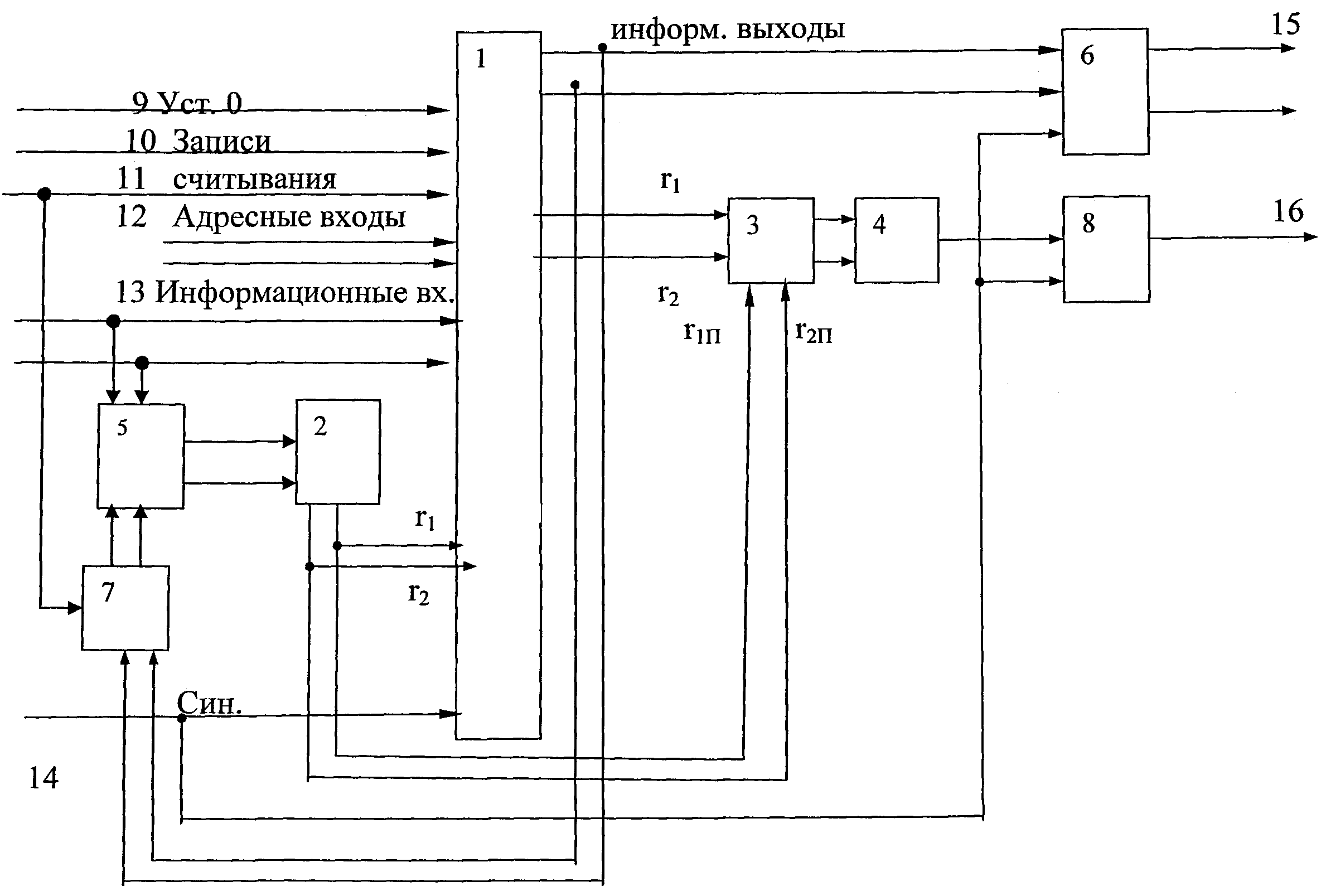

На фиг.1 представлена блок-схема устройства хранения информации.. Устройство хранения информации содержит: узел 1 памяти, блок 2 кодирования, блок 3 выявления ошибки, первый блок 4 элементов ИЛИ, второй блок 5 элементов ИЛИ, первый блок 6 элементов И, второй блок 7 элементов И, элемент 8 И, вход 9 установки в нулевое состояние, вход 10 записи, вход 11 считывания, адресные входы 12, информационные входы 13, вход 14 синхронизации, информационные выходы 15, выход 16 сигнала при возникновении ошибки.Figure 1 shows a block diagram of an information storage device .. The information storage device contains: a memory unit 1, an encoding unit 2, an error detection unit 3, a first block of 4 OR elements, a second block of 5 OR elements, a first block of 6 AND elements, a second block 7 elements AND, element 8 AND, input 9 to zero, input 10 records, input 11 reads, address inputs 12, information inputs 13, synchronization input 14, information outputs 15, signal output 16 when an error occurs.

Вход 9 установки в нулевое состояние, вход 10 записи, вход 11 считывания, адресные входы 12, подключены соответственно к первому, второму, третьему и четвертому входам узла 1 памяти, информационные входы 13 подключены к пятым входам узла 1 памяти и к первым входам второго блока 5 элементов ИЛИ, вторые входы которого подключены к выходам второго блока 7 элементов И, а выходы подключены к входам блока 2 кодирования, выходы которого подключены к шестым входам узла 1 памяти и к первым входам блока 3 выявления ошибки, вход 14 синхронизации подключен к седьмому входу узла 1 памяти и к первым входам первого блока 6 элементов И и к первому входу элемента 8 И, первые выходы узла 1 памяти подключены к вторым входам первого блока 6 элементов И и к первым входам второго блока 7 элементов И, второй вход которого подключен к входу 11 считывания, вторые выходы узла 1 памяти подключены к вторым входам блока 3 выявления ошибки, выходы которого подключены к входам первого блока 4 элементов ИЛИ, выход которого подключен к второму входу элемента 8 И, выходы первого блока 6 элементов И являются информационными выходами 15 устройства, выход 16 элемента 8 И является выходом сигнала при возникновении ошибки.The input 9 is set to zero, input 10 records, input 11 reads, address inputs 12 are connected respectively to the first, second, third and fourth inputs of the memory node 1, information inputs 13 are connected to the fifth inputs of the memory node 1 and to the first inputs of the second block 5 OR elements, the second inputs of which are connected to the outputs of the second block of 7 AND elements, and the outputs are connected to the inputs of the coding unit 2, the outputs of which are connected to the sixth inputs of the memory unit 1 and to the first inputs of the error detection unit 3, the synchronization input 14 is connected to the seventh the first input of the memory node 1 and to the first inputs of the first block of 6 And elements, and to the first input of the 8 And element, the first outputs of the memory node 1 are connected to the second inputs of the first block of 6 And elements and to the first inputs of the second block of 7 And elements, the second input of which is connected to the read input 11, the second outputs of the memory node 1 are connected to the second inputs of the error detection unit 3, the outputs of which are connected to the inputs of the first block of 4 elements OR, the output of which is connected to the second input of the element 8 AND, the outputs of the first block of 6 elements AND are information outputs and device 15 output 16 and the element 8 is the output signal when an error occurs.

Узел 1 памяти, в данном случае, представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых наборов: УК=x1x2x3,y1y2y3r1r2 полученных при кодировании исходных двоичных наборов: У=x1, x2, x3, y1, y2, y3.The memory node 1, in this case, is a static semiconductor operational memory device and is designed to store code sets: K = x 1 x 2 x 3 , y 1 y 2 y 3 r 1 r 2 obtained when encoding the original binary sets: = x 1 , x 2 , x 3 , y 1 , y 2 , y 3 .

Блок 2 кодирования предназначен для формирования значений контрольных разрядов r1, r2 путем сложения по mod2 информационных символов в соответствии с правилом:Block 2 encoding is intended for the formation of the values of the control bits r 1 , r 2 by adding mod2 information symbols in accordance with the rule:

r1=x1⊕x2⊕y1⊕y2;r 1 = x 1 ⊕x 2 ⊕y 1 ⊕y 2 ;

r2=x2⊕x3⊕y2⊕y3.r 2 = x 2 ⊕x 3 ⊕y 2 ⊕y 3 .

и, формирования значений проверочных контрольных разрядов r1П, гзп путем сложения по mod2 информационных символов (хiC, yiC), полученных при считывании информации с узла 1 памяти в соответствии с правилом:and, the formation of the values of the test check bits r 1P , gzp by adding mod2 information symbols (x iC , y iC ) obtained by reading information from the memory node 1 in accordance with the rule:

r1П=x1C⊕x2C⊕y1C⊕r2С; 1H r = x 1C ⊕x 2C ⊕y 1C ⊕r 2C;

r2П=x2С⊕x3C⊕y2С⊕y3C.r 2P = x 2C ⊕x 3C ⊕y 2C ⊕y 3C .

Блок 3 выявления ошибки предназначен для обнаружения ошибки в кодовом наборе при считывании информации с узла 1 памяти путем сложения по mod2 значений контрольных разрядов r1C и r2C, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1П и r2П, сформированных на выходах выходного блока 3 кодирования:Block 3 error detection is designed to detect errors in the code set when reading information from the memory node 1 by adding mod2 values of the control bits r 1C and r 2C , read from the second outputs of the memory node 1, respectively, with the values of the control bits r 1P and r 2P , formed at the outputs of the output coding unit 3:

λ1=r1C⊕r1П;λ 1 = r 1C ⊕r 1P ;

λ2=r2C⊕r2П.λ 2 = r 2C ⊕r 2P .

Нулевой результат суммы свидетельствует об отсутствии ошибки, и ее наличии в противном случае.A zero result of the sum indicates the absence of an error, and its presence otherwise.

Выходы λ1 и λ2 блока 3 сравнение объеденены в один выход первым блоком 4 элементов ИЛИ, значение сигнала на данном выходе поступает на второй вход элемента 8 И.The outputs λ 1 and λ 2 of block 3 are combined into one output by the first block of 4 elements OR, the signal value at this output goes to the second input of element 8 I.

Считывание выходной информации с выходов 15 устройства проводится при поступлении сигнала с входа 14 синхронизации на первые входы первого блока 6 элементов И и элемента 8 И.Reading the output information from the outputs 15 of the device is carried out upon receipt of a signal from the input 14 of the synchronization to the first inputs of the first block of 6 elements And element 8 I.

Устройство работает следующим образом. Перед началом работы устройства на вход 9 "установки в нулевое состояние" подается единичный сигнал, который переводит устройство в нулевое состояние.The device operates as follows. Before starting the operation of the device, a single signal is applied to the input 9 of the "zero state", which puts the device into zero state.

При записи информации в узел 1 памяти, подается единичный сигнал на вход 10 записи, адресные входы 12 и информационные входы 13.When recording information in the memory node 1, a single signal is supplied to the recording input 10, address inputs 12 and information inputs 13.

Например, на информационные входы поступает кодовая комбинация: x1x2x3y1y2y3 соответствующая значению - 000110For example, the information combination receives the code combination: x 1 x 2 x 3 y 1 y 2 y 3 corresponding to the value - 000110

В этом случае входной блок 2 кодирования формирует вектор:In this case, the input coding unit 2 generates a vector:

r1=x1⊕x2⊕y1⊕y2=0; r2=x2⊕x3⊕y2⊕y3=1.r 1 = x 1 ⊕x 2 ⊕y 1 ⊕y 2 = 0; r 2 = x 2 ⊕x 3 ⊕y 2 ⊕y 3 = 1.

Соответственно в узел 1 памяти запишется информация:Accordingly, information is written to the memory node 1:

00011001.00011001.

При считывании информации на вход 11 считывания и адресные входы 12 подаются сигналы, разрешающие считывание информации с узла 1 памяти по указанному адресу. Считываемая информация подается на вторые входы первого блока 6 элементов И и входы второго блока 7 элементов И, с выходов которого информация поступает через второй блок 5 элементов ИЛИ на блок 2 кодирования. Блок 2 кодирования относительно информационных разрядов формирует значения: r1П=0 и R2П=1 которые при отсутствии ошибки равны соответственно значениям r1C и r2C, поэтому, на выходе блока 3 сравнения имеем значения: λ1=0, λ2=0.When reading information at the input 11 of the reading and address inputs 12, signals are given that allow the reading of information from the node 1 memory at the specified address. The information to be read is fed to the second inputs of the first block of 6 AND elements and the inputs of the second block of 7 AND elements, from the outputs of which information is supplied through the second block of 5 OR elements to coding block 2. Coding block 2 with respect to information bits generates values: r 1P = 0 and R 2P = 1 which, in the absence of error, are equal to r 1C and r 2C , respectively, therefore, at the output of comparison block 3 we have the values: λ 1 = 0, λ 2 = 0 .

Допустим, произошла ошибка в первом информационном разряде: 1* 00 110 01. В этом случае на выходах блока 2 кодирования получим значения сигналов: r1П=1 и r2П=1. Так как значение r1П≠r1C(1≠0), то на выходе блока 3 сравнения получим значения сигналов: λ1=1, λ2=0, соответственно на выходе первого блока 4 ИЛИ появится единичное значение сигнала, которое при поступлении сигнала с входа 14 синхронизации, поступит на выход элемента 8 И, что свидетельствует о возникновении ошибки. Аналогичным образом устройство работает при появлении других ошибок.Suppose an error occurred in the first information category: 1 * 00 110 01. In this case, at the outputs of coding unit 2, we obtain the signal values: r 1P = 1 and r 2P = 1. Since the value of r 1P ≠ r 1C (1 ≠ 0), then at the output of block 3 of comparison we get the values of the signals: λ 1 = 1, λ 2 = 0, respectively, at the output of the first block 4 OR, a single value of the signal will appear, which when a signal is received from synchronization input 14, it will go to the output of element 8 AND, which indicates an error. Similarly, the device works when other errors occur.

По сравнению с прототипом в устройстве используется один блок кодирования вместо двух. Так как, блок кодирования строится на сумматорах по mod2, которые содержат по четыре простейших двухвходовых элемента, то его аппаратурные составят (k-k/3-1)2*4 т.е., для шести информационных разрядов аппаратурные затраты на блок кодирования составят 24 двухвходовых логических элементов. Общие аппаратурные затраты на дополнительно введенные второй блок 7 элементов И, второй блок 5 элементов ИЛИ составят 12 двухвходовых логических элементов.Compared with the prototype, the device uses one coding block instead of two. Since the coding block is built on mod2 combiners, which contain four simple two-input elements each, its hardware will be (kk / 3-1) 2 * 4 i.e., for six information bits the hardware costs of the coding block will be 24 two-input logical elements. The total hardware costs for the additionally introduced the second block of 7 AND elements, the second block of 5 OR elements will be 12 two-input logic elements.

Таким образом, предлагаемое устройство позволяет сократить аппаратурные затраты, по сравнению с прототипом, на 12 двухвходовых логических элемента.Thus, the proposed device allows to reduce hardware costs, compared with the prototype, by 12 two-input logic elements.

ИСТОЧНИКИ ИНФОРМАЦИИINFORMATION SOURCES

1. Б.М.Коган, И.Б.Мкртумян Основы эксплуатации ЭВМ. М. - Энергоатом издат, 1988, 430 с., рис.4.17.1. B. M. Kogan, I.B. Mkrtumyan Fundamentals of computer operation. M. - Energoatom published, 1988, 430 p., Fig. 4.17.

2. Патент на полезную модель №76479 "Устройство памяти с обнаружением двойных ошибок" / Бородай В.Э., Бобков С.Г., Осипенко П.Н., Павлов А.А., Царьков А.Н., от о4.04.2008 г.2. Patent for utility model No. 76479 "Memory device with detection of double errors" / Boroday V.E., Bobkov S.G., Osipenko P.N., Pavlov A.A., Tsarkov A.N., from o4. 2008/04

Приложение к заявке на полезную модель: «Устройство хранения информации»Appendix to the application for a utility model: “Information storage device”

Эффективность автоматизированных систем управления, информационных комплексов, средств вычислительной и измерительной техники, устройств хранения и передачи информации в значительной степени определяется достоверностью информации, которая обрабатывается в данных системах [1].The effectiveness of automated control systems, information systems, computer and measuring equipment, information storage and transmission devices is largely determined by the reliability of the information that is processed in these systems [1].

В свою очередь, достоверность функционирования цифровых устройств существенно зависит от выбранного метода обнаружения ошибок (обнаруживающей способности выбранного метода контроля информации и аппаратурных затрат необходимых для реализации данного метода). В настоящее время для этой цели наиболее широко используется метод контроля на четность, который требует минимальных аппаратурных затрат для обнаружения ошибок двоичного набора. Недостатком данного метода является низкая обнаруживающая способность, так как обнаруживаются только нечетные ошибки. В то же время опыт эксплуатации дискретных устройств показывает, что наиболее вероятным событием является возникновение одиночных и двойных ошибок, (соответственно на одиночные ошибки приходится 80-85%, на двойные ошибки 25-20% и ошибки прочей кратности до 2%) [1], т.е. основным недостатком метода контроля на четность является невозможность обнаружения двойных ошибок.In turn, the reliability of the functioning of digital devices substantially depends on the selected method for detecting errors (the detecting ability of the selected method for monitoring information and hardware costs necessary for implementing this method). Currently, for this purpose, the parity check method is most widely used, which requires minimal hardware costs for detecting binary set errors. The disadvantage of this method is its low detecting ability, since only odd errors are detected. At the same time, the experience of operating discrete devices shows that the most probable event is the occurrence of single and double errors (respectively, single errors account for 80-85%, double errors 25–20% and errors of other multiplicity up to 2%) [1] , i.e. The main disadvantage of the parity check method is the inability to detect double errors.

Гораздо большую обнаруживающую способность имеет метод контроля информации по mod3, однако реализация данного метода требует больших аппаратурных затраты на построение схем сверток и временных затрат, связанных с задержкой прохождения сигнала.The method of controlling information by mod3 has a much greater detecting ability, however, the implementation of this method requires large hardware costs for constructing convolution schemes and time costs associated with the delay in the passage of the signal.

В связи с этим, возникает необходимость в разработке метода контроля информации, обнаруживающего 100% одиночных ошибок и максимального количества двойных ошибок, при минимальных аппаратурных и временных затратах на декодирование.In this regard, there is a need to develop a method of information control that detects 100% of single errors and the maximum number of double errors, with minimal hardware and time costs for decoding.

Обоснование метода кодирования информацииJustification of the method of coding information

Пусть исходный двоичный набор представлен тремя информационными разрядами:Let the initial binary set be represented by three information bits:

Для обнаружения ошибок заданной кратности необходимо обеспечить выполнение условия для кодового расстояния d [1]:To detect errors of a given multiplicity, it is necessary to ensure that the condition for the code distance d [1] is satisfied:

где t - число ошибочных разрядов в кодовом наборе.where t is the number of error bits in the code set.

Для обнаружения двойной ошибки необходимо обеспечить кодовое расстояние d≥3, соответственно для этой цели необходимо использовать два контрольных разряда.To detect a double error, it is necessary to provide a code distance d≥3, respectively, for this purpose, it is necessary to use two control bits.

Так как, достоверность функционирования и скорость обработки контролируемой информации существенно зависит от аппаратурных затрат связанных с формированием значений контрольных разрядов, то возникает необходимость выбора метода кодирования информации обеспечивающего минимальные аппаратурные затраты.Since the reliability of the operation and the processing speed of the controlled information substantially depends on the hardware costs associated with the formation of the values of the control bits, it becomes necessary to choose a method of encoding information that provides minimal hardware costs.

В связи с тем, что контроль на четность, по отношению к известным методам обнаружения ошибок, требует минимальных временных и аппаратурных затрат, то для обнаружения двойных ошибок целесообразно использовать метод кодирования информации, требующий для своей реализации аппаратурных и временных затрат соизмеримых с затратами необходимыми при использовании метода контроля на четность.Due to the fact that the parity check, in relation to the known error detection methods, requires minimal time and hardware costs, it is advisable to use the information coding method to detect double errors, requiring for its implementation hardware and time costs commensurate with the costs necessary when using parity control method.

Проведенные для этой цели исследования показали, что для поставленной задачи целесообразно использовать независимые ортогональные проверки. Так, для трехразрядного двоичного набора Y=x1, x2, x3 формирование значений двух контрольных разрядов можно осуществить двумя проверками: r1=x1⊕x2 и r2=x2⊕x3.Studies conducted for this purpose have shown that for the task at hand it is advisable to use independent orthogonal checks. So, for a three-digit binary set Y = x 1 , x 2 , x 3, the formation of the values of two control bits can be carried out by two checks: r 1 = x 1 ⊕x 2 and r 2 = x 2 ⊕x 3 .

Соответственно кодовый набор представляется в виде:Accordingly, the code set is represented as:

В Табл. 1 представлена обнаруживающая способность полученного кода относительно безошибочного кодового набора: YК=00000.In Tab. 1 shows the detecting ability of the received code with respect to error-free code set: Y K = 00000.

Примечание: Символом "*" обозначен признак обнаруживаемой ошибки в соответствующем контрольном разряде, символом "-" - не обнаруживаемой; жирным шрифтом выделены не обнаруживаемые ошибки; наклонным шрифтом представлены двойные ошибки.Note: The symbol "*" indicates a sign of a detected error in the corresponding control category, the symbol "-" - not detected; Undetectable errors are shown in bold; oblique font represents double errors.

Анализ Табл.1, показывает, что из тридцати одного ошибочного кодового набора не обнаруживается семь ошибочных наборов, при этом обнаруживается 100% одиночных ошибок, а из десяти двукратных ошибок не обнаруживается одна ошибка.The analysis of Table 1 shows that out of thirty-one erroneous code sets, seven error sets are not detected, while 100% of single errors are detected, and out of ten double errors, one error is not detected.

Если учесть, что 80% ошибок приходится на одиночную ошибку, а » 20% на двойную, то предлагаемый метод кодирования позволяет существенно повысить вероятность обнаружения возникающих ошибок.If we take into account that 80% of errors are accounted for by a single error, and »20% by a double error, then the proposed coding method can significantly increase the probability of detecting errors that occur.

Для кодирования трехразрядной информации предлагаемым методом потребуется два сумматора по mod2, т.е. такое же количество сумматоров, как и для контроля на четность.To encode three-bit information by the proposed method, two adders with mod2 are required, i.e. the same number of adders as for parity.

Для декодирования информации (сравнения значений контрольных разрядов переданной и полученной информации) для предлагаемого метода, по отношению к контролю на четность потребуется на один сумматор больше, при этом скорость обработки информации не только не снижается, но и уменьшается, т.к. на пути прохождения сигналов, при кодировании и декодировании информации предлагаемым методом, находится по одному сумматору(при контроле на четность по два).For decoding information (comparing the control digits of the transmitted and received information) for the proposed method, one adder is required one more adder with respect to the parity control, while the information processing speed not only does not decrease, but also decreases, because along the signal path, when encoding and decoding information using the proposed method, there is one adder (two for parity).

При кодировании двоичного набора с произвольным числом информационных разрядов (пусть число информационных разрядов кратно трем) разобьем двоичный набор на блоки информации, по три разряда в каждом блоке:When encoding a binary set with an arbitrary number of information bits (let the number of information bits be a multiple of three), we divide the binary set into blocks of information, three bits in each block:

В результате кодирования рассматриваемого двоичного набора предлагаемым методом получим кодовый набор:As a result of encoding the binary set in question by the proposed method, we obtain the code set:

или or

Пример: Пусть число информационных разрядов равно шести, тогда, для рассматриваемого числа информационных разрядов имеем кодовый набор: Example: Let the number of information bits be six, then, for the considered number of information bits we have a code set:

Втабл.2. представлены ошибочные кодовые наборы для одиночных и двойных ошибок относительно безошибочного кодового набора: 00000000.Table 2. erroneous code sets for single and double errors with respect to error-free code set are presented: 00000000.

Анализ Табл.2, показывает, что одиночные ошибки обнаруживаются 100%, из двадцати шести двойных ошибок не обнаруживаются шесть. На кодирование двоичного набора предлагаемым методом потребуется шесть сумматоров по mod2 (при контроле по методу четности - пять сумматоров по mod2). На декодирование кодового набора для предлагаемого метода потребуется восемь сумматоров по mod2 (при контроле на четность шесть сумматоров по mod2).The analysis of Table 2 shows that single errors are detected 100%, out of twenty-six double errors, six are not detected. The binary method coding by the proposed method will require six mod2 adders (for parity testing, five mod2 adders). Decoding the code set for the proposed method will require eight adders mod2 (for parity six adders mod2).

Общие аппаратурные затраты для предлагаемого метода кодирования составят четырнадцать сумматоров по mod2, а для контроля на четность -одиннадцать сумматоров по mod2.The total hardware cost for the proposed coding method will be fourteen adders in mod2, and for parity, eleven adders in mod2.

В этом случае, для предлагаемого метода, при декодировании информации на пути прохождения сигнала находится четыре сумматора по mod2 (формирование значений двух контрольных разрядов осуществляется параллельно), а для контроля на четность шесть сумматоров по mod2.In this case, for the proposed method, when decoding information on the signal path, there are four adders in mod2 (the formation of the values of two control bits is carried out in parallel), and for adherence to parity there are six adders in mod2.

Таким образом, предлагаемый метод обнаружения ошибок позволяет обнаруживать все одиночные ошибки и максимальное количество двойных ошибок при незначительном увеличении аппаратурных затрат по отношению к методу контроля на четность, без снижения быстродействия обработки информации.Thus, the proposed error detection method allows to detect all single errors and the maximum number of double errors with a slight increase in hardware costs in relation to the parity control method, without reducing the speed of information processing.

Claims (1)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010128076/08U RU102403U1 (en) | 2010-07-08 | 2010-07-08 | INFORMATION STORAGE DEVICE |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| RU2010128076/08U RU102403U1 (en) | 2010-07-08 | 2010-07-08 | INFORMATION STORAGE DEVICE |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| RU102403U1 true RU102403U1 (en) | 2011-02-27 |

Family

ID=46310880

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| RU2010128076/08U RU102403U1 (en) | 2010-07-08 | 2010-07-08 | INFORMATION STORAGE DEVICE |

Country Status (1)

| Country | Link |

|---|---|

| RU (1) | RU102403U1 (en) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2448359C1 (en) * | 2011-04-05 | 2012-04-20 | Межрегиональное общественное учреждение "Институт инженерной физики" | Apparatus for storing and transmitting data with error correction in data byte and error detection in data bytes |

-

2010

- 2010-07-08 RU RU2010128076/08U patent/RU102403U1/en not_active IP Right Cessation

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| RU2448359C1 (en) * | 2011-04-05 | 2012-04-20 | Межрегиональное общественное учреждение "Институт инженерной физики" | Apparatus for storing and transmitting data with error correction in data byte and error detection in data bytes |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6018817A (en) | Error correcting code retrofit method and apparatus for multiple memory configurations | |

| RU2403615C2 (en) | Device for storing and transferring information with double error detection | |

| JP2003507985A (en) | System and method for detecting 2-bit errors and correcting errors due to component failure | |

| JPS6349245B2 (en) | ||

| US5761221A (en) | Memory implemented error detection and correction code using memory modules | |

| RU76479U1 (en) | MEMORY DEVICE WITH DUAL ERROR DETECTION | |

| RU2439667C1 (en) | Processor of higher functioning reliability | |

| RU164633U1 (en) | STORAGE AND TRANSMISSION DEVICE WITH ERROR DETECTION | |

| CN108664362B (en) | Memory mirror image processing method, memory controller and user equipment | |

| RU161373U1 (en) | CONTROLLED STORAGE AND TRANSMISSION DEVICE | |

| RU102403U1 (en) | INFORMATION STORAGE DEVICE | |

| RU2450332C1 (en) | Information storage device with single and double error detection | |

| RU2421786C1 (en) | Device to store information of higher functioning validity | |

| RU2422923C1 (en) | Highly reliable information storage and transmission device | |

| RU51428U1 (en) | FAULT-RESISTANT PROCESSOR OF INCREASED FUNCTIONAL RELIABILITY | |

| US11928027B1 (en) | System and method for error checking and correction with metadata storage in a memory controller | |

| RU160959U1 (en) | MALABLE STORAGE DEVICE | |

| RU99624U1 (en) | STORAGE AND TRANSFER OF INFORMATION | |

| RU109888U1 (en) | ERROR DETECTION INFORMATION STORAGE DEVICE | |

| WO2022151724A1 (en) | Error correction system | |

| RU2211492C2 (en) | Fault-tolerant random-access memory | |

| RU2610264C1 (en) | Fault-tolerant memory unit | |

| RU102407U1 (en) | CPU COMPUTER | |

| RU106771U1 (en) | DEVICE FOR STORAGE AND TRANSFER OF DATA WITH CORRECTION OF ERRORS IN THE BYTE OF INFORMATION AND DETECTION OF ERRORS IN THE BYtes OF INFORMATION | |

| RU76730U1 (en) | MEMORY DEVICE WITH ERROR DETECTION |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| MM1K | Utility model has become invalid (non-payment of fees) |

Effective date: 20150709 |