KR920007430B1 - 저항성 금속층 및 그의 제법 - Google Patents

저항성 금속층 및 그의 제법 Download PDFInfo

- Publication number

- KR920007430B1 KR920007430B1 KR1019890002330A KR890002330A KR920007430B1 KR 920007430 B1 KR920007430 B1 KR 920007430B1 KR 1019890002330 A KR1019890002330 A KR 1019890002330A KR 890002330 A KR890002330 A KR 890002330A KR 920007430 B1 KR920007430 B1 KR 920007430B1

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- resistance

- laminate

- mask

- conductive

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/16—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor

- H05K1/167—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor incorporating printed resistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C17/00—Apparatus or processes specially adapted for manufacturing resistors

- H01C17/06—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C17/00—Apparatus or processes specially adapted for manufacturing resistors

- H01C17/06—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base

- H01C17/075—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base by thin film techniques

- H01C17/14—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base by thin film techniques by chemical deposition

- H01C17/16—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base by thin film techniques by chemical deposition using electric current

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C7/00—Non-adjustable resistors formed as one or more layers or coatings; Non-adjustable resistors made from powdered conducting material or powdered semi-conducting material with or without insulating material

- H01C7/006—Thin film resistors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/382—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal

- H05K3/384—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the metal by plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/032—Materials

- H05K2201/0323—Carbon

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0335—Layered conductors or foils

- H05K2201/0355—Metal foils

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0361—Stripping a part of an upper metal layer to expose a lower metal layer, e.g. by etching or using a laser

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0384—Etch stop layer, i.e. a buried barrier layer for preventing etching of layers under the etch stop layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/07—Treatments involving liquids, e.g. plating, rinsing

- H05K2203/0703—Plating

- H05K2203/0723—Electroplating, e.g. finish plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/022—Processes for manufacturing precursors of printed circuits, i.e. copper-clad substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Electroplating Methods And Accessories (AREA)

- Non-Adjustable Resistors (AREA)

- Apparatuses And Processes For Manufacturing Resistors (AREA)

- Laminated Bodies (AREA)

Abstract

내용 없음.

Description

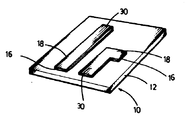

제1도는 절연층, 그 절연층에 접착된 저항층과 그 저항층에 접착된 전도층으로 구성된 적층판(laminate)의 사시도.

제2도는 적층판의 구조를 상세하게 설명하기 위한 제1도의 2-2선을 따라 절단한 단면도.

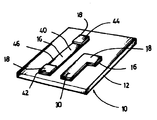

제3도는 첫번째 식각(蝕刻)후의 제1도 적층판의 사시도.

제4도는 저항선과 그 저항선에 전위를 전기적으로 연결하는 수단을 제공하는 구리패드로 구성된 인쇄 회로판의 사시도이다.

* 도면의 주요부분에 대한 부호의 설명

10 : 적층판 12 : 절연판

14 : 다중박충(foil layer) 16 : 저항층

18 : 전도층 30 : 전도선(conductive line)

40 : 저항선(resistive line) 42, 44 : 말단접촉 패드

46 : 기면(절연면)

본 출원은 1988년 2월 26일 출원되어 본 출원 양수인에게 양도된 특허 제160, 794호와 제160,795호의 연속출원이다.

본 출원의 발명은 인쇄회로판용 전구물질과 그 전구물질을 사용, 제조하는 방법에 관한 것이며, 특히 전기도금된 전기저항금속층, 이 저항금속층을 포함하는 다중박층, 그리고 절연층, 전기도금된 저항금속층, 전도층으로 형성된 적층판에 관한 것이다.

1953년 4월 29일 영국 특허 제 690,691호로 발표된 스트롱 일행의 선행기술 이후, 인쇄회로판(PCB) 기술은 현대 전자산업에 있어서 극히 중요한 부분이 되었으며, 전도체 재료로 사용할 박판을 생산하기 위한 클래딩(cladding) 및 관련된 전기도금 공정의 개발로 인해 그 기술이 용이하게 되었다. PCB 구성요소가 차지하는 면적을 최소화하기 위하여, 당 산업분야에서는 평평한 레지스터 테크놀로지에 관심을 기울여왔고, 특히 회로밀도를 증가시키고 신뢰성과 조작특성을 향상시키고, 공장자동화로 전체비용을 감소시키기 위한 노력으로 전기도금된 저항층에 관심을 보였다. 상기의 기술은 "전자 패키징과 생산"의 1986년 1월호 151-154페이지에 실린 "고속 다중층판용 평면 레지스터 기술"이라는 제목의 Mahler의 논문에 요약되어 있다.

식각(蝕刻)이 가능하고 전기도금된 저항물질층에 관한 중요한 발전이 미국특허 3,857,683과 3,808,576으로 발표된 발명자 Castonguay 일행과 PCT/US 86/01173, WO 86/07100으로 발표된 발명자 Rice 일행에 의해 이루어졌다.

저항층으로 유용한 다수의 2원 합금이 미국 특허 3,857,683으로 공표되었다. 그러나 이 합금의 대부분은 실제 상품화하기에는 고유저항이 너무 낮을뿐 아니라, 합금을 생산하기 위한 각각의 전기도금조에 필요한 성분은 구하기 힘들거나 비싸고, 어떤 경우에는 취급하기에 곤란하거나 위험하다. 예를 들면 특허 제 3,857,683호에서의 실시예 11과 실시예 31에서와 같이 안티몬과 코발트 또는 니켈의 플루오르붕산염 및 플루오르붕산이 코발트-안티몬 합금과 니켈-안티몬 합금을 제조하는데 각각 필요하며, 더욱이 선행공지기술은 주어진 2원 합금으로 인쇄회로를 제조하는데 성공적으로 사용되는 특별한 식각제나 식각조건에 대한 설명이 없었다.

미국 특허 제 3,808,576호와 국제 공보 WO 86/07100에서와 같이 한가지 또는 다른 이유때문에 니켈-인 합금이 인쇄회로판에 대한 선구자의 역할로 가장 널리 사용되는 재료가 되었었다.

국제 공보 WO 86/07100에서, 니켈-인 저항층은 황산염과 염화염이 없는 도금조를 사용하여 구리박에 도금되며, 이러한 염은 취성(embrittlement)을 유발하는 까닭에 그 사용을 피해야 한다는 것이 상기 인용 특허에 나타나 있다. 이 도금조는 탄산니켈, 인산, 아인산으로 구성되어 있다. 특허 제 3,808,576호에서는 저항층이 30%(중량비)까지의 인을 포함하고, 전기 도금조가 황산 니켈·6수산화물, 염화 니켈·6수화물, 탄산니켈, 인산, 아인산, 기타 첨가물을 함유한다. 상기의 니켈-인층을 형성하는데 이렇게 많은 시약을 사용하는 것은 기술상 성가실뿐 아니라, 상업적으로 적당한 저항층을 생산하는데 비용의 증가를 가져온다. 더구나 저항합금은 구리박 표면에 전기도금된 후, 산화물로 양극산화하는 것이 필요하다고 일반적으로 생각되고 있으며, 이것 역시 비용의 증가와 불편을 초래한다.

상기의 전기도금된 평면 저항층에 관한 기술의 진보에도 불구하고, 당해 전문가들은 상업적으로 적당하고 가치있는 저항 특성을 가진 저항선과 부위(segment)로 형성된 인쇄회로 구성요소를 제공하기 위해, 안전한 식각제로 바로 식각할 수 있는 저항층을 가져서, 편리하고 재생산이 가능하게 전기도금을 할 수 있는 저항물질을 찾아왔다. 본 발명은 상기 저항층, 그 저항층이 설치된 부품, 그리고 이를 만들기 위한 제법과 도금조에 관한 것으로 구성되어 있다.

본 출원의 발명은 인쇄회로판에 사용할 저항층에 대한 것이며, 상기 저항층은 정상적으로 전도성 있는 금속성분과 탄소, 산소, 황 중에서 최소한 어느 하나로 구성되어 저항을 증가시키는 양만큼의 비금속 첨가물로 된 전기도금층을 포함한다.

본 발명의 바람직한 양상에 있어서, 상기 금속성분은 니켈로 구성되며 비금속 첨가물은 황으로 구성된다. 본 발명의 또다른 바람직한 양상에 있어서는 금속성분이 크롬, 비금속 첨가물이 산소와 탄소로 구성되기도 한다.

본 발명의 중요한 목적은 약 0.1 내지 약 0.4μ의 공칭 두께와 약 15 내지 1000Ohm/Sq의 면적저항(sheet resistance)을 갖는 저항층을 제공하는 것이다.

또한 본 발명은 인쇄회로판에 사용할 다중박층을 제공하는 것이다. 상기 다중박층은 전도층과 이러한 전도층 위에 전기도금될 수 있는 전술한 바와 같은 저항층으로 구성되며, 일반적으로 전도층은 전기도금된 구리박층으로 구성되는 것이 바람직하다.

또한 본 발명은 인쇄회로판 제조에 사용되는 적층판을 제공하며, 상기 적층판을 절연층과 그에 붙어있는 전술한 바와 같은 전기도금된 저항층을 포함하며, 또한 상기 저항에 부착된 전도층을 포함하기도 한다. 이 전도층도 바람직하게는 전기도금된 구리박층으로 구성될 수 있다.

또한 본 발명은 절연층에 접합된 저항선과 절연층으로 구성된 앤쇄회로판을 제공해 준다. 상기 저항선은 정상적으로 전도성이 있는 금속성분과 탄소, 산소, 황중의 적어도 어느 하나로 구성된 저항을 증가시키는 양만큼의 비금속 첨가물의 합성물을 포함하는, 전기도금된 물질로 되어 있다. 또한 이 저항선은 약 15 내지 1000Ohm/Sq의 면적저항을 가지며, 본 발명의 한가지 중요한 양상에 있어서는 상기 저항선이 금속 성분으로 니켈을, 비금속 첨가물로서 황을 포함할 수도 있다. 또 본 발명의 다른 점에 있어서, 상기 저항선은 금속성분으로서 크롬을 포함하고 비금속 첨가물로서 산소와 탄소를 포함할 수 있다. 본 발명의 이러한 형태에 있어서, 인쇄회로판을 전위를 저항선에 전기적으로 접속시키는 수단을 포함할 수 있다. 상기 전기적 접속수단은 저항선에 부착되어 있는 일정 간격이 떨어진 한 쌍의 구리패드로 구성되는 것이 바람직하다. 일반적으로 본 발명의 바람직한 형태에 있어서, 저항선과 구리패드는 각각의 전기도금된 층을 식각함으로써 형성된 것임을 그 특징으로 한다.

또한 여기서 기술한 본 발명은 저항층을 전기도금하는 방법을 제공하기도 한다. 그 방법은 정상적으로 전도성을 갖는 금속성분인 첫번째 공급원과 산소, 탄소, 황중에서 하나 이상을 포함하는 저항을 증가시키는 비금속 첨가물인 두번째 공급원의 수용액을3 함유하는 도금조를 제공하는 단계를 포함한다. 전도성 부재를 도금조에 넣고, 금속성분과 저항을 증가시키는 첨가제의 합성물로 구성된 저항층을, 전도성 부재를 음극으로 사용하여 도금조로 전류를 통과시킴으로써 전도성 부재위로 전기도금시킨다. 상기와 같이 전기도금된 저항층은 정상적으로 전도성이 있는 금속성분으로서 크롬을, 그리고 저항을 증가시키는 비금속 첨가물로서 산소와 탄소를 포함할 수 있다. 또 다른 견지에서, 상기의 전기도금된 저항층은 정상적으로 전도성이 있는 금속성분으로 니켈을, 저항을 증가시키는 비금속 첨가물로서 황을 포함할 수도 있다. 예컨데 저항층이 저항을 증가시키는 비금속 첨가물로서 산소 및/또는 탄소를 포함하는 경우에 그 공급원은 수용성 유기산 또는 그의 이온화염을 포함할 수 있다. 보다 구체적으로 포름산, 아세트산 또는 프로피온산 또는 상기산의 알칼리금속염을 포함한다. 바람직하게는 산소 및/또는 탄소의 공급원이 프로피온산으로 구성되기도 한다. 저항을 증가시키는 비금속 첨가물로 황이 포함되어 있는 저항층을 전기도금하기 위해 상기 방법을 사용할 경우, 그 공급원은 티오항산나트륨을 포함하는 것이 바람직하다.

본 발명의 다른 중요한 점은 정상적으로 전도성이 있는 금속성분인 첫번째 공급원과 산소, 탄소, 황중에서 한개 원소이상을 포함하는 비금속 첨가물인 두번째 공급원과의 수용액을 함유하는 저항층을 전기도금하기 위한 도금조를 제공하는 것이다.

본 발명의 한가지 형태로 있어서, 정상적으로 전도성이 있는 금속성분은 크롬이고 저항을 증가시키는 비금속 첨가물은 산소와 탄소일 수 있다. 본 발명의 또다른 형태에서는 전자로 니켈을 쓰고 후자로 황를 쓸수도 있다. 비금속 첨가물공급원이 산소 및/또는 탄소인 경우에는 상기 공급원이 수용성 유기산 또는 이온화가 가능한 염으로 구성되며, 특히 상기 공급원으로는 포름산 또는 아세트산, 프로피온산 또는 상기산의 알카리금속염 등이 포함된다.

본 발명의 바람직한 실시형태에 있어서, 산소와 탄소의 공급원은 프로피온산으로 구성되며 비금속 첨가물이 황인 경우에는 그 공급원이 티오황산나트륨을 포함하는 것이 바람직하다.

특히 본 발명에서 도금조는 촉매를 포함한다. 본 발명의 바람직한 특색에 있어서 상기 촉매는 과요드산염, 요드산염, 과취소산염, 취소산염, 과염소산염 또는 염소산이온과 같은 옥시-할로 음이온을 포함할 수 있다. 또한 황산이온을 포함할 수도 있다.

상기 발명에서 전도성 있는 금속성분이 크롬인 경우에는 삼삼화크롬이 크롬의 공급원으로서 사용될 수 있으며, 전도성 있는 금속성분이 니켈인 경우에는 황산니켈이 니켈 공급원으로서 사용될 수 있다.

본 발명은 또한 크롬합성물을 함유하는 최소한 하나의 저항선과 절연층위에 전도구역을 갖는 인쇄회로판을 제조하는 방법에 관한 것이다. 본 발명의 이 같은 방법에서는 절연층, 상기 절연층에 접합된 크롬, 탄소, 산소를 함유한 저항층, 그리고 크롬저항층에 접합된 구리 전도박층으로 구성된 적층판이 제공된다. 상기 적층판을 제1마스크로 리고, 제1마스크로 가려지지 않은 크롬저항층 부위로부터 구리전도층을 제거시키기 위해 제2염화구리를 함유하는 제1식각제를 적층판에 접촉시킨다. 이어서, 염산을 함유하는 제2식각제에 적층판을 접촉시켜, 제1마스크로 가려지지 않은 절연층의 모든 부분으로부터 크롬 저항층을 제거한다. 제1마스크를 적층판에서 제거하고, 제2마스크를 씌워준다. 제2마스크로 가려진 적층판은 제2마스크로 가려지지 않은 부위의 적층판으로부터 전도성 구리박층을 제거시키기 위해, 제2염화구리를 함유하는 제3식각제를 가해주며, 최소한 한개의 크롬저항선과 상기 선 부위의 구리전도체 부위를 마련하기 위해 여분의 저항크롬층을 남긴다. 본 발명의 이 같은 형태에서 제2식각제는 18%(중량비)의 염산이며 식각 과정동안 약 50℃의 온도로 유지시킨다.

본 발명의 다른 특색에서는 니켈합성물과 절연층위에 있는 전도구역으로 구성된 최소한 하나의 저항선을 가지는 인쇄회로판을 마련하기 위한 방법이 제공된다. 본 발명의 이러한 특색에서는 한개의 절연층, 그 절연층에 접합된 한 개의 니켈·황 저항층과 상기 니켈·황 저항층에 접합된 한개의 구리전도박층으로 된 적층판이 제공된다. 상기 적층판을 제1마스크로 가린 다음, 제2염화구리를 함유한 제1식각제를 가해주며, 상기 식각제는 제1마스크로 가려지지 않은 모든 절연층부위로부터, 전도성 구리박층과 니켈저항층을 제거시킨다. 이후, 가려진 적층판을 크롬산과 황산으로 구성된 제2식각제와 접촉시켜서, 가려지지 않은 절연층으로부터 나머지 부분을 제거한다. 그후 제1마스크를 제거하고 제2마스크를 도입하며, 제2마스크로 가려진 적층판은 크롬산과 황산으로 구성된 제3식각제와 접촉시켜서, 가려지지 않은 절연층으로부터 나머지 부분을 제거한다. 그후 제1마스크를 제거하고 제2마스크를 도입하며, 제2마스크로 가려진 적층판은 크롬산과 황산으로 구성된 제3식각제와 접촉시켜서, 가려지지 않은 모든 부분의 적층판으로부터 구리전도 적층판을 제거하며, 절연층에 있는 니켈·황 저항선과 니켈저항선 부위에 있는 구리전도체 부위의 경계를 저항하기 위해 여분의 니켈·황 저항층을 남긴다.

상기에서와 같이 본 발명은 하나의 절연층, 전기도금된 하나의 저항금속층과 하나의 전도층을 포함하는, 전기적 저항을 갖는 전기도금된 다중박층에 대한 것이며, 또한 상기 재료로 제조되는 인쇄회로판에 대한 것이기도 하다. 또한 본 발명은 본 발명의 저항금속층이 전기도금될 도금조와 상기 도금조를 사용하는 방법에 관한 것이다. 끝으로 본 발명은, 본 발명의 인쇄회로판을 마련하기 위하여 적층판을 식각하기 위한 방법론에 관한 것이다.

일반적으로 전도층은 인쇄회로판의 기술에 숙련된 사람들에 알려진 구리·니켈등을 포함한 전도물질로 구성된다. 그렇지만 본 발명의 목적에 부합되는 전도층은 산화를 방지하기 위해 처리(안정화)되거나 처리되지 않은 채로의 평평한 전기도금된 구리박인 것이 바람직하다. 저항층과 전도층이 서로 부착되는 방식에 대해서는 본 발명의 내용과는 관계가 없다. 그러나 본 발명의 바람직한 형태에서, 저항층은 전도층의 매트 피(皮)면에 직접 전기도금될 것이다. 따라서, 본 발명의 이같은 바람직한 형태에서는 고전도층이 밀접하게 부착되는 적어도 하나의 전기저항층으로 구성되는 층층이 쌓아 올려진 모양의 새로운 인쇄회로판이 제공된다. 전기저항재료는 정상적으로 전도성이 있는 금속성분과 저항을 증가시키는 양만큼인 비금속 첨가물(탄소, 산소, 황)의 합성물로 전기도금된 층을 포함한다. 정상적으로 전도성이 있으며 전기도금될 수 있는 어떠한 금속도 본 발명의 목적에 맞는 금속성분으로서 사용할 수가 있다. 그러나, 저항층은 크롬, 탄소와 산소의 전기도금된 혼합물이나 니켈과 황의 전기도금된 혼합물로 구성되는 것이 바람직하다.

오늘날 인쇄회로판 부품을 위한 다양한 물질이 알려져 있으며, 상기 인쇄회로판 재료(또는 PCB 선구재료)는 절연기면과, 이 기면의 한면 또는 양면에 있는 고전도 물질의 외판(外板)으로 구성된다. 선구재료를 필요한 제품으로 개조하는 방법으로서 불필요한 전도층 부분은 제거하고 필요한 형상의 전도층 부분만 남겨놓는 방법이 있다. 여기에서 기재된 발명은 고전도층과 관련되어 사용될 전기저항물질(평면저항체)의 제공에 관한 것이다. 물리적으로 고전도층에 부착되어 있는 전기저항물질과 함께, 고전도층은 전도체와 저항체를 포함하는 인쇄회로판의 생산에 사용될 수 있다. 전기저항물질과 물리적으로 부착되어 있는 고전도층으로부터 불필요한 부분을 선택적으로 제거하는 방법은, 저항층에 접합되지 않은 불필요한 전도층의 부분을 제거하는 과거의 방법과 본질적으로 같다.

일반적으로 본 발명의 저항층 물질은 정상적으로 전도성이 있는 금속성분과, 탄소, 산소와 황 중에서 최소한 한개의 원소를 포함하는 저항을 증가시키는 비금속 첨가물과의 전기도금 된 합성물을 구성된다. 또한, 상기 금속성분은 정상적인 전도체이며, 수용액으로부터 전기도금될 수 있는 어떠한 금속이라도 좋다. 그러나 니켈과 크롬이 더 좋으며, 비금속 첨가물은 탄소, 산소와 황중 하나 이상의 원소일 수 있다. 바람직하게는 상기 저항물이 크롬, 탄소와 산소의 전기도금된 합성물(크롬·탄소·산소)이거나 니켈과 황의 전기도금된 합성물(니켈·황)인 것이 바람직하다. 바람직한 저항측은(ㄱ) 600μΩ.cm 이상의 벌크저항을 가지며, (ㄴ) 물리적 보전성의 손실없이 수용액으로부터 절연부재에 부착될 수 있는 고착물을 재생산성을 가지고 낼 수 있도록 전기도금되며, (ㄷ) 비방사는이며, (ㄹ) 450℉ 이상의 온도에서 용융점과 결정학적 상변화를 가지며, (상변화가 일어날 경우에) (ㅁ )적절히 도금되었을 때 약 20℃ 내지 100℃의 온도범위에서 약 300ppm/℃ 이하의 온도저항계수를 가지며, (ㅂ) 현재 사용할 수 있는 저항체의 전형적인 전류 대 전압특성을 가지며, (ㅅ) 부동화(passivation), 양극산화(anodization), 유기층 또는 비유기층으로 과도금 또는 코팅시킴으로써 적절히 보호될때 정상적으로 사용되는 조건을 견디기에 충분한 화학적인 저항을 가지는 것을 특징으로 한다.

본 발명의 저항층은 수용성 전기도금조로부터 안정화된 구리박층과 같은 전도성박에 도금되는 것이다. 또한 공기나 조절된 대기에서 높은 온도로 상기 2중박층을 가열하는 것이, 반드시 필요하지는 않지만 잇점이 있다. 따라서, 이때의 상기 2중 적층판은 한겹 이상의 유리섬유 조직으로 구성된 절연층 위에 저항층으로 적층될 준비가 된 것이며, 상기 유리섬유 조직은 경화성 유지수지를 적절하게 배합하여 미리 함침시킨 것이다. 그 다음에 상기 다중박층과 미리 함침된 유리섬유조직(prepreg)은 250 내지 750psi 압력, 350 내지 450℉ 온도하에서 40분 내지 2시간동안 가압되는 재래의 공정을 이용하여 접합되어 적층판을 형성하며, 상기 적층판은 절연층, 이 절연층에 접합된 전기도금된 전기저항층과 이 저항층에 부착된 외부전도층으로 구성된다.

적층작업에 뒤이어서, 그리고 인쇄회로판의 제조에 사용되는 시점에서, 구리표면은 포토레지스트 물질로 코팅될 수 있다. 포토레지스트층은 저항체와 전도체의 네거티브상(negative image)을 포함하는 포토그래픽 테거티브(photographic negative)에 노출시킬 수 있다. 상기 노출된 레지스트는 현상(developed)하고, 노출되지 않은 부분은 세척해서 제거한다. 이렇게 하여 얻는 상(象)이나 마스크로 덮은 적층판은 노출된 구리가 제거될 때까지 식각제로 식각되는데, 상기 식각제로는 염산으로 산성화된 제2염화철 또는 제2염화구리인 알칼리 식각제 또는 다른 적당한 식각제가 있다. 그후 상기 적층판을 물로 세척한 다음 식각제에 담그는데, 이 식각제로는 노출된 저항성 물질을 제거하는데 적당한 50℃ 이상의 높은 온도의 18%(중량비)의 수용성 염산이 있다. 나머지 노출된 포토레지스트를 벗겨내고, 적층판은 새로운 포토레지스트층으로 코팅시킬 수 있다. 상기 적층판은 전도체 패턴의 네거티브상을 포함하는 포토그래픽 네거티브를 통해 다시 노출시킨다. 노출된 레지스트를 다시 현상하고, 노출되지 않은 부분은 세척한다. 또한 현상된 상을 가지는 적층판은 한번 더 식각하여 노출된 구리를 제거한 후, 세척하여 건조시킨다. 이 시점에서 상기 전도구역과 저항구역의 경계가 정해지며 평면 저항체를 갖는 인쇄회로판을 제공하기 위해 서로 적절히 접촉되어 있다.

일반적으로 상기에서는 본 발명에서 기술하는 적층판으로 인쇄회로판을 만드는 제법에 관한 것을 기술하였으나, 식각해서 제거시킬 특수한 층의 특성에 따라, 기타 다른 과정도 요구된다. 예를 들면, 제1식각제의 사용으로 생긴 잔유물이 형성되기 때문에, 한 단계의 제거를 하는데에도 서로 다른 식각배합제를 사용하는 식각이 요구되기도 한다.

또한 본 발명의 저항층은 정상적으로 전도성이 있는 금속성분과 탄소, 산소, 황들 중 최소한 1개의 원소를 포함하는 저항을 증가시키는 양만큼의 비금속 첨가물과의 합성물로 된 전기도금된 층이다. 본 발명의 신규한 특색중 하나는 첨가물이 맨처음 도금조의 성분인 공급원으로부터 얻어진다는 점이다. 따라서 도금조의 다른 표준성분외에 상기 도금조는 저항층의 성분인 정상적으로 전도성이 있는 금속의 공급원과 산소, 탄소, 황중 최소한 1개의 원소를 포함하는 비금속 첨가물의 공급원을 포함한다. 상기 비금속 첨가물의 공급원은 도금조 수성 매질에 용해될 수 있고 도금조내의 다른 성분에 의해 분해되지 않은 화합물이다. 한편 상기 공급원은 도금조에 전기도금용 전류를 통할때 분해되어야 하며 그 공급원이 분해되며 탄소, 산소 및/또는 황이 방출되어 전착물(electrodeposited mass)에 흡입된다.

본 발명에 따라, 유기산과 그의 염이 탄소와 산소의 공급원으로서 유용하다고 밝혀졌다. 특히, 포름산, 아세트산, 프로피온산 및 그들의 알카리 금속염이 효과적인 것으로 밝혀졌다. 본 발명의 원리와 부합되는 특별히 더 선호할 수 있고 효율적인 산소와 탄소의 공급원은 프로피온산이다. 또 황이 저항을 증가시키는 첨가물로서 사용될 때, 특히 티오황산나트륨이 효과적이고, 더 선호할 수 있는 황의 공급원이라는 것을 알게 되었다.

또한 본 발명에 있어서 더 선호할 수 있는 저항물질중 하나는 표준 전도체 금속 성분인 크롬과 비금속 첨가물인 산소를 함유한 합성물을 포함한다. 상기의 저항물질로부터 저항층을 제조하기 위한 전기도금조는 약 25 내지 450g/ℓ의 크롬산 무수물, 약 0.1 내지 2.35g/ℓ의 황산, 0 내지 약 50g/ℓ의 옥시하로산 음이온과 약 20 내지 300g/ℓ의 유기산(바람직하게는, 지방족산)을 포함한다.

일반적으로 유기산의 양은 필요한 저항성을 얻기에 충분한 양의 탄소 및/또는 산소가 제공되도록 하면 충분하며, 상기 저항성은 첨가물의 양에 따라 변한다. 또한 전기도금된 저항층에 혼합된 첨가물이 감소하면 일반적으로 저항성은 감소된다. 도금된 저항층내 첨가물의 양은 도금조에서 최초로 용해된 공급원의 양에 따라 변한다. 따라서 도금된 저항층의 면적저항은 전기도금조내의 유기산의 양에 따라 변할 것이다(다른 조건이 동일하면). 전기도금작업의 성질로 말미암아 상기 변화는 항시 직접적인 것이 아니며, 도금조에 있는 공급원 산(source acid)의 양과 전기도금된 저항층의 고유저항간의 정확한 관계는 실험을 통해서 결정되어야 한다.

되풀이하건데 도금조의 온도는 도금하는 동안 약 5 내지 50℃로 유지되어야 하며 전류밀도는 약 50ASF(Amp/ft2)에서 직접 얻을 수 있는 최대밀도까지이며, 상기 최대전류밀도는 도금업계에 잘 알려진 기준에 의해서만 제한된다.

본 발명에 따라 제조된 저항층은 인쇄회로판으로서 저장하고 처리하고 이용하는 동안 3차원적으로 안정될수 있게 충분한 두께만 가지면 된다. 그렇지 않으면 상기 두께는 중요한 요소가 아니다. 하지만 일반적으로 본 발명의 저항층은 약 0.1 내지 0.4μ의 두께를 가진다. 일반도금업게의 전문가들이라면 잘 알고있듯이, 전기도금된 층(전착층) 및 그와 유사한 층은 두께에 대한 특정치가 실제로 평균두께가 될 정도의 거칠은 표면을 갖는다.

옥시할로산 음이온은 크롬의 도금을 촉진하기 위해 도금조에서 주로 촉매로 사용된다. 옥시할로이온이 황산과 같이 사용될 때 상승효과가 나타난다. 염소산, 취소산 그리고 요드산 이온들이 효과가 있고, 요드산 이온은 취소산보다, 취소산은 염소산보다 더 효과가 있다.

과요드산과 취소산과 과염소산 같은 과산화 이온도 역시 본 발명에 효과가 좋다. 옥시할로산 음이온은 염소산의 나트룸이나 칼륨염(NaClO3, KClO3)을 공급원으로 하여 얻어지는 것이 바람직한데, 이는 비교적 가격이 싸고 취급하는데 쉽기때문이다. 기능상 옥시할로산 음이온은 강력한 산화제이고 비슷한 촉매효과가 있는 산화제는 과망간이온이다. 그러나 상기 후자의 음이온은 전기도금이 되어 전착층의 성질을 변화시키는 망간의 공급원이 되기 쉽다는 점에서 완전히 만족스럽지는 못하다.

상기에서와 같이 전기도금조내의 유기산은 저항층 제조를 위한 탄소와 산소의 공급원을 제공한다. 전류의 작용으로 산의 분해에서 생긴 산소와 탄소원자가 전착물층 격자가 되어, 전도성을 감소시키거나 반대로 저항성을 증가시키게 된다. 재료의 결정격자에 있어서 불순물과 결점이, 순수한 재료와 비교하여, 상대적으로 전도성을 감소시키는 효과를 가져온다. 본 발명에 따르면 저항층은 금속성분이 갖는 전도성보다 본질적으로 더 작은 전도성(또는 더 큰 면적저항성)을 갖는다. 합성물중의 첨가물중의 정확한 본질과 형상은 완전히 알수 없으며 합성물에서 첨가물은 원소의 형태로 또는 화합물로 존재할 수 있을 것이다. 이점에서 본 발명의 저항합성물은 두가지 요소, 즉 금속성분과 비금속 첨가물을 포함하며, 전기도금된 합성물은 고용체, 순(純)원소, 중간원소화합물 및/또는 혼합물의 형태일 수 있다.

본 발명의 간단한 목적은 약 15 내지 1000Ohm/Sq(바람직하게는 약 250Ohm/Sq)의 면적저항을 얻기 위해, 약 600μΩ.cm 이상의 벌크 저항을 가지며, 약 0.1 내지 약 0.4μ의 두께를 가진 층에 전착되는 소재를 제공하는 것이다. 간단히 서술하면, 본 발명에 따라 제조된 소재는 금속성분과 비금속성분의 합성물일 수 있으며, 상기 소재는 반드시 합금이나 분산액일 필요는 없다. 그러나 후자의 상 또는 상태가 얻어질 수 있다. 상기 저항층의 차원적 물리적인 특성 때문에, 정확한 화학적 성분이나 그 성분비를 결정하는 것은 어렵다. 따라서 바람직한 저항 특성치는 전기도금조내의 성분을 변화시키고 전착층의 저항을 측정하는 실험적인 방법으로 얻어진다.

무스크롬산(CrO3)은 정상적인 전도성을 갖는 금속성분인 크롬의 공급원이다. 황산은 크롬의 도금용으로 알려진 촉매인, 황산음이온의 공급원을 제공한다. 따라서, 탄소와 산소의 공급원의 제공을 1차적인 목적으로하는 유기산이 도금과정을 촉진시키기 위한 황산과 조합해서 작용할 수 있다는 사실을 주목해야 한다.

용액온도, 전류밀도, 도금시간, 교반등을 포함한 도금공정 파라미터의 적절한 제어가 높은 도금효울을 얻기 위해서 필요하며, 약 23℃ 이하와 약 34℃ 이상의 온도에서는 효율에 있어서 역효과가 나타난다. 도금조의 최저온도는 약 25℃ 내지 35℃의 범위이며, 전류밀도는 전극에서 생기는 총 반응률의 척도이다. 너무 높거나 낮은 전류밀도의 사용은 바람직하지 않으며 고전류는 공정제어를 더 어렵게 만드는 열을 발생하게 한다. 또한, 저전류를 사용하면 수소방출때문에 도금효과가 떨어진다. 최적 전류 밀도의 범위는 약 75 내지 300ASF이며 도금조마다 다르다. 도금시간은 전착물의 두께와 직접적으로 관계가 있다. 긴 도금시간은 일반적으로 더 두꺼운 전착층을 생성하며 그로인해 더 낮은 면적저항을 제공하며, 짧은 도금시간은 더 높은 면적저항을 제공한다. 도금처리과정동안 도금조를 교반하는 것은 질량이동을 높이어 사용전류의 한도를 높이고 도금효율을 향상시키는 것이다.

본 발명에 따르면 도금된 저항층은 될 수 있는데로 균일한 것을 요구하고 있다. 정지 전극을 비이커전지(beaker cells)에서 도금의 효율성과 균일성은 전극의 형상에 좌우된다. 수평형전지가 보통 쓰는 수직형전지보다 균일성에서 더 양호하다. 전극의 간격에 있어서 큰 간격은 더 큰 IR 손실을 가져오나 전류분배를 좋게하여 균일한 전착층을 형성하게 한다. 본 발명에 의해 사용되는 5인치×5인치 수평형 전지에서 2인치 간격을 가진 전극을 실험한 결과 좋은 결과를 얻었다. 유동조건은 사용전류가 질량이동(mass transfer) 극한 전류의 약 40% 보다 더 커서는 안된다. 전기도금된 저항층의 균일성은 전착물을 이루는 기면의 거칠은 정도(즉, 조도)와 관련된다. 양호한 균일성을 얻기 위해서, 조도가 작은 기면(substrates)이 더욱 요구된다. 그러나 조도가 작은 기면을 사용하면 박리강(peel strength)가 충분하지 못한 2중저층판이 된다. 그러므로 기면을 선택하는데 균일성과 박리강도와의 조화가 필요하다.

도금조의 모든 구성성분은 조화를 이루는 상태에서 작용하여야 한다. 크롬저항재료는 유기산, 크롬무수물과 황산염이온 만을 함유하는 도금조로부터 생산될 수 있으며, 또한 옥시할로음이온, 크롬무수물과 황산을 함유하는 도금조, 또는 옥시할로음이온, 크롬무수물과 유기산을 함유하는 도금조로부터 생산되기도 한다. 그러나 옥시할로이온의 사용으로 도금조는 더 많은 황산염을 필요로한다. 예를 들면, 옥시할로이온이 없고, 황산염이온이 0.5g/ℓ을 초과할 때 결과는 나쁘게 나타난다. 그러나, 옥시할로음이온이 있고 황산염이온이 2.0g/ℓ를 초과할 때는 도금처리과정에서 매우 좋은 효과를 타나낸다. 물론 높은 수준의 옥시할로음이온을 함유하는 도금조를 사용하면, 할로겐의 산화물이 폭발적으로 형성되는 것을 알 수 있게 된다. 이러한 이유때문에 옥시할로이온의 수준은 7 내지 8g/ℓ을 초과하지 않아야 한다.

본 발명의 개념과 원리에 따라 크롬·산소·탄소 저항층의 면적저항은 도금조내의 크롬산 무수물과 황산의 농도에 따라 변한다. 면적저항은 또한 도금하는 동안 용액온도와 전류밀도에 변하기도 한다. 상기 결과들은, 크롬산무수물, 황산과 초산을 함유하는 시스템에서 실시된 실험결과를 나타내는 표 1 내지 표5에서 예시하고 있다. 크롬산, 초산과 황산의 농도를 각각 변화시켰을 때의 결과가 표 1,2,3에서 각각 보이고 있다.

상기 3가지 용액성분중 도금된 층의 면적저항은 황산농도에 가장 민감하다. 표 3에서와 같이 황산의 양을 증가시킴으로써 처음에는 면적저항이 감소되고, 최소저항 구역을 지난후에는 증가하게 된다. 또한 표 3에서는 크롬 저항층의 크롬함량에 수반되는 변화를 나타내고 있다. 이는, 면적저항의 감소가 크롬함량 증가에 수반된 것임을 나타낸다. 크롬함량은 가장 낮은 저항을 갖는 층에서 제일 높아서, 도금효율이 더 큰 시점을 지시해준다. 또한 표 3에서 가장 높은 도금효율은 황산 농도가 약 200 내지 약 250ppm의 범위인 지점에서 생긴것을 알 수 있다. 전기 도금된 저항층의 면적저항은 다른 성분의 농도의 변화에는 민감하지 않다. 그러나 상기 성분의 농도를 변화시킴으로써 일어나는 결과는 면적 저항이 최저수준조건으로 되면 황산의 결과와 비슷하며, 이것은 크롬산이 약 275g/ℓ일때, 아세트산이 약 140-170g/ℓ일때, 일어난다.

[표 1]

*C.D. : 전류밀도(current density)

**ASF : 암페어/피이트2(Ampere Per square foot)

[표 2]

[표 3]

표 4는 용액의 온도가 약 28-33℃전도가 적당하다는 것을 보여준다. 면적저항은 상기 온도범위나 아래에서 더 높아지는 경향이 있다. 이 표는 28-48℃의 온도에서는 단지 도금시간을 조절하여 줌으로써 원하는 면적저항을 얻게할 수 있다는 것을 알려준다.

[표 4]

표5는 도금된 면적저항이 전류밀도 600 ASF일때 모다 300 ASF일때 훨씬 낮다는 것을 보여준다.

[표 5]

크롬의 도금은 염소산 나트륨을, 300g/ℓ의 크롬산, 200g/ℓ의 아세트산과 100ppm의 황산이 들어 있는 저항 크롬 전기도금조에 첨가함으로 촉진된다. 염소산 나트륨을 도금조에 첨가하면 표 6에서처럼 면적저항이 더 낮아지게 되는 것이다.

표 6의 데이타는, 전류밀도 300 ASF, 도금조 온도 30℃, 도금시간 45초로하여 얻어진 것이다. 염소산의 존재는 단지 크롬의 부착속도를 증가시키는 것으로 생각된다. 염소산 및 다른 산화 할로겐화물이 도금조에서 사용되면, 도금작용이 더 효율적이며, 덜 쉽게 조절된다.

[표 6]

상술한 표들의 데이타를 얻기 위한 실험에서, 유기산으로서 아세트산을 사용한다. 그러나 크롬 저항층의 탄소와 산소의 공급원으로서 현재까지의 가장 좋은 물질로는 프로피온산 이라고 생각된다. 따라서, 도금조는 300g/ℓ의 CrO3, 15ml/ℓ의 프로피온산, 3g/ℓ의 염소산 나트륨을 포함한다. 도금조의 온도는 22℃ 전류밀도는 75 SAF, 도금시간은 45초로 했다. 이렇게하여 생성된 저항층은 면적저항이 25Ohm/Sq.였다.

현재까지 일관성있는 결과를 내는 3가지 방법의 전기도금조가 결정되었다. 도금조의 화학성분과 작용조건은 다음의 표 7에 나타나 있다. 도금작용은 수평의 비이커 전지(breaker cell)에서 행해졌으며, 면적저항은 250hm/Sq. 였다.

[표 7.]

*두께가 약 35μ, 평균 조도(roughness)가 약 1μ이하이며, 안정화 이외에는 아무런 조작을 하지 않는 낮은 프로필(LP)의 구리박.

상기 표에서 방법(다)는 단지 전류밀도가 낮을 수도 있기 때문에 선호된다. 각 도금 작용의 결과로 약 0.25-0.35μ의 두께인 전기도금된 저항 크롬판과, 약 35μ의 두께를 갖는 전도 구리판으로 구성된 다중 박층을 얻는다. 본 발명에 있어서, 반응중에 음극으로는 구리 기면이 사용되며, 저항 크롬층은 평평하고 안정화된 구리박의 매트피(皮)쪽에 직접 전기도금된다.

표7의 방법(다)의 조건에서 생성된 다중 박층은, 구리 전도층이 밖으로 노출되도록, 부분적으로 경화된 에폭시 액체수지로 초기에 도포된 다수의 직조 유리판으로 구성된 수지 침투 가공재에 결합시킨다. 상기 수지 침투 가공재는 해당 전문인에게는 잘 알려진 것이며, 상업적으로 구입이 가능하다. 결합작용은 단지 열과 압력을 그 구조물에 가해줌으로 일어나며, 결국 생성되는 것은 제1도와 2도에서 나타낸 적층판(10)이고, 도면에 타나난 층들의 두께는 실제 크기에 비례되어야만 하는 것은 아니다. 본 발명에 의한 저항층은 인쇄회로판 산업 관계자에게 알려진 전도층과도 함께 사용될 수 있다.

예를 들어, 저항층은 처리되었거나 처리되지 않은 구리박 위에 전기도금될 수도 있다. 따라서 저항층은 전기도금된 전도박의 매트 피 쪽에 일반적으로 있게 해야하며, 실제적으로 구리박은 산화를 방지하도록 처리(안정화)된 것이어야 한다. 그러나 어떤 경우엔 저항층을 처리되지 않은 구리박 또는 완전히 본드 처리된 저항층에 적용하는 것이 덜 바람직한때도 있다. 본 발명과 관련되어 사용될 수 있는 다른 전도층에는 압연구리(rolled copper)와 전기도금된 니켈박등이 있다. 또한 절연판은 전술한 것처럼 수지 침투 가공재일 필요는 없다.

저항층을 포함하는 다중 박층(14)은 접찹제가 도포되어 있는 폴리에스테르 필름에 결함될수 있다는 것을 알게 되었다. 적층판 온도를 300℉로, 압력은 40-300psi로, 가압시간을 10-90초로 하면, 폴리에스테르 필름 절열판을 사용하여, 박리 강도(peel stregth)가 9.5파운드/inch보다 큰 적층판을 얻게 된다.

본 발명에 의한 저항층은 온도와 에이징(aging)에 대해 뛰어난 안정성을 가지고 있는 것이 특징이다. 크롬 저항층은 일반적으로, 20-100℃범위에서 저항 온도계수가 300ppm/℃이하인 것이 특징이다. 즉, 약 25Ohm/Sq.의 면적저항의 경우, 상기 온도 범위에서 1℃ 상승할때마다 약 0.0075Ohm/Sq.가 증가된다. 에이징 안정성의 경우, 순환하는 공기에서 26주, 상대습도 70%의 40℃ 대기압에서 18시간 저장하거나, 또는 125℃공기에 4시간 노출시키면, 모두 크롬 합성물 면적저항이 1.5%보다 적은 알짜 변화를 초래한다. 제1도와 2도의 크롬 저항층(16)을 가지고 있는 적층판(10)과 같은 다중 박층 적층판은 인쇄회로판을 제조하는데 사용될 수 있다.

종래의 방법을 사용하여 전도선을 결정해 주는 포토레지스트를 적층판(10)의 구리 전도층(18) 윗 표면에 부착할 수 있다. 상기 포토레지스트는 종래의 방법으로 원하는 패턴의 자외선에 노출되고, 레지스트 필름의 노출되지 않은 부위를 제거함으로써 현상된다. 남은 것은 패턴이 있는 포토레지스트, 즉 전도선 마스크인데, 구리 전도층(18)의 일부는 노출되고 다른 일부는 마스크에의해 도포된 상태에 있게 된다.

차폐된 적층판(10)은 전도선 마스크에 의해 덮혀지지 않은 부위의 구리박을 식각하는 CuCl2/HCl 부식액에 다중 박층(14)이 노출되도록 처리한다. 예를 들어 식각조(槽)는 200g/l의 CuCl2와 12ml/l의 농염산을 포함할 수도 있다. 식각조는 약 25℃정도로 유지될 수 있다. 포토레지시스트 마스크로 도포되지 않은 부위의 구리전도박층(18)을 제거한다. 밑은 노출된, 산소, 탄소 저항층은 50℃에서 18%(중량비)의 염산을 적층판(10) 저항층의 노출된 부분에 접촉시킴으로 제거될 수 있다. 크롬, 산소, 탄소 저항층(16)의 제거를 확실히 하도록 염산용액에 적층판(10)을 약 10초간 담그는 것이 바람직하다. 전도선을 마스킹하고 있는 포토레지스트를 구리전도박층(18)으로부터 떼어낸다. 제3도에서가장 잘 나타나 있는 전도선(30)의 패턴이 남게된다. 각각의 전도선(30)은 구리전도박층(18)을 표면에 가지게되며 절연면(12)에 붙어있는 저항 크롬층(16)은 전도박층(18)밑에 있게 된다.

하나 또는 그 이상의 평면 저항체의 경계를 정하기 위해서, 저항선을 한정해주는 포토레지스트층을 제3도에 나타나 있는 전도선의 패턴에 부착할 수 있다. 포토레지스트 패턴은 종래의 방법으로 어떤 패턴의 자외선에 포토레지스트를 노출시키고, 노출되지 않은 포토레지스트의 부위를 제거함으로써 윤곽이 생기게 할 수 있다. 저항선 포토레지스트의 부위는 남게되어 전도선(30)이나 절연면(12)에 남아있는 부위를 마스크하게 된다. 저항선 마스크에 의해 도포되지 않은 구리박층(18)의 부위는 적층판(10)을 상기의 CuCl2/HCl 식각액에 담그거나, 단지 구리박층(18)을 접촉시킴으로서 제거된다. 저항선 마스크는 제거되어 제4도에서와 같은 인쇄회로판을 제공하게 되며, 그 회로판은 원래의 크롬, 산소, 탄소저항층(16)의 부위와, 저항선(40)과 근접하게 전기적 접촉을 하고 있는 한쌍의 구리 전도박층 말단 접촉패드(42,44)로 구성된 저항선(40)에, 전압을 전기적으로 커플링하기 위한 부위로 구성된 저항선(40)을 가지고 있다. 더우기, 다양한 저항 및 저항성질을 제공하기 위해, 각각의 여러개의 저항선 평면저항체는 적당한 전도체에 의해 상호 연결되어 있거나 그물망처럼 배열 될 수 있다는 것도 고려되어야 한다. 제4도의 인쇄회로판은 종래의 방식으로 전기를 전도하는 전도선(30)을 한개 이상 가질 수 도 있다.

본 발명에 의하면, 단지 전기도금 조건과 도금조의 화학성분을 변화시킴으로 전기도금되는 탄소 및/또는 산소이 양을 변화시켜, 크롬 저항층 또는 선의 면적저항을 고의적으로 변경할 수도 있다. 상기한 것처럼, 탄소와 산소의 공급원의 유기산, 더 구체적으로는 지방족산일 수 있다. 크롬과, 저항을 증가시키는 양의 산소, 탄소와 같은 비금속 첨가제의 합성물의 전기 도금된 층을 사용함으로 몇가지 잇점이 있다. 크롬, 산소, 산소 정항물질은 CuCl2/HCl 식각액에 의해 식각되지 않으므로 선택적으로 구리를 제거할 때 이용될 수 있다.

따라서, 식각 과정을 조절할 수 있게 되며, 결과 생성품의 질을 증가시키게 되는 것이다. 크롬, 탄소, 산소 저항층은 부식도 잘 되지 않으므로 생산품을 저장하거나 실제 쓰일때에 생산품의 안정성에 큰 기여를 하다. 비록 저항 크롬층은 크롬산 식각액을 사용하여 식각될 수도 있지만, 식각 과정은 반응 시약으로 크롬산을 사용할 필요가 없어, 크롬산과 그로 오염되 물질을 폐기할때 관련되는 환경 문제를 줄일 수도 있다. 또, 본 발명의 크롬 저항물질은 H2O2/H2SO4, FeCl3, 알칼리 암모니아와 CuCl2식각액(구리를 제거할 수 있다)에 의해 식각되지 않으며, 사용되는 특성 전도층과 저항층의 식각 특성에 따라 적당한 식각속도를 내도록 식각제를 선정한다.

본 발명에 의한 본 응용의 다른 면으로는, 정상적으로 전도하는 금속 성분으로서 니켈과, 비금속 첨가제로서 저항을 증가시키는 양의 황으로 구성된 합성물로 된 저항층의 제공이 있다. 니켈·황의 저항층은 100g/ℓ의 NiSO4, 6H2O, 30g/ℓ의 H3BO3, 50g/ℓ의 Na2L2O3.5H2O가 들어 있는 수용액으로 구성된 도금조를 사용하여 생성될 수도 있다. 이런 용액은 보통 정도의 산성이어서 pH는 약 3.2정도이며, pH메타로 측정하여 용액이 약 6정도가 되도록 NaOH를 충분량 첨가함으로 도금전에 pH를 조정할 수도 있다. 전기도금조의 용액은 약 45℃까지 가열하여 그 온도를 유지하는 동안 도금될 전도성 구리박층은 비이커 전기도금 장치의 음극으로서 연결되어 도금조에 담가진다. 전류밀도가 약 10-40 ASF인 전류를 도금조에 통해주어 니켈·황 합성물층이 구리박 위에 깔리게 된다. 또, 100g/ℓ의 NiSO4.6H2O, 30g/ℓ의 H3BO3, 10g/ℓ의 Na2S2O3, 5H2O가 사용될 수도 있다. 용액의 pH 는 NaOH로 약 6이 되도록 조절하여 상기 방법으로 도금이 실시된다. 두 방법 모두, 도금용액을 통과하는 전류의 전류밀도가 약 10-40 ASF로 다양할 수 있고, 도금시간도 전류밀도 40 ASF에서 약 30초 해주는 것부터, 10 ASF의 전류밀도에서 약 120초 해주는 등으로 다양할 수 있다.

니켈·황 층이 구리박 기면에 형성된 후 다중 박층을 도금조에서 꺼낸다. 필요하다면, 다중 박층을 도금조로부터 꺼낸후, 그 다중 박층의 저항층을 안정화시키기 위하여 약 2g/ℓ의 CrO3용액에 담글수도 있다.

상기 도금시간과 전류밀도를 이용하여 상기 도금조에서 전도성 구리박에 형성된 니켈·황 합성물층은 25Ohm/Sq.의 면적저항을 가질 것이다. 이렇게 해서 형성된 니켈 저항층은 매우 안정하며, 장시간의 공기에 대한 노출에도 면적저항이 평균 2%이하 정도로만 달라진다. 구리 전도층에 니켈·황 저항층을 전기도금하여 생긴 다중 박층은 인쇄회로판을 제조하는데 필요한 전층판을 만드는데 사용될 수 있다. 제1도와 2도를 참조해보면, 이 경우엔 저항층(16)이 상기한 크롬·탄소·산소층이라기 보다는 니켈·황 층이다. 적층판(10)의 다른 것은 상기한 것과 같다. 따라서 적층판(10)은 기면(12)에 결합되어 있는 전기도금된 저항 니켈층과, 인쇄회로를 제조하는데 적당한 구리전도박층(18)으로 구성된 다중 박층(14)으로 구성된다. 상업적으로는, 도금조의 음극으로 구리전도박층(18)이 사용되기전에, 산화에 대한 저항성을 증가시키기 위해 구리 전도박을 안정화시키는 것이 바람직하다.

니켈·황 저항층(16)을 포함하는 적층판(10)은 상기한 온도와 압력을 가해줌으로써 얻어질 수 있다. 결과적으로 생긴 적층판은 인쇄회로판을 제조하기 위해 식각 될수 있는 것이다. 상기 했던것처럼 포토레지스트를 붙여 선택된 패턴의 자외선을 쬐어준다. 따라서 구리전도박층(18)의 일부는 가리고 일부는 가리지 않은 패턴이 있는 포토레지스트층이나 전도선 마스크를 얻게 된다. 적층판(10)의 다중 박층(14)을 상기한 것처럼 CuCl2/HCl 식각액에 노출시킨다. 식각조는 127ml/ℓ의 농 HCl과 200g/ℓ의 CuCl2를 포함할 수도 있다. 식각중에서 식각조는 약 52℃로 유지하는 것이 바람직하다. 이러한 식각조는 포토레지스트 마스크에 의해 가려지지 않은 부위의 구리전도층(18)과 니켈·황 저항층(16)을 제거한다.

적층판을 상기한 것처럼 처리하면 기면(12)에 정해 미상의 잔사가 남을 수 있으며, 300g/ℓ의 크롬산과 300ml/ℓ의 농황산으로 된 잔사를 제거 식각제를 사용하여 이 잔사를 제거할 수 있다. 이용액조는 45℃정도로 유지되고, 잔사 제거는 약 15초만에 일어난다. 남은 포토레지스트를 구리박층(18)에서 제거하면, 제3의 패턴이 있는 전도선(30)이 남는다. 각각의 전도선은 전도구리박층(18)의 표면을 가지며, 그 밑에 기면(12)에 붙어있는 니켈 저항층을 가진다.

하나 이상이 평면 저항체의 경계를 정하기 위하여, 저항선을 한정하게 되는 포토 플리며 필름 레지스트층이 다중 박층이 있는 적층판(10) 또는 회로판에 붙어있을 수도 있다. 두번째 포토레지스트 패턴은 포토레지스트를 자외선 패턴에 노출시킴으로 생기고, 적절히 현상된다. 저항선 포토레지스트의 현상되지 않은 부위는 제거되고, 남은 부위는 전도선(30)이나 기면(12)에 남아있을 부위를 덮고 있는 저항선 마스크를 제공한다. 전도선(30)의 다른 부위는 저항선 마스크로 덮혀있지 않는다. 전도선(30)의 구리박층(18)의 노출된 부분은, 300g/ℓ 의 크롬산, 300ml/ℓ의 농황산으로 구성된 바람직한 식각제를 접촉시킴으로 제거될 수 있다. 45℃에서 크롬산/황산 식각제는 니켈·황 저항층(16)을 식각하지 않을 것이다.

저항선 마스크를 제거하면 제4도에서 볼 수 있듯이, 인쇄회로판은 저항선과 근접한 전기적 연결이 있는 한쌍의 전도구리박층 말단 접촉패드(42,44)를 포함하는 니켈·황 저항선(40)에 전압을 전기적으로 커플링하기 위한 부위와 니켈·황 합성물로 구성된 저하층을 갖는다. 인쇄회로판은 한개 이상의 전도선(30)을 가지고 있어 종래의 방법으로 전기를 전도할 수 있게하며, 여러개의 저항선(40)은 적당한 그물망으로 배열되어 있을 수도 있다.

본 발명의 니켈·황 저항물질은 제조하는데 있어서 정상적으로 전도성이 있는 금속 니켈의 공급원으로서 NiSO4, 비금속 저항을 증가시키는 첨가제로서 Na2S2O3.5H2O, pH완충제로서 붕산을 포함하는 용액조가 사용될 수 있다. 상기 물질의 농도는 기대하는 효과에 따라 변화시킬 수 있다. 용액조의 NiSO4의 농도가 진할수록 전기도금된 저항층의 니켈의 농도는 더 진해져서 전도성이 증가하게 되며, 따라서 전기도금된 층의 면적저항이 감소된다. 그러나, NiSO4의 망이 많으면 일반 적으로 끌어냄 현상(drag out)에 의해 전기도금 과정중 화학적 손실이 크게 된다. Na2S2O3.5H2O의 양이 많으면 전기도금된 저항층에 있는 황의 양이 많아지게 되어 일반적으로 전기도금된 층의 면적 저항이 증가된다.

니켈·황 저항층을 만들때, 전류밀도와 도금시간은 다른 결과를 얻기 위해 다양하게 변화시킬 수 있다. 일반적으로 니켈·황 층의 단면적이 면적저항을 결정하기 때문에 층이 다른 두께를 가지면 다른 저항을 갖게 된다. 용액을 통해 일정 전하를 통하게해주면, 특정 두께로 도금되게 된다.

전류밀도는 약 10,40 ASF로 다양할 수 있고, 도금시간도 각 전류밀도에서 약 30-120초로 변화시킬 수 있다. 이 범위내에서 전기도금된 저항층의 두께는 도금시간에 비례하여 증가하므로 면적저항은 도금시간이 증가함에 따라 감소한다. 본 발명에 의하면, 1200쿨릉을 사용하여 전도성 구리박 기면위에 전기도금된 니켈·황 저항층은 약 0.4μ의 두께를 갖게 되며, 약 25Ohm/Sq.의 면적저항을 갖게 된다.

본 발명에 의하면, 전기도금된 물질의 결정 격자의 불순물이나 결함은 보통 순수한 물질의 전도성을 감소시키는 영향이 있다고 여겨진다. 구리기면이나 관련있는 어떤 다른 기면위에 도금된 저항 크롬·니켈층은 상응하는 금속성 크롬 니켈층보다 본래 낮은 전도성(또는 큰 면적 저항)을 갖는다. 크롬, 니켈 저항층의 면적저항이 더 큰것은 탄소, 산소, 황 불순물이 금속성 부착물에 포함되기 때문이라 생각된다.

본래 면적저항이 크면, 국소부위에 원하는 면적저항을 갖도록 층의 유효 단면적을 감소시키기 위해 원하는 부위의 층을 제거 또는 얇게 하기 위한 기계적 또는 화학적 방법을 사용할 필요없이 전도체의 전 표면에 저항이 미칠 수 있다. 단지 전기 도금조의 화학량 및 조건을 변화시킴으로써, 원하는 면적저항을 이룰 수 있다.

본 발명에 의한 저항층은 전도체 전 표면을 덮기 위해 상기의 방식으로 사용된다. 더욱이, 저항층이 유전(誘電)기면에 덮여지고 구리가 원하는 부위에서 제거된후, 저항체층은 완전히 유전 기면을 덮는다. 저항체가 적절한 마스크 디자인과 기술을 이용하여 정확히 결정되었다면, 원하는 저항을 갖게하기 위해 기계적 및 화학적 방법으로 저항력있는 물질을 후처리할 필요가 없게 된다.

예를 들어 저항층(16)의 두께는, 크롬·산소·탄소의 합성물이든 니켈·황의 합성물이든 간에, 상업적으로 필요한 형태를 갖는 평평한 저항체와 그의 면적 저항을 얻도록 조절될 수 있다. 전도층(18)의 두께는 저항체의 저항에 영향을 미치지 않는다. 전형적으로 본 발명에 의해 면적저항 25Ohm/Sq.를 얻기 위해, 저항층(16)은 약 0.1-0.4μ의 두께를 갖는다.

본 발명에 있어서, 원하는 면적저항 범위는 약 15-1000Ohm/Sq.이다. 기능을 갖는 저항체는, 식각된 저항체의 기하학을 조절함으로써, 즉 회로판의 식각된 저항체의 길이와 폭을 다양하게 함으로써 상기 범위의 면적저항을 갖도록 할 수 있다. 이 저항 범위내에서, 면적저항치가 약 25Ohm/Sq.인 것이 생산공정의 단순화를 위해 바람직하다. 따라서, 도금시간을 조절함으로써, 상기한 거의 모든 도금조 조건(도금조의 성분 농도, 온도등)은 25 Ohm/Sq.의 면적저항을 갖는 저항체를 만들어 내는데 사용될 수 있다.

물리적, 지형적 디자인을 적절히 조화시킴으로, 25, 100 및 1000Ohm/Sq.의 면적 저항을 본 발명에 의해 이룰 수 있으며, 편리하게는 상업적으로 바람직한 1Ohm 내지 1메가 Ohm의 범위의 저항을 갖는 평면저항체를 만드는데 사용될 수 있다.

Claims (20)

- 정상시에 전도성을 갖는 금속 성분과 저항을 증가시키는 적당량의 탄소 또는 산소 중에서 적어도 하나로 구성되는 비금속 첨가제로 이루어져 있는 합성물로 전기도금된 인쇄회로판 제조에 사용되는 저항층.

- 제1항에 있어서, 상기 금속 성분이 니켈 또는 크롬으로 구성된 저항층.

- 전도박층과 그 위에 전기도금되어 얻어지는 제1항의 저항층으로 구성되며, 인쇄회로판 제조에 사용되는 다중 박층.

- 제3항에 있어서, 상기 전도박층이 구리로 구성된 다중 박층.

- 절연층과 그에 부착되어 있는 제1항의 저항층으로 구성되며, 인쇄 회로판을 제조하는데 사용되는 적층판.

- 제6항에 있어서, 전도박층이 상기 저항층에 부착되어 있는 적층판.

- 제6항에 있어서, 상기 전도층이 구리로 구성된 적층판.

- 절연층에 저항선이 부착되어 있으며, 정상시에 전도성을 갖는 금속성분과 저항을 증가시키는 양의 탄소 또는 산소중 적어도 하나로 구성되는 비금속 첨가제로 구성된 조성물로 전기도금된 것인 저항선과 절연층을 포함하는 인쇄회로판.

- 가) 정상시에 전도성을 갖는 금속성분을 제공하는 첫번째 공급원가 탄소 또는 산소중에의 하나 이상으로 구성되는 저항을 증가시키는 비금속 첨가제의 두번째 공급원을 포함하는 수용액을 넣는 도금조를 준비하고, 나) 전도성 부재를 상기 도금조에 넣고, 다) 상기 전도성 부재를 음극으로 하여, 도금조에 전류를 흐르게함으로써 상기 전도성 부재에, 금속 성분과 첨가제로 구성되는 층을 전기도금하는 것으로 구성된 저항층의 전기 도금법.

- 제9항에 있어서, 상기 첫번째 공급원이 크롬 또는 니켈의 공급원인 방법.

- 제9항에 있어서, 상기 첫번째 공급원이 수용성 유기산 또는 그의 이온화가 가능한 염인 방법.

- 제9항에 있어서, 촉매를 상기 도금조에 가하는 것을 특징으로 하는 방법.

- 제9항에 있어서, 상기 촉매가 알카리 금속염소산염으로 구성되고 상기 첫번째 공급원이 크롬산으로 구성되며 상기 두번째 공급원이 프로피온산으로 구성된 방법.

- 정상시에 전도성을 갖는 금속성분을 제공하는 첫번째 공급원과 산소 또는 탄소 중 하나 이상을 함유하며 저항을 증가시키는 비금속 첨가제의 두번째 공급원으로된 수용액으로 구성된 저항층을 전기도금시키는 도금조.

- 제14항에 있어서, 상기 첫번째 공급원이 크롬 또는 니켈의 공급원인 도금조.

- 제14항에 있어서, 상기 두번째 공급원이 물에 녹은 유기산 또는 그것의 이온화 가능한 염으로 구성된 도금조.

- 제14항에 있어서, 촉매를 상기 도금조에 가하는 것을 특징으로 하는 도금조.

- 제14항에 있어서, 상기 촉매가 알카리 금속염소산염으로 구성되고 상기 첫번째 공급원이 크롬산으로 구성되면 상기 두번째 공급원이 프로피온산으로 구성된 도금조.

- (가) 절연층. 절연층에 결합되어 있고 탄소 또는 산소중 최소한 하나로 구성된 크롬저항층 및 크롬저항층에 붙어있는 구리전도박층을 갖는 적층판을 준비하고, (나) 첫번째 마스크로 적층판을 마스킹하고, (다) 첫번째 마스크로 마스킹된 염화구리를 함유하는 첫번째 식각액에 접촉시켜서 첫번째 마스크로 도포되지 못한 크롬저항층의 모든 부분으로부터 구리전도박층을 제거하고, (라) 염산을 함유하는 두번째 식각액에 적층판을 접촉시켜서 첫번째 마스크로 도포되지 못한 절연층의 모든 부분으로부터 크롬저항층을 제거하고, (마) 적층판에서 첫번째 마스크를 제거하고, (바) 두번째 마스크로 적층판을 마스킹하고, (사) 두번째 마스크로 마스킹된 적층판을 염화구리를 함유하는 세번째 식각액에 접촉시켜서 절연층위에 크롬저항선 및 크롬저항선의 일부분 위에 있는 구리전도영역이 뚜렷하게 나타나도록 잔류 크롬저항층을 남겨두면서 두번째 마스크에 도포되지 못한 적층판의 모든 부분에서 구리전도박층을 제거하는 것으로 구성된 최소한 하나의 저항선 및 절연층 위의 전도 영역을 갖는 인쇄회로판의 제조방법.

- (가) 절연층, 그 절연층에 결합되어 있고 산소 또는 탄소중 최소한 하나로 구성되는 니켈 저항층에 붙어있는 구리전도박층을 갖는 적청판을 준비하고, (나) 첫번째 마스크로 적층판을 마스킹하고, (다) 첫번째 마스크로 마스킹된 염화구리를 함유하는 첫번째 식각액에 접촉시켜서 첫번째 마스크로 도포되지 못한 절연층의 모든 부분으로부터 구리전도박층과 니켈 저항층을 제거하고, (라) 첫번째 마스크로 마스킹된 적층판을 크롬산과 황산을 함유하는 두번째 식각액에 접촉시켜서 절연층의 마스킹된지 못한 모든 부분에서 잔류물을 제거하고, (마) 첫번째 마스크를 적층판에 제거하고, (바) 두번째 마스크로 그 적층판을 마스킹하고, (사) 두번째 마스크로 마스킹된 적층판을 크롬산과 황산을 함유하는 세번째 식각액에 접촉시켜서 절연층위에 니켈 저항선과 니켈 저항선의 일부분위에 있는 구리전도영역이 뚜렷하게 나타나도록 잔류 니켈저항층을 남겨두면서 적층판의 마스킹되지 못한 모든 부분에서 구리전도박층을 제거하는 것으로 구성된 최소한 하나의 저항선 및 절연층 위의 전도영역을 갖는 인회로판의 제조방법.

Applications Claiming Priority (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US160,795 | 1980-06-19 | ||

| US16079588A | 1988-02-26 | 1988-02-26 | |

| US16079488A | 1988-02-26 | 1988-02-26 | |

| US160794 | 1988-02-26 | ||

| US160795 | 1988-02-26 | ||

| US160,794 | 1988-02-26 | ||

| US307,793 | 1989-02-08 | ||

| US30749389A | 1989-02-09 | 1989-02-09 | |

| US307493 | 1989-02-09 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR890013225A KR890013225A (ko) | 1989-09-22 |

| KR920007430B1 true KR920007430B1 (ko) | 1992-08-31 |

Family

ID=27388511

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019890002330A KR920007430B1 (ko) | 1988-02-26 | 1989-02-27 | 저항성 금속층 및 그의 제법 |

Country Status (9)

| Country | Link |

|---|---|

| EP (2) | EP0330210A3 (ko) |

| JP (1) | JP3022969B2 (ko) |

| KR (1) | KR920007430B1 (ko) |

| CN (1) | CN1051198C (ko) |

| AU (1) | AU622637B2 (ko) |

| BR (1) | BR8900871A (ko) |

| IL (1) | IL89407A0 (ko) |

| IN (1) | IN171824B (ko) |

| MY (1) | MY104939A (ko) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5243320A (en) * | 1988-02-26 | 1993-09-07 | Gould Inc. | Resistive metal layers and method for making same |

| US6281090B1 (en) * | 1996-10-16 | 2001-08-28 | Macdermid, Incorporated | Method for the manufacture of printed circuit boards with plated resistors |

| US6194990B1 (en) * | 1999-03-16 | 2001-02-27 | Motorola, Inc. | Printed circuit board with a multilayer integral thin-film metal resistor and method therefor |

| US6622374B1 (en) * | 2000-09-22 | 2003-09-23 | Gould Electronics Inc. | Resistor component with multiple layers of resistive material |

| EP1261241A1 (en) * | 2001-05-17 | 2002-11-27 | Shipley Co. L.L.C. | Resistor and printed wiring board embedding those resistor |

| JP4761792B2 (ja) * | 2005-03-02 | 2011-08-31 | ローム株式会社 | 低抵抗のチップ抵抗器とその製造方法 |

| CN100397960C (zh) * | 2005-04-08 | 2008-06-25 | 神基科技股份有限公司 | 印刷电路板结构及其制造方法 |

| JP4487875B2 (ja) * | 2005-07-20 | 2010-06-23 | セイコーエプソン株式会社 | 電子基板の製造方法及び電気光学装置の製造方法並びに電子機器の製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2165622C3 (de) * | 1971-12-30 | 1979-01-04 | Siemens Ag, 1000 Berlin Und 8000 Muenchen | Dünnschichtschaltkreis |

| US3886578A (en) * | 1973-02-26 | 1975-05-27 | Multi State Devices Ltd | Low ohmic resistance platinum contacts for vanadium oxide thin film devices |

| JPS5469768A (en) * | 1977-11-14 | 1979-06-05 | Nitto Electric Ind Co | Printing circuit substrate with resistance |

| US4190474A (en) * | 1977-12-22 | 1980-02-26 | Gould Inc. | Method of making a printed circuit board having mutually etchable copper and nickel layers |

| DE3321900C2 (de) * | 1982-06-16 | 1986-01-16 | Nitto Electric Industrial Co., Ltd., Ibaraki, Osaka | Substrat für eine Schaltung mit einer Widerstandsschicht und Verfahren zu dessen Herstellung |

| JPS6016117B2 (ja) * | 1982-06-16 | 1985-04-23 | 日東電工株式会社 | 抵抗体付き回路基板とその製造法 |

| US4808967A (en) * | 1985-05-29 | 1989-02-28 | Ohmega Electronics | Circuit board material |

| US4682143A (en) * | 1985-10-30 | 1987-07-21 | Advanced Micro Devices, Inc. | Thin film chromium-silicon-carbon resistor |

-

1989

- 1989-02-23 EP EP19890103215 patent/EP0330210A3/en not_active Withdrawn

- 1989-02-23 EP EP99124541A patent/EP1011111A1/en not_active Withdrawn

- 1989-02-24 IN IN157/CAL/89A patent/IN171824B/en unknown

- 1989-02-24 AU AU30752/89A patent/AU622637B2/en not_active Ceased

- 1989-02-24 CN CN89102522A patent/CN1051198C/zh not_active Expired - Fee Related

- 1989-02-24 BR BR898900871A patent/BR8900871A/pt unknown

- 1989-02-24 MY MYPI89000225A patent/MY104939A/en unknown

- 1989-02-24 IL IL89407A patent/IL89407A0/xx unknown

- 1989-02-27 KR KR1019890002330A patent/KR920007430B1/ko not_active IP Right Cessation

- 1989-02-27 JP JP1046346A patent/JP3022969B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP0330210A3 (en) | 1990-11-07 |

| CN1040298A (zh) | 1990-03-07 |

| CN1051198C (zh) | 2000-04-05 |

| JP3022969B2 (ja) | 2000-03-21 |

| EP1011111A1 (en) | 2000-06-21 |

| EP0330210A2 (en) | 1989-08-30 |

| MY104939A (en) | 1994-07-30 |

| JPH01309301A (ja) | 1989-12-13 |

| IN171824B (ko) | 1993-01-23 |

| AU622637B2 (en) | 1992-04-16 |

| BR8900871A (pt) | 1989-10-17 |

| KR890013225A (ko) | 1989-09-22 |

| IL89407A0 (en) | 1989-09-10 |

| AU3075289A (en) | 1989-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5243320A (en) | Resistive metal layers and method for making same | |

| US3808576A (en) | Circuit board with resistance layer | |

| US4204187A (en) | Printed circuit substrate with resistance elements | |

| US4808967A (en) | Circuit board material | |

| US4888574A (en) | Circuit board material and method of making | |

| US4392013A (en) | Fine-patterned thick film conductor structure and manufacturing method thereof | |

| WO2001014135A1 (fr) | Feuille de cuivre electrolytique avec feuille de support et stratifie plaque cuivre utilisant cette feuille de cuivre electrolytique | |

| US5689227A (en) | Circuit board material with barrier layer | |

| EP1439952A1 (en) | Copper foil with low profile bond enhancement | |

| JP2014082320A (ja) | 2層フレキシブル基板、並びに2層フレキシブル基板を基材としたプリント配線板 | |

| US6902824B2 (en) | Copper foil and metal foil with carrier foil for printed wiring board, and semi-additive process for producing printed wiring board using the same | |

| KR920007430B1 (ko) | 저항성 금속층 및 그의 제법 | |

| KR101156414B1 (ko) | 프린트 배선 기판의 제조 방법 및 이 제조 방법에 의해 얻어진 프린트 배선 기판 | |

| EP1167580B1 (en) | Electrolytic copper foil | |

| KR900003158B1 (ko) | 기판상의 전기회로 형성방법 | |

| JPH0512878B2 (ko) | ||

| US5207889A (en) | Method of producing treated copper foil, products thereof and electrolyte useful in such method | |

| US3984290A (en) | Method of forming intralayer junctions in a multilayer structure | |

| CA2337186A1 (en) | Composition and method for manufacturing integral resistors in printed circuit boards | |

| KR20100009598A (ko) | 프린트 배선 기판의 제조 방법 및 이 제조 방법에 의해 얻어진 프린트 배선 기판 | |

| US4968398A (en) | Process for the electrolytic removal of polyimide resins | |

| JPH0573359B2 (ko) | ||

| KR830002578B1 (ko) | 후막파인 패턴도전체(厚膜 fine patterned 導電體)의 제조 방법 | |

| JP2673825B2 (ja) | 多層回路基板の製造方法 | |

| JPH02147333A (ja) | 銅張積層板およびプリント配線板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 19960726 Year of fee payment: 5 |

|

| LAPS | Lapse due to unpaid annual fee |