KR20190018424A - 높은 전력 공급 제거비 및 단락 보호를 갖는 보상된 저 드롭아웃 - Google Patents

높은 전력 공급 제거비 및 단락 보호를 갖는 보상된 저 드롭아웃 Download PDFInfo

- Publication number

- KR20190018424A KR20190018424A KR1020187035273A KR20187035273A KR20190018424A KR 20190018424 A KR20190018424 A KR 20190018424A KR 1020187035273 A KR1020187035273 A KR 1020187035273A KR 20187035273 A KR20187035273 A KR 20187035273A KR 20190018424 A KR20190018424 A KR 20190018424A

- Authority

- KR

- South Korea

- Prior art keywords

- ldo

- voltage regulator

- low dropout

- compensating

- amplifier

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/565—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor

- G05F1/569—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection

- G05F1/573—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for protection with overcurrent detector

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/575—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices characterised by the feedback circuit

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

Abstract

LDO(low dropout) 전압 조정기가 개시되며, 이 LDO(low dropout) 전압 조정기는 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키도록 구성된 차동 증폭기, 차동 증폭기에 커플링되고 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터, 차동 증폭기의 출력 노드에 커플링된 보상 커패시터, 및 보조 증폭기를 포함하며, 여기서, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

Description

[0001]

본 개시내용의 양상들은 높은 전력 공급 제거비(PSRR; power supply rejection ratio) 및 단락 보호를 갖는 보상된 저 드롭아웃(LDO; low dropout) 전압 조정기들에 관한 것이다.

[0002]

전력 관리는 전자 산업에서 중요한 역할을 맡는다. 배터리 동력식 및 핸드헬드 디바이스들은, 배터리 수명을 연장시키고 디바이스들의 성능 및 동작을 개선시키기 위한 전력 관리 기법들을 요구한다. 전력 관리의 일 양상은 동작 전압들을 제어하는 것을 포함한다. 종래의 전자 시스템들, 특히 SOC(system on-chip)들은 흔히, 다양한 서브시스템들을 포함한다. 다양한 서브시스템들은 서브시스템들의 특정 필요들에 맞춤화된 상이한 동작 전압들 하에서 동작될 수 있다.

[0003]

특정된 전압들을 다양한 서브시스템들에 전달하기 위해 전압 조정기들이 사용된다. 전압 조정기들은 또한, 서브시스템들을 서로 격리된 상태로 유지하기 위해 사용될 수 있다. LDO(low dropout) 전압 조정기들은 흔히, 고정 전압들을 생성 및 공급하고 저-잡음 회로소자를 달성하기 위해 사용된다.

[0004]

다음은 본원에서 개시된 하나 또는 그 초과의 양상들 및/또는 실시예들에 관한 단순화된 요약을 제시한다. 따라서, 다음의 요약은 모든 고려된 양상들 및/또는 실시예들에 관한 광범위한 개요로 간주되지도 않아야 하며, 다음의 요약은 모든 고려된 양상들 및/또는 실시예들에 관한 핵심적인 또는 중요한 엘리먼트들을 식별하거나 또는 임의의 특정 양상 및/또는 실시예와 연관된 범위를 제한하는 것으로 여겨지지도 않아야 한다. 그에 따라서, 다음의 요약은 본원에서 개시된 메커니즘들에 관한 하나 또는 그 초과의 양상들 및/또는 실시예들에 관한 소정의 개념들을, 아래에서 제시된 상세한 설명에 앞서 단순화된 형태로 제시하는 유일한 목적을 갖는다.

[0005]

LDO(low dropout) 전압 조정기는 기준 전압과 조정 출력 전압 사이의 차동(differential)을 증폭시키도록 구성된 차동 증폭기, 차동 증폭기에 커플링되고 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터, 차동 증폭기의 출력 노드에 커플링된 보상 커패시터, 및 보조 증폭기를 포함하며, 여기서, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

[0006]

LDO 전압 조정기를 보상하기 위한 방법은, 차동 증폭기가 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키는 단계, 차동 증폭기에 커플링된 패스 트랜지스터에서, 차동 증폭기의 출력을 수신하는 단계, 및 보조 증폭기로부터의 출력 신호를 보상 커패시터에서 수신하는 단계를 포함하며, 여기서, 보상 커패시터는 차동 증폭기의 출력 노드에 커플링되고, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

[0007]

LDO 전압 조정기를 보상하기 위한 장치는, 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키도록 구성된 차동 증폭기, 차동 증폭기에 커플링되고 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터, 차동 증폭기의 출력 노드에 커플링된 보상 수단, 및 보조 증폭 수단을 포함하며, 여기서, 보조 증폭 수단의 출력 노드는 보상 수단에 커플링되며, 그리고 보조 증폭 수단의 입력 노드는 패스 트랜지스터에 커플링된다.

[0008]

LDO 전압 조정기를 보상하기 위한 비-일시적인 컴퓨터-판독가능 매체는, 차동 증폭기에 의해 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키기 위한 적어도 하나의 명령, 차동 증폭기에 커플링된 패스 트랜지스터에서 차동 증폭기의 출력을 수신하기 위한 적어도 하나의 명령, 및 보조 증폭기로부터의 출력 신호를 보상 커패시터에서 수신하기 위한 적어도 하나의 명령을 포함하며, 여기서, 보상 커패시터는 차동 증폭기의 출력 노드에 커플링되고, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

[0009]

본원에서 개시된 양상들 및 실시예들과 연관된 다른 목적들 및 장점들은 첨부된 도면들 및 상세한 설명에 기반하여 당업자들에게 자명할 것이다.

[0010]

본 개시내용의 실시예들의 더욱 완전한 인식은, 본 개시내용의 제한이 아니라 오직 예시를 위해서만 제시되는 첨부된 도면들과 관련하여 고려될 때 다음의 상세한 설명을 참조함으로써, 이들이 더욱 잘 이해됨에 따라 용이하게 획득될 것이며, 이 도면들에서:

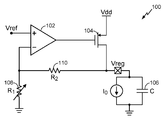

[0011] 도 1은 종래의 LDO(low dropout) 전압 조정기를 예시한다.

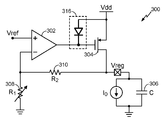

[0012] 도 2는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기를 포함하는 LDO 전압 조정기를 예시한다.

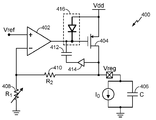

[0013] 도 3은 본 개시내용의 적어도 하나의 양상에 따른, 액티브 클램프를 포함하는 LDO 전압 조정기를 예시한다.

[0014] 도 4는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기, 보상 커패시터, 및 액티브 클램프를 포함하는 LDO 전압 조정기(400)를 예시한다.

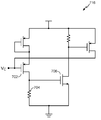

[0015] 도 5는 본 개시내용의 적어도 하나의 양상에 따른 예시적인 차동 증폭기를 예시한다.

[0016] 도 6은 본 개시내용의 적어도 하나의 양상에 따른 예시적인 보조 증폭기를 예시한다.

[0017] 도 7은 본 개시내용의 적어도 하나의 양상에 따른 액티브 클램프 설계를 예시한다.

[0018] 도 8은 본 개시내용의 적어도 하나의 양상에 따른, LDO 전압 조정기를 보상하기 위한 예시적인 흐름을 예시한다.

[0011] 도 1은 종래의 LDO(low dropout) 전압 조정기를 예시한다.

[0012] 도 2는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기를 포함하는 LDO 전압 조정기를 예시한다.

[0013] 도 3은 본 개시내용의 적어도 하나의 양상에 따른, 액티브 클램프를 포함하는 LDO 전압 조정기를 예시한다.

[0014] 도 4는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기, 보상 커패시터, 및 액티브 클램프를 포함하는 LDO 전압 조정기(400)를 예시한다.

[0015] 도 5는 본 개시내용의 적어도 하나의 양상에 따른 예시적인 차동 증폭기를 예시한다.

[0016] 도 6은 본 개시내용의 적어도 하나의 양상에 따른 예시적인 보조 증폭기를 예시한다.

[0017] 도 7은 본 개시내용의 적어도 하나의 양상에 따른 액티브 클램프 설계를 예시한다.

[0018] 도 8은 본 개시내용의 적어도 하나의 양상에 따른, LDO 전압 조정기를 보상하기 위한 예시적인 흐름을 예시한다.

[0019]

LDO(low dropout) 전압 조정기가 개시되며, 이 LDO(low dropout) 전압 조정기는 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키도록 구성된 차동 증폭기, 차동 증폭기에 커플링되고 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터, 차동 증폭기의 출력 노드에 커플링된 보상 커패시터, 및 보조 증폭기를 포함하며, 여기서, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

[0020]

LDO 전압 조정기를 보상하기 위한 방법은, 차동 증폭기가 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키는 단계, 차동 증폭기에 커플링된 패스 트랜지스터에서, 차동 증폭기의 출력을 수신하는 단계, 및 보조 증폭기로부터의 출력 신호를 보상 커패시터에서 수신하는 단계를 포함하며, 여기서, 보상 커패시터는 차동 증폭기의 출력 노드에 커플링되고, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링되며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링된다.

[0021]

본 개시내용의 이러한 그리고 다른 양상들은, 본 개시내용의 특정 실시예들에 관한 다음의 설명 및 관련된 도면들에서 개시된다. 본 개시내용의 범위를 벗어나지 않으면서, 대안적인 실시예들이 고안될 수 있다. 부가적으로, 본 개시내용의 관련 있는 세부사항들을 모호하게 하지 않기 위하여, 본 개시내용의 잘 알려진 엘리먼트들은 상세히 설명되지 않거나 또는 생략될 것이다.

[0022]

"예시적인" 및/또는 "예"란 단어들은 "예, 사례, 또는 예시로서의 역할을 하는" 것을 의미하기 위해 본원에서 사용된다. "예시적인" 것으로서 그리고/또는 "예"로서 본원에서 설명된 임의의 실시예가 반드시 다른 실시예들보다 바람직하거나 또는 유리한 것으로서 해석되어야 하는 것은 아니다. 마찬가지로, "본 개시내용의 실시예들"이란 용어는, 본 개시내용의 모든 실시예들이 논의된 특징, 장점 또는 동작 모드를 포함할 것을 요구하지는 않는다.

[0023]

추가로, 많은 실시예들이 예컨대 컴퓨팅 디바이스의 엘리먼트들에 의해 수행될 액션들의 시퀀스들 측면에서 설명된다. 본원에서 설명된 다양한 액션들이 특정 회로들(예컨대, ASIC(application specific integrated circuit)들)에 의해, 하나 또는 그 초과의 프로세서들에 의해 실행되는 프로그램 명령들에 의해, 또는 이 둘의 결합에 의해 수행될 수 있다는 것이 인식될 것이다. 부가적으로, 본원에서 설명된 액션들의 이러한 시퀀스는 컴퓨터 명령들의 대응하는 세트를 저장하고 있는 임의의 형태의 컴퓨터 판독가능 저장 매체 내에 전적으로 구현되는 것으로 간주될 수 있으며, 이 컴퓨터 명령들은, 실행 시, 연관된 프로세서로 하여금, 본원에서 설명된 기능성을 수행하게 할 것이다. 따라서, 본 개시내용의 다양한 양상들은 다수의 상이한 형태들로 구현될 수 있으며, 이러한 형태들 전부는 청구되는 발명의 요지의 범위 내에 있는 것으로 고려되었다. 부가하여, 본원에서 설명된 실시예들 각각에 대해, 임의의 그러한 실시예들의 대응하는 형태는 예컨대, 설명된 액션을 수행"하도록 구성된 로직"으로서 본원에서 설명될 수 있다.

[0024]

전력 관리는 전자 산업에서 중요한 역할을 맡는다. 배터리 동력식 디바이스들은, 배터리 수명을 연장시키고 디바이스들의 성능 및 동작을 개선시키기 위한 전력 관리 기법들을 요구한다. 전력 관리의 일 양상은 동작 전압들을 제어하는 것을 포함한다. 종래의 전자 시스템들, 특히 SOC(systems on-chip)들은 흔히, 다양한 서브시스템들을 포함한다. 다양한 서브시스템들은 서브시스템들의 특정 필요들에 맞춤화된 상이한 동작 전압들 하에서 동작될 수 있다.

[0025]

연산 증폭기("오피-앰프(op-amp)"로 지칭됨)는, 차동 입력 그리고 종종 싱글-엔디드(single-ended) 출력을 갖는 DC(direct current)-커플링된 고-이득 전자 전압 증폭기이다. 이 구성에서, 오피-앰프는 (회로 접지에 관련된) 출력 전위를 생성하며, 이 출력 전위는 통상적으로, 이 오피-앰프의 입력 단자들 사이의 전위차보다 수십 만 배 더 크다. 더욱 구체적으로, 오피-앰프의 차동 입력들은, 전압 V+를 갖는 비-반전 입력 (+)과 전압 V-를 갖는 반전 입력 (-)으로 구성된다. 이상적으로, 오피-앰프는 차동 입력 전압으로 지칭되는, 두 입력들 사이의 전압의 차이만을 증폭시킨다. 예측가능한 동작이 원해지면, 출력 전압의 일부분을 반전 입력에 인가함으로써, 네거티브 피드백이 사용된다. 이러한 폐쇄 루프 피드백은 회로의 이득을 크게 감소시킨다.

[0026]

특정된 전압들을 디바이스의 다양한 서브시스템들에 전달하기 위해 전압 조정기들이 사용된다. 전압 조정기들은 또한, 서브시스템들을 서로 격리된 상태로 유지하기 위해 사용될 수 있다. LDO(low dropout) 전압 조정기들은 흔히, 고정 전압들을 생성 및 공급하고 저-잡음 회로소자를 달성하기 위해 사용된다.

[0027]

LDO는 폐쇄-루프 오피-앰프이다. LDO가 대형 오프-칩 커패시터("부하 커패시터"로 지칭됨)를 구동하고 큰 전류를 공급해야 할 때, 안정성을 보장하기 위해, 오피-앰프를 보상하는 것은 매우 어렵다. 넓은 범위의 부하 커패시터들 및 부하 전류들은, 회로에 대한 PSRR(power supply rejection ratio)과 안정성을 동시에 충족시키는 것을 더욱 어렵게 한다. PSRR은, 오피-앰프에서의 공급 전압의 변화 대 이 오피-앰프가 생성하는 등가 출력 전압의 비(ratio)(데시벨(dB)로 종종 표현됨)로서 정의된다. 이상적인 오피-앰프는 무한 PSRR을 가질 것이다.

[0028]

도 1은 종래의 LDO 전압 조정기(100)를 예시한다. 도 1에서 예시된 바와 같이, LDO 전압 조정기(100)의 차동 증폭기(102)("에러 증폭기"로 또한 지칭됨)는 입력 기준 전압(Vref)을 수용하고, 조정 출력 전압(Vreg)을 생성한다. 차동 증폭기(102) 증가 출력은 대형 패스 트랜지스터인 트랜지스터(104)(양상에서, PMOS(p-channel metal oxide semiconductor)일 수 있음)를 극적으로 구동한다. LDO 전압 조정기(100)는, 부하 커패시터(C)(106) 그리고 저항기들(R1(108) 및 R2(110))을 더 포함한다. LDO 전압 조정기(100)는 SoC의 다른 서브-블록들에 대한 부하 전류(I0)를 공급한다. 부하 전류(I0)가 부하 커패시터(106)와 연관되지 않음이 주목된다. 부하 전류(I0)는 시스템의 나머지에 공급되며, 부하 커패시터(106)는, LDO 전압 조정기(100)가 고정된 그리고 저잡음의 출력 전압을 제공할 수 있도록 추가된다. 저항기들(R1(108) 및 R2(110))은 피드백 회로를 형성한다. 이 저항기들(R1(108) 및 R2(110)) 중 하나를 조절하는 것은, LDO 전압 조정기(100)의 출력 전압을 프로그래밍하기에 충분하다.

[0029]

LDO 전압 조정기, 이를테면 도 1의 LDO 전압 조정기(100)는 "2 극(pole)" 시스템이다. "극" 그리고 "제로(zero)"가 전기 회로의 안정성의 표시이다. 더욱 구체적으로, 시스템(즉, LDO 전압 조정기(100))의 극들 및 제로들의 주파수들은, 주파수에 대해 그려지는 루프 이득 및 루프 위상을 정의한다. 이들 극들에서 회로의 안정성을 유지하기 위하여, 루프 이득에 대한 댐핑 팩터(damping factor)들로서의 역할을 하는 다른 회로 엘리먼트들을 이용하여 극들은 보상된다. 예컨대 다중 저항기-커패시터 결합들에 기인하여 다수의 극들이 존재하면, 주요 극(dominant pole)을 보상하는 것에 초점이 두어질 수 있다. 그러한 시스템들에서, 비-주요(non-dominant) 극이 주요 극으로부터 멀리 떨어진 상태로 놓이는 것이 바람직하다. 이러한 극 어레인지먼트는 보상 방법을 통해 실현되어야 한다.

[0030]

다시 도 1을 참조하면, 패스 디바이스(예컨대, 트랜지스터(104))의 게이트에 그리고 부하(예컨대, 부하 커패시터(106))에 2개의 (비교적) 저주파수 극들이 존재한다. 안정성을 보장하기 위해, LDO 전압 조정기(100)는 보상될 필요가 있다.

[0031]

예에서, LDO 전압 조정기(100)는, 포지티브 공급 전압(Vdd), 이를테면 1.8V로 바이어싱된 고-전력 1.1V 디지털 베이스-밴드 LDO이며 1.1V 조정 전압을 제공할 수 있다. 이 예에서, 전류(I0)는 5uA로부터 50mA로 변하며, 부하 커패시터(106)는 3.3 내지 대략 10 uF의 커패시턴스를 갖는 대형-부하 오프-칩 바이패스 커패시터이다. 10 uF가 안정성에 대한 극단적인 경우임이 주목된다. 큰 과도(transient) 전류들을 갖는 회로들의 경우, 부하 조정을 개선시키고 전압 과도들을 감소시키기 위해, 대형 오프-칩 바이패스 커패시터(예컨대, 부하 커패시터(106))가 사용된다.

[0032]

안정성과 PSRR을 동시에 충족시키기 위해 오피-앰프를 보상하는 것에 대한 난제들은, 극저(ultra-low) 전력 애플리케이션, 이를테면 배터리-작동식 디바이스 및 대형 오프-칩 바이패스 커패시터(예컨대, 부하 커패시터(106))에 대해 설계할 때 해결하기가 더욱 어려워진다. 종래에, 밀러 보상(Miller compensation)은 강건한 오피-앰프 안정화 방법이지만, 위에서 주목된 난제들을 고려하면, 밀러 보상은 칩 상에 배치될 수 없는 대형 보상 커패시터를 요구한다. 밀러 보상은 또한, 어떤 PSR(power supply rejection)도 제공하지 않는다. 그러므로, 충분한 PSRR도 또한 제공하는, 입수가능한(affordable) 커패시터를 이용한 보상된 오피-앰프가 필요하다.

[0033]

본 개시내용은 LDO 전압 조정기에 보조 증폭기를 도입한다. 더욱 구체적으로, 보조 증폭기는 보상 커패시터 앞에 추가된다. 보조 증폭기에 의해 제공되는 이득에 기반하여, 보상 커패시터의 효과가 증가된다. 예컨대, 보조 증폭기가 20dB 이득을 제공하면, 이는 보상 커패시터의 효과를 10배 더 크게 한다. 따라서 보상 커패시터는 10배 더 작을 수 있다. 예컨대, 전통적인 밀러 보상을 위한 보상 커패시터가 400 피코 패럿(pF)이면, 보조 증폭기를 갖는 보상기를 위한 보상 커패시터는 단지 40pF이 될 필요가 있다(즉, 400 pF이 10배 감소되거나, 또는 10으로 나누어짐).

[0034]

도 2는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기(214) 및 보상 커패시터(212)를 포함하는 LDO 전압 조정기(200)를 예시한다. 도 1에서와 같이, LDO 전압 조정기(200)의 차동 증폭기(202)는 입력 기준 전압(Vref)을 수용하고, 조정 출력 전압(Vreg)을 생성한다. 차동 증폭기(202)의 출력은 대형 패스 트랜지스터인 트랜지스터(204)(양상에서, PMOS일 수 있음)를 구동한다. LDO 전압 조정기(100)와 유사하게, LDO 전압 조정기(200)는, 부하 커패시터(C)(206) 그리고 저항기들(R1(208) 및 R2(210))을 더 포함한다. LDO 전압 조정기(200)는 시스템의 다른 서브-블록들에 대한 부하 전류(I0)를 공급한다. 그러나, LDO 전압 조정기(100)와는 대조적으로, LDO 전압 조정기(200)는, 위에서 설명된 바와 같이, 보상 커패시터(212) 앞에 보조 증폭기(214)를 포함한다.

[0035]

보상 커패시터(212) 앞에 보조 증폭기(214)를 추가하는 것의 이득들은, 위에서 설명된 바와 같이, 보조 증폭기(214)의 이득의 양만큼, 보상 커패시터(212)의 크기의 감소를 포함한다. 예컨대, 보조 증폭기(214)가 20dB 이득을 제공하면, 이는 보상 커패시터(212)의 효과를 10배 더 크게 한다. 따라서, LDO 전압 조정기(200)가 단지 보조 증폭기(214)를 포함하면, 보상 커패시터(212)가 달리 되어야 할 것보다, 보상 커패시터(212)는 10배 더 작을 수 있다. 부가하여, PSRR은 보조 증폭기(214)의 이득의 양만큼 개선된다. 보조 증폭기(214)가 없으면, 고주파수들에서, 공급 잡음(supply noise)은 LDO 출력에 직접적으로 커플링될 것이며, 어떤 공급 제거(supply rejection)도 존재하지 않을 것이다.

[0036]

실시예에서, LDO 전압 조정기(이를테면, LDO 전압 조정기(100))는 단락 클램프를 포함할 수 있다. 그러한 LDO 전압 조정기는 배터리로부터 포지티브 공급 전압(Vdd)(예컨대, 2V 내지 3.6V)을 수신하고 조정 출력 전압(Vreg), 이를테면 1.8V를 제공할 수 있다. 큰 입력 전압들의 경우, 단락 보호(short circuit protection)를 갖는 것이 바람직한데, 그 이유는 PMOS 디바이스(예컨대, 트랜지스터(104))의 게이트-소스 전압들이 3.6V만큼 커지고, 출력이 쇼트되면, LDO 전압 조정기에 큰 전류를 생성할 수 있기 때문이다. PMOS의 출력에 직렬 저항기를 추가하는 것이 그러한 단락을 제한할 수 있지만, 그러한 LDO 전압 조정기가 제공하는 큰 전류 및 저전압 헤드룸(headroom)을 이용하여, V=I*R 전압 강하를 방지하는 것이 바람직하다.

[0037]

이들 이슈들을 해결하기 위해, LDO 전압 조정기에 액티브 클램프가 추가될 수 있다. 액티브 클램프는 바람직하게는, 이 액티브 클램프가 LDO 전압 조정기의 정상 동작에 관여되는 것이 아니라, 전류의 단락 서지를 제한하기 위해 PMOS 게이트를 유지함을 보장하도록, 비-선형이어야 한다.

[0038]

도 3은 본 개시내용의 적어도 하나의 양상에 따른, 액티브 클램프(316)를 포함하는 LDO 전압 조정기(300)를 예시한다. 도 1의 LDO 전압 조정기(100)와 유사하게, LDO 전압 조정기(300)의 차동 증폭기(302)는 입력 기준 전압(Vref)을 수용하고, 조정 출력 전압을 생성한다. 차동 증폭기(302)의 출력은 대형 패스 트랜지스터인 트랜지스터(304)(양상에서, PMOS일 수 있음)를 구동한다. LDO 전압 조정기(100)처럼, LDO 전압 조정기(300)는, 부하 커패시터(C)(306) 그리고 저항기들(R1(308) 및 R2(310))을 더 포함한다. LDO 전압 조정기(300)는 시스템의 다른 서브-블록들에 대한 부하 전류(I0)를 공급한다.

[0039]

도 3에서 도시된 바와 같이, 차동 증폭기(302)와 트랜지스터(304) 사이에 액티브 클램프(316)가 배치된다. LDO 전압 조정기(300)에서의 액티브 클램프(316)의 설계(도 7에서 도시됨)는, 통상적인 CMOS 비선형성과 대조적으로, 그것의 비선형성을 강화한다. 이 설계는 또한, 오피-앰프 이득을 방해하지 않기 위해 높은 출력 저항을 제공하며, 이 출력 저항을 설계할 때 자유도를 제공한다. LDO 전압 조정기(300)는 배터리로부터 예컨대 2V 내지 3.6V의 포지티브 공급 전압(Vdd)을 공급받고, 예컨대 1.8V의 조정 출력 전압(Vreg)을 오프-칩 부하 커패시터에 공급한다. 액티브 클램프(316)가 없으면, LDO 전압 조정기(300)는 단락 보호를 갖지 않을 것이다.

[0040]

도 4는 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기(414), 보상 커패시터(412), 및 액티브 클램프(416)를 포함하는 LDO 전압 조정기(400)를 예시한다. 도 2에서와 같이, LDO 전압 조정기(400)의 차동 증폭기(402)는 입력 기준 전압(Vref)을 수용하고, 조정 출력 전압을 생성한다. 차동 증폭기(402)의 출력은 대형 패스 트랜지스터인 트랜지스터(404)(양상에서, PMOS 디바이스일 수 있음)를 구동한다. 위에서 설명된 바와 같이, LDO 전압 조정기(400)는, 부하 커패시터(C)(406), 저항기들(R1(408) 및 R2(410)), 그리고 보상 커패시터(412) 앞의 보조 증폭기(414)를 더 포함한다.

[0041]

도 4의 예에서, LDO 전압 조정기(400)는 또한, 도 3을 참조하여 위에서 설명된 바와 같이, 차동 증폭기(402)와 트랜지스터(404) 사이에 배치된 액티브 클램프(416)를 포함한다. LDO 전압 조정기(300)와 유사하게, LDO 전압 조정기(400)는 배터리로부터 예컨대 2V 내지 3.6V의 포지티브 공급 전압(Vdd)을 공급받고, 예컨대 1.8V의 조정 출력 전압을 오프-칩 부하 커패시터에 공급한다.

[0042]

도 5는 본 개시내용의 적어도 하나의 양상에 따른, 차동 증폭기(502), 이를테면 도 2의 차동 증폭기(202), 도 3의 차동 증폭기(302), 또는 도 4의 차동 증폭기(402)의 다이어그램이다. 차동 증폭기(502)는 낮은 바이어스 전류(Ibias), 이를테면 1.2 마이크로 암페어(uA)를 사용하는데, 그 이유는 위에서 주목된 바와 같이, 이러한 낮은 바이어스 전류(Ibias)가 저전력 배터리-작동식 디바이스에서 활용되기 때문이다(예컨대, 차동 증폭기(502)의 포지티브 공급 전압(Vdd)은 1.3V일 수 있음). 차동 증폭기(502)는 예컨대 800mV DC 전압 및 예컨대 밴드갭 전류(Ibandgap)에 의해 제공되는 25 나노 암페어(nA) 전류로 바이어싱된다.

[0043]

도 6은 본 개시내용의 적어도 하나의 양상에 따른, 보조 증폭기(614), 이를테면 도 2의 보조 증폭기(214), 도 3의 보조 증폭기(314), 및 도 4의 보조 증폭기(414)의 다이어그램이다. 보조 증폭기(614)는 이득을 제한하기 위해 저항성 부하(Rload), 이를테면 5MΩ을 갖는 저전력 개방 루프 차동 증폭기이다. 예에서, 포지티브 공급 전압(Vdd)은 1.3V일 수 있고, 밴드갭 전류(Ibandgap)는 25 nA일 수 있고, 제1 바이어스 전류(Ibias1)는 650nA일 수 있으며, 그리고 제2 바이어스 전류(Ibias2)는 1.4uA일 수 있다.

[0044]

도 7은 본 개시내용의 적어도 하나의 양상에 따른, 액티브 클램프(716), 이를테면 도 3의 액티브 클램프(316) 및/또는 도 4의 액티브 클램프(416)의 다이어그램이다. LDO 전압 조정기(예컨대, 도 3의 LDO 전압 조정기(300) 또는 도 4의 LDO 전압 조정기(400))의 출력이 쇼트될 때, 액티브 클램프(716)의 부재 시, 패스 디바이스(예컨대, 도 3의 트랜지스터(304) 또는 도 4의 트랜지스터(404))의 게이트 전압(제어 전압(VC)으로 또한 지칭됨)은 너무 많이(예컨대, 100mV 미만으로) 강하할 것이며, 상당한 전류 서지(예컨대, 2 암페어만큼 큰 전류 서지)가 패스 디바이스를 통과할 것이다. 그러나, 액티브 클램프(716)의 존재 시, VC의 전압 강하는 디바이스(702)에서 전류 흐름을 유발한다. 이 전류는 저항기(704)를 통과하고, 그런 다음, 다른 디바이스(706)에 의해, VC에 대한 이 다른 디바이스(706)의 비선형성을 강화하기 위해 증폭된다. VC의 작은 강하(예컨대, 0.5V)는 전류가 노드(VC)에 주입되게 한다. 액티브 클램프(716)가 없으면, VC는 내내 0V로 강하할 수 있다. 주입된 전류는 차동 증폭기(예컨대, 도 3의 차동 증폭기(302) 또는 도 4의 차동 증폭기(402))에 의해 싱크되며, 차동 증폭기의 제한된 바이어스 전류는 액티브 클램프(716)에서의 전류를 제한한다. 그 결과, VC는 너무 많이 강하할 수 없다. 예컨대, LDO 전압 조정기에서의 3.6V 배터리 전압에 대해, VC의 2V 강하가 너무 많을 것인 반면, VC의 0.5V 강하는 용인될 수 있다. 전류 서지 측면에서, 2A의 전류가 너무 많을 것인 반면, 200mA의 전류는 용인가능할 것이다.

[0045]

도 8은 본 개시내용의 적어도 하나의 양상에 따른, LDO 전압 조정기를 보상하기 위한 예시적인 흐름(800)을 예시한다. LDO 전압 조정기는 폐쇄 루프 연산 증폭기일 수 있다. 양상에서, LDO 전압 조정기는 밀러 보상을 활용할 수 있다.

[0046]

802에서, 흐름(800)은, 차동 증폭기(예컨대, 도 2의 차동 증폭기(202), 도 3의 차동 증폭기(302), 또는 도 4의 차동 증폭기(402))가 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키는 단계를 포함한다.

[0047]

804에서, 흐름(800)은, 차동 증폭기에 커플링된 패스 트랜지스터(예컨대, 도 2의 트랜지스터(204), 도 3의 트랜지스터(304), 또는 도 4의 트랜지스터(404))에서, 차동 증폭기의 출력을 수신하는 단계를 포함한다.

[0048]

806에서, 흐름(800)은, 보조 증폭기(예컨대, 도 2의 보조 증폭기(214) 또는 도 4의 보조 증폭기(414))로부터의 출력 신호를 보상 커패시터(예컨대, 도 2의 보상 커패시터(212) 또는 도 4의 보상 커패시터(412))에서 수신하는 단계를 포함한다. 도 2 및 도 4에서 예시된 바와 같이, 보상 커패시터는 차동 증폭기의 출력 노드에 커플링될 수 있고, 보조 증폭기의 출력 노드는 보상 커패시터에 커플링될 수 있으며, 그리고 보조 증폭기의 입력 노드는 패스 트랜지스터에 커플링될 수 있다. 보조 증폭기는 저전류 개방 루프 차동 증폭기일 수 있다. 예컨대, 저전류는 25 나노 암페어의 전류일 수 있다.

[0049]

808에서, 흐름(800)은 선택적으로, 차동 증폭기의 출력 노드 및 패스 트랜지스터에 액티브 클램프를 커플링하는 단계를 포함한다. 액티브 클램프는 패스 트랜지스터로부터의 단락 전류 서지들을 제한한다. 패스 트랜지스터는 배터리로부터 2V 내지 3.6V의 전압을 수신하며, LDO 전압 조정기는 1.8V의 전압을 오프-칩 부하 커패시터에 공급한다.

[0050]

양상에서, 보조 증폭기로부터의 출력 신호는, 보상 커패시터의 보상이 보조 증폭기로부터의 입력 신호에 의해 제공되는 이득의 양에 기반하여 증가하게 할 수 있다. 그 경우, 보상 커패시터의 보상은 LDO 전압 조정기를 포함하는 회로를 안정시킨다.

[0051]

다른 양상에서, LDO 전압 조정기를 포함하는 회로의 PSRR은 보조 증폭기에 의해 제공되는 이득의 양에 기반하여 개선될 수 있다.

[0052]

또 다른 양상에서, 보조 증폭기는, 보조 증폭기의 이득의 양을 제한하는 저항성 부하를 포함할 수 있다.

[0053]

당업자들은, 정보 및 신호들이 다양한 상이한 기술들 및 기법들 중의 임의의 것을 사용하여 표현될 수 있다는 것을 인식할 것이다. 예컨대, 위의 상세한 설명 전체에 걸쳐 참조될 수 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들, 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 자기 입자들, 광학 필드들 또는 광학 입자들, 또는 이들의 임의의 결합에 의해 표현될 수 있다.

[0054]

추가로, 당업자들은, 본원에서 개시된 실시예들과 관련하여 설명된 다양한 예시적인 로직 블록들, 모듈들, 회로들, 및 알고리즘 단계들이 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이 둘의 결합들로서 구현될 수 있다는 것을 인식할 것이다. 하드웨어와 소프트웨어의 이러한 상호교환가능성을 명확하게 예시하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들은 일반적으로 그들의 기능성 측면에서 위에서 설명되었다. 그러한 기능성이 하드웨어로서 구현되는지 또는 소프트웨어로서 구현되는지는 특정 애플리케이션, 및 전체 시스템에 부과된 설계 제약들에 따라 좌우된다. 당업자들은 설명된 기능성을 각각의 특정 애플리케이션에 대해 다양한 방식들로 구현할 수 있지만, 그러한 구현 결정들은 본 개시내용의 범위를 벗어나게 하는 것으로서 해석되지 않아야 한다.

[0055]

본원에서 개시된 실시예들과 관련하여 설명된 다양한 예시적인 로직 블록들, 모듈들, 및 회로들은 범용 프로세서, DSP(digital signal processor), ASIC(application specific integrated circuit), FPGA(field programmable gate array) 또는 다른 프로그램가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본원에서 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합으로 구현되거나 또는 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수 있다. 프로세서는 또한, 컴퓨팅 디바이스들의 결합, 예컨대, DSP와 마이크로프로세서의 결합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 또는 그 초과의 마이크로프로세서들, 또는 임의의 다른 그러한 구성으로서 구현될 수 있다.

[0056]

본원에서 개시된 실시예들과 관련하여 설명된 방법들, 시퀀스들 및/또는 알고리즘들은 직접적으로 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로, 또는 이 둘의 결합으로 구현될 수 있다. 소프트웨어 모듈은 RAM 메모리, 플래시 메모리, ROM 메모리, EPROM 메모리, EEPROM 메모리, 레지스터들, 하드 디스크, 탈착가능 디스크, CD-ROM, 또는 기술분야에서 알려진 임의의 다른 형태의 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독하고 저장 매체에 정보를 기록할 수 있도록, 프로세서에 커플링된다. 대안적으로, 저장 매체는 프로세서에 일체형일 수 있다. 프로세서 및 저장 매체는 ASIC에 상주할 수 있다. ASIC는 사용자 단말(예컨대, UE)에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 사용자 단말에서 이산 컴포넌트들로서 상주할 수 있다.

[0057]

하나 또는 그 초과의 예시적인 실시예들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 결합으로 구현될 수 있다. 소프트웨어로 구현되면, 기능들은 컴퓨터-판독가능 매체 상의 하나 또는 그 초과의 명령 또는 코드로서 저장되거나 또는 이를 통해 송신될 수 있다. 컴퓨터-판독가능 매체는, 일 장소로부터 다른 장소로의 컴퓨터 프로그램의 전송을 용이하게 하는 임의의 매체를 포함하는 통신 매체 및 컴퓨터 저장 매체 둘 모두를 포함한다. 저장 매체는 컴퓨터에 의해 액세스될 수 있는 임의의 이용가능한 매체일 수 있다. 제한이 아닌 예로서, 그러한 컴퓨터-판독가능 매체는 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장부, 자기 디스크 저장부 또는 다른 자기 저장 디바이스들, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드를 반송(carry)하거나 또는 저장하기 위해 사용될 수 있고, 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다. 또한, 임의의 연결이 컴퓨터-판독가능 매체로 적절히 불린다. 예컨대, 소프트웨어가 동축 케이블, 광섬유 케이블, 연선(twisted pair), DSL(digital subscriber line), 또는 적외선, 라디오, 및 마이크로파와 같은 무선 기술들을 사용하여 웹사이트, 서버, 또는 다른 원격 소스로부터 송신되면, 동축 케이블, 광섬유 케이블, 연선, DSL, 또는 적외선, 라디오, 및 마이크로파와 같은 무선 기술들이 매체의 정의에 포함된다. 본원에서 사용된 바와 같이, 디스크(disk) 및 디스크(disc)는 컴팩트 디스크(CD; compact disc), 레이저 디스크(disc), 광학 디스크(disc), 디지털 다기능 디스크(DVD; digital versatile disc), 플로피 디스크(disk) 및 블루-레이 디스크(disc)를 포함하며, 여기서 디스크(disk)들은 대개 자기적으로 데이터를 재생하는 반면, 디스크(disc)들은 레이저들을 이용하여 광학적으로 데이터를 재생한다. 상기한 것들의 결합들이 또한, 컴퓨터-판독가능 매체의 범위 내에 포함되어야 한다.

[0058]

전술한 개시내용이 본 개시내용의 예시적인 실시예들을 나타내지만, 첨부된 청구항들에 의해 정의된 본 개시내용의 범위를 벗어나지 않으면서, 다양한 변화들 및 수정들이 본원에서 이루어질 수 있다는 것이 주목되어야 한다. 본원에서 설명된 개시내용의 실시예들에 따른 방법 청구항들의 기능들, 단계들 및/또는 액션들은 임의의 특정 순서로 수행될 필요가 없다. 더욱이, 본 개시내용의 엘리먼트들이 단수형으로 설명되거나 또는 청구될 수 있지만, 단수형으로의 제한이 명시적으로 진술되지 않는 한, 복수형이 고려된다.

Claims (30)

- LDO(low dropout) 전압 조정기로서,

기준 전압과 조정 출력 전압 사이의 차동(differential)을 증폭시키도록 구성된 차동 증폭기;

상기 차동 증폭기에 커플링되고, 상기 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터;

상기 차동 증폭기의 출력 노드에 커플링된 보상 커패시터; 및

보조 증폭기

를 포함하며,

상기 보조 증폭기의 출력 노드는 상기 보상 커패시터에 커플링되며, 그리고 상기 보조 증폭기의 입력 노드는 상기 패스 트랜지스터에 커플링되는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 보상 커패시터의 보상은 상기 보조 증폭기에 의해 제공되는 이득의 양에 기반하여 증가되는,

LDO(low dropout) 전압 조정기. - 제2 항에 있어서,

상기 보상 커패시터의 보상은 상기 LDO 전압 조정기를 포함하는 회로를 안정시키는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 LDO 전압 조정기를 포함하는 회로의 PSRR(power supply rejection ratio)은 상기 보조 증폭기에 의해 제공되는 이득의 양에 기반하여 개선되는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 LDO 전압 조정기는 밀러 보상(Miller compensation)을 활용하는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 보조 증폭기는 저전류 개방 루프 차동 증폭기를 포함하는,

LDO(low dropout) 전압 조정기. - 제6 항에 있어서,

상기 저전류는 25 나노 암페어의 전류를 포함하는,

LDO(low dropout) 전압 조정기. - 제6 항에 있어서,

상기 보조 증폭기는, 상기 보조 증폭기의 이득의 양을 제한하는 저항성 부하를 포함하는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 LDO 전압 조정기는 폐쇄 루프 연산 증폭기를 포함하는,

LDO(low dropout) 전압 조정기. - 제1 항에 있어서,

상기 차동 증폭기의 상기 출력 노드 및 상기 패스 트랜지스터에 커플링된 액티브 클램프

를 더 포함하는,

LDO(low dropout) 전압 조정기. - 제10 항에 있어서,

상기 액티브 클램프는 상기 패스 트랜지스터로부터의 단락 전류 서지들을 제한하는,

LDO(low dropout) 전압 조정기. - 제10 항에 있어서,

상기 패스 트랜지스터는 배터리로부터 2V 내지 3.6V의 전압을 수신하며, 상기 LDO 전압 조정기는 1.8V의 전압을 오프-칩 부하 커패시터에 공급하는,

LDO(low dropout) 전압 조정기. - LDO(low dropout) 전압 조정기를 보상하기 위한 방법으로서,

차동 증폭기가 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키는 단계;

상기 차동 증폭기에 커플링된 패스 트랜지스터에서, 상기 차동 증폭기의 출력을 수신하는 단계; 및

보조 증폭기로부터의 출력 신호를 보상 커패시터에서 수신하는 단계

를 포함하며,

상기 보상 커패시터는 상기 차동 증폭기의 출력 노드에 커플링되고, 상기 보조 증폭기의 출력 노드는 상기 보상 커패시터에 커플링되며, 그리고 상기 보조 증폭기의 입력 노드는 상기 패스 트랜지스터에 커플링되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 보조 증폭기로부터의 상기 출력 신호는, 상기 보상 커패시터의 보상이 상기 보조 증폭기로부터의 입력 신호에 의해 제공되는 이득의 양에 기반하여 증가하게 하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제14 항에 있어서,

상기 보상 커패시터의 보상은 상기 LDO 전압 조정기를 포함하는 회로를 안정시키는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 LDO 전압 조정기를 포함하는 회로의 PSRR(power supply rejection ratio)은 상기 보조 증폭기에 의해 제공되는 이득의 양에 기반하여 개선되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 LDO 전압 조정기는 밀러 보상을 활용하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 보조 증폭기는 저전류 개방 루프 차동 증폭기를 포함하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제18 항에 있어서,

상기 저전류는 25 나노 암페어의 전류를 포함하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제18 항에 있어서,

상기 보조 증폭기는, 상기 보조 증폭기의 이득의 양을 제한하는 저항성 부하를 포함하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 LDO 전압 조정기는 폐쇄 루프 연산 증폭기를 포함하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제13 항에 있어서,

상기 차동 증폭기의 상기 출력 노드 및 상기 패스 트랜지스터에 액티브 클램프를 커플링하는 단계

를 더 포함하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제22 항에 있어서,

상기 액티브 클램프는 상기 패스 트랜지스터로부터의 단락 전류 서지들을 제한하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - 제22 항에 있어서,

상기 패스 트랜지스터는 배터리로부터 2V 내지 3.6V의 전압을 수신하며, 상기 LDO 전압 조정기는 1.8V의 전압을 오프-칩 부하 커패시터에 공급하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 방법. - LDO(low dropout) 전압 조정기를 보상하기 위한 장치로서,

기준 전압과 조정 출력 전압 사이의 차동을 증폭시키도록 구성된 차동 증폭기;

상기 차동 증폭기에 커플링되고, 상기 차동 증폭기의 출력에 의해 구동되는 패스 트랜지스터;

상기 차동 증폭기의 출력 노드에 커플링된 보상 수단; 및

보조 증폭 수단

을 포함하며,

상기 보조 증폭 수단의 출력 노드는 상기 보상 수단에 커플링되며, 그리고 상기 보조 증폭 수단의 입력 노드는 상기 패스 트랜지스터에 커플링되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 장치. - 제25 항에 있어서,

상기 보상 수단의 보상은 상기 보조 증폭 수단에 의해 제공되는 이득의 양에 기반하여 증가되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 장치. - 제25 항에 있어서,

상기 LDO 전압 조정기를 포함하는 회로의 PSRR(power supply rejection ratio)은 상기 보조 증폭 수단에 의해 제공되는 이득의 양에 기반하여 개선되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 장치. - LDO(low dropout) 전압 조정기를 보상하기 위한 비-일시적인 컴퓨터-판독가능 저장 매체로서,

차동 증폭기에 의해 기준 전압과 조정 출력 전압 사이의 차동을 증폭시키기 위한 적어도 하나의 명령;

상기 차동 증폭기에 커플링된 패스 트랜지스터에서 상기 차동 증폭기의 출력을 수신하기 위한 적어도 하나의 명령; 및

보조 증폭기로부터의 출력 신호를 보상 커패시터에서 수신하기 위한 적어도 하나의 명령

을 포함하며,

상기 보상 커패시터는 상기 차동 증폭기의 출력 노드에 커플링되고, 상기 보조 증폭기의 출력 노드는 상기 보상 커패시터에 커플링되며, 그리고 상기 보조 증폭기의 입력 노드는 상기 패스 트랜지스터에 커플링되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 비-일시적인 컴퓨터-판독가능 저장 매체. - 제28 항에 있어서,

상기 보조 증폭기로부터의 상기 출력 신호는, 상기 보상 커패시터의 보상이 상기 보조 증폭기로부터의 입력 신호에 의해 제공되는 이득의 양에 기반하여 증가하게 하는,

LDO(low dropout) 전압 조정기를 보상하기 위한 비-일시적인 컴퓨터-판독가능 저장 매체. - 제28 항에 있어서,

상기 LDO 전압 조정기를 포함하는 회로의 PSRR(power supply rejection ratio)은 상기 보조 증폭기에 의해 제공되는 이득의 양에 기반하여 개선되는,

LDO(low dropout) 전압 조정기를 보상하기 위한 비-일시적인 컴퓨터-판독가능 저장 매체.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/186,411 US10175706B2 (en) | 2016-06-17 | 2016-06-17 | Compensated low dropout with high power supply rejection ratio and short circuit protection |

| US15/186,411 | 2016-06-17 | ||

| PCT/US2017/033812 WO2017218141A1 (en) | 2016-06-17 | 2017-05-22 | Compensated low dropout with high power supply rejection ratio and short circuit protection |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20190018424A true KR20190018424A (ko) | 2019-02-22 |

Family

ID=58794252

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187035273A KR20190018424A (ko) | 2016-06-17 | 2017-05-22 | 높은 전력 공급 제거비 및 단락 보호를 갖는 보상된 저 드롭아웃 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US10175706B2 (ko) |

| EP (1) | EP3472682A1 (ko) |

| JP (1) | JP2019518282A (ko) |

| KR (1) | KR20190018424A (ko) |

| CN (1) | CN109219786A (ko) |

| BR (1) | BR112018075103A2 (ko) |

| WO (1) | WO2017218141A1 (ko) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9817416B2 (en) * | 2015-08-17 | 2017-11-14 | Skyworks Solutions, Inc. | Apparatus and methods for programmable low dropout regulators for radio frequency electronics |

| EP3586272B1 (de) * | 2016-02-29 | 2020-10-07 | Gerd Reime | Bidirektionaler transponder mit geringem energieverbrauch |

| CN109634344A (zh) * | 2017-03-08 | 2019-04-16 | 长江存储科技有限责任公司 | 一种高带宽低压差线性稳压器 |

| WO2019008817A1 (ja) * | 2017-07-03 | 2019-01-10 | 三菱電機株式会社 | 半導体スイッチング素子の短絡保護回路 |

| US10382030B2 (en) * | 2017-07-12 | 2019-08-13 | Texas Instruments Incorporated | Apparatus having process, voltage and temperature-independent line transient management |

| US11009901B2 (en) * | 2017-11-15 | 2021-05-18 | Qualcomm Incorporated | Methods and apparatus for voltage regulation using output sense current |

| US10411599B1 (en) | 2018-03-28 | 2019-09-10 | Qualcomm Incorporated | Boost and LDO hybrid converter with dual-loop control |

| US10444780B1 (en) | 2018-09-20 | 2019-10-15 | Qualcomm Incorporated | Regulation/bypass automation for LDO with multiple supply voltages |

| US10591938B1 (en) | 2018-10-16 | 2020-03-17 | Qualcomm Incorporated | PMOS-output LDO with full spectrum PSR |

| US10545523B1 (en) | 2018-10-25 | 2020-01-28 | Qualcomm Incorporated | Adaptive gate-biased field effect transistor for low-dropout regulator |

| US10726881B1 (en) * | 2019-04-08 | 2020-07-28 | Texas Instruments Incorporated | Supply voltage clamping for improved power supply rejection ratio |

| US11372436B2 (en) | 2019-10-14 | 2022-06-28 | Qualcomm Incorporated | Simultaneous low quiescent current and high performance LDO using single input stage and multiple output stages |

| US11526187B2 (en) * | 2020-01-03 | 2022-12-13 | Skyworks Solutions, Inc. | Method and system for boosting output current |

| DE102020115851B3 (de) | 2020-06-16 | 2021-10-28 | Infineon Technologies Ag | Schneller spannungsregler und verfahren zur spannungsregelung |

| CN112130612A (zh) * | 2020-09-23 | 2020-12-25 | 中国电子科技集团公司第五十八研究所 | 一种具有稳定性补偿的大电流线性稳压器电路 |

| CN114442714A (zh) * | 2020-11-02 | 2022-05-06 | 圣邦微电子(北京)股份有限公司 | 一种用于钳位PMOS的Vgs的新型钳位结构 |

| CN112327987B (zh) * | 2020-11-18 | 2022-03-29 | 上海艾为电子技术股份有限公司 | 一种低压差线性稳压器及电子设备 |

| US11687104B2 (en) | 2021-03-25 | 2023-06-27 | Qualcomm Incorporated | Power supply rejection enhancer |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2356991B (en) | 1999-12-02 | 2003-10-22 | Zetex Plc | A negative feedback amplifier circuit |

| US6246221B1 (en) * | 2000-09-20 | 2001-06-12 | Texas Instruments Incorporated | PMOS low drop-out voltage regulator using non-inverting variable gain stage |

| JP2002343874A (ja) * | 2001-05-17 | 2002-11-29 | Nippon Telegr & Teleph Corp <Ntt> | シリーズレギュレータ回路 |

| US6522112B1 (en) | 2001-11-08 | 2003-02-18 | National Semiconductor Corporation | Linear regulator compensation inversion |

| US6600299B2 (en) | 2001-12-19 | 2003-07-29 | Texas Instruments Incorporated | Miller compensated NMOS low drop-out voltage regulator using variable gain stage |

| EP1378808B1 (en) * | 2002-07-05 | 2008-02-20 | Dialog Semiconductor GmbH | LDO regulator with wide output load range and fast internal loop |

| US6977490B1 (en) * | 2002-12-23 | 2005-12-20 | Marvell International Ltd. | Compensation for low drop out voltage regulator |

| JP2005202781A (ja) * | 2004-01-16 | 2005-07-28 | Artlogic Inc | 電圧レギュレータ |

| US7002409B1 (en) | 2004-02-11 | 2006-02-21 | Marvell International Ltd. | Compensation circuit for amplifiers having multiple stages |

| US6975099B2 (en) * | 2004-02-27 | 2005-12-13 | Texas Instruments Incorporated | Efficient frequency compensation for linear voltage regulators |

| KR100608112B1 (ko) | 2004-08-27 | 2006-08-02 | 삼성전자주식회사 | 과전류 보호회로를 구비한 전원 레귤레이터 및 전원레귤레이터의 과전류 보호방법 |

| US7323854B2 (en) * | 2005-08-05 | 2008-01-29 | Micrel, Incorporated | Zero cancellation in multiloop regulator control scheme |

| JP4833652B2 (ja) * | 2005-12-08 | 2011-12-07 | ローム株式会社 | レギュレータ回路およびそれを搭載した自動車 |

| US7446515B2 (en) | 2006-08-31 | 2008-11-04 | Texas Instruments Incorporated | Compensating NMOS LDO regulator using auxiliary amplifier |

| TWI332134B (en) * | 2006-12-28 | 2010-10-21 | Ind Tech Res Inst | Adaptive pole and zero & pole zero cancellation control low drop-out voltage regulator |

| US7710091B2 (en) * | 2007-06-27 | 2010-05-04 | Sitronix Technology Corp. | Low dropout linear voltage regulator with an active resistance for frequency compensation to improve stability |

| CN201152948Y (zh) * | 2008-02-03 | 2008-11-19 | 深圳艾科创新微电子有限公司 | 一种带短路保护的可变输出线性稳压器 |

| US8872492B2 (en) | 2010-04-29 | 2014-10-28 | Qualcomm Incorporated | On-chip low voltage capacitor-less low dropout regulator with Q-control |

| US9134743B2 (en) * | 2012-04-30 | 2015-09-15 | Infineon Technologies Austria Ag | Low-dropout voltage regulator |

| CN102722207B (zh) * | 2012-05-28 | 2014-08-20 | 华为技术有限公司 | 一种低压差线性稳压器 |

| EP2816438B1 (en) | 2013-06-20 | 2017-11-15 | Dialog Semiconductor GmbH | Active clamps for multi-stage amplifiers in over/under-voltage condition |

| US9552004B1 (en) * | 2015-07-26 | 2017-01-24 | Freescale Semiconductor, Inc. | Linear voltage regulator |

-

2016

- 2016-06-17 US US15/186,411 patent/US10175706B2/en active Active

-

2017

- 2017-05-22 KR KR1020187035273A patent/KR20190018424A/ko not_active Application Discontinuation

- 2017-05-22 EP EP17726511.3A patent/EP3472682A1/en not_active Withdrawn

- 2017-05-22 JP JP2018560981A patent/JP2019518282A/ja active Pending

- 2017-05-22 BR BR112018075103A patent/BR112018075103A2/pt not_active IP Right Cessation

- 2017-05-22 WO PCT/US2017/033812 patent/WO2017218141A1/en unknown

- 2017-05-22 CN CN201780034598.8A patent/CN109219786A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20170364110A1 (en) | 2017-12-21 |

| EP3472682A1 (en) | 2019-04-24 |

| JP2019518282A (ja) | 2019-06-27 |

| US10175706B2 (en) | 2019-01-08 |

| BR112018075103A2 (pt) | 2019-03-26 |

| CN109219786A (zh) | 2019-01-15 |

| WO2017218141A1 (en) | 2017-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10175706B2 (en) | Compensated low dropout with high power supply rejection ratio and short circuit protection | |

| US10534385B2 (en) | Voltage regulator with fast transient response | |

| US8872492B2 (en) | On-chip low voltage capacitor-less low dropout regulator with Q-control | |

| US7893670B2 (en) | Frequency compensation scheme for stabilizing the LDO using external NPN in HV domain | |

| US8154263B1 (en) | Constant GM circuits and methods for regulating voltage | |

| US8289009B1 (en) | Low dropout (LDO) regulator with ultra-low quiescent current | |

| CN110096086B (zh) | 电压调节器装置 | |

| US9553548B2 (en) | Low drop out voltage regulator and method therefor | |

| CN110968145B (zh) | 低压降稳压电路及其稳压方法 | |

| US9146570B2 (en) | Load current compesating output buffer feedback, pass, and sense circuits | |

| US9367074B2 (en) | Voltage regulator capable of stabilizing an output voltage even when a power supply fluctuates | |

| CN112925378B (zh) | 快速响应线性稳压器及其快速响应放大电路 | |

| US10067521B2 (en) | Low dropout regulator with PMOS power transistor | |

| CN113467559B (zh) | 一种应用于ldo的自适应动态零点补偿电路 | |

| GB2539457A (en) | Voltage regulators | |

| CN107305399B (zh) | Pmos功率电晶体线性降压稳压电路 | |

| WO2018100378A1 (en) | Voltage regulator | |

| CN110366713A (zh) | 用于补偿低压差线性稳压器的方法和电路系统 | |

| WO2015168497A1 (en) | Current-limiting in an amplifier system | |

| US8576011B2 (en) | Amplifier with high power supply noise rejection | |

| CN117970989A (zh) | 稳压器电路 | |

| Peng et al. | A high current efficiency rail-to-rail buffer for low drop-out regulators with load regulation-enhanced |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |