KR20170093130A - 저전력 연산 트랜스컨덕턴스 증폭기 - Google Patents

저전력 연산 트랜스컨덕턴스 증폭기 Download PDFInfo

- Publication number

- KR20170093130A KR20170093130A KR1020177014796A KR20177014796A KR20170093130A KR 20170093130 A KR20170093130 A KR 20170093130A KR 1020177014796 A KR1020177014796 A KR 1020177014796A KR 20177014796 A KR20177014796 A KR 20177014796A KR 20170093130 A KR20170093130 A KR 20170093130A

- Authority

- KR

- South Korea

- Prior art keywords

- pair

- coupled

- ota

- frequency

- frequency pole

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/08—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements

- H03F1/083—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements in transistor amplifiers

- H03F1/086—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements in transistor amplifiers with FET's

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

- H03F3/45183—Long tailed pairs

- H03F3/45188—Non-folded cascode stages

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/447—Indexing scheme relating to amplifiers the amplifier being protected to temperature influence

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/45—Indexing scheme relating to amplifiers the load of the amplifier being a capacitive element, e.g. CRT

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45024—Indexing scheme relating to differential amplifiers the differential amplifier amplifying transistors are cascode coupled transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45034—One or more added reactive elements, capacitive or inductive elements, to the amplifying transistors in the differential amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45058—Indexing scheme relating to differential amplifiers the cascode stage of the differential amplifier comprising a reactive element

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45194—At least one active load circuit of the two load circuits in a differential amplifier being realised with a combination of more than one transistor

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45296—Indexing scheme relating to differential amplifiers the AAC comprising one or more discrete capacitive elements, e.g. a transistor coupled as capacitor

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45631—Indexing scheme relating to differential amplifiers the LC comprising one or more capacitors, e.g. coupling capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Theoretical Computer Science (AREA)

- Amplifiers (AREA)

Abstract

증폭기(예컨대, 연산 트랜스컨덕턴스 증폭기 또는 OTA)에 관련된 방법 및 장치가 제공된다. OTA는 제 1 노드 및 제 2 노드를 포함한다. OTA는 입력을 수신하기 위한 차동 트랜지스터 쌍을 더 포함한다. 차동 트랜지스터 쌍은 제 1 노드 및 제 2 노드에 커플링된다. OTA는, 입력에 대한 응답을 출력하기 위한 한 쌍의 출력 노드들을 포함한다. 한 쌍의 출력 노드들에서의 응답은 제 1 주파수 폴을 포함한다. 제 1 노드와 제 2 노드 간에 용량성 엘리먼트가 커플링된다. 응답은, 용량성 엘리먼트에 기초한 제 2 주파수 폴을 포함한다. 제 2 주파수 폴은 제 1 주파수 폴보다 더 큰 주파수에 있다.

Description

관련 출원에 대한 상호-참조

[0001]

본 출원은, “LOW POWER OPERATIONAL TRANSCONDUCTANCE AMPLIFIER”라는 명칭으로 2014년 12월 10일자로 출원된 미국 특허 출원 제 14/566,539호를 우선권으로 주장하며, 상기 미국 특허 출원은 그 전체가 인용에 의해 본원에 명백히 통합된다.

[0002]

본 개시내용은 일반적으로 전자 회로들에 관한 것으로, 더 상세하게는, 저전력 연산 트랜스컨덕턴스 증폭기(OTA; operational transconductance amplifier)에 관한 것이다.

[0003]

무선 통신 기술들 및 모바일 전자 디바이스들(예컨대, 셀룰러 폰들, 태블릿들, 랩톱들 등)은 지난 몇 년 동안 대중성이 성장하고 사용이 증가해 왔다. 점차적으로, 모바일 전자 디바이스들은 복잡도가 증가되었고, 이제는 일반적으로, 모바일 디바이스 사용자들이 복잡하고 전력 집약적인 소프트웨어 애플리케이션(예컨대, 웹 브라우저들, 비디오 스트리밍 애플리케이션들 등)들을 실행하는 것을 허용하는 다수의 프로세서들 및 다른 리소스들을 포함한다.

[0004]

모바일 디바이스들에서의 더 많은 프로세싱 능력에 대한 요구가 계속 증가함에 따라, 낮은 전력 소모가 모바일 전자 디바이스들의 컴포넌트들에 대한 공통 설계 요건이 되었다. OTA는 오늘날 무선 기술의 핵심 컴포넌트이다. 예를 들어, 무선 트랜시버는 수신된 아날로그 신호를 디지털화하기 위해 델타-시그마 아날로그-디지털 변환기(ADC; analog-to-digital converter)를 사용할 수 있다. OTA는 그러한 델타-시그마 ADC에 대한 적분기에 대해 사용될 수 있다. 델타-시그마 ADC의 타이밍 요건을 충족시키기 위해, OTA는 많은 전력의 소모를 요구할 수 있다. 통상적으로, OTA는 다른 델타-시그마 ADC 컴포넌트들보다 더 많은 전력을 요구한다.

[0005]

본 개시내용의 양상에서, OTA에 관련된 방법 및 장치가 제공된다. OTA는 제 1 노드 및 제 2 노드를 포함한다. OTA는 입력을 수신하기 위한 차동 트랜지스터 쌍을 더 포함한다. 차동 트랜지스터 쌍은 제 1 노드 및 제 2 노드에 커플링된다. OTA는, 입력에 대한 응답을 출력하기 위한 한 쌍의 출력 노드들을 포함한다. 한 쌍의 출력 노드들에서의 응답은 제 1 주파수 폴(pole)을 포함한다. 제 1 노드와 제 2 노드 간에 용량성(capacitive) 엘리먼트가 커플링된다. 응답은, 용량성 엘리먼트에 기초한 제 2 주파수 폴을 포함한다. 제 2 주파수 폴은 제 1 주파수 폴보다 더 큰 주파수에 있다.

[0006]

도 1은, 예시적인 실시예가 포함될 수 있는 무선 디바이스 및 시스템들을 예시한다.

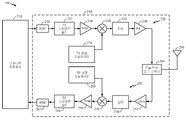

[0007] 도 2는, 예시적인 실시예가 포함될 수 있는 무선 디바이스의 일 부분의 블록도이다.

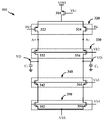

[0008] 도 3은 예시적인 실시예의 OTA를 예시한다.

[0009] 도 4는, 제 2 주파수 폴 커패시터가 없는 OTA를 예시한다.

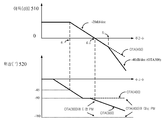

[0010] 도 5는, 제 2 주파수 폴 커패시터를 갖는 OTA와 제 2 주파수 폴 커패시터가 없는 OTA의 응답들을 비교하는 보드 선도(Bode plot)들을 예시한다.

[0011] 도 6은, 위상 마진(margin)들에 기초한 다양한 OTA 응답들을 예시한다.

[0012] 도 7은, 예시적인 실시예의 OTA의 동작들의 흐름도이다.

[0007] 도 2는, 예시적인 실시예가 포함될 수 있는 무선 디바이스의 일 부분의 블록도이다.

[0008] 도 3은 예시적인 실시예의 OTA를 예시한다.

[0009] 도 4는, 제 2 주파수 폴 커패시터가 없는 OTA를 예시한다.

[0010] 도 5는, 제 2 주파수 폴 커패시터를 갖는 OTA와 제 2 주파수 폴 커패시터가 없는 OTA의 응답들을 비교하는 보드 선도(Bode plot)들을 예시한다.

[0011] 도 6은, 위상 마진(margin)들에 기초한 다양한 OTA 응답들을 예시한다.

[0012] 도 7은, 예시적인 실시예의 OTA의 동작들의 흐름도이다.

[0013]

첨부된 도면들과 관련하여 아래에 기재되는 상세한 설명은, 다양한 구성들의 설명으로서 의도되며, 여기에 설명된 개념들이 실시될 수 있는 유일한 구성들만을 표현하도록 의도되지 않는다. 상세한 설명은 다양한 개념들의 철저한 이해를 제공하려는 목적을 위해 특정한 세부사항들을 포함한다. 그러나, 이들 개념들이 이들 특정한 세부사항들 없이도 실시될 수 있다는 것은 당업자들에게 명백할 것이다. 몇몇 예시들에서, 그러한 개념들을 불명료하게 하는 것을 회피하기 위해, 잘 알려진 구조들 및 컴포넌트들은 블록도 형태로 도시되어 있다. 용어 "예시적인"은 "예, 예시, 또는 예증으로서 기능하는 것"을 의미하도록 본원에서 사용된다. "예시적인" 것으로 본원에 설명된 어떠한 설계도 다른 설계들에 비해 반드시 바람직하거나 유리한 것으로서 해석될 필요는 없다.

[0014]

이제 원격통신 시스템들의 여러 양상들이 다양한 장치 및 방법들에 관하여 제시될 것이다. 이러한 장치 및 방법들은 다음의 상세한 설명에서 설명될 것이며 첨부된 도면들에서 (통칭하여 "엘리먼트들"로 지칭되는) 다양한 블록들, 모듈들, 컴포넌트들, 회로들, 단계들, 프로세스들, 알고리즘들 등에 의해 예시될 것이다. 이러한 엘리먼트들은 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이들의 임의의 결합을 사용하여 구현될 수 있다. 그러한 엘리먼트들이 하드웨어로서 구현되는지 또는 소프트웨어로서 구현되는지는 특정 애플리케이션 및 전체 시스템에 부과된 설계 제약들에 의존한다.

[0015]

예로서, 엘리먼트 또는 엘리먼트의 임의의 부분 또는 엘리먼트들의 임의의 결합은 하나 또는 그 초과의 프로세서들을 포함하는 "프로세싱 시스템"으로 구현될 수 있다. 프로세서들의 예들은, 마이크로프로세서들, 마이크로제어기들, 디지털 신호 프로세서(DSP: digital signal processor)들, 필드 프로그래밍가능 게이트 어레이(FPGA: field programmable gate array)들, 프로그래밍가능 로직 디바이스(PLD: programmable logic device)들, 상태 머신들, 게이티드(gated) 로직, 이산 하드웨어 회로들, 및 본 개시내용 전반에 걸쳐 설명되는 다양한 기능을 수행하도록 구성된 다른 적절한 하드웨어를 포함한다. 프로세싱 시스템의 하나 또는 그 초과의 프로세서들은 소프트웨어를 실행할 수 있다. 소프트웨어는, 소프트웨어, 펌웨어, 미들웨어, 마이크로코드, 하드웨어 디스크립션(description) 언어 또는 다른 식으로 지칭되든지 간에, 명령들, 명령 세트들, 코드, 코드 세그먼트들, 프로그램 코드, 프로그램들, 서브프로그램들, 소프트웨어 모듈들, 애플리케이션들, 소프트웨어 애플리케이션들, 소프트웨어 패키지들, 루틴들, 서브루틴들, 오브젝트들, 실행가능한 것(executable)들, 실행 스레드들, 절차들, 함수들 등을 의미하는 것으로 광범위하게 해석될 것이다.

[0016]

따라서, 하나 또는 그 초과의 예시적인 실시예들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 결합으로 구현될 수 있다. 소프트웨어로 구현되는 경우, 기능들은 컴퓨터-판독가능 매체 상에 하나 또는 그 초과의 명령들 또는 코드로서 저장되거나 또는 인코딩될 수 있다. 컴퓨터-판독가능 매체들은 컴퓨터 저장 매체들을 포함한다. 저장 매체들은 컴퓨터에 의해 액세스될 수 있는 임의의 이용가능한 매체들일 수 있다. 제한이 아닌 예로서, 그러한 컴퓨터-판독가능 매체들은 RAM(random-access memory), ROM(read-only memory), EEPROM(electronically erasable programmable ROM), CD(compact disk) ROM(CD-ROM), 또는 다른 광학 디스크 저장부, 자기 디스크 저장 또는 다른 자기 저장 디바이스들, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드를 반송 또는 저장하는데 사용될 수 있고, 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다. 본원에 사용된 바와 같이, 디스크(disk) 및 디스크(disc)는 CD, 레이저 디스크(disc), 광학 디스크(disc), DVD(digital versatile disc), 및 플로피 디스크(disk)를 포함하며, 여기서 디스크(disk)들은 일반적으로 데이터를 자기적으로 재생하지만 디스크(disc)들은 레이저들을 이용하여 데이터를 광학적으로 재생한다. 또한, 상기의 것들의 결합들이 컴퓨터-판독가능 매체들의 범위 내에 포함되어야 한다.

[0017]

도 1은, 예시적인 실시예가 포함될 수 있는 무선 디바이스(예컨대, 무선 디바이스(110)) 및 시스템들(예컨대, 무선 시스템들(120, 122))을 예시한다. 무선 디바이스(110)는 상이한 무선 시스템들(120, 122)과 통신한다. 무선 시스템들(120, 122) 각각은 CDMA(Code Division Multiple Access) 시스템, GSM(Global System for Mobile Communications) 시스템, LTE(Long Term Evolution) 시스템, WLAN(wireless local area network) 시스템, 또는 몇몇 다른 무선 시스템일 수 있다. CDMA 시스템은 광대역 CDMA(WCDMA), CDMA 1X 또는 cdma2000, TD-SCDMA(Time Division Synchronous Code Division Multiple Access), 또는 몇몇 다른 버전의 CDMA를 구현할 수 있다. TD-SCDMA는 또한, 유니버셜 지상 라디오 액세스(UTRA; Universal Terrestrial Radio Access) 시간 분할 듀플렉스(TDD; Time Division Duplex) 1.28 Mcps 옵션 또는 LCR(Low Chip Rate)로 지칭된다. LTE는 주파수 분할 듀플렉싱(FDD) 및 시간 분할 듀플렉싱(TDD) 둘 모두를 지원한다. 예를 들어, 무선 시스템(120)은 GSM 시스템일 수 있고, 무선 시스템(122)은 WCDMA 시스템일 수 있다. 다른 예로서, 무선 시스템(120)은 LTE 시스템일 수 있고, 무선 시스템(122)은 CDMA 시스템일 수 있다.

[0018]

간략화를 위해, 도면(100)은, 하나의 기지국(130) 및 하나의 시스템 제어기(140)를 포함하는 무선 시스템(120), 및 하나의 기지국(132) 및 하나의 시스템 제어기(142)를 포함하는 무선 시스템(122)을 도시한다. 일반적으로, 각각의 무선 시스템은 임의의 개수의 기지국들 및 임의의 세트의 네트워크 엔티티(entity)들을 포함할 수 있다. 각각의 기지국은 그 기지국의 커버리지 내의 무선 디바이스들에 대한 통신을 지원할 수 있다. 기지국들은 또한, Node B, eNB(evolved Node B), 액세스 포인트, 베이스 트랜시버 스테이션, 라디오 기지국, 라디오 트랜시버, 트랜시버 기능부, 기본 서비스 세트(BSS; basic service set), 확장 서비스 세트(ESS; extended service set) 또는 몇몇 다른 적절한 전문용어로 지칭될 수 있다. 무선 디바이스(110)는 또한, 사용자 장비(UE), 모바일 디바이스, 원격 디바이스, 무선 디바이스, 무선 통신 디바이스, 스테이션, 모바일 스테이션, 가입자 스테이션, 모바일 가입자 스테이션, 단말, 모바일 단말, 원격 단말, 무선 단말, 액세스 단말, 클라이언트, 모바일 클라이언트, 모바일 유닛, 가입자 유닛, 무선 유닛, 원격 유닛, 핸드셋, 사용자 에이전트, 또는 몇몇 다른 적절한 전문용어로 지칭될 수 있다. 무선 디바이스(110)는, 셀룰러 폰, 스마트폰, 태블릿, 무선 모뎀, 개인 휴대 정보 단말(PDA), 핸드헬드(handheld) 디바이스, 랩톱 컴퓨터, 스마트북, 넷북, 코드리스(cordless) 폰, 무선 로컬 루프(WLL) 스테이션, 또는 몇몇 다른 유사한 기능 디바이스일 수 있다.

[0019]

무선 디바이스(110)는 무선 시스템(120 및/또는 122)과 통신하는 것이 가능할 수 있다. 무선 디바이스(110)는 또한, 브로드캐스트 스테이션(134)과 같은 브로드캐스트 스테이션들로부터 신호들을 수신하는 것이 가능할 수 있다. 무선 디바이스(110)는 또한, 하나 또는 그 초과의 글로벌 내비게이션 위성 시스템들(GNSS)에서, 위성(150)과 같은 위성들로부터 신호들을 수신하는 것이 가능할 수 있다. 무선 디바이스(110)는, GSM, WCDMA, cdma2000, LTE, 802.11 등과 같은 무선 통신을 위한 하나 또는 그 초과의 라디오 기술들을 지원할 수 있다. 용어 "라디오 기술", "라디오 액세스 기술", "에어(air) 인터페이스" 및 "표준"은 상호교환가능하게 사용될 수 있다.

[0020]

무선 디바이스(110)는, 다운링크 및 업링크를 통해 무선 시스템 내의 기지국과 통신할 수 있다. 다운링크(또는 순방향 링크)는 기지국으로부터 무선 디바이스로의 통신 링크를 지칭하고, 업링크(또는 역방향 링크)는 무선 디바이스로부터 기지국으로의 통신 링크를 지칭한다. 무선 시스템은 TDD 및/또는 FDD를 활용할 수 있다. TDD의 경우, 다운링크 및 업링크는 동일한 주파수를 공유하고, 다운링크 송신들 및 업링크 송신들은 상이한 시간 기간들에서 동일한 주파수를 통해 전송될 수 있다. FDD의 경우, 다운링크 및 업링크에는 별개의 주파수들이 할당된다. 다운링크 송신들은 하나의 주파수를 통해 전송될 수 있고, 업링크 송신들은 다른 주파수를 통해 전송될 수 있다. TDD를 지원하는 몇몇 예시적인 라디오 기술들은 GSM, LTE, 및 TD-SCDMA를 포함한다. FDD를 지원하는 몇몇 예시적인 라디오 기술들은 WCDMA, cdma2000, 및 LTE를 포함한다.

[0021]

도 2는, 예시적인 실시예가 포함될 수 있는 무선 디바이스(예컨대, 무선 디바이스(110))의 일 부분의 블록도이다. 무선 트랜시버(218)는, 양-방향 통신을 지원하는 송신기(220) 및 수신기(250)를 포함한다. 송신기(220) 및/또는 수신기(250)는, 슈퍼-헤테로다인(super-heterodyne) 아키텍쳐 또는 직접-변환 아키텍쳐로 구현될 수 있다. 슈퍼-헤테로다인 아키텍쳐에서, 신호는 다수의 스테이지들에서 RF와 기저대역 사이에서 주파수-변환된다(예컨대, 수신기의 경우, 하나의 스테이지에서 RF로부터 중간 주파수(IF; intermediate frequency)로, 그리고 그 후 다른 스테이지에서 IF로부터 기저대역으로 주파수-변환됨). 제로-IF(zero-IF) 아키텍쳐로 또한 지칭되는 직접-변환 아키텍쳐에서, 신호는 하나의 스테이지에서 RF와 기저대역 사이에서 주파수 변환된다. 슈퍼-헤테로다인 및 직접-변환 아키텍쳐들은, 상이한 회로 블록들을 사용하고 그리고/또는 상이한 요건들을 가질 수 있다. 도 2에 도시된 예시적인 실시예에서, 송신기(220) 및 수신기(250)는 직접-변환 아키텍쳐를 이용하여 구현된다.

[0022]

송신 경로에서, 기저대역 프로세서(210)는 디지털-아날로그 변환기(DAC; digital-to-analog converter)(230)에 데이터를 제공한다. DAC(230)는 디지털 입력 신호를 아날로그 출력 신호로 변환한다. 아날로그 출력 신호는 필터(232)에 제공되고, 필터(232)는, DAC(230)에 의한 앞선 디지털-아날로그 변환에 의해 야기되는 이미지(image)들을 제거하기 위해 아날로그 출력 신호를 필터링한다. 증폭기(234)는, 필터(232)로부터의 신호를 증폭하여 증폭된 기저대역 신호를 제공하기 위해 사용된다. 믹서(236)는 증폭된 기저대역 신호, 및 TX 로컬 오실레이터(local oscillator)(276)로부터의 LO 신호를 수신한다. 믹서(236)는 증폭된 기저대역 신호를 LO 신호와 믹싱하여 상향변환된 신호를 제공한다. 필터(238)는, 주파수 믹싱에 의해 야기되는 이미지들을 제거하기 위해, 상향변환된 신호를 필터링하는데 사용된다. 전력 증폭기(PA)(240)는, 원하는 출력 전력 레벨의 출력 RF 신호를 획득하기 위해, 필터(238)로부터의 신호를 증폭하기 위해 사용된다. 출력 RF 신호는, 무선 채널을 통한 송신을 위해, 듀플렉서(264)를 통해 안테나(290)로 라우팅(route)된다.

[0023]

수신 경로에서, 안테나(290)는 원격 디바이스에 의해 송신되는 신호들을 수신할 수 있다. 수신된 RF 신호는 듀플렉서(264)를 통해 수신기(250)로 라우팅될 수 있다. 수신기(250) 내에서, 수신된 RF 신호가 저잡음 증폭기(LNA; low noise amplifier)(252)에 의해 증폭되고 필터(254)에 의해 필터링되어, 입력 RF 신호가 획득된다. 믹서(256)는 입력 RF 신호, 및 RX 로컬 오실레이터(286)로부터의 LO 신호를 수신한다. 믹서(256)는 입력 RF 신호를 LO 신호와 믹싱하여 하향변환된 신호를 제공한다. 하향변환된 신호가 증폭기(258)에 의해 증폭되어, 증폭된 하향변환된 신호가 획득된다. 필터(260)는, 주파수 믹싱에 의해 야기되는 이미지들을 제거하기 위해, 증폭된 하향변환된 신호를 필터링하는데 사용된다. 필터(260)로부터의 신호는 ADC(262)에 제공된다. ADC(262)는 그 신호를 디지털 출력 신호로 변환한다. 디지털 출력 신호는 추가적인 프로세싱을 위해 기저대역 프로세서(210)에 제공될 수 있다. ADC(262)는, 적분 기능을 수행하는 OTA의 예시적인 실시예를 포함하는 델타-시그마 타입 ADC일 수 있다.

[0024]

송신기(220) 및 수신기(250)에서 신호들을 컨디셔닝(condition)하는 것은, 증폭기들, 필터들, 믹서들 등의 하나 또는 그 초과의 스테이지들에 의해 수행될 수 있다. 이들 회로들은 도 2에 도시된 구성과 상이하게 배열될 수 있다. 뿐만 아니라, 도 2에 도시되지 않은 다른 회로들이 또한 송신기(220) 및 수신기(250)에서 신호들을 컨디셔닝하는데 사용될 수 있다. 예를 들어, PA(240)의 출력, LNA(252)의 입력, 안테나(290)와 듀플렉서(264) 사이 등에 임피던스 매칭 회로들이 로케이팅될 수 있다.

[0025]

도 3은 예시적인 실시예의 OTA(예컨대, OTA(300))를 예시한다. OTA(300)는, 노드들 IN+ 및 IN-에서 차동 입력을 수신하고 노드들 VO+ 및 VO-에서 차동 출력을 출력하는, 단일 스테이지의 텔레스코픽 캐스코드(telescopic cascode) 연산 증폭기일 수 있다. OTA는 차동 입력을 수신하기 위한 차동 트랜지스터 쌍(320)을 포함한다. 차동 트랜지스터 쌍(320)은 P-타입 금속-산화물-반도체(PMOS) 트랜지스터들(322 및 324)을 포함한다. 일 예에서, 차동 트랜지스터 쌍(320)은 (차동) 입력을 수신하기 위한 입력 수단을 제공한다. 차동 트랜지스터 쌍(320)은 PMOS 트랜지스터(310)에 커플링(예컨대, 전기적으로 연결)되며, PMOS 트랜지스터(310)는 공급 전압 VDD에 커플링되어 OTA(300)에 전류를 제공한다. PMOS 트랜지스터(310)의 게이트는 기준 전압 Vb1에 커플링된다. PMOS 트랜지스터(322)의 게이트는 노드 IN+로부터 입력을 수신한다. PMOS 트랜지스터(322)의 드레인은 노드 A+에 커플링된다. PMOS 트랜지스터(324)의 게이트는 노드 IN-로부터 입력을 수신한다. PMOS 트랜지스터(324)의 드레인은 노드 A-에 커플링된다. 따라서, 차동 트랜지스터 쌍(320)은 노드들 A+ 및 A+에 커플링되거나 또는 전기적으로 연결된다. 노드들(예컨대, A+ 및 A-; N+ 및 N-)의 예는 차동 트랜지스터 쌍(320)과 제 1 캐스코드 쌍(330)을 연결하는 전도성 부분들(금속, 폴리실리콘 등)을 포함할 수 있다.

[0026]

용량성 엘리먼트(예컨대, 제 2 주파수 폴 커패시터 CX)가 노드들 A+ 및 A-에 커플링(예컨대, 전기적으로 연결)된다. 일 예에서, 제 2 주파수 폴 커패시터 CX의 커패시턴스는 100 fF 내지 200 fF의 범위에 있다. 차동 트랜지스터 쌍(320)은 추가로, 노드들 A+ 및 A-에서 제 1 캐스코드 쌍(330)에 커플링된다. 제 1 캐스코드 쌍(330)은 PMOS 트랜지스터들(332 및 334)을 포함한다. PMOS 트랜지스터(332)는 노드 A+ 및 출력 노드 VO+에 커플링된다. PMOS 트랜지스터(334)는 노드 A- 및 출력 노드 VO-에 커플링된다. PMOS 트랜지스터들(332 및 334)의 게이트들 둘 모두는 기준 전압 Vb2에 커플링된다. 출력 노드들 VO+ 및 VO- 각각은 로드(load) 커패시터 CL에 커플링된다. 일 예에서, 출력 노드들 VO+ 및 VO-는 OTA(300)의 응답을 출력하기 위한 출력 수단을 제공한다. 출력 노드들 VO+ 및 VO-의 예들은 제 1 캐스코드 쌍(330)과 제 2 캐스코드 쌍(340)을 연결하는 전도성 부분들(금속, 폴리실리콘 등)을 포함할 수 있다.

[0027]

OTA(300)의 로드는, 출력 노드들 VO+ 및 VO-에 커플링(예컨대, 전기적으로 연결)되는 저항기 또는 적어도 하나의 전류 소스(예컨대, 제 2 캐스코드 쌍(340) 및 전류 소스 쌍(350))를 포함할 수 있다. 제 2 캐스코드 쌍(340)은, 출력 노드 VO+에 커플링되는 N-타입 금속-산화물-반도체(NMOS) 트랜지스터(342) 및 출력 노드 VO-에 커플링되는 NMOS 트랜지스터(344)를 포함한다. NMOS 트랜지스터들(342 및 344)의 게이트들은 기준 전압 Vb3에 커플링된다. 전류 소스 쌍(350)은, (NMOS 트랜지스터(342)를 통해) 출력 노드 VO+에 커플링되는 NMOS 트랜지스터(352) 및 (NMOS 트랜지스터(344)를 통해) 출력 노드 VO-에 커플링되는 NMOS 트랜지스터(354)를 포함한다. NMOS 트랜지스터들(352 및 354)의 게이트들은 기준 전압 Vb4에 커플링된다. 제 2 캐스코드 쌍(340) 및 전류 소스 쌍(350)은 VSS에 커플링되며, VSS는 접지(GND)일 수 있다. 따라서, 일 예에서, 제 2 캐스코드 쌍(340) 및/또는 전류 소스 쌍(350)은, 차동 트랜지스터 쌍(320) 및 출력 노드들 VO+ 및 VO-를 통해 전류들을 흐르게 하기 위한 수단을 제공한다.

[0028]

기준 전압들 Vb1, Vb2, Vb3, 및 Vb4는 OTA(300)를 통해 흐르는 바이어스 전류를 제어하도록 구성되고, 당업계의 알려져 있는 전압 생성기들을 이용하여 생성될 수 있다. 당업자들에 의해 이해될 바와 같이, OTA(300)의 트랜지스터들의 타입들은 반전될 수 있다(예컨대, 차동 트랜지스터 쌍(320)은 NMOS 트랜지스터들일 수 있고, 로드는 PMOS 캐스코드 쌍들일 수 있음).

[0029]

OTA(300)의 일 양상에서, 제 2 주파수 폴 커패시터 CX는 OTA(300)의 응답에 제 2 주파수 폴을 도입시킨다. 따라서, OTA(300)는, 자신의 응답에서 제 1 주파수 폴 및 제 2 주파수 폴을 갖는 단일-스테이지의 텔레스코픽 캐스코드 OTA이다. 비교를 위해, 도 4는, 제 2 주파수 폴 커패시터가 CX가 없는 OTA(400)를 예시한다. 일 예에서, OTA(400)는, 제 2 주파수 폴 커패시터 CX의 결여를 제외하고는 OTA(300)와 동일하다. OTA(400)는, 자신의 응답에서 단일 폴을 갖는 단일 스테이지의 텔레스코픽 캐스코드 OTA이다. OTA(300)가 OTA(400)와의 비교에서 설명될 것이다.

[0030]

도 3을 참조하면, 예시적인 실시예의 OTA는 제 1 노드(예컨대, A+) 및 제 2 노드(예컨대, A-)를 포함할 수 있다. 예시적인 실시예의 OTA는 입력을 수신하기 위한 차동 트랜지스터 쌍(예컨대, 320)을 포함할 수 있다. 차동 트랜지스터 쌍은 제 1 노드(예컨대, A+) 및 제 2 노드(예컨대, A-)에 커플링된다. 예를 들어, 차동 트랜지스터 쌍(320)은 PMOS 트랜지스터들(322 및 324)을 포함할 수 있다. PMOS 트랜지스터들(322 및 324)은 노드들 IN+ 및 IN-에서 입력을 수신한다. PMOS 트랜지스터(322)의 드레인은 제 1 노드(노드 A+)에 연결되고, PMOS 트랜지스터(324)의 드레인은 제 2 노드(노드 A-)에 연결된다. 예시적인 실시예의 OTA는, 입력에 대한 응답을 출력하기 위한 한 쌍의 출력 노드들(예컨대, VO+ 및 VO-)을 더 포함할 수 있다. 한 쌍의 출력 노드들에서의 응답은 제 1 주파수 폴을 포함한다. 예컨대, 주파수 f1에서 도 5를 참조한다(아래에 설명됨). 예시적인 실시예의 OTA는, 제 1 노드(A+)와 제 2 노드(A-) 사이에 커플링되는 용량성 엘리먼트(예컨대, 제 2 주파수 폴 커패시터 CX)를 더 포함할 수 있다. 예시적인 실시예의 OTA의 응답은 제 2 주파수 폴을 포함할 수 있으며, 이는 용량성 엘리먼트의 함수이다. 제 2 주파수 폴(주파수 f2)은 제 1 주파수 폴(주파수 f1)보다 더 큰 주파수에 있다. 예컨대, 아래에 설명되는 도 5의 주파수 f2를 참조한다.

[0031]

예시적인 실시예의 OTA는 한 쌍의 출력 노드들(VO+ 및 VO-)에 커플링되는 적어도 하나의 용량성 로드를 더 포함할 수 있다. 예컨대, 출력 노드들 VO+ 및 VO-에 연결되는 로드 커패시터들 CL을 참조한다. 제 2 주파수 폴(주파수 f2)은 적어도 하나의 용량성 로드의 함수이다(도 2 및 아래의 첨부된 설명을 참조함). 예시적인 실시예의 OTA는 한 쌍의 출력 노드들(VO+ 및 VO-)에 커플링되는 캐스코드 트랜지스터 쌍(예컨대, 330)을 더 포함할 수 있다. 한 쌍의 출력 노드들은 캐스코드 트랜지스터 쌍을 통해 차동 트랜지스터 쌍에 커플링된다. 예를 들어, 캐스코드 트랜지스터 쌍(330)은 PMOS 트랜지스터들(332 및 334)을 포함한다. PMOS 트랜지스터(332)의 드레인은 출력 노드 VO+에 연결되고, PMOS 트랜지스터(334)의 드레인은 출력 노드 VO-에 연결된다. 출력 노드들 VO+ 및 VO-는 캐스코드 트랜지스터 쌍(330)을 통해 차동 트랜지스터 쌍(320)에 연결된다. 차동 트랜지스터 쌍(320) 및 캐스코드 트랜지스터 쌍(330)은 제 1 타입의 MOS 트랜지스터들(예컨대, PMOS 트랜지스터들)을 포함할 수 있다.

[0032]

예시적인 실시예의 OTA는 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍(예컨대, 340)을 더 포함할 수 있다. 제 2 캐스코드 트랜지스터 쌍은 제 2 타입의 MOS 트랜지스터들(예컨대, NMOS 트랜지스터들)을 포함한다. 예를 들어, 제 2 캐스코드 트랜지스터 쌍(340)은 NMOS 트랜지스터들(342 및 344)을 포함한다. NMOS 트랜지스터(342)의 드레인은 캐스코드 트랜지스터 쌍(330)의 PMOS 트랜지스터(332)의 드레인에 연결되고, NMOS 트랜지스터(344)의 드레인은 캐스코드 트랜지스터 쌍(330)의 PMOS 트랜지스터(334)의 드레인에 연결된다. 또한, 예시적인 실시예의 OTA에서, 용량성 엘리먼트(예컨대, 제 2 주파수 폴 커패시터 CX) 및 적어도 하나의 용량성 로드(예컨대, CL)는 동일한 타입의 커패시터들을 포함한다. 예를 들어, 제 2 주파수 폴 커패시터 CX 및 용량성 로드 CL 둘 모두는 금속-절연체-반도체 커패시터들을 포함할 수 있다.

[0033]

예시적인 실시예의 OTA는, 응답의 위상 마진이 대략적으로 40° - 90°이도록, 응답의 이득, 용량성 엘리먼트의 커패시턴스, 및 적어도 하나의 용량성 로드의 커패시턴스를 더 포함할 수 있다(아래의 도 5의 설명 참조). 예시적인 실시예의 OTA는 추가로, 시그마-델타 아날로그-디지털 변환의 적분 기능을 수행할 수 있다. 예를 들어, ADC(262)는 시그마-델타 ADC일 수 있고, 적분 기능을 수행하는 예시적인 실시예의 OTA를 포함한다. 또한, 예시적인 OTA는 도 3에 도시된 바와 같이 단일 스테이지 OTA일 수 있다.

[0034]

도 3을 참조하면, 예시적인 실시예의 OTA는 차동 트랜지스터 쌍에서 입력을 수신하기 위한 수단을 포함할 수 있다. 그러한 수단은, 예를 들어, 노드들 A+ 및 A-를 포함할 수 있다. 예시적인 실시예의 OTA는 한 쌍의 출력 노드들(예컨대, VO+ 및 VO-)을 통해 전류들을 흐르게 하기 위한 수단을 더 포함할 수 있다. 용량성 엘리먼트(예컨대, CL)는 한 쌍의 출력 노드들에 커플링된다. 예를 들어, 그러한 수단은, 노드들 A+ 및 A-를 통해 전류들을 흐르게 하도록 동작하는 PMOS 트랜지스터(310)를 포함할 수 있다. 예시적인 실시예의 OTA는, 한 쌍의 출력 노드들에서, 제 1 주파수 폴 및 제 2 주파수 폴을 갖는 응답을 출력하기 위한 수단을 더 포함할 수 있다. 제 2 주파수 폴은 용량성 엘리먼트의 함수이고, 제 2 주파수 폴은 제 1 주파수 폴보다 더 큰 주파수에 있다. 예를 들어, 제 2 주파수 폴 CX는, 한 쌍의 출력 노드들 VO+ 및 VO-에서, (주파수 f1에서) 제 1 주파수 폴을 그리고 (주파수 f2에서) 제 2 주파수 폴을 갖는 응답을 출력하도록 동작한다. 도 5 및 아래의 첨부된 설명을 참조한다. (주파수 f2에 있는) 제 2 주파수 폴은 용량성 엘리먼트 CX의 함수이고 CX, (주파수 f2에 있는) 제 2 주파수 폴은 (주파수 f1에 있는) 제 1 주파수 폴보다 더 큰 주파수에 있다.

[0035]

예시적인 실시예의 OTA는, 한 쌍의 출력 노드들(예컨대, VO+ 및 VO-)에 커플링되는 캐스코드 트랜지스터 쌍(예컨대, 330)을 통해 전류들을 흐르게 하기 위한 수단을 더 포함할 수 있다. 한 쌍의 출력 노드들은 캐스코드 트랜지스터 쌍을 통해 차동 트랜지스터 쌍에 커플링된다. 예를 들어, 그러한 수단은, 기준 전압 Vb2를 캐스코드 트랜지스터 쌍(330)에 제공하기 위한 연결을 포함할 수 있다. 기준 전압 Vb2를 제공하는 연결은, 캐스코드 트랜지스터 쌍(330)을 통해 전류들을 흐르게 한다. 예시적인 실시예의 OTA는 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍(예컨대, 340)을 통해 전류들을 흐르게 하기 위한 수단을 더 포함할 수 있다. (제 2) 캐스코드 트랜지스터 쌍(340)은 제 2 타입의 MOS 트랜지스터들(예컨대, NMOS)을 포함한다. 그러한 수단은, 기준 전압 Vb3을 캐스코드 트랜지스터 쌍(340)에 제공하기 위한 연결을 포함할 수 있다. 기준 전압 Vb3을 제공하는 연결은, 캐스코드 트랜지스터 쌍(340)을 통해 전류들을 흐르게 한다. 예시적인 실시예의 OTA는 추가로, 시그마-델타 아날로그-디지털 변환의 적분 기능을 수행하기 위한 수단을 포함할 수 있다. 예를 들어, ADC(262)는 OTA(300)를 포함하는 시그마-델타 ADC일 수 있다. ADC(262) 내의 OTA(300)에 대한 연결들은, 시그마-델타 아날로그-디지털 변환의 적분 기능을 수행하기 위한 수단을 제공한다.

[0036]

도 5는, 제 2 주파수 폴 커패시터를 갖는 OTA(300)와 제 2 주파수 폴 커패시터가 없는 OTA(400)의 응답들을 비교하는 보드 선도들을 예시한다. 플롯(510)은, 주파수 대 응답들의 이득들(데시벨 또는 dB 단위)을 예시한다. 플롯(520)은, 주파수 대 응답들의 위상들(°단위)을 예시한다. 제 1 폴 주파수 f1에서, 이득은 -20dB/dec의 기울기로 감소하기 시작한다. 위상은 -45°에 있다. 일 예에서, 제 1 주파수 폴은 트랜스컨덕턴스의 함수 이다. 다른 예에서, 제 1 주파수 폴은 이며, 여기서, ROUT은 예에서의 OTA(300)의 출력 저항이다. 트랜스컨덕턴스 gm은 OTA(300)의 응답의 이득의 예이다. 단위 이득(unity gain) 주파수 fUG에서, 이득은 0dB(단위 이득)에 있다. 단일-폴형(single-poled) OTA(400)의 경우, 이득은 -20dB/dec의 기울기로 계속 감소하고, 위상은 -90°에서 안정화된다. 따라서, OTA(400)의 위상 마진은 90°(-90°와 -180°의 위상들 간의 차이)에 있다. OTA(300)의 경우, 응답에서의 제 2 주파수 폴은 주파수 f2에서 발생한다. 이득은 기울기가 -40dB/dec로 변경된다. 일 예에서, 제 2 주파수 폴은 트랜스컨덕턴스의 함수 이다. OTA(300)의 위상 마진은 주파수 fUG에서 측정될 수 있다. 주파수 fUG에서, 위상 마진은 -180°에 대한 OTA(300)의 위상에서의 차이이며, 이는 90°미만이다. 일 예에서, OTA(300)의 위상 마진은 70°내지 90°이며, 여전히 성능 요건(예컨대, 응답 시간)을 충족시킨다. 예시된 바와 같이, OTA(300)의 응답은 f1에서 제 1 주파수 폴을 그리고 f2에서 제 2 주파수 폴을 포함하며, f2는 f1보다 더 큰 주파수에 있다.

[0037]

제 2 주파수 폴 커패시터 CX에 의해 도입되는 제 2 주파수 폴의 특징들 중 하나는 도 5에 도시된 감소된 위상 마진일 수 있다. 도 6은 위상 마진들에 기초한 다양한 OTA 응답들을 예시한다. 도면(610)은 입력이다. 도면들(620-640)은 다양한 위상 마진들에서의 응답들이며, 링잉(ringing)이 없는 응답들이 점선들로 도시된다. 도면(620)은 45°의 위상 마진에서의, 도면(610)에 도시된 입력에 대한 응답이다. OTA(300)의 응답의 예는 도면(620)과 유사할 수 있다. 도면(630)은 70°의 위상 마진에서의, 도면(610)에 도시된 입력에 대한 응답이다. OTA(300)의 응답의 예는 도면(630)과 유사할 수 있다. 도면(640)은 90°의 위상 마진에서의, 도면(610)에 도시된 입력에 대한 응답이다. 따라서, OTA(400)의 응답은 도면(640)과 유사할 수 있다. 도면들(610-640)에 도시된 바와 같이, 위상 마진이 감소함에 따라 응답 시간이 개선된다. 그러나, 응답들에서의 링잉이 증가하고, 이는, 링잉이 없는 응답에 비해 증가된 에러를 초래한다. 일 예에서, 40°내지 90°의 위상 마진에서의 OTA(300)는 OTA(400)보다 더 고속의 응답 시간을 갖는다. 따라서, OTA(300)의 동작 전류는 전력 절감을 달성하기 위해 감소될 수 있으며, 여전히 성능 요건을 충족시킨다.

[0038]

일 예에서, 제 2 주파수 폴 커패시터 CX의 값은, OTA(300)의 트랜스컨덕턴스 gm, 로드 커패시터 CL의 값, 및 위상 마진의 함수일 수 있다. 제 2 주파수 폴 커패시터 CX의 부가는 위상 마진에 크기 영향을 미치지 않을 수 있다. 따라서, OTA(300)의 일 특징은, 로드 커패시터 CL(그에 따라 트랜스컨덕턴스 gm) 및 제 2 주파수 폴 커패시터 CX의 값들을 조정함으로써 위상 마진이 비교적 용이하게 결정 및 조정될 수 있음을 제공한다. 제 2 주파수 폴 커패시터 CX 및 로드 커패시터 CL은 동일한 타입의 커패시터들일 수 있다. 예를 들어, 이들 둘 모두는 금속-절연체-금속 커패시터들일 수 있다. 이러한 방식에서, 코너(corner) 조건들(예컨대, 전압 및 온도 코너들)에 걸쳐 동일한 위상 마진이 유지될 수 있는데, 이는, 둘 모두의 주파수 폴들이 동일한 타입의 커패시터들에 의해 좌우되기 때문이다.

[0039]

OTA(300)의 응답은 다음과 같이 설명될 수 있다.

여기서, 대역폭 BW는 대략적으로 gm과 CL의 비이다. 일 예에서, 위상 마진은 70°를 목표로 하고, CX는 100fF - 200fF으로 셋팅된다. 응답에서의 에러는 다음과 같다.

여기서, errnorm은 실제의 응답과 이상적 응답(예컨대, 링잉 없는 응답) 간의 차이이고, t는 시간이다.

[0040]

제 2 주파수 폴 커패시터 CX의 부가는, 슬루-레이트(slew-rate), 잡음, 선형성, CMRR(common-mode rejection ratio), 및 PSRR(power supply rejection ratio)과 같은 OTA(300)의 다른 파라미터들에 크게 영향을 미치지 않을 수 있다. 비교를 위해, 제 2 주파수 폴 커패시터 CX가 없는 OTA(400)의 응답은 다음과 같이 설명될 수 있다.

여기서, BW는 OTA(400)의 대역폭이다. 일 예에서, 위상 마진은 90°를 목표로 한다. 응답에서의 에러는 다음과 같다.

여기서, errnorm은 실제의 응답과 이상적 응답 간의 차이이고, t는 시간이다.

[0041]

도 7은 예시적인 실시예의 OTA(예컨대, OTA(300))의 동작들의 흐름도(700)이다. 점선들로 도시된 단계들은 선택적일 수 있다. 702에서, 차동 트랜지스터 쌍(예컨대, 도 3의 (320))에서 입력이 수신된다. 704에서, 한 쌍의 출력 노드들(예컨대, 도 3의 VO+ 및 VO-)을 통해 전류들이 흐르게 된다. 용량성 엘리먼트(예컨대, 도 3의 CX)가 한 쌍의 출력 노드들에 커플링된다. 706에서, 한 쌍의 출력 노드들에서 응답이 출력된다. 응답은 (예컨대, 도 5의 f1 및 f2에서) 제 1 주파수 폴 및 제 2 주파수 폴을 갖는다. 제 2 주파수 폴은 용량성 엘리먼트의 함수이다. 제 2 주파수 폴은 제 1 주파수 폴보다 더 큰 주파수에 있다. 708에서, 한 쌍의 출력 노드들에 커플링된 캐스코드 트랜지스터 쌍(예컨대, 도 3의 (330))을 통해 전류들이 흐르게 된다. 한 쌍의 출력 노드들은 캐스코드 트랜지스터 쌍을 통해 차동 트랜지스터 쌍에 커플링된다. 710에서, 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍(예컨대, 도 3의 (340))을 통해 전류들이 흐르게 된다. 716에서, 수신된 입력이 적분된다. 718에서, 적분에 기초하여 시그마-델타 아날로그-디지털 변환(예컨대, 도 2의 ADC(262))이 수행된다. 이들 단계들의 예들은 도 2-6 및 첨부된 설명과 함꼐 설명된다.

[0042]

개시된 프로세스들의 단계들의 특정 순서 또는 계층 구조는 예시적인 접근법들의 예시라는 것을 이해한다. 설계 선호도들을 기초하여, 프로세스들의 단계들의 특정 순서 또는 계층 구조는 재배열될 수도 있음을 이해한다. 추가로, 몇몇 단계들은 결합되거나 또는 생략될 수 있다. 첨부한 방법 청구항들은 다양한 단계들의 엘리먼트들을 예시적인 순서로 제시하며, 제시된 특정 순서 또는 계층 구조로 한정되는 것으로 여겨지는 것은 아니다.

[0043]

이전의 설명은 임의의 당업자가 본원에 설명된 다양한 양상들을 실시할 수 있도록 제공된다. 이들 양상들에 대한 다양한 변형들은 당업자들에게는 용이하게 명백할 것이며, 본원에 정의된 일반적인 원리들은 다른 양상들에 적용될 수 있다. 따라서, 청구항들은 본원에 설명된 양상들로 제한되도록 의도되는 것이 아니라, 청구항들의 문언에 부합하는 최대 범위를 부여하려는 것이며, 여기서, 단수형의 엘리먼트에 대한 참조는 특정하게 그렇게 나타내지 않으면 "하나 및 오직 하나"를 의미하기보다는 오히려 "하나 또는 그 초과"를 의미하도록 의도된다. 달리 특정하게 나타내지 않으면, 용어 "몇몇"은 하나 또는 그 초과를 지칭한다. 당업자들에게 알려져 있거나 추후에 알려지게 될 본 개시내용 전반에 걸쳐 설명된 다양한 양상들의 엘리먼트들에 대한 모든 구조적 및 기능적 균등물들은, 인용에 의해 본원에 명백히 포함되고, 청구항들에 의해 포함되도록 의도된다. 또한, 본원에 개시된 어떠한 것도, 청구항들에 이러한 개시내용이 명시적으로 언급되어 있는지 여부와 관계없이, 공중이 사용하도록 의도되는 것은 아니다. 어떤 청구항 엘리먼트도, 그 엘리먼트가 어구 "하기 위한 수단"을 사용하여 명백히 언급되지 않는 한, 수단 + 기능으로서 해석되지 않아야 한다.

Claims (26)

- 연산 트랜스컨덕턴스 증폭기(OTA; operational transconductance amplifier)로서,

제 1 노드 및 제 2 노드;

입력을 수신하기 위한 차동 트랜지스터 쌍 ― 상기 차동 트랜지스터 쌍은 상기 제 1 노드 및 상기 제 2 노드에 커플링됨 ―;

상기 입력에 대한 응답을 출력하기 위한 한 쌍의 출력 노드들 ― 상기 한 쌍의 출력 노드들에서의 상기 응답은 제 1 주파수 폴(pole)을 포함함 ―;

상기 제 1 노드와 상기 제 2 노드 사이에 커플링되는 용량성(capacitive) 엘리먼트를 포함하며,

상기 응답은 제 2 주파수 폴을 포함하고, 상기 제 2 주파수 폴은 상기 용량성 엘리먼트에 의해 도입되고, 상기 제 2 주파수 폴은 상기 제 1 주파수 폴보다 더 큰 주파수에 있고, 상기 제 2 주파수 폴에서의 이득은 0 미만인, 연산 트랜스컨덕턴스 증폭기. - 제 1 항에 있어서,

상기 한 쌍의 출력 노드들에 커플링되는 적어도 하나의 용량성 로드(load)를 더 포함하며,

상기 제 2 주파수 폴은 상기 적어도 하나의 용량성 로드의 함수인, 연산 트랜스컨덕턴스 증폭기. - 제 2 항에 있어서,

상기 한 쌍의 출력 노드들에 커플링되는 캐스코드 트랜지스터 쌍을 더 포함하며,

상기 한 쌍의 출력 노드들은 상기 캐스코드 트랜지스터 쌍을 통해 상기 차동 트랜지스터 쌍에 커플링되는, 연산 트랜스컨덕턴스 증폭기. - 제 3 항에 있어서,

상기 차동 트랜지스터 쌍 및 상기 캐스코드 트랜지스터 쌍은 제 1 타입의 금속 산화물 반도체(MOS; metal oxide semiconductor) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 4 항에 있어서,

상기 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍을 더 포함하며,

상기 제 2 캐스코드 트랜지스터 쌍은 제 2 타입의 금속 산화물 반도체(MOS) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 2 항에 있어서,

상기 용량성 엘리먼트 및 상기 적어도 하나의 용량성 로드는 동일한 타입의 커패시터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 2 항에 있어서,

상기 응답의 이득, 상기 용량성 엘리먼트의 커패시턴스, 및 상기 적어도 하나의 용량성 로드의 커패시턴스는, 상기 응답의 위상 마진이 대략적으로 40°- 90°이도록 구성되는, 연산 트랜스컨덕턴스 증폭기. - 제 1 항에 있어서,

상기 OTA는 시그마-델타 아날로그-디지털(sigma-delta analog-to-digital) 변환의 적분 기능을 수행하도록 구성되는, 연산 트랜스컨덕턴스 증폭기. - 제 1 항에 있어서,

상기 OTA는 단일 스테이지인, 연산 트랜스컨덕턴스 증폭기. - 연산 트랜스컨덕턴스 증폭기(OTA)를 위한 방법으로서,

차동 트랜지스터 쌍에서 입력을 수신하는 단계;

한 쌍의 출력 노드들을 통해 전류들을 흐르게 하는 단계 ― 상기 한 쌍의 출력 노드들에 용량성 엘리먼트가 커플링됨 ―; 및

상기 한 쌍의 출력 노드들에서, 제 1 주파수 폴 및 제 2 주파수 폴을 갖는 응답을 출력하는 단계를 포함하며,

상기 제 2 주파수 폴은 상기 용량성 엘리먼트에 의해 도입되고, 상기 제 2 주파수 폴은 상기 제 1 주파수 폴보다 더 큰 주파수에 있고, 상기 제 2 주파수 폴에서의 이득은 0 미만인, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 10 항에 있어서,

상기 제 2 주파수 폴은 상기 한 쌍의 출력 노드들에 커플링되는 적어도 하나의 용량성 로드의 함수인, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 11 항에 있어서,

상기 한 쌍의 출력 노드들에 커플링되는 캐스코드 트랜지스터 쌍을 통해 전류들을 흐르게 하는 단계를 더 포함하며,

상기 한 쌍의 출력 노드들은 상기 캐스코드 트랜지스터 쌍을 통해 상기 차동 트랜지스터 쌍에 커플링되는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 12 항에 있어서,

상기 차동 트랜지스터 쌍 및 상기 캐스코드 트랜지스터 쌍은 제 1 타입의 금속 산화물 반도체(MOS) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 13 항에 있어서,

상기 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍을 통해 전류들을 흐르게 하는 단계를 더 포함하며,

상기 제 2 캐스코드 트랜지스터 쌍은 제 2 타입의 금속 산화물 반도체(MOS) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 11 항에 있어서,

상기 용량성 엘리먼트 및 상기 적어도 하나의 용량성 로드는 동일한 타입의 커패시터들을 포함하는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 11 항에 있어서,

상기 응답의 이득, 상기 용량성 엘리먼트의 커패시턴스, 및 상기 적어도 하나의 용량성 로드의 커패시턴스는, 상기 응답의 위상 마진이 대략적으로 40°- 90°이도록 구성되는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 제 10 항에 있어서,

입력을 적분하는 단계; 및

상기 적분에 기초하여 시그마-델타 아날로그-디지털 변환을 수행하는 단계를 더 포함하는, 연산 트랜스컨덕턴스 증폭기를 위한 방법. - 연산 트랜스컨덕턴스 증폭기(OTA)로서,

차동 트랜지스터 쌍에서 입력을 수신하기 위한 수단;

한 쌍의 출력 노드들을 통해 전류들을 흐르게 하기 위한 수단 ― 상기 한 쌍의 출력 노드들에 용량성 엘리먼트가 커플링됨 ―; 및

상기 한 쌍의 출력 노드들에서, 제 1 주파수 폴 및 제 2 주파수 폴을 갖는 응답을 출력하기 위한 수단을 포함하며,

상기 제 2 주파수 폴은 상기 용량성 엘리먼트에 의해 도입되고, 상기 제 2 주파수 폴은 상기 제 1 주파수 폴보다 더 큰 주파수에 있고, 상기 제 2 주파수 폴에서의 이득은 0 미만인, 연산 트랜스컨덕턴스 증폭기. - 제 18 항에 있어서,

상기 제 2 주파수 폴은 상기 한 쌍의 출력 노드들에 커플링되는 적어도 하나의 용량성 로드의 함수인, 연산 트랜스컨덕턴스 증폭기. - 제 19 항에 있어서,

상기 한 쌍의 출력 노드들에 커플링되는 캐스코드 트랜지스터 쌍을 통해 전류들을 흐르게 하기 위한 수단을 더 포함하며,

상기 한 쌍의 출력 노드들은 상기 캐스코드 트랜지스터 쌍을 통해 상기 차동 트랜지스터 쌍에 커플링되는, 연산 트랜스컨덕턴스 증폭기. - 제 20 항에 있어서,

상기 차동 트랜지스터 쌍 및 상기 캐스코드 트랜지스터 쌍은 제 1 타입의 금속 산화물 반도체(MOS) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 21 항에 있어서,

상기 캐스코드 트랜지스터 쌍에 커플링되는 제 2 캐스코드 트랜지스터 쌍을 통해 전류들을 흐르게 하기 위한 수단을 더 포함하며,

상기 제 2 캐스코드 트랜지스터 쌍은 제 2 타입의 금속 산화물 반도체(MOS) 트랜지스터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 19 항에 있어서,

상기 용량성 엘리먼트 및 상기 적어도 하나의 용량성 로드는 동일한 타입의 커패시터들을 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 19 항에 있어서,

상기 응답의 이득, 상기 용량성 엘리먼트의 커패시턴스, 및 상기 적어도 하나의 용량성 로드의 커패시턴스는, 상기 응답의 위상 마진이 대략적으로 40°- 90°이도록 구성되는, 연산 트랜스컨덕턴스 증폭기. - 제 18 항에 있어서,

시그마-델타 아날로그-디지털 변환의 적분 기능을 수행하기 위한 수단을 더 포함하는, 연산 트랜스컨덕턴스 증폭기. - 제 18 항에 있어서,

상기 OTA는 단일 스테이지인, 연산 트랜스컨덕턴스 증폭기.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/566,539 | 2014-12-10 | ||

| US14/566,539 US9369099B1 (en) | 2014-12-10 | 2014-12-10 | Low power operational transconductance amplifier |

| PCT/US2015/057366 WO2016093966A1 (en) | 2014-12-10 | 2015-10-26 | Low power operational transconductance amplifier |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170093130A true KR20170093130A (ko) | 2017-08-14 |

Family

ID=54477328

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177014796A KR20170093130A (ko) | 2014-12-10 | 2015-10-26 | 저전력 연산 트랜스컨덕턴스 증폭기 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9369099B1 (ko) |

| EP (1) | EP3231087B1 (ko) |

| JP (1) | JP6692815B2 (ko) |

| KR (1) | KR20170093130A (ko) |

| CN (1) | CN107005203B (ko) |

| WO (1) | WO2016093966A1 (ko) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11016519B2 (en) * | 2018-12-06 | 2021-05-25 | Stmicroelectronics International N.V. | Process compensated gain boosting voltage regulator |

| JP2020184665A (ja) * | 2019-05-07 | 2020-11-12 | 株式会社村田製作所 | 送受信回路 |

| CN112865800B (zh) * | 2020-12-31 | 2024-04-02 | 瑞声科技(南京)有限公司 | 一种优化OTA的sigma-delta ADC调制器及电子设备 |

| US11736071B2 (en) * | 2021-03-22 | 2023-08-22 | Qualcomm Incorporated | Wideband amplifier |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5384501A (en) * | 1990-06-15 | 1995-01-24 | Kabushiki Kaisha Toshiba | Integration circuit including a differential amplifier having a variable transconductance |

| US5631598A (en) * | 1995-06-07 | 1997-05-20 | Analog Devices, Inc. | Frequency compensation for a low drop-out regulator |

| EP0777318B1 (en) * | 1995-11-30 | 2003-03-12 | STMicroelectronics S.r.l. | Frequency self-compensated operational amplifier |

| JP3361021B2 (ja) * | 1996-12-16 | 2003-01-07 | 株式会社東芝 | フィルタ回路 |

| JP4086371B2 (ja) * | 1998-08-18 | 2008-05-14 | 富士通株式会社 | 半導体増幅回路 |

| US6114907A (en) * | 1998-12-08 | 2000-09-05 | National Semiconductor Corporation | Amplifier with dynamic compensation and method |

| US6191637B1 (en) * | 1999-03-05 | 2001-02-20 | National Semiconductor Corporation | Switched capacitor bias circuit for generating a reference signal proportional to absolute temperature, capacitance and clock frequency |

| US7049894B1 (en) | 2004-02-27 | 2006-05-23 | Marvell International Ltd. | Ahuja compensation circuit with enhanced bandwidth |

| US7248117B1 (en) | 2005-02-04 | 2007-07-24 | Marvell International Ltd. | Frequency compensation architecture for stable high frequency operation |

| US7639078B2 (en) * | 2006-07-27 | 2009-12-29 | Linear Technology Corporation | Class AB folded-cascode amplifier having cascode compensation |

| US8237509B2 (en) | 2007-02-23 | 2012-08-07 | Qualcomm, Incorporated | Amplifier with integrated filter |

| US7949322B2 (en) | 2007-03-09 | 2011-05-24 | Qualcomm, Incorporated | Frequency selective amplifier with wide-band impedance and noise matching |

| US7760019B2 (en) * | 2008-03-04 | 2010-07-20 | Micron Technology, Inc. | Adaptive operational transconductance amplifier load compensation |

| US7646247B2 (en) * | 2008-06-02 | 2010-01-12 | Mediatek Singapore Pte Ltd. | Ahuja compensation circuit for operational amplifier |

| CN101615894B (zh) * | 2008-06-27 | 2013-06-19 | 深圳赛意法微电子有限公司 | 可调线性运算跨导放大器 |

| US7750837B2 (en) * | 2008-08-01 | 2010-07-06 | Qualcomm Incorporated | Adaptive bias current generation for switched-capacitor circuits |

| KR20100021938A (ko) | 2008-08-18 | 2010-02-26 | 삼성전자주식회사 | 개선된 위상 마진을 갖는 폴디드 캐스코드 연산 증폭기 |

| IT1392081B1 (it) | 2008-12-05 | 2012-02-09 | St Wireless Sa | "amplificatore operazionale a trasconduttanza a due stadi di amplificazione" |

| US8072267B2 (en) * | 2009-06-09 | 2011-12-06 | Infineon Technologies Ag | Phase margin modification in operational transconductance amplifiers |

| US7889004B1 (en) * | 2009-09-30 | 2011-02-15 | Analog Devices, Inc. | Operational amplifiers with enhanced parameters |

| GB201102562D0 (en) * | 2011-02-14 | 2011-03-30 | Nordic Semiconductor Asa | Analogue-to-digital converter |

| CN103929138B (zh) * | 2014-04-24 | 2016-08-31 | 东南大学 | 一种低功耗高增益高摆率的运算跨导放大器 |

-

2014

- 2014-12-10 US US14/566,539 patent/US9369099B1/en active Active

-

2015

- 2015-10-26 JP JP2017530765A patent/JP6692815B2/ja active Active

- 2015-10-26 KR KR1020177014796A patent/KR20170093130A/ko unknown

- 2015-10-26 EP EP15790771.8A patent/EP3231087B1/en active Active

- 2015-10-26 WO PCT/US2015/057366 patent/WO2016093966A1/en active Application Filing

- 2015-10-26 CN CN201580065176.8A patent/CN107005203B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017537556A (ja) | 2017-12-14 |

| WO2016093966A1 (en) | 2016-06-16 |

| CN107005203A (zh) | 2017-08-01 |

| US20160173044A1 (en) | 2016-06-16 |

| EP3231087B1 (en) | 2022-01-05 |

| EP3231087A1 (en) | 2017-10-18 |

| JP6692815B2 (ja) | 2020-05-13 |

| CN107005203B (zh) | 2020-06-26 |

| US9369099B1 (en) | 2016-06-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8903343B2 (en) | Single-input multiple-output amplifiers with independent gain control per output | |

| KR101177738B1 (ko) | 조정 가능한 선형성을 갖는 sps 수신기 | |

| US10715094B2 (en) | Amplification circuit, apparatus for amplifying, low noise amplifier, radio receiver, mobile terminal, base station, and method for amplifying | |

| Wang et al. | Highly reconfigurable analog baseband for multistandard wireless receivers in 65-nm CMOS | |

| US8750437B1 (en) | Radio-frequency apparatus with programmable performance and associated methods | |

| EP3342051B1 (en) | Low noise amplifier and notch filter | |

| KR20170013248A (ko) | 온-칩 이중-공급 다중-모드 cmos 레귤레이터들 | |

| CN107005203B (zh) | 低功率运算跨导放大器 | |

| US20160380592A1 (en) | Front-end architecture for transmitter | |

| US20200106394A1 (en) | Reconfigurable broadband and noise cancellation low noise amplifier (lna) with intra-carrier aggregation (ca) capability | |

| US20160181983A1 (en) | Low power operational transconductance amplifier | |

| EP3146628B1 (en) | Differential mode bandwidth extension technique with common mode compensation | |

| US20170279445A1 (en) | Area-efficient differential switched capacitors | |

| US20170054415A1 (en) | Differential voltage reference buffer with resistor chopping |