KR20170090421A - 3중-커플링된 인덕터들을 갖는 증폭기 - Google Patents

3중-커플링된 인덕터들을 갖는 증폭기 Download PDFInfo

- Publication number

- KR20170090421A KR20170090421A KR1020177014276A KR20177014276A KR20170090421A KR 20170090421 A KR20170090421 A KR 20170090421A KR 1020177014276 A KR1020177014276 A KR 1020177014276A KR 20177014276 A KR20177014276 A KR 20177014276A KR 20170090421 A KR20170090421 A KR 20170090421A

- Authority

- KR

- South Korea

- Prior art keywords

- inductor

- coupled

- amplifier

- input

- signal

- Prior art date

Links

- 238000010168 coupling process Methods 0.000 claims abstract description 37

- 238000005859 coupling reaction Methods 0.000 claims abstract description 37

- 230000008878 coupling Effects 0.000 claims abstract description 36

- 238000000034 method Methods 0.000 claims description 32

- 230000007774 longterm Effects 0.000 claims description 4

- 230000003321 amplification Effects 0.000 claims description 3

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 3

- 230000003412 degenerative effect Effects 0.000 claims description 2

- 238000013461 design Methods 0.000 description 14

- 238000010586 diagram Methods 0.000 description 9

- 238000004891 communication Methods 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000002776 aggregation Effects 0.000 description 3

- 238000004220 aggregation Methods 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 230000001939 inductive effect Effects 0.000 description 3

- 238000004804 winding Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000007850 degeneration Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/08—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements

- H03F1/22—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements by use of cascode coupling, i.e. earthed cathode or emitter stage followed by earthed grid or base stage respectively

- H03F1/223—Modifications of amplifiers to reduce detrimental influences of internal impedances of amplifying elements by use of cascode coupling, i.e. earthed cathode or emitter stage followed by earthed grid or base stage respectively with MOSFET's

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/56—Modifications of input or output impedances, not otherwise provided for

- H03F1/565—Modifications of input or output impedances, not otherwise provided for using inductive elements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/189—High-frequency amplifiers, e.g. radio frequency amplifiers

- H03F3/19—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/189—High-frequency amplifiers, e.g. radio frequency amplifiers

- H03F3/19—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only

- H03F3/193—High-frequency amplifiers, e.g. radio frequency amplifiers with semiconductor devices only with field-effect devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/30—Single-ended push-pull [SEPP] amplifiers; Phase-splitters therefor

- H03F3/3001—Single-ended push-pull [SEPP] amplifiers; Phase-splitters therefor with field-effect transistors

- H03F3/3022—CMOS common source output SEPP amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/222—A circuit being added at the input of an amplifier to adapt the input impedance of the amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/294—Indexing scheme relating to amplifiers the amplifier being a low noise amplifier [LNA]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/387—A circuit being added at the output of an amplifier to adapt the output impedance of the amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/451—Indexing scheme relating to amplifiers the amplifier being a radio frequency amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/541—Transformer coupled at the output of an amplifier

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

Abstract

장치는 증폭기 및 증폭기의 입력에 커플링된 제 1 인덕터를 포함한다. 장치는 또한 제 1 인덕터에 유도가능하게 커플링되고 그리고 제 1 공급 노드에 증폭기를 커플링하는 제 2 인덕터를 포함한다. 장치는 또한 제 1 인덕터에 그리고 제 2 인덕터에 유도가능하게 커플링되고 그리고 제 2 공급 노드에 증폭기를 커플링하는 제 3 인덕터를 포함한다.

Description

관련 출원들에 대한 상호-참조

[0001]

본 출원은 2014년 12월 4일자로 출원된 공동 소유의 미국 정식 특허 출원 제14/560,285호를 우선권으로 주장하며, 그 내용은 그 전체가 인용에 의해 본 명세서에 명백히 포함된다.

[0002]

본 개시내용은, 일반적으로 전자장치들(electronics)에 관한 것이고, 더욱 구체적으로 RFIC(radio frequency integrated circuit)들에 관한 것이다.

[0003]

기술에 있어서의 진보는 더욱 소형의 그리고 더욱 강력한 컴퓨팅 디바이스들을 야기해 왔다. 예컨대, 작고 경량이며 사용자들에 의해 쉽게 휴대되는 휴대용 무선 전화기들, PDA(personal digital assistant)들, 및 페이징 디바이스들과 같은 무선 컴퓨팅 디바이스들을 포함하는 다양한 휴대용 개인 컴퓨팅 디바이스들이 현재 존재한다. 더욱 구체적으로, 셀룰러 전화기들 및 인터넷 프로토콜(IP) 전화기들과 같은 휴대용 무선 전화기들은 무선 네트워크들을 통해 음성 및 데이터 패킷들을 통신할 수 있다. 게다가, 수많은 이러한 무선 전화기들은 내부에 통합된 다른 타입들의 디바이스들을 포함한다. 예컨대, 무선 전화기는 또한 디지털 정지 카메라, 디지털 비디오 카메라, 디지털 리코더, 및 오디오 파일 플레이어를 포함할 수 있다. 또한, 이러한 무선 전화기들은, 인터넷에 액세스하는데 사용될 수 있는 소프트웨어 애플리케이션들, 이를테면, 웹 브라우저 애플리케이션을 포함하는 실행가능 명령들을 프로세싱할 수 있다. 이로써, 이러한 무선 전화기들은 중대한 컴퓨팅 성능들을 포함할 수 있다.

[0004]

RFIC(radio frequency integrated circuit)들이 무선 디바이스들에 사용된다. RFIC들은, 다수의 LNA(low noise amplifier)들을 포함할 수 있고, 상이한 통신 채널들을 위한 다수의 주파수 대역들(예컨대, 셀룰러 대역 또는 wifi 대역)을 수용할 수 있다. 다수의 대역 RFIC의 일 예는, UHB(ultra-high frequency band) 및 LTE(long-term evolution) 주파수 대역을 지원한다. 멀티-대역 RFIC들은 동작을 위해 다수의 주파수 대역들 중 하나를 선택하기 위한 스위칭 성능을 포함한다. 또한, RFIC 성능은 임피던스 매칭에 의해 영향을 받는 한편 RFIC 내의 LNA들은 업계 표준을 충족시키기 위해(예컨대, 캐리어 어그리게이션 및 신호 프로세싱을 수행하기 위해) 성능 및 선형성 사양들을 충족시키도록 요구될 수 있지만, (디바이스 크기 및 전력 소모를 감소시키려는 목적으로 인해) 인덕터들 및 변압기들과 같은 전자기 에너지-타입 디바이스들에 이용가능한 집적 회로 칩 면적은 제한적이다.

[0005]

도 1은 무선 시스템과 통신하는 무선 디바이스를 도시한다.

[0006] 도 2는 도 1의 무선 디바이스의 블록도를 도시한다.

[0007] 도 3은 3중-커플링된 인덕터들을 갖는 증폭기의 예시적인 실시예의 회로도를 도시한다.

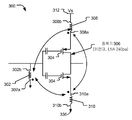

[0008] 도 4는 3중-커플링된 예시적인 인덕터 어레인지먼트의 도면을 도시한다.

[0009] 도 5는 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 예시적인 실시예의 회로도를 도시한다.

[0010] 도 6은 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 다른 예시적인 실시예의 회로도를 도시한다.

[0011] 도 7은 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 다른 예시적인 실시예의 회로도를 도시한다.

[0012] 도 8은 3중-커플링된 인덕터들을 갖는 증폭기 구조체를 사용하는 신호 증폭 방법의 흐름도를 예시한다.

[0006] 도 2는 도 1의 무선 디바이스의 블록도를 도시한다.

[0007] 도 3은 3중-커플링된 인덕터들을 갖는 증폭기의 예시적인 실시예의 회로도를 도시한다.

[0008] 도 4는 3중-커플링된 예시적인 인덕터 어레인지먼트의 도면을 도시한다.

[0009] 도 5는 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 예시적인 실시예의 회로도를 도시한다.

[0010] 도 6은 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 다른 예시적인 실시예의 회로도를 도시한다.

[0011] 도 7은 3중-커플링된 인덕터들을 갖는 스위칭가능한 증폭기의 다른 예시적인 실시예의 회로도를 도시한다.

[0012] 도 8은 3중-커플링된 인덕터들을 갖는 증폭기 구조체를 사용하는 신호 증폭 방법의 흐름도를 예시한다.

[0013]

아래에 설명된 상세한 설명은 본 개시내용의 예시적인 설계들의 설명으로서 의도되며, 본 개시내용이 실시될 수 있는 유일한 설계들만을 표현하는 것으로 의도되지 않는다. 용어 "예시적인"은 "예, 예시, 또는 예증으로서 기능하는 것"을 의미하도록 본 명세서에서 사용된다. "예시적인" 것으로서 본 명세서에 설명된 임의의 설계가 다른 설계들에 비해 반드시 바람직하거나 유리한 것으로서 해석될 필요는 없다. 상세한 설명은 본 개시내용의 예시적인 설계들의 완전한 이해를 제공하려는 목적을 위한 특정한 세부사항들을 포함한다. 본 명세서에 설명된 예시적인 설계들이 이들 특정한 세부사항들 없이도 실행될 수도 있다는 것은 당업자들에게는 명백할 것이다. 몇몇 예시들에서, 잘 알려진 구조들 및 디바이스들은 본 명세서에 제시된 예시적인 설계들의 신규성을 모호하게 하는 것을 회피하기 위해 블록도 형태로 도시된다.

[0014]

도 1은 무선 디바이스(110)가 무선 통신 시스템(120)과 통신하는 것을 도시한다. 무선 통신 시스템(120)은, LTE(Long Term Evolution) 시스템, CDMA(Code Division Multiple Access) 시스템, GSM(Global System for Mobile Communications) 시스템, WLAN(wireless local area network) 시스템, 또는 몇몇 다른 무선 시스템일 수 있다. CDMA 시스템은, WCDMA(Wideband CDMA), CDMA 1X, EVDO(Evolution-Data Optimized), TD-SCDMA(Time Division Synchronous CDMA), 또는 CDMA의 몇몇 다른 버전을 구현할 수 있다. 단순화를 위해, 도 1은 2개의 기지국들(130 및 132) 및 하나의 시스템 제어기(140)를 포함하는 무선 통신 시스템(120)을 도시한다. 일반적으로, 무선 시스템은 임의의 수의 기지국들 및 임의의 세트의 네트워크 엔티티들을 포함할 수 있다.

[0015]

무선 디바이스(110)는 또한, 사용자 장비(UE), 모바일 스테이션, 단말, 액세스 단말, 가입자 유닛, 스테이션 등으로 지칭될 수 있다. 무선 디바이스(110)는, 셀룰러 폰, 스마트폰, 태블릿, 무선 모뎀, PDA(personal digital assistant), 핸드헬드 디바이스, 랩탑 컴퓨터, 스마트북, 넷북, 코드리스 폰, WLL(wireless local loop) 스테이션, 블루투스 디바이스 등일 수 있다. 무선 디바이스(110)는 무선 시스템(120)과 통신할 수 있다. 무선 디바이스(110)는 또한, 브로드캐스트 스테이션들(예컨대, 브로드캐스트 스테이션(134))로부터 신호들, 하나 또는 그 초과의 GNSS(global navigation satellite system)들에서, 위성들(예컨대, 위성(150))로부터의 신호들 등을 수신할 수 있다. 무선 디바이스(110)는, 무선 통신을 위한 하나 또는 그 초과의 라디오 기술들, 이를테면, LTE, WCDMA, CDMA 1X, EVDO, TD-SCDMA, GSM, 802.11, 등을 지원할 수 있다. 예시적인 실시예에서, 무선 디바이스(110)는 적분기(integrator)를 포함할 수 있다.

[0016]

게다가, 예시적인 실시예에서, 본 명세서에 추가로 설명된 바와 같이, 무선 디바이스(110)는 3중-커플링된 인덕터들을 갖는 증폭기를 포함할 수 있다. 증폭기는, 다수의 주파수 대역들 사이에서 무선 디바이스(110)를 스위칭하는 것을 가능하게 하는 회로를 포함할 수 있거나 이 회로에 커플링될 수 있다.

[0017]

도 2는 도 1의 무선 디바이스(110)의 예시적인 설계의 블록도를 도시한다. 이러한 예시적인 설계에서, 무선 디바이스(110)는, 주요 안테나(210)에 커플링된 트랜시버(220), 안테나 인터페이스 회로(226)를 통해 보조 안테나(212)에 커플링된 트랜시버(222), 및 데이터 프로세서/제어기(280)를 포함한다. 트랜시버(220)는, 다중 주파수 대역들, 다중 라디오 기술들, 캐리어 어그리게이션 등을 지원하기 위해 다수의(K개) 수신기들(230pa 내지 230pk) 및 다수의(K개) 송신기들(250pa 내지 250pk)을 포함한다. 트랜시버(222)는, 다수의 주파수 대역들, 다수의 라디오 기술들, 캐리어 어그리게이션, 수신 다이버시티, 다수의 송신 안테나들로부터 다수의 수신 안테나들로의 MIMO(multiple-input multiple-output) 송신 등을 지원하기 위해 다수의(L개) 수신기들(230sa 내지 230sl) 및 다수의(L개) 송신기들(250sa 내지 250sl)을 포함한다.

[0018]

도 2에 도시된 예시적인 설계에서, 각각의 수신기(230)는 LNA(240) 및 수신 회로들(242)을 포함한다. 데이터 수신의 경우, 안테나(210)는, 기지국들 및/또는 다른 송신기 스테이션들로부터 신호들을 수신하고 수신된 RF 신호를 제공하는데, 그 RF 신호는 안테나 인터페이스 회로(224)를 통해 라우팅되고 입력 RF 신호로서 선택된 수신기에, 예컨대, 제 1 입력 신호 경로(225)를 통해 수신기(230pa)에 또는 제 2 입력 신호 경로(235)를 통해 수신기(230pk)에 제공된다. 안테나 인터페이스 회로(224)는, 스위치들, 듀플렉서들, 송신 필터들, 수신 필터들, 매칭 회로들 등을 포함할 수 있다. 특정 실시예에서, LNA들(240) 중 하나 또는 그 초과는, 도 3 내지 도 7을 참조로 추가로 설명되는 바와 같이, 3중-커플링된 인덕터들을 포함하는 증폭기 회로에 대응할 수 있다. 도 2의 예에서, 무선 디바이스(110)의 더 많은, 더 적은, 및/또는 상이한 증폭기들은 대안적인 실시예들에서 3중-커플링된 인덕터들을 포함할 수 있지만(또는 이들과 연관될 수 있지만), 수신기(230pa) 내의 LNA(240pa)는 3중-커플링된 인덕터들을 포함하는 것으로서(또는 이들과 연관된 것으로서) 표시된다.

[0019]

이하의 설명은, 수신기(230pa)가 선택된 수신기임을 가정한다. 수신기(230pa) 내에서, LNA(240pa)는 입력 RF 신호를 증폭시키고 출력 RF 신호를 제공한다. 수신 회로들(242pa)은, 출력 RF 신호를 RF에서 기저대역으로 다운컨버팅하고, 다운컨버팅된 신호를 증폭시키고 필터링하여, 아날로그 입력 신호를 데이터 프로세서(280)에 제공한다. 수신 회로들(242pa)은, 혼합기들, 필터들, 증폭기들, 매칭 회로들, 오실레이터, LO(local oscillator) 생성기, PLL(phase locked loop) 등을 포함할 수 있다. 트랜시버들(220 및 222)에서의 각각의 나머지 수신기(230)는 수신기(230pa)와 유사한 방식으로 동작할 수 있다.

[0020]

도 2에 도시된 예시적인 설계에서, 각각의 송신기(250)는 송신 회로들(252) 및 PA(power amplifier)(254)를 포함한다. 데이터 송신의 경우, 데이터 프로세서(280)는 송신될 데이터를 프로세싱(예컨대, 인코딩 및 변조)하고, 아날로그 출력 신호를 선택된 송신기에 제공한다. 이하의 설명은, 송신기(250pa)가 선택된 송신기임을 가정한다. 송신기(250pa) 내에서, 송신 회로들(252pa)은, 아날로그 출력 신호를 기저대역에서 RF로 증폭, 필터링, 및 업컨버팅하여, 변조된 RF 신호를 제공한다. 송신 회로들(252pa)은, 증폭기들, 필터들, 혼합기들, 매칭 회로들, 오실레이터, LO 생성기, PLL 등을 포함할 수 있다. PA(254pa)는, 변조된 RF 신호를 수신하고 증폭시키고, 적절한 출력 전력 레벨을 갖는 송신 RF 신호를 제공한다. 송신 RF 신호는, 안테나 인터페이스 회로(224)를 통해 라우팅되고, 안테나(210)를 통해 송신된다. 트랜시버들(220 및 222)에서의 각각의 나머지 송신기(250)는 송신기(250pa)와 유사한 방식으로 동작할 수 있다.

[0021]

도 2는 수신기(230) 및 송신기(250)의 예시적인 설계를 도시한다. 수신기 및 송신기는 또한, 도 2에 도시되지 않은 다른 회로들, 이를테면, 필터들, 매칭 회로들 등을 포함할 수 있다. 트랜시버들(220 및 222)의 전부 또는 일부는, 하나 또는 그 초과의 아날로그 IC(integrated circuit)들, RF IC들(RFIC들), 혼합-신호 IC들 등 상에서 구현될 수 있다. 예컨대, LNA들(240) 및 수신 회로들(242)은, RFIC 등일 수 있는 하나의 모듈 상에서 구현될 수 있다. 트랜시버들(220 및 222) 내의 회로들은 또한 다른 방식들로 구현될 수 있다.

[0022]

데이터 프로세서/제어기(280)는 무선 디바이스(110)에 대한 다양한 기능들을 수행할 수 있다. 예컨대, 데이터 프로세서(280)는, 수신기들(230)을 통해 수신되는 데이터 및 송신기들(250)을 통해 송신되는 데이터에 대한 프로세싱을 수행할 수 있다. 제어기(280)는 트랜시버들(220 및 222) 내의 다양한 회로들의 동작을 제어할 수 있다. 메모리(282)는 데이터 프로세서/제어기(280)에 대한 프로그램 코드들 및 데이터를 저장할 수 있다. 데이터 프로세서/제어기(280)는 하나 또는 그 초과의 ASIC(application specific integrated circuit)들 및/또는 다른 IC들 상에서 구현될 수 있다.

[0023]

무선 디바이스(110)는 다수의 대역 그룹들, 다수의 라디오 기술들, 및/또는 다수의 안테나들을 지원할 수 있다. 무선 디바이스(110)는 다수의 대역 그룹들, 다수의 라디오 기술들, 및/또는 다수의 안테나들을 통해 수신을 지원하기 위한 다수의 LNA들을 포함할 수 있다.

[0024]

예시적인 실시예에서, 무선 디바이스(110)와 같은 장치는 3중-커플링된 인덕터들을 갖는 스위칭가능한 하이-패스 증폭기를 포함할 수 있다. 장치는 다수의 주파수 대역들(예컨대, LTEU(UHB/LTE-Unlicensed)) 사이에서 스위칭가능한 회로(예컨대, 도 2의 LNA들(240)을 포함)를 포함할 수 있다.

[0025]

도 3은 인덕터들의 3중-커플링된 어레인지먼트에 커플링된 증폭기(306)의 예시적인 실시예(300)를 예시한다. 증폭기(306)는, 션트 인덕터(302)로서 예시된 제 1 인덕터, 제 2 인덕터(308), 및 제 3 인덕터(310)에 커플링될 수 있다. 션트 인덕터(302)는 증폭기(306)의 입력에 커플링된다(예컨대, 인버터-타입 LNA의 게이트들(304)에 커플링된다). 션트 인덕터(302)의 제 1 단자(302a)는 접지에 연결되고, 션트 인덕터(302)의 제 2 단자(302b)는 제 1 증폭기(306)의 입력에 커플링된다. 션트 인덕터(302)는, 도시된 바와 같이 커플링된 단자들(308a 및 308b)을 갖는 제 2 인덕터(308)에, 그리고 도시된 바와 같이 커플링된 단자들(310a 및 310b)을 갖는 제 3 인덕터(310)에 유도가능하게 커플링된다. 예시적인 예에서, 인덕터들(308, 310)은 도 3에 도시된 것과 같은 변성 변압기(degeneration transformer)의 변성 인덕터(degenerative inductor)들이다. 인덕터(308)는 제 1 공급 노드(312)(예컨대, 전압 공급기(Vs))에 제 1 증폭기(306)를 커플링하고, 인덕터(310)는 제 2 공급 노드(336)(예컨대, 접지)에 제 1 증폭기(306)를 커플링한다. 제 2 공급 노드(336)가 접지 노드로서 예시되지만, 다른 실시예들에서 제 2 공급 노드(336)는 비-접지 공급 전압을 제공할 수 있다. 도 3에서, 3중-커플링 인덕터들(302, 308, 310) 각각의 극성은 점-표기법을 사용하여 표시된다.

[0026]

인덕터들(302, 308, 310)의 3중-커플링된 인덕터 어레인지먼트는 견고하게 커플링된 중첩된(nested)(예컨대, 동심형) 루프들의 사용에 의해 작은 영역에서 구현될 수 있다. 일례로서, 도 4에 도시된 예시적인 설계는 100x100 마이크로미터(㎛)의 면적 내에서 인덕터들(302, 308 및 310)의 3중-커플링된 어레인지먼트를 형성하기 위해 사용될 수 있는 인덕터들의 어레인지먼트를 도시한다. 도 4에 도시된 바와 같이, 인덕터들(302, 308, 310)은 도 2의 트랜시버(220)를 포함하는 RFIC와 같은 디바이스의 칩 상의 영역을 보존하기 위해 중첩될 수 있다. 동심형 인덕터들(302, 308 및 310)의 권선축(예컨대, 공동축)은 도 4의 402에 도시된다. 대안적인 실시예들에서, 인덕터들(302, 308 및 310) 중 하나 또는 그 초과는, 도 4에 도시된 것과는 상이한 어레인지먼트들의 유도성 권선들을 사용하여 구현될 수 있다. 예컨대, 예시된 것과 상이한 인덕터는 3중-커플링된 인덕터 어레인지먼트의 가장 안쪽, 중간, 또는 가장 바깥쪽 인덕터일 수 있다. 다른 예로서, 인덕터(들)의 단자들은 상이하게 배열될 수 있다.

[0027]

도 5는, 인덕터들의 개별적인 3중-커플링된 어레인지먼트에 각각 커플링된 증폭기(306) 및 제 2 증폭기(316)를 포함하는 회로의 예시적인 실시예(500)를 도시한다. 제 1 스위치(320)는 입력 노드(390)(예컨대, 도 2의 안테나 인터페이스 회로(224) 내부의 노드)를 제 1 입력 신호 경로(225)를 통해 제 1 증폭기(306)의 입력으로 선택적으로 커플링한다. 제 2 스위치(322)는 입력 노드(390)를 제 2 증폭기(316)의 입력으로 선택적으로 커플링한다. 제 1 증폭기(306)의 출력(330)은 제 1 변압기(332) 및 제 1 혼합기(334)를 포함하는 제 1 수신기 회로에 커플링된다. 제 2 증폭기(316)의 출력(340)은 제 2 변압기(342) 및 제 2 혼합기(344)를 포함하는 제 2 수신기 회로에 커플링된다. 제 1 증폭기(306) 및 제 1 수신기 회로는, 도 2의 LNA(240pa) 및 수신기 회로(242pa)에 각각 대응할 수 있고, 제 2 증폭기(316) 및 제 2 수신기 회로는 LNA(240pk) 및 수신기 회로(242pk)에 각각 대응할 수 있다.

[0028]

제 1 증폭기(306)는 제 1 주파수 대역(예컨대, LTEU 주파수 대역)에 대응하는 RF 신호들 상에서 동작하도록 구성될 수 있다. 제 1 증폭기(306)는, 션트 인덕터(302)로서 예시된 제 1 인덕터, 제 2 인덕터(308), 및 제 3 인덕터(310)를 포함하는 3중-커플링된 매칭 변압기(예컨대, 3중-커플링된 LTEU 매칭 변압기(315))에 커플링될 수 있다. 션트 인덕터(302)는 제 1 증폭기(306)의 입력에 커플링된다(예컨대, 인버터-타입 LNA의 게이트들(304)에 커플링된다). 션트 인덕터(302)는 3중-커플링된 인덕터 어레인지먼트를 형성하기 위해 다른 인덕터들(308, 310)(예컨대, 도 5에 도시된 바와 같이 변성 변압기의 인덕터들)에 유도가능하게 커플링된다. 인덕터(308)는 제 1 공급 노드(312)(예컨대, 전압 공급기(Vs))에 제 1 증폭기(306)를 커플링하고, 인덕터(310)는 제 2 공급 노드(336)(예컨대, 접지)에 제 1 증폭기(306)를 커플링한다. 제 2 공급 노드(336)가 접지 노드로서 예시되지만, 다른 실시예들에서 제 2 공급 노드(336)는 비-접지 공급 전압을 제공할 수 있다.

[0029]

제 2 증폭기(316)는 제 2 주파수 대역(예컨대, UHB 주파수 대역)에 대응하는 RF 신호들 상에서 동작하도록 구성될 수 있다. 제 2 증폭기(316)는, 션트 인덕터(352)로서 예시된 제 4 인덕터, 제 5 인덕터(358), 및 제 6 인덕터(360)를 포함하는 3중-커플링된 매칭 변압기(예컨대, 3중-커플링된 UHB 매칭 변압기(325))에 커플링될 수 있다. 션트 인덕터(352)는, 제 2 증폭기(316)의 입력에 커플링되고, 인덕터들(358, 360)에 유도가능하게 커플링되어 3중-커플링된 인덕터 어레인지먼트를 형성한다. 인덕터(358)는 제 1 공급 노드(348)(예컨대, 전압 공급기(Vs))에 제 2 증폭기(316)를 커플링하고, 인덕터(360)는 제 2 공급 노드(346)(예컨대, 접지)에 제 2 증폭기(316)를 커플링한다. 제 2 공급 노드(346)가 접지 노드로서 예시되지만, 다른 실시예들에서 제 2 공급 노드(346)는 비-접지 공급 전압을 제공할 수 있다. 예시적인 예에서, 인덕터들(352, 358, 360)의 3중-커플링된 인덕터 어레인지먼트는, 인덕터들(302, 308, 310)과 관련하여 도 4에 도시된 바와 같이 견고하게 커플링된 중첩된(예컨대, 동심형) 루프들의 사용에 의해 작은 영역 내에서 구현된다.

[0030]

제 1 증폭기(306)의 출력(330)에 커플링된 수신 회로는 제 1 주파수 대역(예컨대, LTEU 주파수 대역)에 대응하는 신호들을 프로세싱하도록 구성될 수 있다. 예컨대, 변압기(332)는 LTEU 변압기일 수 있고, 혼합기(334)는 LTEU 주파수 대역 신호를 기저대역 신호로 또는 중간 주파수 신호로 하향-혼합하도록 구성될 수 있다. 제 2 증폭기(316)의 출력(340)에 커플링된 수신 회로는 제 2 주파수 대역(예컨대, UHB 주파수 대역)에 대응하는 신호들을 프로세싱하도록 구성될 수 있다. 예컨대, 변압기(342)는 UHB 변압기일 수 있고, 혼합기(344)는 UHB 주파수 대역 신호를 기저대역 신호로 또는 중간 주파수 신호로 하향-혼합하도록 구성될 수 있다.

[0031]

제 1 증폭기(306)에 대응하는 3중-커플링된 변압기 어레인지먼트는, 제 1 커플링 계수(K12)로 제 2 인덕터(308)에 유도가능하게 커플링된 션트 인덕터(302)를 포함한다. 션트 인덕터(302)는 또한 제 2 커플링 계수(K13)로 제 3 인덕터(310)에 유도가능하게 커플링된다. 도 5에 예시된 바와 같이, 제 1 커플링 계수(K12) 및 제 2 커플링 계수(K13)는 실질적으로 동일한 값(예컨대, K12=K13=0.3)을 가질 수 있다. 제 2 인덕터(308)는 제 3 커플링 계수(K23)(예컨대, K23=0.5)로 제 3 인덕터(310)에 유도가능하게 커플링된다. 인덕터 계수 K(예컨대, K12, K13, 및/또는 K23)의 값은 제 1 증폭기(306)의 임피던스를 튜닝하도록 선택 및/또는 수정될 수 있다. 도 5는 제 1 커플링 계수(K12)와 제 2 커플링 계수(K13)가 실질적으로 동일한 값을 갖는 것으로서 예시하지만, 다른 실시예들에서 제 1 커플링 계수(K12)는 제 2 커플링 계수(K13)와는 상이할 수 있다. 3중-커플링된 인덕터들(302, 308, 310) 각각의 극성은 도 5에서 점-표기법을 사용하여 표시된다.

[0032]

유사하게, 제 2 증폭기(316)에 대응하는 3중-커플링된 변압기 어레인지먼트는, 제 4 커플링 계수(K45)로 제 5 인덕터(358)에 유도가능하게 커플링되는 션트 인덕터(352)를 포함한다. 션트 인덕터(352)는 또한 제 5 커플링 계수(K46)로 제 6 인덕터(360)에 유도가능하게 커플링된다. 도 5에 예시된 바와 같이, 제 4 커플링 계수(K45) 및 제 5 커플링 계수(K46)는 실질적으로 동일한 값(예컨대, K45=K46=0.35)을 가질 수 있다. 제 5 인덕터(358)는 제 6 커플링 계수(K56)(예컨대, K56=0.5)로 제 6 인덕터(360)에 유도가능하게 커플링된다. K45, K46, 및/또는 K56의 값은 제 2 증폭기(316)의 임피던스를 튜닝하도록 선택 및/또는 수정될 수 있다. 도 5는 제 4 커플링 계수(K45)와 제 5 커플링 계수(K46)가 실질적으로 동일한 값을 갖는 것으로서 예시하지만, 다른 실시예들에서 제 4 커플링 계수(K45)는 제 5 커플링 계수(K46)와는 상이할 수 있다.

[0033]

도 5에 예시된 3중-커플링된 인덕터 어레인지먼트들은 증폭기들(306, 316)의 하나 또는 그 초과의 동작 특징들을 개선시킬 수 있다. 예컨대, 션트 인덕터(302)를 변성 인덕터들(308, 310)에 커플링하는 것은, 제 1 증폭기(306)의 선형성을 개선시킬 수 있다. 예시를 위해, 하이-패스 필터 매칭은, 하측 방해 전파(lower side jammer)를 필터링할 수 있고, 그리고 OOB(out of band) IIP2(second order intercept point) 및/또는 IIP3(third order intercept point)(IIP2/IIP3) 성능 측정들을 개선시킬 수 있다. OOB IIIP2/IIIP3의 개선은 제 1 증폭기(306)의 개선된 선형성을 나타낸다. 유사하게, 인덕터들(352, 358, 및 360)의 3중-커플링된 어레인지먼트는 제 2 증폭기(316)의 선형성을 개선시킬 수 있다.

[0034]

도 5의 회로에서 션트 인덕터(302)와 변성 인덕터들(308, 310) 사이의 유도성 커플링(K)을 튜닝함으로써, (증폭기의 게이트에 커플링된) 직렬 커패시터를 사용하고 그리고 션트 인덕터를 사용하는 특정 하이-패스 매칭 회로들과는 대조적으로, 매칭 변압기(315)는 증폭기의 게이트에 커플링된 직렬 커패시터를 생략하기 위해 충분한 임피던스 매칭을 제공하도록 설계될 수 있으며, 이에 의해 회로 영역을 추가로 감소시킬 수 있다.

[0035]

따라서, 도 5는, 제 1 주파수 대역의 신호를 증폭시키도록 구성된 제 1 증폭기(306)(예컨대, LTE를 위한 LNA) 및 제 2 주파수 대역의 신호를 증폭시키도록 구성된 제 2 증폭기(316)(예컨대, UHB를 위한 LNA)를 예시한다. 각각의 증폭기(306, 316)는 앞서 설명된 바와 같이 3중-커플링된 인덕터 어레인지먼트를 사용한다. 션트 인덕터(302)는, 제 1 증폭기(306)의 선형성을 개선시키고, 임피던스 매칭을 수행하고, 그리고 면적을 감소시키기 위해 변성 인덕터들(308, 310)에 커플링된다(즉, 3중-커플링된다). 션트 인덕터(352)는, 제 2 증폭기(316)의 선형성을 개선시키고, 임피던스 매칭을 수행하고, 그리고 면적을 감소시키기 위해 변성 인덕터들(358, 360)에 커플링된다(즉, 3중-커플링된다). 따라서, 3중-커플링된 인덕터들을 사용함으로써 면적을 덜 소모하는 스위칭가능한 멀티-대역 증폭 회로가 제공된다.

[0036]

도 5는 션트 인덕터들(302, 352) 각각이 증폭기 입력과 접지 사이에 커플링된 것으로서 예시하지만, 다른 예시적인 실시예들에서, 션트 인덕터들(302, 352) 중 하나 또는 둘 다는, 도 6과 관련하여 추가로 상세하게 설명된 것과 같이, 입력 노드(390)와 증폭기 입력 사이에 커플링된 직렬 인덕터에 의해 교체될 수 있다. 도 5는 증폭기들(306, 316)이 스위치들(320, 322)을 통해 입력 노드(390)에 선택적으로 커플링되는 것(예컨대, 증폭기 선택은 동작 모드(예컨대, LTEU/UHB)에 기반하여 도 2의 데이터 프로세서/제어기(280)로부터의 제어 신호들을 통해 제어될 수 있음)을 예시하지만, 다른 실시예들에서, 증폭기들(306, 316)이 도 2의 안테나 인터페이스 회로(224)의 별도의 신호 출력 노드들에 커플링되는 구성과 같이, 스위치들(320, 322) 중 하나 또는 둘 다는 생략될 수 있다. 도 5는 2개의 증폭기들(306, 316)이 입력 노드(390)에 선택적으로 커플링된 것을 예시하지만, 다른 실시예들에서, 3개 또는 그 초과의 증폭기들은 하나 또는 그 초과의 스위칭 엘리먼트들을 통해, 이를테면, 디멀티플렉서 회로를 통해 입력 노드(390)에 선택적으로 커플링될 수 있고 그리고 입력 노드(390)로부터 선택적으로 디커플링될 수 있다.

[0037]

도 6은, 도 5의 션트 인덕터들(302, 352) 대신에 직렬-커플링된 인덕터들(602, 652)을 사용하는 도 5의 증폭기들(306, 316)의 예시적인 실시예(600)를 예시한다. 제 1 스위치(320)는 입력 신호를 수신하기 위해 제 1 직렬-커플링된 인덕터(602)의 제 1 단자(예컨대, 포지티브 단자)에 제 1 입력 신호 경로(225)를 통해 입력 노드(390)를 선택적으로 커플링한다. 제 1 직렬-커플링된 인덕터(602)의 제 2 단자(예컨대, 네거티브 단자)는 제 1 증폭기(306)의 입력에 커플링된다. 제 2 스위치(322)는 제 2 직렬-커플링된 인덕터(652)의 제 1 단자에 제 2 입력 신호 경로(235)를 통해 입력 노드(390)를 선택적으로 커플링한다. 제 2 직렬-커플링된 인덕터(652)의 제 2 단자는 제 2 증폭기(316)의 입력에 커플링된다. 제 1 증폭기(306)의 출력(330)은 제 1 변압기(332) 및 제 1 혼합기(334)를 포함하는 제 1 수신기 회로에 커플링된다. 제 2 증폭기(316)의 출력(340)은 제 2 변압기(342) 및 제 2 혼합기(344)를 포함하는 제 2 수신기 회로에 커플링된다.

[0038]

제 1 증폭기(306)는, 제 1 직렬-커플링된 인덕터(602), 제 2 인덕터(308), 및 제 3 인덕터(310)를 포함하는 3중-커플링된 매칭 변압기(615)에 커플링된다. 제 2 증폭기(316)는, 제 2 직렬-커플링된 인덕터(652), 제 5 인덕터(358), 및 제 6 인덕터(360)를 포함하는 3중-커플링된 매칭 변압기(625)에 커플링된다.

[0039]

제 1 증폭기(306)에 대한 인덕터들(602, 308, 310)의 3중-커플링된 인덕터 어레인지먼트 및 제 2 증폭기(316)에 대한 인덕터들(652, 358, 및 360)의 3중-커플링된 인덕터 어레인지먼트는 견고하게 커플링된 중첩된 (예컨대, 동심형) 루프들의 사용에 의해 작은 영역(예컨대, 도 4 참조)에서 구현될 수 있다. 예로서, 제 1 증폭기(306)의 인덕터들(602, 308, 및 310)은 100x100 마이크로미터(㎛)의 영역에서 3중-커플링된 어레인지먼트로 도 4에 도시된 것과 같이 배열될 수 있다. 대안적인 실시예들에서, 인덕터들(602, 308 및 310) 중 서로 다른 것들은 도 4에 도시된 3중-커플링된 어레인지먼트의 가장 안쪽, 중간, 및 가장 바깥쪽 인덕터들일 수 있으며, 그리고/또는 인덕터들(602, 308, 및 310) 중 하나 또는 그 초과는 도 4에 도시된 것과는 상이한 어레인지먼트들의 유도성 권선들을 사용하여 구현될 수 있다.

[0040]

도 6에 예시된 3중-커플링된 인덕터 어레인지먼트들은 증폭기들(306, 316)의 하나 또는 그 초과의 동작 특성들을 개선시킬 수 있다. 예컨대, 도 6의 3중-커플링된 인덕터 어레인지먼트들은 도 5와 관련하여 설명된 것과 유사한 방식으로 증폭기 선형성을 개선시킬 수 있다. 그러나, 더 낮은 주파수 성분들이 접지로 션트됨에 따라서 하이-패스 필터 매칭을 제공하는 도 5의 션트 인덕터들(302, 352)과는 대조적으로, 도 6의 직렬-커플링된 인덕터들(602, 652)은 더 높은 주파수 성분들이 증폭기 입력에서 직렬 인덕턴스에 의해 차단되기 때문에 고주파 방해 전파 차단을 그 대신에 제공할 수 있다.

[0041]

도 7은, 캐스코드 구성을 갖는, 도 5의 제 1 증폭기(306) 및 제 2 증폭기(316)를 포함하는 시스템의 다른 예시적인 실시예(700)를 예시한다. 제 1 스위치(320)는, 제 1 증폭기(306)의 입력에 커플링된 션트 인덕터(302)에, 제 1 입력 신호 경로(225)를 통해 입력 노드(390)를 선택적으로 커플링하도록 구성된다. 제 2 스위치(322)는 입력 노드(390)를 제 2 입력 신호 경로(235)를 통해 제 2 증폭기(316)에 선택적으로 커플링할 수 있다. 제 1 증폭기(306)의 출력(330)은 제 1 변압기(332) 및 제 1 혼합기(334)를 포함하는 제 1 수신기 회로에 커플링된다. 제 2 증폭기(316)의 출력(340)은 제 2 변압기(342) 및 제 2 혼합기(344)를 포함하는 제 2 수신기 회로에 커플링된다.

[0042]

제 1 증폭기(306)는 제 1 캐스코드 트랜지스터(704)(예컨대, p-타입 트랜지스터, 이를테면, PMOS(p-type metal oxide semiconductor) 트랜지스터) 및 제 2 캐스코드 트랜지스터(706)(예컨대, n-타입 트랜지스터, 이를테면, NMOS(N-type MOS) 트랜지스터)를 포함한다. 제 1 캐스코드 트랜지스터(704)는 제 1 바이어스 전압(Vcasc_p)에 의해 바이어싱될 수 있고, 제 2 캐스코드 트랜지스터(706)는 제 2 바이어스 전압(Vcasc_n)에 의해 바이어싱될 수 있다. 캐스코드 트랜지스터들(704, 706)은, 제 1 증폭기(306)의 출력 임피던스를 증가시킬 수 있고, 제 1 증폭기(306)의 입/출력 분리를 개선시킬 수 있다. 도 5의 제 2 증폭기(316)는 또한, 제 1 증폭기(306)와 유사한 캐스코드 구성을 갖는 캐스코드 트랜지스터들(704, 706)을 포함한다.

[0043]

도 7이 션트 인덕터(302)를 포함하는 3중-커플링된 매칭 변압기에 커플링된 제 1 증폭기(306)의 캐스코드 구성을 도시하지만, 다른 실시예들에서, 캐스코드 증폭기 구성은 직렬-커플링된 인덕터를 포함하는 3중-커플링된 매칭 변압기에 커플링될 수 있다. 예컨대, 제 1 캐스코드 트랜지스터(704) 및 제 2 캐스코드 트랜지스터(706)는 도 6의 제 1 증폭기(306) 및/또는 제 2 증폭기(316)에 포함될 수 있다.

[0044]

신호 증폭의 예시적인 방법(800)은 도 8에 도시된다. 방법(800)은, 802에서, 증폭기의 입력에서 제 1 신호를 수신하는 단계를 포함할 수 있다. 입력은 제 1 인덕터에 커플링될 수 있다. 예컨대, 도 5를 참조로, 제 1 입력 신호 경로(225)를 통해 제 1 증폭기(306)의 입력에서 신호가 수신될 수 있다. 제 1 증폭기(306)의 입력은 제 1 인덕터(302)에 커플링된다.

[0045]

방법(800)은 또한, 804에서, 증폭된 출력 신호를 제공하기 위해 증폭기의 입력 신호를 증폭시키는 단계를 포함할 수 있다. 증폭기는 제 1 인덕터에 유도가능하게 커플링된 제 2 인덕터에 의해 전압원에 커플링될 수 있다. 예컨대, 도 5를 참조로, 동작 동안, 제 1 증폭기(306)는 입력 신호를 증폭시켜, 증폭된 출력 신호를 출력(330)에 제공한다. 제 1 증폭기(306)는 제 1 인덕터(302)에 유도가능하게 커플링된 제 2 인덕터(308)에 의해 공급 노드(예컨대, 전압원)(312)에 커플링된다. 증폭기는 또한 제 1 인덕터에 유도가능하게 커플링된 제 3 인덕터에 의해 접지에 커플링될 수 있다. 예컨대, 도 5를 참조로, 제 1 증폭기(306)는 제 1 인덕터(302)에 유도가능하게 커플링된 제 3 인덕터(310)에 의해 접지에 커플링된다. 다른 예로서, 도 6를 참조로, 제 1 증폭기(306)는 제 1 직렬-커플링된 인덕터(602)에 유도가능하게 커플링된 제 3 인덕터(310)에 의해 접지에 커플링된다. 증폭된 출력 신호는, 제 1 증폭기(306)로부터 변압기, 이를테면, 도 5의 변압기(332)에 제공될 수 있다.

[0046]

방법(800)은 또한 제 2 증폭기에서 제 2 신호를 증폭시키는 단계를 포함할 수 있다. 예컨대, 도 5를 참조로, 제 2 신호는 제 2 입력 신호 경로(235)를 통해 제 2 증폭기(316)의 입력에서 수신될 수 있다. 제 1 신호는 LTE 주파수 대역 신호일 수 있고, 제 2 신호는 UHB 신호일 수 있다.

[0047]

3중-커플링된 구성으로 3개의 인덕터들에 커플링된 증폭기, 이를테면, 도 3 및 도 5의 션트 인덕터(302) 및 변성 인덕터들(308, 310)에 커플링된 제 1 증폭기(306)에서 입력 신호를 증폭시키는 것은, 증폭기의 강화된 선형성 및/또는 임피던스 매칭으로 인해 개선된 출력 신호 특징들을 초래할 수 있다. 인덕터들의 3중-커플링된 구성은, 도 2의 트랜시버(220)를 포함하는 RFIC와 같은 칩 또는 디바이스 상에서의 면적 사용을 추가로 감소시킬 수 있다.

[0048]

설명된 실시예들과 관련하여, 장치는 증폭시키기 위한 수단의 입력에서 신호를 증폭시키기 위한 수단을 포함할 수 있다. 예컨대, 증폭시키기 위한 수단은, 도 2의 LNA(240), 도 3, 도 5, 도 6, 또는 도 7의 제 1 증폭기(306), 도 5, 도 6, 또는 도 7의 제 2 증폭기(316), 하나 또는 그 초과의 다른 디바이스들, 회로들, 또는 이들의 임의의 조합을 포함할 수 있다.

[0049]

장치는 또한 제 1 공급 노드에 증폭시키기 위한 수단을 커플링하기 위한 제 1 수단을 포함할 수 있다. 예컨대, 커플링하기 위한 제 1 수단은, 도 3, 도 4, 도 5, 도 6, 또는 도 7의 인덕터(308), 도 5 또는 도 6의 인덕터(358), 하나 또는 그 초과의 다른 디바이스들, 회로들, 또는 이들의 임의의 조합을 포함할 수 있다.

[0050]

장치는 제 2 공급 노드에 증폭시키기 위한 수단을 커플링하기 위한 제 2 수단을 더 포함할 수 있다. 예컨대, 커플링하기 위한 제 2 수단은, 도 3, 도 4, 도 5, 도 6, 또는 도 7의 인덕터(310), 도 5, 도 6 또는 도 7의 인덕터(360), 하나 또는 그 초과의 다른 디바이스들, 회로들, 또는 이들의 임의의 조합을 포함할 수 있다.

[0051]

장치는 또한, 증폭시키기 위한 수단의 입력에 인덕턴스를 제공하기 위한 수단을 포함할 수 있다. 인덕턴스를 제공하기 위한 수단은 커플링하기 위한 제 1 수단 및 커플링하기 위한 제 2 수단에 유도가능하게 커플링될 수 있다. 예컨대, 인덕턴스를 제공하기 위한 수단은, 도 3, 도 5 또는 도 7의 인덕터(302), 도 3, 도 5 또는 도 7의 인덕터(352), 도 6의 인덕터(602), 도 6의 인덕터(652), 하나 또는 그 초과의 다른 디바이스들, 회로들, 또는 이들의 임의의 조합을 포함할 수 있다.

[0052]

당업자들은, 정보 및 신호들이 다양한 상이한 기법들 및 기술들 중 임의의 기법 및 기술을 사용하여 표현될 수도 있음을 이해할 것이다. 예를 들어, 상기 설명 전반에 걸쳐 참조될 수도 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들, 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 자기 입자들, 광학 필드들 또는 광학 입자들, 또는 이들의 임의의 조합에 의해 표현될 수도 있다.

[0053]

당업자들은, 본 명세서에 기재된 실시예들과 관련하여 설명된 다양한 예시적인 로직 블록들, 구성들, 모듈들, 회로들, 및 알고리즘 단계들이 전자 하드웨어, 프로세서에 의해 실행되는 컴퓨터 소프트웨어, 또는 이 둘의 결합들로서 구현될 수도 있음을 추가적으로 인식할 것이다. 다양한 예시적인 컴포넌트들, 블록들, 구성들, 모듈들, 회로들, 및 단계들은 그들의 기능 관점들에서 일반적으로 상술되었다. 그러한 기능이 하드웨어로 구현되는지 또는 프로세서 실행가능한 명령들로 구현되는지 여부는 특정 애플리케이션, 및 전체 시스템에 부과된 설계 제약들에 의존한다. 당업자들은 설명된 기능을 각각의 특정 애플리케이션에 대한 다양한 방식들로 구현할 수도 있지만, 그러한 구현 결정들이 본 개시내용의 범위를 벗어나게 하는 것으로서 해석되지는 않아야 한다.

[0054]

본 명세서에 기재된 실시예들과 관련하여 설명된 방법 또는 알고리즘의 단계들은 직접 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로, 또는 이 둘의 조합으로 구현될 수 있다. 소프트웨어 모듈은, 랜덤 액세스 메모리(RAM), 플래시 메모리, 판독-전용 메모리(ROM), 프로그래밍가능 판독-전용 메모리(PROM), 소거가능한 프로그래밍가능 판독-전용 메모리(EPROM), 전기적으로 소거가능한 프로그래밍가능 판독-전용 메모리(EEPROM), 레지스터들, 하드 디스크, 탈착식 디스크, 컴팩트 디스크 판독-전용 메모리(CD-ROM), 또는 당업계에 알려진 임의의 다른 형태의 비-일시적인 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독하고, 저장 매체에 정보를 기입할 수 있도록 프로세서에 커플링된다. 대안적으로, 저장 매체는 프로세서에 통합될 수 있다. 프로세서 및 저장 매체는 주문형 집적 회로(ASIC)에 상주할 수 있다. ASIC는 컴퓨팅 디바이스 또는 사용자 단말에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 컴퓨팅 디바이스 또는 사용자 단말에서 개별 컴포넌트들로서 상주할 수 있다.

[0055]

기재된 실시예의 이전 설명은 당업자가 기재된 실시예들을 사용하거나 또는 실시할 수 있도록 제공된다. 이들 실시예들에 대한 다양한 변형들은 당업자들에게 용이하게 명백할 것이며, 본 명세서에서 정의된 원리들은 본 개시내용의 범위를 벗어나지 않으면서 다른 실시예들에 적용될 수 있다. 따라서, 본 개시내용은 본 명세서에 나타낸 실시예들로 제한되도록 의도되는 것이 아니라, 다음의 청구항들에 의해 정의된 바와 같은 원리들 및 신규한 특성들과 일치하는 가능한 가장 넓은 범위에 부합할 것이다.

Claims (20)

- 장치로서,

증폭기;

상기 증폭기의 입력에 커플링된 제 1 인덕터;

상기 제 1 인덕터에 유도가능하게 커플링되고 그리고 제 1 공급 노드에 상기 증폭기를 커플링하는 제 2 인덕터; 및

상기 제 1 인덕터에 그리고 상기 제 2 인덕터에 유도가능하게 커플링되고 그리고 제 2 공급 노드에 상기 증폭기를 커플링하는 제 3 인덕터를 포함하는,

장치. - 제 1 항에 있어서,

상기 제 1 인덕터는 상기 증폭기의 상기 입력에 연결되고,

상기 제 2 인덕터는 상기 제 1 공급 노드에 상기 증폭기를 연결하는 제 2 변성(degenerative) 인덕터이며,

상기 제 3 인덕터는 상기 제 2 공급 노드에 상기 증폭기를 연결하는 제 3 변성 인덕터인,

장치. - 제 1 항에 있어서,

상기 제 2 인덕터 및 상기 제 3 인덕터 둘 다는, 인덕터 계수에 의해 상기 제 1 인덕터에 유도가능하게 커플링되는,

장치. - 제 3 항에 있어서,

상기 인덕터 계수의 값은 상기 증폭기의 임피던스를 튜닝하도록 수정되는,

장치. - 제 1 항에 있어서,

상기 제 1 인덕터는 션트 인덕터인,

장치. - 제 5 항에 있어서,

상기 제 1 공급 노드는 전압 공급기에 대응하고,

상기 제 2 공급 노드는 접지에 대응하며,

상기 션트 인덕터의 제 1 단자는 접지에 커플링되고,

상기 션트 인덕터의 제 2 단자는 상기 증폭기의 상기 입력에 커플링되는,

장치. - 제 1 항에 있어서,

상기 제 1 인덕터는 직렬 커플링된 인덕터인,

장치. - 제 7 항에 있어서,

상기 직렬 커플링된 인덕터의 네거티브 단자는 상기 증폭기의 상기 입력에 커플링되고,

상기 직렬 커플링된 인덕터의 제 1 단자는 입력 신호를 수신하도록 커플링되는,

장치. - 제 1 항에 있어서,

제 2 증폭기를 더 포함하는,

장치. - 제 9 항에 있어서,

상기 증폭기는 제 1 LNA(low noise amplifier)를 포함하고, 상기 제 2 증폭기는 제 2 LNA를 포함하며,

상기 제 1 LNA는 제 1 주파수 대역의 신호들을 증폭시키도록 구성되고, 상기 제 2 LNA는 제 2 주파수 대역의 신호들을 증폭시키도록 구성되는,

장치. - 제 10 항에 있어서,

상기 제 1 주파수 대역은 LTE(long term evolution) 주파수 대역을 포함하고,

상기 제 2 주파수 대역은 UHB(ultra high frequency band)를 포함하는,

장치. - 제 10 항에 있어서,

상기 제 2 증폭기는, 제 4 인덕터, 제 5 인덕터, 및 제 6 인덕터를 포함하는 3중-커플링된 인덕터에 커플링되는,

장치. - 제 12 항에 있어서,

상기 제 1 LNA는 제 1 스위치를 통해 입력에 커플링되고,

상기 제 2 LNA는 제 2 스위치를 통해 상기 입력에 커플링되는,

장치. - 제 13 항에 있어서,

상기 제 1 LNA는 제 1 변압기를 통해 제 1 혼합기에 커플링되고,

상기 제 2 LNA는 제 2 변압기를 통해 제 2 혼합기에 커플링되는,

장치. - 제 1 항에 있어서,

상기 제 1 인덕터, 상기 제 2 인덕터, 및 상기 제 3 인덕터는 중첩된 루프들(nested loops)에 배열되는,

장치. - 신호 증폭 방법으로서,

증폭기의 입력에서 제 1 신호를 수신하는 단계 - 상기 입력은 제 1 인덕터에 커플링됨 -; 및

증폭된 출력 신호를 제공하기 위해 상기 증폭기에서 상기 제 1 신호를 증폭시키는 단계를 포함하고,

상기 증폭기는 상기 제 1 인덕터에 유도가능하게 커플링된 제 2 인덕터에 의해 제 1 공급 노드에 커플링되고,

상기 증폭기는 상기 제 1 인덕터에 유도가능하게 커플링된 제 3 인덕터에 의해 제 2 공급 노드에 커플링되는,

장치. - 제 16 항에 있어서,

제 2 증폭기에서 제 2 신호를 증폭시키는 단계를 더 포함하고,

상기 제 1 신호는 LTE(long term evolution) 주파수 대역 신호를 포함하고,

상기 제 2 신호는 UHB(ultra high frequency band) 신호를 포함하는,

장치. - 장치로서,

증폭시키기 위한 수단의 입력에서 신호를 증폭시키기 위한 수단;

제 1 공급 노드에 상기 증폭시키기 위한 수단을 커플링하기 위한 제 1 수단;

제 2 공급 노드에 상기 증폭시키기 위한 수단을 커플링하기 위한 제 2 수단; 및

상기 증폭시키기 위한 수단의 상기 입력에 인덕턴스를 제공하기 위한 수단을 포함하고,

상기 인덕턴스를 제공하기 위한 수단은, 상기 커플링하기 위한 제 1 수단 및 상기 커플링하기 위한 제 2 수단에 유도가능하게 커플링되는,

장치. - 제 18 항에 있어서,

상기 제 1 공급 노드는 전압 공급기에 대응하고,

상기 제 2 공급 노드는 접지에 대응하는,

장치. - 제 18 항에 있어서,

증폭시키기 위한 제 2 수단을 더 포함하고,

상기 증폭시키기 위한 수단은 제 1 LNA(low noise amplifier)를 포함하고, 상기 증폭시키기 위한 제 2 수단은 제 2 LNA를 포함하며,

상기 제 1 LNA는 제 1 주파수 대역의 신호들을 증폭시키고, 상기 제 2 LNA는 제 2 주파수 대역의 신호들을 증폭시키는,

장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/560,285 US9853614B2 (en) | 2014-12-04 | 2014-12-04 | Amplifier with triple-coupled inductors |

| US14/560,285 | 2014-12-04 | ||

| PCT/US2015/060801 WO2016089579A1 (en) | 2014-12-04 | 2015-11-16 | Amplifier with triple-coupled inductors |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170090421A true KR20170090421A (ko) | 2017-08-07 |

Family

ID=54697700

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177014276A KR20170090421A (ko) | 2014-12-04 | 2015-11-16 | 3중-커플링된 인덕터들을 갖는 증폭기 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9853614B2 (ko) |

| EP (1) | EP3227999B1 (ko) |

| JP (1) | JP2017536779A (ko) |

| KR (1) | KR20170090421A (ko) |

| CN (1) | CN107078701A (ko) |

| BR (1) | BR112017011797A2 (ko) |

| WO (1) | WO2016089579A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200006920A (ko) * | 2018-07-11 | 2020-01-21 | 주식회사 인스파워 | 전력 증폭기 |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6386312B2 (ja) * | 2014-09-09 | 2018-09-05 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US9917555B2 (en) * | 2015-12-17 | 2018-03-13 | Twaiwan Semiconductor Manufactoring Company, Ltd. | Amplifier and method of operating same |

| US9825597B2 (en) * | 2015-12-30 | 2017-11-21 | Skyworks Solutions, Inc. | Impedance transformation circuit for amplifier |

| FR3047606B1 (fr) * | 2016-02-04 | 2018-03-09 | Stmicroelectronics Sa | Amplificateur faible bruit entierement integre. |

| WO2017173119A1 (en) | 2016-04-01 | 2017-10-05 | Skyworks Solutions, Inc. | Multi-mode stacked amplifier |

| US10062670B2 (en) | 2016-04-18 | 2018-08-28 | Skyworks Solutions, Inc. | Radio frequency system-in-package with stacked clocking crystal |

| KR102629723B1 (ko) | 2016-04-19 | 2024-01-30 | 스카이워크스 솔루션즈, 인코포레이티드 | 무선 주파수 모듈의 선택적 차폐 |

| US10211795B2 (en) | 2016-07-21 | 2019-02-19 | Skyworks Solutions, Inc. | Impedance transformation circuit and overload protection for low noise amplifier |

| KR102504292B1 (ko) * | 2016-11-18 | 2023-02-28 | 삼성전자 주식회사 | 광대역 rf 신호를 수신하는 수신기, 수신기를 포함하는 무선 통신 장치 및 무선 통신 장치의 동작 방법 |

| US10250195B2 (en) * | 2016-11-18 | 2019-04-02 | Samsung Electronics Co., Ltd. | Receiver receiving wideband radio frequency signal, wireless communication device including the same, and method of operating the wireless communication device |

| TWI800014B (zh) * | 2016-12-29 | 2023-04-21 | 美商天工方案公司 | 前端系統及相關裝置、積體電路、模組及方法 |

| US10454432B2 (en) | 2016-12-29 | 2019-10-22 | Skyworks Solutions, Inc. | Radio frequency amplifiers with an injection-locked oscillator driver stage and a stacked output stage |

| US10515924B2 (en) | 2017-03-10 | 2019-12-24 | Skyworks Solutions, Inc. | Radio frequency modules |

| US10171037B2 (en) | 2017-04-25 | 2019-01-01 | Qorvo Us, Inc. | Multi-mode power management system supporting fifth-generation new radio |

| US10103926B1 (en) * | 2017-08-08 | 2018-10-16 | Qorvo Us, Inc. | Multi-mode power management circuit |

| US10879852B2 (en) | 2017-08-08 | 2020-12-29 | Qorvo Us, Inc. | Power management circuit and related radio frequency front-end circuit |

| US10090809B1 (en) | 2017-08-15 | 2018-10-02 | Qorvo Us, Inc. | Multi-mode mobile power management circuit |

| US10326408B2 (en) | 2017-09-18 | 2019-06-18 | Qorvo Us, Inc. | Envelope tracking power management circuit |

| US10553530B2 (en) | 2017-09-29 | 2020-02-04 | Qorvo Us, Inc. | Three-dimensional (3D) inductor-capacitor (LC) circuit |

| GB201717857D0 (en) | 2017-10-30 | 2017-12-13 | Novelda As | Amplifier |

| US10965261B2 (en) * | 2017-12-05 | 2021-03-30 | Qualcomm Incorporated | Power amplifier circuit |

| US10361667B2 (en) | 2017-12-08 | 2019-07-23 | Qorvo Us, Inc. | Low noise amplifier circuit |

| US10097145B1 (en) | 2017-12-11 | 2018-10-09 | Qorvo Us, Inc. | Multi-mode power management circuit |

| US10645787B2 (en) | 2017-12-13 | 2020-05-05 | General Electric Company | System and method for providing electrical power to a load |

| JP6479280B1 (ja) * | 2018-03-08 | 2019-03-06 | 三菱電機株式会社 | 可変インダクタ回路 |

| JP2019192992A (ja) * | 2018-04-20 | 2019-10-31 | 株式会社村田製作所 | フロントエンドモジュールおよび通信装置 |

| CN110149099B (zh) * | 2019-06-27 | 2024-08-20 | 中国电子科技集团公司第五十四研究所 | 一种基于Cascode电感异位耦合的低噪声放大器 |

| US11159191B1 (en) * | 2020-09-11 | 2021-10-26 | Apple Inc. | Wireless amplifier circuitry for carrier aggregation |

| US20230188096A1 (en) * | 2021-12-10 | 2023-06-15 | Qorvo Us, Inc. | Complementary balanced low-noise amplifier circuit |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3705932C1 (de) * | 1987-02-25 | 1988-09-22 | Telefunken Electronic Gmbh | Verstaerker |

| US5164682A (en) * | 1991-07-24 | 1992-11-17 | Taralp Guener | Two-port wideband bipolar transistor amplifiers |

| US6407640B1 (en) * | 2000-09-22 | 2002-06-18 | Qualcomm, Incorporated | Two-stage LNA with good linearity |

| JP4094239B2 (ja) * | 2001-02-19 | 2008-06-04 | 富士通株式会社 | 増幅器 |

| US6949979B2 (en) | 2002-12-05 | 2005-09-27 | Memetics Technology Co. LTD | Designing methods and circuits for multi-band electronic circuits |

| US6940365B2 (en) * | 2003-07-18 | 2005-09-06 | Rfstream Corporation | Methods and apparatus for an improved discrete LC filter |

| KR100644273B1 (ko) * | 2004-12-21 | 2006-11-10 | 한국전자통신연구원 | 광대역 가변 입력 매칭 저잡음 증폭기 |

| KR100667303B1 (ko) * | 2005-02-01 | 2007-01-12 | 삼성전자주식회사 | Uwb용 lna |

| US7489192B2 (en) * | 2006-05-22 | 2009-02-10 | Theta Microelectronics, Inc. | Low-noise amplifiers |

| KR100882103B1 (ko) * | 2007-09-28 | 2009-02-06 | 삼성전기주식회사 | 수동 소자로 이루어진 다중대역 출력 임피던스 정합 회로,수동 소자로 이루어진 다중대역 입력 임피던스 정합 회로를갖는 증폭기 및 수동 소자로 이루어진 다중대역 입출력임피던스 정합 회로를 갖는 증폭기 |

| TWI342666B (en) * | 2007-11-12 | 2011-05-21 | Univ Nat Taiwan | Wideband low noise amplifiers |

| US8279018B1 (en) | 2009-03-16 | 2012-10-02 | Marvell International Ltd. | Trifila balun for wireless transceiver |

| US8229367B2 (en) | 2009-04-14 | 2012-07-24 | Qualcomm, Incorporated | Low noise amplifier with combined input matching, balun, and transmit/receive switch |

| US8102213B2 (en) | 2009-07-23 | 2012-01-24 | Qualcomm, Incorporated | Multi-mode low noise amplifier with transformer source degeneration |

| US8626084B2 (en) * | 2010-05-13 | 2014-01-07 | Qualcomm, Incorporated | Area efficient concurrent matching transceiver |

| US8760240B2 (en) | 2010-09-15 | 2014-06-24 | Wilocity, Ltd. | Method for designing coupling-function based millimeter wave electrical elements |

| WO2012088520A2 (en) * | 2010-12-23 | 2012-06-28 | Marvell Asia Pte, Ltd. | Techniques on input transformer to push the op1db higher in power amplifier design |

| US12081243B2 (en) * | 2011-08-16 | 2024-09-03 | Qualcomm Incorporated | Low noise amplifiers with combined outputs |

| US8975966B2 (en) | 2012-03-07 | 2015-03-10 | Qualcomm Incorporated | Shared bypass capacitor matching network |

| US20140015614A1 (en) * | 2012-07-10 | 2014-01-16 | Infineon Technologies Ag | System and Method for a Low Noise Amplifier |

| US8912845B2 (en) * | 2013-01-07 | 2014-12-16 | Analog Devices, Inc. | Multiple winding transformer coupled amplifier |

| US9059665B2 (en) | 2013-02-22 | 2015-06-16 | Qualcomm Incorporated | Amplifiers with multiple outputs and configurable degeneration inductor |

| US9106185B2 (en) | 2013-03-11 | 2015-08-11 | Qualcomm Incorporated | Amplifiers with inductive degeneration and configurable gain and input matching |

| US9350310B2 (en) | 2013-05-24 | 2016-05-24 | Qualcomm Incorporated | Receiver front end for carrier aggregation |

| CN103457555B (zh) * | 2013-09-12 | 2016-04-13 | 东南大学 | 采用任意耦合系数片上变压器的毫米波放大器单向化网络 |

| US9692368B2 (en) * | 2014-09-09 | 2017-06-27 | Qualcomm Incorporated | Dual-band low noise amplifier |

| US9473101B2 (en) * | 2015-02-09 | 2016-10-18 | Qualcomm Incorporated | Amplifier with integral notch filter |

-

2014

- 2014-12-04 US US14/560,285 patent/US9853614B2/en active Active

-

2015

- 2015-11-16 JP JP2017529791A patent/JP2017536779A/ja active Pending

- 2015-11-16 EP EP15798658.9A patent/EP3227999B1/en active Active

- 2015-11-16 WO PCT/US2015/060801 patent/WO2016089579A1/en active Application Filing

- 2015-11-16 BR BR112017011797A patent/BR112017011797A2/pt not_active Application Discontinuation

- 2015-11-16 KR KR1020177014276A patent/KR20170090421A/ko unknown

- 2015-11-16 CN CN201580063120.9A patent/CN107078701A/zh active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200006920A (ko) * | 2018-07-11 | 2020-01-21 | 주식회사 인스파워 | 전력 증폭기 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3227999A1 (en) | 2017-10-11 |

| US20160164476A1 (en) | 2016-06-09 |

| JP2017536779A (ja) | 2017-12-07 |

| US9853614B2 (en) | 2017-12-26 |

| WO2016089579A1 (en) | 2016-06-09 |

| CN107078701A (zh) | 2017-08-18 |

| BR112017011797A2 (pt) | 2018-02-27 |

| EP3227999B1 (en) | 2018-06-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3227999B1 (en) | Amplifier with triple-coupled inductors | |

| US9712195B2 (en) | Radio frequency low noise amplifier with on-chip matching and built-in tunable filter | |

| US9692368B2 (en) | Dual-band low noise amplifier | |

| KR102504244B1 (ko) | 복수의 lna들 간의 캐스캐이딩된 스위치 | |

| US8903343B2 (en) | Single-input multiple-output amplifiers with independent gain control per output | |

| US9419560B2 (en) | Low power multi-stacked power amplifier | |

| KR101793148B1 (ko) | 멀티-대역 전력 증폭기 | |

| JP6224849B2 (ja) | 信号のブロッカー成分のフィルタリング | |

| EP3189588B1 (en) | Multi-band low noise amplifier | |

| US20160079946A1 (en) | Multi-band low noise amplifier with a shared degeneration inductor |