KR20160076531A - 다차원 범위에 걸쳐 분리가능한 서브 시스템들을 포함하는 시스템의 평가 - Google Patents

다차원 범위에 걸쳐 분리가능한 서브 시스템들을 포함하는 시스템의 평가 Download PDFInfo

- Publication number

- KR20160076531A KR20160076531A KR1020167013660A KR20167013660A KR20160076531A KR 20160076531 A KR20160076531 A KR 20160076531A KR 1020167013660 A KR1020167013660 A KR 1020167013660A KR 20167013660 A KR20167013660 A KR 20167013660A KR 20160076531 A KR20160076531 A KR 20160076531A

- Authority

- KR

- South Korea

- Prior art keywords

- subsystems

- parameter

- subsystem

- neurons

- sweep

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/082—Learning methods modifying the architecture, e.g. adding, deleting or silencing nodes or connections

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/049—Temporal neural networks, e.g. delay elements, oscillating neurons or pulsed inputs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/10—Interfaces, programming languages or software development kits, e.g. for simulating neural networks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/10—Interfaces, programming languages or software development kits, e.g. for simulating neural networks

- G06N3/105—Shells for specifying net layout

-

- G—PHYSICS

- G08—SIGNALLING

- G08B—SIGNALLING OR CALLING SYSTEMS; ORDER TELEGRAPHS; ALARM SYSTEMS

- G08B17/00—Fire alarms; Alarms responsive to explosion

- G08B17/005—Fire alarms; Alarms responsive to explosion for forest fires, e.g. detecting fires spread over a large or outdoors area

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Health & Medical Sciences (AREA)

- Computing Systems (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- Computational Linguistics (AREA)

- Data Mining & Analysis (AREA)

- Evolutionary Computation (AREA)

- Life Sciences & Earth Sciences (AREA)

- Molecular Biology (AREA)

- Artificial Intelligence (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Health & Medical Sciences (AREA)

- Image Analysis (AREA)

- Feedback Control In General (AREA)

- Management, Administration, Business Operations System, And Electronic Commerce (AREA)

- Testing And Monitoring For Control Systems (AREA)

- Testing Or Calibration Of Command Recording Devices (AREA)

Abstract

인공 뉴럴 네트워크는 소정의 입력 파라미터들의 영향을 테스트하도록 구성될 수도 있다. 시스템 성능을 변경하지 않을 수도 있는 테스트 런들을 회피하기 위해서 그리고 테스팅 효율을 개선하기 위해서, 뉴런들 또는 뉴런들의 그룹들에 대한 입력 파라미터들의 영향이 그러한 그룹들에 대한 소정의 파라미터들의 영향에 기초하여 뉴런들을 그룹들로 분류하기 위해 결정될 수도 있다. 그룹들은 그룹들의 상호접속된 성질에 기초하여 그리고 일 그룹에서의 뉴런들의 출력이 다른 것의 동작에 영향을 미칠 수도 있는지 여부에 기초하여 직렬로 및/또는 병렬로 오더링될 수도 있다. 그룹 성능에 영향을 미치지 않는 파라미터들은, 시스템 테스트들을 런하기 전에 특정 그룹에 대한 입력들로서 프루닝될 수도 있고, 이로써 테스팅 동안 프로세싱 리소스들을 보전한다.

Description

본 개시물의 소정의 양태들은 일반적으로 뉴럴 시스템 엔지니어링에 관한 것이고, 특히 파라미터 탐색의 실행 시간을 개선하는 것에 의한 뉴럴 네트워크의 개발 및 테스팅에 관한 것이다.

인공 뉴럴 네트워크들은, 종래의 연산 기술들이 번거롭거나 비실용적이거나 또는 부적절한 소정의 어플리케이션들에 혁신적이고 유용한 연산 기술들을 제공할 수도 있다. 인공 뉴럴 네트워크들은 생물학적 뉴럴 네트워크들에 있어서의 대응하는 구조 및/또는 기능을 가질 수도 있다. 인공 뉴런들 (즉, 뉴런 모델들) 의 상호접속된 그룹을 포함할 수도 있는 인공 뉴럴 네트워크는 연산 디바이스이거나 또는 연산 디바이스에 의해 수행될 방법을 나타낸다. 인공 뉴럴 네트워크들이 관측들로부터 기능을 추론할 수 있기 때문에, 그러한 네트워크들은, 태스크 또는 데이터의 복잡성이 종래 기술들에 의한 기능의 설계를 부담스럽게 만드는 어플리케이션들에서 특히 유용하다.

일 양태에서, 무선 통신의 방법이 개시된다. 방법은, 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 서브 시스템들을 직렬화하는 단계, 및/또는 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 서브 시스템들을 병렬화하는 단계를 포함한다. 방법은, 각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝 (pruning) 하는 단계를 더 포함한다.

다른 양태는, 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 서브 시스템들을 직렬화하는 수단, 및/또는 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 서브 시스템들을 병렬화하는 수단을 포함하는 장치를 개시한다. 장치는, 각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하는 수단을 더 포함한다.

다른 양태에서, 비일시적 컴퓨터 판독가능 매체를 갖는 무선 네트워크에서의 무선 통신을 위한 컴퓨터 프로그램 제품이 개시된다. 컴퓨터 판독가능 매체는 비일시적 프로그램 코드가 기록되고, 프로그램 코드는, 프로세서(들) 에 의해 실행될 때, 프로세서(들) 로 하여금, 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 서브 시스템들을 직렬화하고, 및/또는 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 서브 시스템들을 병렬화하는 동작들을 수행하게 한다. 프로그램 코드는 또한, 프로세서(들) 로 하여금 각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하게 한다.

다른 양태는 메모리 및 메모리에 커플링된 적어도 하나의 프로세서를 갖는 무선 통신을 개시한다. 프로세서(들) 은, 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 서브 시스템들을 직렬화하고, 및/또는 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 서브 시스템들을 병렬화하도록 구성된다. 프로세서(들)은 또한, 각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하도록 구성된다.

개시물의 부가적인 피처들 및 이점들은 하기에서 기재될 것이다. 당업자는 본 개시물의 동일한 목적들을 수행하기 위해 다른 구조들을 수정하거나 설계하기 위한 기초로서 이 개시물이 쉽게 활용될 수도 있다는 것을 이해하여야 한다. 또한, 당업자는 그러한 등가의 구성들은 첨부된 청구항들에서 기술되는 바와 같은 개시물의 교시들로부터 벗어나지 않는다는 것을 알아야 한다. 추가적인 목적들 및 이점들과 함께 동작의 체계화 및 방법의 양자에 관하여 개시물의 특징적인 것으로 여겨지는 신규 피처들은, 첨부 도면들과 관련하여 고려될 때 다음의 기재로부터 더 잘 이해될 것이다. 하지만, 도면들의 각각은 단지 도시 및 설명을 위해 제공되고 본 개시물의 제한들의 정의로서 의도되지 않는다는 것을 명백히 이해해야 한다.

본 개시물의 피처들, 성질, 및 이점들은 같은 참조 문자들이 전체에 걸쳐 상응하여 식별하는 도면들과 함께 취해질 때 하기에 기재된 상세한 설명으로부터 더 명백해질 것이다.

도 1 은 본 개시물의 소정 양태들에 따른 뉴런들의 예시적인 네트워크를 도시한다.

도 2 는 본 개시물의 소정 양태들에 따른 연산 네트워크 (뉴럴 시스템 또는 뉴럴 네트워크) 의 프로세싱 유닛 (뉴런) 의 예를 도시한다.

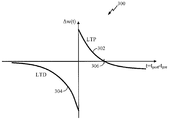

도 3 은 본 개시물의 소정 양태들에 따른 스파이크-타이밍 의존 가소성 (STDP; spike-timing dependent plasticity) 곡선의 예를 도시한다.

도 4 는 본 개시물의 소정 양태들에 따른 뉴런 모델의 거동을 정의하기 위한 포지티브 레짐 (positive regime) 및 네거티브 레짐 (negative regime) 의 예를 도시한다.

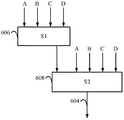

도 5a 및 도 5b 는 본 개시물의 양태들에 따른 뉴럴 네트워크의 예들을 도시한다.

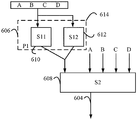

도 6a 내지 도 6d 는 본 개시물의 양태들에 따른 뉴럴 네트워크의 예들을 도시한다.

도 7 은 본 개시물의 일 양태에 다른 뉴럴 네트워크의 파라미터 평가를 개선하기 위한 방법을 도시하는 블록 다이어그램이다.

도 8 은 본 개시물의 일 양태에 따른 뉴럴 네트워크의 파라미터 평가를 개선하기 위한 기능들을 도시하는 블록 다이어그램이다.

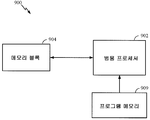

도 9 은 본 개시물의 소정 양태들에 따른 범용 프로세서를 사용하여 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

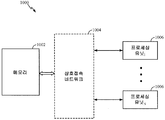

도 10 은 본 개시물의 소정 양태들에 따른 메모리가 개별 분산 프로세싱 유닛들과 인터페이싱될 수도 있는 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

도 11 는 본 개시물의 소정 양태들에 따른 분산 메모리들 및 분산 프로세싱 유닛들에 기초한 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

도 12 은 본 개시물의 소정 양태들에 따른 뉴럴 네트워크의 예시적인 구현을 도시한다.

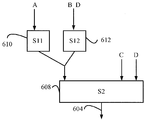

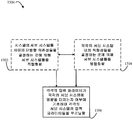

도 13 은 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프 (sweep) 를 수행하기 위한 방법을 도시하는 블록 다이어그램이다.

도 1 은 본 개시물의 소정 양태들에 따른 뉴런들의 예시적인 네트워크를 도시한다.

도 2 는 본 개시물의 소정 양태들에 따른 연산 네트워크 (뉴럴 시스템 또는 뉴럴 네트워크) 의 프로세싱 유닛 (뉴런) 의 예를 도시한다.

도 3 은 본 개시물의 소정 양태들에 따른 스파이크-타이밍 의존 가소성 (STDP; spike-timing dependent plasticity) 곡선의 예를 도시한다.

도 4 는 본 개시물의 소정 양태들에 따른 뉴런 모델의 거동을 정의하기 위한 포지티브 레짐 (positive regime) 및 네거티브 레짐 (negative regime) 의 예를 도시한다.

도 5a 및 도 5b 는 본 개시물의 양태들에 따른 뉴럴 네트워크의 예들을 도시한다.

도 6a 내지 도 6d 는 본 개시물의 양태들에 따른 뉴럴 네트워크의 예들을 도시한다.

도 7 은 본 개시물의 일 양태에 다른 뉴럴 네트워크의 파라미터 평가를 개선하기 위한 방법을 도시하는 블록 다이어그램이다.

도 8 은 본 개시물의 일 양태에 따른 뉴럴 네트워크의 파라미터 평가를 개선하기 위한 기능들을 도시하는 블록 다이어그램이다.

도 9 은 본 개시물의 소정 양태들에 따른 범용 프로세서를 사용하여 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

도 10 은 본 개시물의 소정 양태들에 따른 메모리가 개별 분산 프로세싱 유닛들과 인터페이싱될 수도 있는 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

도 11 는 본 개시물의 소정 양태들에 따른 분산 메모리들 및 분산 프로세싱 유닛들에 기초한 뉴럴 네트워크를 설계하는 예시적인 구현을 도시한다.

도 12 은 본 개시물의 소정 양태들에 따른 뉴럴 네트워크의 예시적인 구현을 도시한다.

도 13 은 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프 (sweep) 를 수행하기 위한 방법을 도시하는 블록 다이어그램이다.

첨부된 도면들과 함께 하기에 기술되는 상세한 설명은, 다양한 구성들의 설명으로서 의도되고 단지 본 명세서에 기재된 개념들이 실시될 수도 있는 구성들만을 나타내는 것으로 의도되지 않는다. 상세한 설명은 다양한 개념들의 철저한 이해를 제공하기 위해 특정 상세들을 포함한다. 하지만, 이러한 특정 상세들 없이도 이들 개념들이 실시될 수도 있다는 것이 당업자에게 자명할 것이다. 일부 경우들에서, 주지된 구조들 및 컴포넌트들은 그러한 개념들을 모호하게 하는 것을 회피하기 위해서 블록 다이어그램으로 나타낸다.

교시들에 기초하여, 당업자는, 본 개시물의 임의의 다른 양태와 독립적으로 구현되든 또는 결합되든, 본 개시물의 범위가 본 개시물의 임의의 양태를 커버하도록 의도됨을 인식할 것이다. 예를 들어, 설명된 임의의 수의 양태들을 이용하여 일 장치가 구현될 수도 있거나 일 방법이 실시될 수도 있다. 부가적으로, 본 개시물의 범위는, 설명된 본 개시물의 다양한 양태들에 부가하여 또는 그 이외에 구조 및 기능, 또는 다른 구조, 기능을 이용하여 실시되는 그러한 장치 또는 방법을 커버하도록 의도된다. 개시된 본 개시물의 임의의 양태는 청구항의 하나 이상의 엘리먼트들에 의해 구현될 수도 있음을 이해해야 한다.

단어 "예시적인" 은 "예, 예증, 또는 예시로서 작용하는" 을 의미하도록 본 명세서에서 사용된다. "예시적인" 것으로서 본 명세서에서 설명되는 임의의 양태가 다른 양태들에 비해 반드시 선호되거나 유리한 것으로서 해석되지는 않아야 한다.

소정 양태들이 본 명세서에서 설명되지만, 이들 양태들의 다수의 변형들 및 치환들은 본 개시물의 범위 내에 있다. 선호된 양태들의 일부 이익들 및 이점들이 언급되지만, 본 개시물의 범위는 특정 이익들, 사용들, 또는 목적들에 한정되도록 의도되지 않는다. 대신, 본 개시물의 양태들은 상이한 기술들, 시스템 구성들, 네트워크들, 및 프로토콜들에 널리 적용가능하도록 의도되며, 이들 중 일부는 도면들에서, 그리고 선호된 양태들의 다음의 설명에서 예로써 예시된다. 상세한 설명 및 도면들은 한정하는 것보다는 본 개시물의 단지 예시일 뿐이며, 본 개시물의 범위는 첨부된 청구항들 및 그 균등물들에 의해 정의된다.

예시적인 뉴럴 시스템, 트레이닝 및 동작

도 1 은 본 개시물의 소정 양태들에 따른 뉴런들의 다중 레벨들을 갖는 예시적인 인공 뉴럴 시스템 (100) 을 도시한다. 뉴럴 시스템 (100) 은 시냅스 접속들 (즉, 피드-포워드 접속들) 의 네트워크 (104) 를 통해 뉴런들의 다른 레벨 (106) 에 접속되는 뉴런들의 레벨 (102) 을 가질 수도 있다. 단순화를 위해, 비록 뉴런들의 오직 2개 레벨들만이 도 1 에 도시되어 있더라도, 뉴런들의 더 적거나 더 많은 레벨들이 뉴럴 시스템에 존재할 수도 있다. 뉴런들의 일부가 측면 접속들을 통해 동일한 계층의 다른 뉴런들에 접속할 수도 있다는 점을 유의해야 한다. 더욱이, 뉴런들의 일부는 피드백 접속들을 통해 이전 계층의 뉴런에 다시 접속할 수도 있다.

도 1 에 도시된 바와 같이, 레벨 (102) 의 각각의 뉴런은, 이전 레벨 (도 1 에 도시 안됨) 의 뉴런들에 의해 생성될 수도 있는 입력 신호 (108) 를 수신할 수도 있다. 신호 (108) 는 레벨 (102) 뉴런의 입력 (전류) 을 나타낼 수도 있다. 이 전류는 멤브레인 전위를 충전하기 위해 뉴런 멤브레인 상에 누적될 수도 있다. 멤브레인 전위가 그 임계 값에 도달할 경우, 뉴런은 발화하고, 뉴런들의 다음 레벨 (예를 들어, 레벨 (106)) 로 전송될 출력 스파이크를 생성할 수도 있다. 일부 경우들에서, 뉴런은 뉴런들의 다음 레벨로 신호를 연속적으로 송신할 수도 있다. 송신된 신호는 멤브레인 전위의 함수일 수도 있다. 그러한 거동은 하기에 기재되는 것과 같은 아날로그 및 디지털 구현들을 포함한, 하드웨어 및/또는 소프트웨어에서 에뮬레이션되거나 시뮬레이션될 수 있다.

생물학적 뉴런들에 있어서, 뉴런이 발화할 때 생성되는 출력 스파이크는 활동 전위로서 지칭된다. 이러한 전기 신호는 대략 100 mV 의 진폭 및 약 1 ms 의 지속기간을 갖는, 상대적으로 빠른, 일시적인, 신경 임펄스이다. 접속된 뉴런들의 시리즈를 갖는 뉴럴 시스템의 특정 실시형태 (예를 들어, 도 1 에서 뉴런들의 일 레벨로부터 다른 레벨로의 스파이크들의 전송) 에 있어서, 모든 활동 전위는 기본적으로 동일한 진폭 및 지속기간을 가지며, 따라서, 신호 내 정보는 진폭에 의해서라기 보다는 오히려 오직 스파이크들의 주파수 및 개수 또는 스파이크들의 시간에 의해서만 표현될 수도 있다. 활동 전위에 의해 반송되는 정보는 스파이크, 스파이킹된 뉴런, 및 다른 스파이크 또는 스파이크들에 대한 그 스파이크의 시간에 의해 결정될 수도 있다. 스파이크의 중요성은 하기에서 설명되는 바와 같이 뉴런들 사이의 접속에 가해지는 가중치에 의해 결정될 수도 있다.

도 1 에 도시된 바와 같이, 뉴런들의 일 레벨로부터 다른 레벨로의 스파이크들의 전송은 시냅스 접속들의 네트워크 (또는 간단히 "시냅스들") (104) 를 통해 달성될 수도 있다. 시냅스들 (104) 에 대해, 레벨 (102) 의 뉴런들은 시냅스전 뉴런들로 고려될 수도 있고 레벨 (106) 의 뉴런들은 시냅스후 뉴런들로 고려될 수도 있다. 시냅스들 (104) 은 레벨 (102) 뉴런들로부터 출력 신호들 (즉, 스파이크들) 을 수신하고 그 신호들을 조정가능한 시냅스 가중치들 (w1 (i,i+1),..., wP (i,i+1)) 에 따라 스케일링될 수도 있으며, 여기서 P 는 레벨들 (102 및 106) 의 뉴런들 사이의 시냅스 접속들의 총 개수이고, i 는 뉴런 레벨의 표시자이다. 예를 들어, 도 1 의 예에서, i 는 뉴런 레벨 (102) 를 나타내고, i + 1 은 뉴런 레벨 (106) 을 나타낸다. 추가로, (스케일링된) 신호들은 레벨 (106) 에서의 각각의 뉴런의 입력 신호로서 결합될 수도 있다. 레벨 (106) 에서의 모든 뉴런은 대응하는 결합된 입력 신호에 기초하여 출력 스파이크들 (110) 을 생성할 수도 있다. 출력 스파이크들 (110) 은 시냅스 접속들의 다른 네트워크 (도 1 에 도시되지 않음) 를 이용하여 뉴런들의 다른 레벨들로 전송될 수도 있다.

생물학적 시냅스들은 시냅스후 뉴런들에서의 흥분성 또는 억제성 (과분극하는) 활동들을 중재할 수 있으며, 또한 뉴런 신호들을 증폭하도록 기능할 수 있다. 흥분성 신호들은 멤브레인 전위를 탈분극시킨다 (즉, 휴지 전위에 대해 멤브레인 전위를 증가시킴). 멤브레인 전위를 임계 초과로 탈분극시키기 위해 충분한 흥분성 신호들이 소정 시간 기간 이내에 수신되면, 활동 전위가 시냅스후 뉴런에서 발생한다. 이에 반하여, 억제성 신호들은 일반적으로 멤브레인 전위를 과분극시킨다 (즉, 감소시킨다). 억제성 신호들은, 충분히 강하면, 흥분성 신호들의 총합을 상쇄시킬 수 있으며 멤브레인 전위가 임계에 도달하는 것을 방지할 수 있다. 시냅스 흥분을 상쇄시키는 것에 부가하여, 시냅스 억제는 자발적 활성 뉴런들에 걸쳐 강력한 제어를 행할 수 있다. 자발적 활성 뉴런은 추가적인 입력없이, 예를 들어, 그의 역학 또는 피드백으로 인해 스파이크하는 뉴런을 지칭한다. 이들 뉴런들에 있어서 활동 전위들의 자발적 생성을 억제함으로써, 시냅스 억제는 스컬쳐링 (sculpturing) 으로 일반적으로 지칭되는, 뉴런에서의 발화의 패턴을 형상화할 수 있다. 다양한 시냅스들 (104) 은 원하는 거동에 의존하여, 흥분성 또는 억제성 시냅스들의 임의의 조합으로서 작용할 수도 있다.

뉴럴 시스템 (100) 은 범용 프로세서, 디지털 신호 프로세서 (DSP), 주문형 집적회로 (ASIC), 필드 프로그램가능 게이트 어레이 (FPGA) 또는 다른 프로그램가능 로직 디바이스 (PLD), 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 프로세서에 의해 실행되는 소프트웨어 모듈, 또는 이들의 임의의 조합에 의해 에뮬레이션될 수도 있다. 뉴럴 시스템 (100) 은 이미지 및 패턴 인식, 머신 학습, 모터 제어 등과 같은 광범위한 어플리케이션들에서 활용될 수도 있다. 뉴럴 시스템 (100) 에서의 각각의 뉴런은 뉴런 회로로서 구현될 수도 있다. 출력 스파이크를 개시하는 임계 값까지 하전되는 뉴런 멤브레인은, 예를 들어, 그것을 통해 흐르는 전류를 적분하는 커패시터로서 구현될 수도 있다.

일 양태에 있어서, 커패시터는 뉴런 회로의 전류 적분 디바이스로서 제거될 수도 있고, 더 작은 멤리스터 엘리먼트가 대신 사용될 수도 있다. 이러한 접근법은 뉴런 회로들에 뿐만 아니라, 벌키 커패시터들이 전류 적분기들로서 활용되는 다양한 다른 어플리케이션들에 적용될 수도 있다. 부가적으로, 시냅스들 (104) 의 각각은 멤리스터 엘리먼트에 기초하여 구현될 수도 있으며, 여기서 시냅스 가중치 변경들은 멤리스터 저항의 변경들과 관련될 수도 있다. 나노미터 피처 사이징된 멤리스터들을 사용하여, 뉴런 회로 및 시냅스들의 면적이 실질적으로 감소될 수도 있으며, 이는 대규모 뉴럴 시스템 하드웨어 구현을 보다 실제적으로 구현할 수도 있다.

뉴럴 시스템 (100) 을 에뮬레이션하는 뉴럴 프로세서의 기능은 뉴런들 사이의 접속들의 강도들을 제어할 수도 있는, 시냅스 접속들의 가중치들에 의존할 수도 있다. 시냅스 가중치들은, 파워-다운된 이후 프로세서의 기능을 보존하기 위해 비-휘발성 메모리에 저장될 수도 있다. 일 양태에 있어서, 시냅스 가중치 메모리는 메인 뉴럴 프로세서 칩과는 별개의 외부 칩 상에 구현될 수도 있다. 시냅스 가중치 메모리는 교체가능한 메모리 카드로서 뉴럴 프로세서 칩과는 별개로 패키징될 수도 있다. 이는 뉴럴 프로세서에 다양한 기능들을 제공할 수도 있으며, 여기서 특정 기능은 뉴럴 프로세서에 현재 부착된 메모리 카드에 저장되는 시냅스 가중치들에 기초할 수도 있다.

도 2 는 본 개시물의 소정 양태들에 따른 연산 네트워크 (예를 들어, 뉴럴 시스템 또는 뉴럴 네트워크) 의 프로세싱 유닛 (예를 들어, 뉴런 또는 뉴런 회로 (202)) 의 예시적인 다이어그램 (200) 을 도시한다. 예를 들어, 뉴런 (202) 은 도 1 로부터의 레벨들 (102 및 106) 의 뉴런들 중 임의의 뉴런에 대응할 수도 있다. 뉴런 (202) 은 다중의 입력 신호들 (2041-204N(X19N)) 을 수신할 수도 있으며, 이 다중의 입력 신호들은 뉴럴 시스템 외부의 신호들, 또는 동일한 뉴럴 시스템의 다른 뉴런들에 의해 생성되는 신호들, 또는 이들 양자일 수도 있다. 입력 신호는 실수 값 및/또는 복소수 값인 전류, 컨덕턴스, 전압일 수도 있다. 입력 신호는 고정-소수점 또는 부동-소수점 표현을 가진 수치 값을 포함할 수도 있다. 이들 입력 신호들은 조정가능한 시냅스 가중치들 (2061-206N(W1-WN)) 에 따라 신호들을 스케일링하는 시냅스 접속들을 통해서 뉴런 (202) 으로 전달될 수도 있으며, 여기서 N 은 뉴런 (202) 의 입력 접속들의 총 개수일 수도 있다.

뉴런 (202) 은 스케일링된 입력 신호들을 결합하고, 그 결합된 스케일링된 입력들을 이용하여 출력 신호 (208) (즉, 신호 (Y)) 를 생성할 수도 있다. 출력 신호 (208) 는 실수 값 및/또는 복소수 값인 전류, 컨덕턴스, 전압일 수도 있다. 출력 신호는 고정-소수점 또는 부동-소수점 표현을 가진 수치 값일 수도 있다. 그 후, 출력 신호 (208) 는 동일한 뉴럴 시스템의 다른 뉴런들로의 입력 신호로서, 또는 동일한 뉴런 (202) 으로의 입력 신호로서, 또는 뉴럴 시스템의 출력으로서 전송될 수도 있다.

프로세싱 유닛 (뉴런 (202)) 은 전기 회로에 의해 에뮬레이션될 수도 있으며, 그 입력 및 출력 접속들은 시냅스 회로들을 가진 전기적 접속들에 의해 에뮬레이션될 수도 있다. 프로세싱 유닛 (202) 및 그 입력 및 출력 접속들은 또한 소프트웨어 코드에 의해 에뮬레이션될 수도 있다. 프로세싱 유닛 (202) 은 또한 전기 회로에 의해 에뮬레이션될 수도 있지만, 그 입력 및 출력 접속들은 소프트웨어 코드에 의해 에뮬레이션될 수도 있다. 일 양태에 있어서, 연산 네트워크에서의 프로세싱 유닛 (202) 은 아날로그 전기 회로일 수도 있다. 다른 양태에 있어서, 프로세싱 유닛 (202) 은 디지털 전기 회로일 수도 있다. 또 다른 양태에 있어서, 프로세싱 유닛 (202) 은 아날로그 및 디지털 컴포넌트들 양자와의 믹싱된 신호 전기 회로를 포함할 수도 있다. 연산 네트워크는 프로세싱 유닛들을 전술한 형태들 중 임의의 형태로 포함할 수도 있다. 그러한 프로세싱 유닛들을 이용한 연산 네트워크 (뉴럴 시스템 또는 뉴럴 네트워크) 는, 이미지 및 패턴 인식, 머신 학습, 모터 제어 등과 같은 광범위한 어플리케이션들에서 활용될 수도 있다.

뉴럴 네트워크를 트레이닝하는 과정 동안, 시냅스 가중치들 (예를 들어, 도 1 로부터의 가중치들 (w1 (i,i+1),..., wP (i,i+1)) 및/또는 도 2 로부터의 가중치들 (2061-206N)) 은 랜덤 값들로 초기화되고, 학습 규칙에 따라 증가되거나 감소될 수도 있다. 당업자는 학습 규칙의 일부 예들이 스파이크-타이밍 의존 가소성 (STDP) 학습 규칙, Hebb 규칙, Oja 규칙, BCM (Bienenstock-Copper-Munro) 규칙 등을 포함하지만 이에 제한되지 않는다는 것을 알 것이다. 소정의 양태들에서, 가중치들은 2개의 값들 (즉, 가중치들의 이봉 (bimodal) 분포) 중 하나로 정하거나 수렴할 수도 있다. 이 효과는 각각의 시냅스 가중치에 대한 비트수를 감소시키고, 시냅스 가중치들을 저장하는 메모리로부터 판독하고 그 메모리에 기입하는 속도를 증가시키고, 그리고 시냅스 메모리의 전력 및/또는 프로세서 소비를 감소시키는데 활용될 수 있다.

시냅스 타입

뉴럴 네트워크들의 하드웨어 및 소프트웨어 모델들에 있어서, 시냅스 관련 기능들의 프로세싱은 시냅스 타입에 기초할 수 있다. 시냅스 타입들은 비가소성 (non-plastic) 시냅스들 (가중치 및 지연의 변화들이 없음), 가소성 시냅스들 (가중치가 변할 수도 있음), 구조적 지연 가소성 시냅스들 (가중치 및 지연이 변할 수도 있음), 완전 가소성 시냅스들 (가중치, 지연 및 접속도가 변할 수도 있음), 및 그 변형예들 (예를 들어, 지연이 변할 수도 있지만, 가중치 또는 접속도에서의 변화는 없음) 을 포함할 수도 있다. 다중 타입들의 이점은 프로세싱이 세분될 수 있다는 점이다. 예를 들어, 비가소성 시냅스들은 가소성 기능들을 실행하지 (또는, 그러한 기능들이 완료하기를 대기하지) 않을 수도 있다. 유사하게, 지연 및 가중치 가소성은, 함께 또는 별개로, 순차적으로 또는 병렬로, 동작할 수도 있는 동작들로 세분될 수도 있다. 상이한 타입들의 시냅스들은, 적용하는 상이한 가소성 타입들의 각각에 대해 상이한 룩업 테이블들 또는 공식들 및 파라미터들을 가질 수도 있다. 따라서, 그 방법들은 시냅스의 타입에 대한 관련 테이블들, 공식들, 파라미터들에 액세스할 것이다. 다양한 시냅스 타입들의 사용은 인공 뉴럴 네트워크에 유연성 및 설정성 (configurability) 을 부가할 수도 있다.

시냅스 가소성과는 독립적으로 실행되는 스파이크-타이밍 의존 구조적 가소성의 구현들이 존재한다. 구조적 가소성은, 구조적 가소성 (즉, 지연 변화의 양) 이 사전-사후 스파이크 시간 차이의 직접 함수일 수도 있기 때문에, 가중치 크기에 어떠한 변화도 없더라도 (예를 들어, 가중치가 최소 또는 최대 값에 도달하였거나, 또는 일부 다른 이유로 인해 변화되지 않으면) 실행될 수도 있다. 대안적으로, 구조적 가소성은 가중치 변화량의 함수로서, 또는 가중치들 또는 가중치 변화들의 한계들에 관련된 조건들에 기초하여 설정될 수도 있다. 예를 들어, 시냅스 지연은 오직 가중치 변화가 발생할 때 또는 가중치들이 제로에 도달하면 변할 수도 있지만, 이들이 최대값에 있으면 변하지 않을 수도 있다. 하지만, 이들 프로세스들이 병렬화되어 메모리 액세스들의 수 및 중첩을 감소시킬 수 있도록 독립적인 기능들을 갖는 것이 유리할 수도 있다.

시냅스 가소성의 결정

신경가소성 (또는, 간단히 "가소성") 은 새로운 정보, 감각 자극, 발달, 손상, 또는 기능장애에 응답하여, 그 시냅스 접속들 및 거동을 변경하기 위한 뇌에서의 뉴런들 및 뉴럴 네트워크들의 역량이다. 가소성은 생물학에서의 학습 및 기억 뿐만 아니라 연산 신경과학 및 뉴럴 네트워크들에 대해 중요하다. (예를 들어, Hebbian 이론에 따른) 시냅스 가소성, 스파이크-타이밍 의존 가소성 (STDP), 비-시냅스 가소성, 활동 의존 가소성, 구조적 가소성, 및 항상적 가소성과 같은 다양한 형태들의 가소성이 연구되었다.

STDP 는 뉴런들 사이의 시냅스 접속들의 강도를 조정하는 학습 프로세스이다. 접속 강도들은 특정 뉴런의 출력 및 수신된 입력 스파이크들 (즉, 활동 전위들) 의 상대적인 타이밍에 기초하여 조정된다. STDP 프로세스 하에서, 특정 뉴런으로의 입력 스파이크가, 평균적으로, 그 뉴런의 출력 스파이크 직전에 발생하는 경향이 있으면, 장기 강화 (LTP) 가 발생할 수도 있다. 그 후, 그 특정 입력은 다소 더 강하게 이루어진다. 다른 한편으로, 입력 스파이크가, 평균적으로, 출력 스파이크 직후에 발생하는 경향이 있으면, 장기 억압 (LTD) 이 발생할 수도 있다. 그 후, 그 특정 입력이 다소 더 약하게 이루어지며, 따라서, "스파이크-타이밍 의존 가소성" 으로 명명한다. 결과적으로, 시냅스후 뉴런의 흥분의 원인일 수도 있는 입력들은 장래에 기여할 가능성이 훨씬 더 많게 이루어지지만, 시냅스후 스파이크의 원인이 아닌 입력들은 장래에 기여할 가능성이 적게 이루어진다. 프로세스는, 접속들의 초기 세트의 서브세트가 유지되는 한편 모든 나머지 영향이 중요하지 않은 레벨로 감소될 때까지 계속한다.

뉴런이 일반적으로, 그 입력들 중 다수가 짧은 기간 내에 발생할 때 (즉, 출력을 야기하기에 충분히 누적적인 입력들) 출력 스파이크를 생성하기 때문에, 통상적으로 남아 있는 입력들의 서브세트는 시간적으로 상관되려는 경향이 있는 입력들을 포함한다. 부가적으로, 출력 스파이크 전에 발생하는 입력들이 강화되기 때문에, 가장 이른 충분히 누적적인 상관의 표시를 제공하는 입력들이 결국 뉴런으로의 최종 입력이 될 것이다.

STDP 학습 규칙은 시냅스전 뉴런을 시냅스후 뉴런에 접속하는 시냅스의 시냅스 가중치를 시냅스전 뉴런의 스파이크 시간 (tpre) 과 시냅스후 뉴런의 스파이크 시간 (tpost) 사이의 시간 차이 (즉, t=tpost-tpre) 의 함수로서 효과적으로 적응시킬 수도 있다. STDP 의 통상적인 공식화 (formulation) 는, 시간 차이가 포지티브이면 (시냅스전 뉴런이 시냅스후 뉴런 이전에 발화하면) 시냅스 가중치를 증가시키고 (즉, 시냅스를 강화하고), 그리고 시간 차이가 네거티브이면 (시냅스후 뉴런이 시냅스전 뉴런 전에 발화하면) 시냅스 가중치를 감소시키는 (즉, 시냅스를 억압하는) 것이다.

STDP 프로세스에 있어서, 시간에 걸친 시냅스 가중치의 변화는 통상적으로, 다음으로 주어진 바와 같이, 지수적 감쇠를 이용하여 달성될 수도 있으며,

여기서, k+ 및 는 각각 포지티브 및 네거티브 시간 차이에 대한 시상수들이고, α+ 및 α- 는 대응하는 스케일링 크기들이고,μ는 포지티브 시간 차이 및/또는 네거티브 시간 차이에 적용될 수도 있는 오프셋이다.

도 3 은 STDP 에 따른 시냅스전 및 시냅스후 스파이크들의 상대적인 타이밍의 함수로서의 시냅스 가중치 변화의 예시적인 다이어그램 (300) 을 도시한다. 시냅스전 뉴런이 시냅스후 뉴런 이전에 발화하면, 대응하는 시냅스 가중치가, 그래프 (300) 의 부분 (302) 에 도시된 바와 같이, 증가될 수도 있다. 이 가중치 증가는 시냅스의 LTP 로서 지칭될 수 있다. LTP 의 양이 시냅스전 및 시냅스후 스파이크 시간들 사이의 차이의 함수로서 대략 지수적으로 감소할 수도 있다는 것이 그래프 부분 (302) 으로부터 관측될 수 있다. 발화의 역방향 순서는 시냅스 가중치를 감소시켜, 그래프 (300) 의 부분 (304) 에 도시된 바와 같이, 시냅스의 LTD 를 야기할 수도 있다.

도 3 에서의 그래프 (300) 에 도시된 바와 같이, 네거티브 오프셋 (μ) 은 STDP 그래프의 LTP (인과관계) 부분 (302) 에 적용될 수도 있다. x축 (y=0) 의 교차 포인트 (306) 는 계층 i-1 로부터의 인과관계 입력들에 대한 상관을 고려하기 위해 최대 시간 래그와 일치하도록 구성될 수도 있다. 프레임 기반 입력의 경우 (즉, 스파이크들 또는 펄스들의 특정 지속기간의 프레임인 입력), 오프셋 값 (μ) 은 프레임 경계를 반영하도록 연산될 수 있다. 프레임에 있어서의 제 1 입력 스파이크 (펄스) 는 시냅스후 전위에 의해 직접적으로 모델링될 때와 같이 또는 뉴럴 상태에 대한 효과의 관점에서 시간에 걸쳐서 감쇠하는 것으로 고려될 수도 있다. 프레임에 있어서의 제 2 입력 스파이크 (펄스) 가 특정 시간 프레임과 상관되거나 관련되는 것으로 고려되면, 프레임 전후의 관련 시간들은, 그 관련 시간들에서의 값이 상이할 수 있도록 (예를 들어, 일 프레임보다 큰 것에 대해 네거티브 및 일 프레임보다 작은 것에 대해 포지티브) STDP 곡선의 하나 이상의 부분들을 오프셋함으로써, 그 시간 프레임 경계에서 분리될 수도 있으며, 가소성 항들에서 상이하게 취급될 수도 있다. 예를 들어, 네거티브 오프셋 (μ) 은, 곡선이 실제로 프레임 시간보다 큰 사전-사후 시간에서 제로 아래로 가며 따라서 LTP 대신 LTD 의 부분이도록, LTP 를 오프셋하도록 설정될 수도 있다.

뉴런 모델들 및 동작

유용한 스파이킹 뉴런 모델을 설계하기 위한 일부 일반적인 원리들이 존재한다. 양호한 뉴런 모델은 2개의 연산 레짐들: 즉, 일치 검출 및 함수적 연산의 관점에서, 풍부한 전위 거동을 가질 수도 있다. 더욱이, 양호한 뉴런 모델은 시간 코딩을 허용하기 위해 2개의 엘리먼트들을 가질 것이다. 예를 들어, 입력들의 도달 시간은 출력 시간에 영향을 미치며 일치 검출은 좁은 시간 윈도우를 가질 수 있음. 부가적으로, 연산적으로 흥미를 끌기 위해서, 양호한 뉴런 모델은 연속적인 시간에 있어서 닫힌 형태의 해 (closed-form solution), 그리고 가까운 어트랙터들 (attractors) 및 새들 (saddle) 포인트들을 포함한 안정적인 거동을 가질 수도 있다. 즉, 유용한 뉴런 모델은, 풍부하고 현실적이고 생물학적으로 일관된 거동들을 모델링하는데 사용될 뿐만 아니라 뉴럴 회로들을 설계하고 역설계하는데 모두 사용될 수 있으며 그리고 실용적인 모델이다.

뉴런 모델은 입력 도달, 출력 스파이크 또는 내부든 또는 외부든 다른 이벤트와 같은 이벤트들에 의존할 수도 있다. 풍부한 거동 레파토리를 획득하기 위해, 복잡한 거동들을 나타낼 수 있는 상태 머신이 소망될 수도 있다. 입력 기여 (있다면) 와는 별개인 이벤트 자체의 발생이 상태 머신에 영향을 미치거나 그 이벤트에 후속하는 역학을 구속할 수 있으면, 시스템의 장래 상태는 오직 상태 및 입력의 함수라기 보다는, 상태, 이벤트, 및 입력의 함수이다.

일 양태에서, 뉴런 (n) 은 다음의 역학에 의해 지배되는 멤브레인 전압 (νn(t)) 을 가진 스파이킹 누설 적분 발화 (spiking leaky-integrate-and-fire) 뉴런으로서 모델링될 수도 있으며,

여기서, α 및 β 는 파라미터들이고, wm,n 는 시냅스전 뉴런 (m) 을 시냅스후 뉴런 (n) 에 접속하는 시냅스에 대한 시냅스 가중치이고, ym(t) 는 뉴런 (n) 의 세포체에서의 도달까지 △tm,n 에 따른 수상 (dendritic) 또는 축삭 (axonal) 지연에 의해 지연될 수도 있는 뉴런 (m) 의 스파이킹 출력이다.

시냅스후 뉴런으로의 충분한 입력이 확립될 때의 시간으로부터 시냅스후 뉴런이 실제로 발화할 때의 시간까지 지연이 존재한다는 점에 유의해야 한다. Izhikevich 의 단순 모델과 같은 동적 스파이킹 뉴런 모델에 있어서, 시간 지연은 탈분극 임계 (νt) 와 피크 스파이크 전압 (νpeak) 사이의 차이가 존재하면 초래될 수도 있다. 예를 들어, 단순 모델에 있어서, 뉴런 세포체 역학은, 다음과 같은, 전압 및 회복에 대한 미분 방정식들의 쌍에 의해 지배될 수 있으며, 즉,

여기서, ν 는 멤브레인 전위이고, u 는 멤브레인 회복 변수이고, k 는 멤브레인 전위 (ν) 의 시간 스케일을 기술하는 파라미터이고, α 는 회복 변수 (u) 의 시간 스케일을 기술하는 파라미터이고, b 는 멤브레인 전위 (ν) 의 임계 아래의 (sub-threshold) 변동들에 대한 회복 변수 (u) 의 감도를 기술하는 파라미터이고, νr 은 멤브레인 휴지 전위이고, I 는 시냅스 전류이고, C 는 멤브레인의 커패시턴스이다. 이 모델에 따르면, 뉴런은 ν>νpeak 일 때 스파이킹하도록 정의된다.

Hunzinger Cold 모델

Hunzinger Cold 뉴런 모델은 뉴럴 거동들의 풍부한 변종을 재현할 수 있는 최소 듀얼-레짐 스파이킹 선형 역학 모델이다. 모델의 1차원 또는 2차원 선형 역학은 2개의 레짐들을 가질 수 있으며, 여기서, 시상수 (및 커플링) 는 그 레짐에 의존할 수 있다. 임계 아래의 레짐에 있어서, 관례에 의해 네거티브인 시상수는, 생물학적으로 일관된 선형 방식으로 셀을 휴지로 복귀시키기 위해 일반적으로 작용하는 누설 채널 역학을 나타낸다. 관례에 의해 포지티브인 임계 이상의 (supra-threshold) 레짐에 있어서의 시상수는, 스파이크 발생에 있어서 레이턴시를 초래하면서 스파이킹하도록 셀을 일반적으로 구동하는 누설 방지 채널 역학을 반영한다.

도 4 에 도시된 바와 같이, 모델 (400) 의 역학은 2개의 (또는 그 이상의) 레짐들로 분할될 수도 있다. 이들 레짐들은 네거티브 레짐 (402) (누설 적분 발화 (LIF) 레짐 (누설 적분 발화 (LIF) 뉴런 모델과 상이함) 으로서 상호대체가능하게 또한 지칭됨) 및 포지티브 레짐 (404) (누설 방지 적분 발화 (ALIF) 뉴런 모델과 혼동되지 않도록, 누설 방지 적분 발화 (ALIF) 레짐으로서 상호대체가능하게 또한 지칭됨) 으로 칭해 질 수도 있다. 네거티브 레짐 (402) 에 있어서, 그 상태는 장래 이벤트 시에 휴지 (ν-) 로 향하는 경향이 있다. 이 네거티브 레짐에 있어서, 모델은 일반적으로, 시간 입력 검출 특성들 및 다른 임계 아래의 거동을 나타낸다. 포지티브 레짐 (404) 에 있어서, 그 상태는 스파이킹 이벤트 (νS) 로 향하는 경향이 있다. 이 포지티브 레짐에 있어서, 모델은 후속 입력 이벤트들에 의존하여 스파이킹하기 위해 레이턴시를 초래하는 것과 같은, 연산 특성들을 나타낸다. 이벤트들의 관점에서의 역학의 공식화 및 이들 2개의 레짐들로의 역학의 분리는 모델의 기본 특성들이다.

(상태들 (ν 및 u) 에 대해) 선형 듀얼-레짐 2차원 역학은 다음과 같이 관례에 의해 정의될 수도 있으며,

여기서, qρ 및 r 은 커플링을 위한 선형 변환 변수들이다.

심볼 (ρ) 은, 특정 레짐에 대한 관계를 논의하거나 표현할 때, 네거티브 및 포지티브 레짐들에 대해 심볼 (ρ) 을 부호 "-" 또는 "+" 로 각각 대체하는 관례를 갖는 역학 레짐을 표기하기 위해 본 명세서에서 사용된다.

모델 상태는 멤브레인 전위 (전압) (ν) 및 회복 전류 (u) 에 의해 정의된다. 기본 형태에 있어서, 레짐은 본질적으로 모델 상태에 의해 결정된다. 정확하고 일반적인 정의의 미묘하지만 중요한 양태들이 존재하지만, 지금은, 전압 (ν) 이 임계 (ν+) 보다 크면 모델이 포지티브 레짐 (404) 에 있는 것으로, 그렇지 않으면 네거티브 레짐 (402) 에 있는 것으로 간주한다.

레짐 의존적인 시상수들은 네거티브 레짐 시상수인 τ-, 및 포지티브 레짐 시상수인 τ+ 을 포함한다. 회복 전류 시상수 (τu) 는 통상적으로 레짐과 무관하다. 편의를 위해, 네거티브 레짐 시상수 (τ-) 는 통상적으로, 감쇠를 반영하기 위해 네거티브 양으로서 명시되어, τu 인 바와 같은, 전압 발전 (voltage evolution) 을 위한 동일한 표현이 지수 및 τ+ 가 일반적으로 포지티브일 포지티브 레짐에 대해 사용될 수 있다.

2개의 상태 엘리먼트들의 역학은, 이벤트들에서 그 널-클라인(null-cline)들로부터 그 상태들을 오프셋하는 변환들에 의해 커플링될 수도 있으며, 여기서, 변환 변수들은,

이며, 여기서, δ, ε, β 및 ν-, ν+ 는 파라미터들이다. νρ 에 대한 2개의 값들은 2개의 레짐들에 대한 참조 전압들을 위한 베이스이다. 파라미터 (ν-) 는 네거티브 레짐에 대한 베이스 전압이고, 멤브레인 전위는 일반적으로 네거티브 레짐에서 ν- 를 향해 감쇠할 것이다. 파라미터 (ν+) 는 포지티브 레짐에 대한 베이스 전압이고, 멤브레인 전위는 일반적으로 포지티브 레짐에서 ν+ 로부터 이격되는 경향이 있을 것이다.

ν 및 u 에 대한 널-클라인들은 변환 변수들 (qρ 및 r) 의 네거티브에 의해 각각 주어진다. 파라미터 (δ) 는 u 널-클라인의 기울기를 제어하는 스케일 팩터이다. 파라미터 (ε) 는 통상적으로 -ν- 와 동일하게 설정된다. 파라미터 (β) 는 레짐들 양자 모두에서 ν 널-클라인들의 기울기를 제어하는 저항값이다. τρ 시상수 파라미터들은 지수적 감쇠들 뿐만 아니라 널-클라인 기울기들을 각각의 레짐에서 별개로 제어한다.

모델은 전압 (ν) 이 값 νS 에 도달할 때 스파이킹하도록 정의될 수도 있다. 후속적으로, 그 상태는 일반적으로 (기술적으로 하나이고 스파이크 이벤트와 동일할 수도 있는) 리셋 이벤트로 리셋될 수도 있으며:

순간적인 커플링의 원리에 의해, 닫힌 형태의 해는 상태 (및 단일 지수 항을 가진 상태) 에 대해서 뿐만 아니라 특정 상태에 도달하는데 요구되는 시간에 대해서 가능하다. 닫힌 형태의 상태 해들은 다음과 같다.

따라서, 모델 상태는 오직 입력 (시냅스전 스파이크) 또는 출력 (시냅스후 스파이크) 과 같은 이벤트들 시에만 업데이트될 수도 있다. 동작들은 또한 (입력이든 또는 출력이든) 임의의 특정 시간에 수행될 수도 있다.

더욱이, 순간적인 커플링 원리에 의해, 시냅스후 스파이크의 시간은 예상될 수도 있어서, 특정 상태에 도달하기 위한 시간이 반복 기법들 또는 수치 방법들 (예를 들어, Euler 수치 방법) 없이 미리 결정될 수도 있다. 이전 전압 상태 (ν0) 가 주어지면, 전압 상태 (νf) 가 도달되기 전까지의 시간 지연은 다음과 같이 주어진다.

전압 상태 (ν) 가 νS 에 도달하는 시간에서 발생하는 것으로 스파이크가 정의되면, 전압이 주어진 상태 (ν) 에 있는 시간으로부터 측정될 때 스파이크가 발생할 때까지, 시간의 양 또는 상대적인 지연에 대한 닫힌 형태의 해는 다음과 같으며,

모델 역학의 상기 정의들은 모델이 포지티브 레짐에 있는지 또는 네거티브 레짐에 있는지에 의존한다. 언급된 바와 같이, 커플링 및 레짐 (ρ) 은 이벤트들 시에 연산될 수도 있다. 상태 전파의 목적들을 위해, 레짐 및 커플링 (변환) 변수들은 최종 (사전) 이벤트 시의 상태에 기초하여 정의될 수도 있다. 스파이크 출력 시간을 후속적으로 예상하려는 목적을 위해, 레짐 및 커플링 변수는 다음 (현재) 이벤트 시의 상태에 기초하여 정의될 수도 있다.

Cold 모델의 수개의 가능한 구현예들이 존재하며, 시뮬레이션, 에뮬레이션 또는 모델을 시간적으로 실행하고 있다. 이는, 예를 들어, 이벤트-업데이트, 스텝-이벤트 업데이트, 및 스텝-업데이트 모드들을 포함한다. 이벤트 업데이트는, 상태들이 (특정 순간들에서) 이벤트들 또는 "이벤트 업데이트" 에 기초하여 업데이팅되는 업데이트이다. 스텝 업데이트는 모델이 간격들 (예컨대, 1ms) 로 업데이팅될 경우의 업데이트이다. 이는 반복 방법들 또는 수치적 방법들을 반드시 요구하지는 않는다. 이벤트 기반 구현은 또한, 스텝들에서 또는 스텝들 사이에서, 또는 "스텝-이벤트" 업데이트에 의해 이벤트가 발생하면 모델을 단지 업데이팅함으로써, 스텝 기반 시뮬레이터에 있어서, 제한된 시간 해상도에서 가능하다.

파라미터 평가

뉴럴 네트워크 모델들의 개발은 파라미터들의 다양한 조합들을 평가하기 위한 사양들을 포함할 수도 있다. 예를 들어, 설계 프로세스 동안, 뉴럴 네트워크들은 뉴럴 네트워크의 설계를 개선하기 위해 다양한 파라미터들로 테스트될 수도 있다. 파라미터들은 시냅스들의 가중치, 지연들, 뉴런 모델 파라미터들, 엘리먼트들을 기술하는 파라미터들, 예컨대 스파이크 임계 및/최대 컨덕턴스, 입력들을 기술하는 파라미터들, 예컨대 사용된 이미지들 및/또는 오디오 파일들의 수, 학습 파라미터들, 및/또는 다른 뉴럴 네트워크의 변수들을 포함할 수도 있다. 파라미터들을 상이한 값들로 설정하고 그 상이한 값들로 테스팅을 수행함으로써, 뉴럴 네트워크들이 뉴럴 네트워크의 효율과 같은, 다양한 기준에 기초하여 평가될 수도 있다.

일 예로서, 예시적인 뉴럴 네트워크의 파라미터들은 파라미터들 (A-D) 로서 설정될 수도 있다. 뉴럴 네트워크는 파라미터들을 평가하기 위해 함수 (F) 를 사용할 수도 있다. 예를 들어, 함수 F (A, B, C, D) 은, A = 1, 2, … 10 등과 같은 임의의 값으로 파라미터들이 주어질 수도 있는 파라미터들 (A-D) 를 평가한다. 뉴럴 네트워크를 평가하기 위해서, 가능한 많은 파라미터들의 조합들을 시도하는 것이 요망될 수 있다.

통상적인 뉴럴 네트워크에 있어서, 파라미터 탐색은 조합 확산과 상관된다. 즉, 함수 (F) 와 같은, 함수를 평가하기 위한 시간 양은, 제 1 파라미터, 예컨대 파라미터 (A) 에 대한 변수들 모두를 평가하기 위한 시간 양, 제 2 파라미터, 예컨대 파라미터 (B) 에 대한 변수들 모두를 평가하기 위한 위한 시간 양 등의 곱과 동등하다. 이 예에서, 전체 함수 (F) 의 평가 시간을 위한 방정식은, T(F) = T(A) * T(B) * T(C) * T(D) 로서 표현될 수도 있으며, 식 중 T 는 시간을 나타낸다. 파라미터 탐색은 파라미터 스위프로서 지칭될 수도 있다. 각각의 파라미터에 대한 포텐셜 값들의 수에 의존하여, T(F) 는 매우 커지게 될 수도 있다.

도 5a 는 뉴럴 네트워크 (500) 의 일 예를 도시한다. 도 5a 에 나타낸 바와 같이, 뉴럴 네트워크는 시냅스들 (504) 을 통해 상호접속되는 다중 뉴런들 (502) 을 포함할 수도 있다. 일부 경우들에 있어서, 상호접속된 뉴런들의 제 1 그룹은 상호접속된 제 2 그룹과 피드 순방향 접속을 가질 수도 있다. 즉, 상호접속된 뉴런들의 제 2 그룹은 상호접속된 뉴런들의 제 1 그룹과 단방향으로 의존성을 갖는다. 보다 구체적으로, 상호접속된 뉴런들의 제 1 그룹의 출력은 상호접속된 뉴런들의 제 2 그룹에 영향을 미친다. 부가적으로, 상호접속된 뉴런들의 제 2 그룹의 출력은 상호접속된 뉴런들의 제 1 그룹에 영향을 미치지 않는다. 따라서, 상호접속된 뉴런들의 제 1 그룹은 뉴런들이 제 1 은닉 서브 시스템으로서 지정되고, 상호접속된 뉴런들의 제 2 그룹은 뉴런들의 제 2 은닉 서브 시스템일 수도 있다.

도 5b 는 은닉 서브 시스템들로 구분된 일 예의 뉴럴 네트워크를 도시한다. 구체적으로, 도 5a 의 뉴럴 네트워크는 도 5b 의 예시적인 뉴럴 네트워크 (530) 를 생성하기 위해 은닉 서브 시스템들로 구분되었다. 본 개시물의 일 양태에 기초하여, 뉴럴 네트워크 (530) 는 뉴럴 네트워크 (530) 의 은닉 서브 시스템들 (506, 508, 510) 을 결정하기 위해 분석될 수도 있다.

3 개의 은닉 서브 시스템들 (506, 508, 510) 이 은닉 서브 시스템들로서 지칭될 수도 있는데, 이는 이 서브 시스템들이 뉴럴 네트워크의 개발자 및/또는 훈련되지 않은 눈에 쉽게 결정되지 않기 때문이다. 서브 시스템들은 컴포넌트들 또는 한정된 세트들로서 지칭될 수도 있다. 도 5a 및 도 5b 는 단지 각각의 은닉 서브 시스템들 (506, 510) 로부터 하나의 피드 순방향 접속 (520, 522) 만을 도시하지만, 본 개시물은 단지 하나의 피드 순방향 접속만을 갖는 서브 시스템들에 제한되지 않으며 또한 다중 피드 순방향 접속들을 위해 고려된다.

구체적으로, 도 5b 에 나타낸 바와 같이, 제 1 은닉 서브 시스템 (506) 의 상호접속된 뉴런들은 제 2 은닉 서브 시스템 (508) 의 상호접속된 뉴런들로의 피드 순방향 접속 (520) 을 갖는다. 즉, 제 1 은닉 서브 시스템 (506) 의 출력은 제 2 은닉 서브 시스템 (508) 에 영향을 미친다. 부가적으로, 제 3 은닉 서브시스템 (510) 의 상호접속된 뉴런들은 제 2 은닉 서브 시스템 (508) 의 상호접속된 뉴런들로의 피드 순방향 접속 (522) 을 갖는다. 즉, 제 3 은닉 서브 시스템 (510) 의 출력은 제 2 은닉 서브 시스템 (508) 에 영향을 미친다. 따라서, 뉴럴 네트워크 (530) 는 상호접속된 뉴런들의 3 개의 은닉 서브 시스템들 (506, 508, 510) 으로 구분될 수도 있다.

본 예에서, 각각의 서브 시스템은, 10 개의 가능한 값들 (1 내지 10) 을 갖는 관심의 2 개의 파라미터들 (A 및 B) 를 갖는다. 파라미터들 중 하나에 대해 가능한 값들 중 하나로 하나의 서브 시스템을 평가하기 위해 런 (run) 되는 단일 테스팅은 1 분이 걸릴 수도 있다. 따라서, 뉴럴 네트워크 (530) 에서의 파라미터들 모두에 대한 모든 가능한 조합들을 평가하기 위해 2 년 (즉, 106 런들) 이 걸리게 된다. 이것은 명백히 비실용적이다. 이에 따라, 뉴럴 네트워크의 모든 가능한 파라미터들을 평가하기 위한 시간을 감소시키는 것이 필요하다.

본 개시물의 일 양태에 따라, 뉴럴 네트워크의 가능한 파라미터들에 대한 평가 시간을 개선하기 위해서, 도 5b 에 나타낸 바와 같이, 네트워크가 기능적으로 격리된 서브 네트워크들로 분리될 수도 있다. 일 구성에 있어서, 서브 시스템들의 파라미터들은 프루닝 (예를 들어, 제거) 될 수도 있는 파라미터들을 결정하기 위해 분석될 수도 있다.

도 6a 내지 도 6d 는 본 개시물의 일 양태에 따른, 뉴럴 네트워크를 기능적으로 격리된 서브 네트워크들로 분리하기 위한 블록 다이어그램들을 도시한다.

도 6a 에 나타낸 바와 같이, 뉴럴 네트워크 (F)(602) 는 파라미터들 (A, B, C 및 D) 에 대한 입력을 수신한다. 게다가, 뉴럴 네트워크 (602) 는 출력 (604) 을 가질 수도 있다. 도 6b 에 나타낸 바와 같이, 뉴럴 네트워크 (602) 및 파라미터 입력들 (A-D) 을 식별한 후, 뉴럴 네트워크 (602) 는 뉴럴 네트워크 (602) 의 계층들을 결정하기 위해 직렬화될 수도 있다. 뉴럴 네트워크의 계층들은 도 5b 의 은닉 서브 시스템들과 유사하다. 계층들은 제 1 계층 (예를 들어, 입력 계층), 및 제 2 계층, 제 3 계층 등과 같은 하위 계층들을 포함할 수도 있다.

제 1 계층은 내부 입력들이 없고 상호접속된 뉴런들의 다른 그룹에 프로젝트하는 상호접속된 뉴런들의 그룹을 지칭한다. 도 6b 에서, 제 1 직렬화 계층 (S1)(601) 은 내부 입력들이 없는 상호접속된 뉴런들의 제 1 그룹이다. 제 1 직렬화 계층 (606) 은 제 2 직렬화 계층 (S2)(608)(예를 들어, 하위 계층) 에 프로젝트할 수도 있다. 하위 계층들은 상위 계층으로부터 입력을 수신하는 상호접속된 뉴런들의 제 2 그룹을 지칭한다. 즉, 제 2 직렬화 계층 (608) 은 제 1 직렬화 계층 (606) 으로부터 입력을 수신하는 상호접속된 뉴런들의 그룹이다. 또한, 제 2 직렬화 계층 (608) 은 제 1 직렬화 계층 (606) 으로 입력하지 않는다. 도 6 의 뉴럴 네트워크 (602) 와 같은 뉴럴 네트워크는 많은 직렬화 계층들을 가질 수도 있다. 이 예에서는, 단지 2 개의 직렬화 계층들 (606 및 608) 만이 도시된다.

도 6 에 나타낸 바와 같이, 계층들을 직렬화한 후에, 각각의 직렬화 계층 (606, 608) 은 병렬화될 수도 있다. 즉, 상반되는 접속들을 사용하여, 뉴런들의 그룹들 또는 섬들이 각각의 직렬화 계층에서 결정될 수도 있다. 구체적으로, 병렬화를 위해, 계층, 또는 직렬화 계층의 상호 의존성들이 결정된다. 이들 상호 의존성들에 기초하여, 뉴런들은 하나의 병렬화 클러스터의 출력이 다른 병렬화 클러스터의 출력으로부터 독립적인 병렬화 클러스터들로 그룹화될 수도 있다. 이러한 방식으로, 뉴런들은 직렬화 계층 내에서 병렬 클러스터들로 그룹화될 수도 있다. 뉴런들은 또한 계층들의 직렬화 없이 병렬화 클러스터들로 그룹화될 수도 있다.

예를 들어, 도 6c 에 나타낸 바와 같이, 제 1 직렬화 계층 (606) 은 제 1 병렬화 클러스터 (S11)(610) 및 제 2 병렬화 클러스터 (S12)(612) 로 병렬화될 수도 있다. 이러한 구성에서, 제 1 병렬화 클러스터 (610) 및 제 2 병렬화 클러스터 (612) 는 제 1 직렬화 계층 (606) 의 부분이다. 여전히, 제 1 병렬화 클러스터 (610) 의 뉴런들의 출력이 제 2 병렬화 클러스터 (612) 의 출력으로부터 독립적이기 때문에, 제 1 직렬화 계층 (606) 의 뉴런들이 위에서 언급된 병렬화 클러스터들로 병렬화될 수도 있다. 제 1 병렬화 클러스터 (610) 및 제 2 병렬화 클러스터 (612) 는 병렬화 블록 (P1)(614) 으로서 지칭될 수도 있다.

직렬화 계층들 및 병렬화 클러스터들은 서브 시스템들로서 지칭될 수도 있다. 일 구성에서, 뉴럴 네트워크의 서브 시스템들이 결정되면, 뉴럴 네트워크의 파라미터들이 프루닝된다. 즉, 각각의 서브 시스템의 파라미터들은, 파라미터들이 서브 시스템들의 출력에 영향을 미치는지를 결정하기 위해 분석된다. 파라미터가 서브 시스템에 영향을 미치지 않는다면, 파라미터의 값이 각 서브 시스템의 최종 출력을 변경하지 않기 때문에 각 서브 시스템을 평가하기 위한 목적으로 파라미터가 프루닝될 수도 있다.

도 6d 에 나타낸 바와 같이, 제 1 병렬화 클러스터 (610), 제 2 병렬화 클러스터 (612), 및 제 2 직렬화 계층 (608)(예를 들어, 서브 시스템들) 으로의 입력들이 프루닝된다. 이 예에서, 시스템은, 파라미터 (A) 가 제 1 병렬화 클러스터 (610) 에만 영향을 미치고, 파라미터들 (B 및 C) 는 제 2 병렬화 클러스터 (612) 에만 영향을 미치며, 파라미터들 (C 및 D) 는 제 2 직렬화 계층 (608) 에만 영향을 미친다고 결정할 수도 있다. 따라서, 특정 서브 시스템에 영향을 미치지 않는 파라미터들은 각 서브 시스템에 대한 입력들로서 프루닝되고 제거된다.

일 구성에서, 계층들의 식별은 재귀적으로 수행될 수도 있다. 즉, 각각의 직렬화 계층은 다른 직렬화 계층들을 결정하기 위해 직렬화 입력 계층으로서 처리될 수도 있다. 구체적으로, 이전에 논의된 바와 같이, 제 1 계층은 내부 입력들이 없는 상호접속된 뉴런들의 그룹을 지칭한다. 제 1 계층은 또한 상호접속된 뉴런들의 다른 그룹 (예를 들어, 상호접속된 뉴런들의 제 2 계층) 에 출력한다. 즉, 뉴런들의 제 1 계층은 네트워크에서의 다른 뉴런들 중 어느 것의 출력들에 의해 영향을 받지 않는다. 더욱이, 뉴런들의 제 1 계층은 뉴럴 네트워크의 외부로부터 입력들을 수신할 수도 있다.

예를 들어, 사용자는 제 1 계층에 뉴럴 스파이킹 표현으로 변환 (transduce) 되는 이미지 파일들을 입력할 수도 있다. 뉴런들의 제 1 계층을 식별한 후에, 제 1 계층에서의 뉴런들로부터 입력을 수신하는 뉴런들의 제 2 계층이 식별된다. 뉴런들의 제 2 계층은 단지 뉴런들의 제 1 계층으로부터의 입력들만을 수신한다. 즉, 뉴런들의 제 1 계층의 입력들은 외부 입력들로서 처리된다. 따라서, 뉴런들의 상이한 계층에 대한 탐색은 이전 계층들로부터의 입력들만을 수신하고 다른 내부 입력들이 없는 계층들에 기초하여 재귀적으로 수행된다.

본 개시물은 직렬화 계층들 및 병렬화 계층들 양자에 제한되지 않는다. 일 구성에서, 뉴럴 네트워크만이 직렬화되고 프루닝된다. 대안으로, 다른 구성에서, 뉴럴 네트워크만이 병렬화되고 프루닝된다. 다른 구성에서, 사용자는 서브 시스템들을 식별할 수도 있다. 또 다른 구성에서, 서브 시스템들의 식별은, 뉴럴 네트워크가 컴플라이될 때 컴플라이어에 의해 식별될 수도 있다.

상술한 바와 같이, 서브 시스템은 네트워크 접속성에 기초하여 정의될 수도 있다. 부가적으로 또는 대안으로, 일 구성에서, 서브 시스템은 스위프의 활동 레벨들을 모니터링하는 것에 의해 정의될 수도 있다. 즉, 제 1 계층 서브 시스템이 제 2 계층 서브 시스템으로부터 입력을 수신할 때, 제 1 계층 서브 시스템은 하위 계층의 저장된 출력들 모두에 걸쳐 그 출력들을 계산한다. 제 1 계층의 출력들의 일부 (예를 들어, 제 2 계층으로의 입력들) 가 서로 유사하면 (예를 들어, 특정 파라미터 범위들에 대해 스파이킹 출력이 없으면), 시스템은 모든 감소된 입력들에 대해 계산을 한번 실행할 수도 있다. 더욱이, 하나의 런에 대한 제 2 계층의 출력은, 제 1 계층으로부터 감소된 출력을 생성했던 전체 범위에 대한 결합된 런의 출력으로서 저장될 수도 있다.

또한, 일 구성에서, 스위프에서의 각 단계 후에, 각각의 서브 시스템의 출력이 저장된다. 즉, 파라미터 스위프는 결합된 시스템의 출력들의 큰 집합을 생성할 수도 있다. 따라서, 사용자는 결합된 네트워크의 출력들에 대해 정의되는 기능에 따라 출력들을 분석하기를 요망할 수도 있다. 예를 들어, 사용자는, 뉴런들이 최종 직렬화 계층에서 개별 뉴런들의 스파이킹 출력들의 패턴에 선택적으로 응답하는지 여부를 분석하기를 요망할 수도 있다.

도 7 은 본 개시물의 일 양태에 따라 뉴럴 네트워크의 파라미터 평가를 개선하기 위한 방법 (700) 을 도시한다. 블록 (702) 에서, 방법은 뉴럴 네트워크를 계층들로 직렬화한다. 일 구성에서, 직렬화는 파라미터들의 입력들을 수신하지만 다른 내부 입력들은 없는 제 1 계층 (예를 들어, 입력 계층) 을 결정한다. 부가적으로, 이러한 구성에서, 블록 (702) 의 직렬화는 또한 제 1 계층으로부터 입력을 수신하는 제 2 계층을 결정한다. 계층을 직렬화한 후에, 직렬화 계층은 블록 (704) 에서 병렬화된다. 일 구성에서, 병렬화는 직렬화 계층 내에서 뉴런들의 클러스터들을 결정하기 위해 상반되는 접속들을 사용한다. 직렬화 계층 내의 뉴런들의 각각의 클러스터는 병렬화 클러스터로서 지칭될 수도 있다.

블록 (706) 에서, 뉴럴 네트워크의 파라미터들이 프루닝된다. 프루닝은 특정 병렬화 클러스터 및/또는 직렬화 계층에 의해 사용되지 않는 파라미터들을 제거하는 것을 지칭한다. 이전에 논의된 바와 같이, 뉴럴 네트워크의 병렬화 클러스터들 및 직렬화 계층들은 서브 시스템들, 한정된 세트들, 또는 컴포넌트들로 지칭될 수도 있다. 블록 (708) 에서, 각각의 서브 시스템에 대한 소모 시간 (Te) 및 저장 요건들 (S, Ta) 이 결정된다. 일 구성에서, 블록 (708) 에서 각각의 서브 시스템에 대한 소모 시간 (Te) 및 저장 요건들 (S, Ta) 을 결정한 후에, 블록들 (702-706) 이 부가 세트들을 결정하기 위해 재귀적으로 수행 (병렬화 및/또는 직렬화) 될 수도 있다. 다른 구성에서, 블록 (710) 에서, 목적의 기능은 액세스 시간, 메모리 액세스 시간, 및/또는 계산 시간에 기초하여 캐시하기 위해 서브 시스템들을 결정한다.

도 8 은 본 개시물의 일 양태에 기초하여 파라미터들을 평가하기 위한 기능들을 도시한다. 도 8 의 플로우 챠트는 도 6a 내지 도 6d 의 블록 다이어그램들에 기초한다. 블록 (802) 에 나타낸 바와 같이, 뉴럴 네트워크의 파라미터들 (A, B, C, 및 D) 은 함수 F(A,B,C,D) 에 기초하여 평가될 수도 있으며, 여기서 F 는 파라미터들을 평가하기 위한 함수이다. 제 1 직렬화 계층 (S1)(606) 의 출력은 그 입력들, 파라미터들 (A, B, C, 및 D) 의 함수이고, 이에 따라 S1(A,B,C,D) 로서 표현될 수도 있다. 제 2 직렬화 계층 (608) 의 출력은 또한 그 입력들의 함수로서 표현될 수도 있다. 제 2 직렬화 계층으로의 입력들이 파라미터들 (A, B, C, 및 D) 일 때, 제 1 직렬화 계층 (606) 으로부터의 출력에 부가하여, 제 2 직렬화 계층의 출력은 S2(S1(A,B,C,D), A,B,C,D) 로서 표현될 수도 있다. 블록 (802) 에 나타낸 바와 같이, 제 2 직렬화 계층 (608) 이 시스템의 최종 계층이기 때문에, 함수 F(A,B,C,D) 는 제 2 직렬화 계층 (608) 의 출력과 동등하다. 이에 따라, 시스템 함수 F(A,B,C,D) 의 출력은 S2(S1(A,B,C,D), A,B,C,D) 와 동등하다고 언급될 수도 있다.

블록 (804) 에서, 제 1 직렬화 계층 (606) 에 대한 함수가 결정된다. 즉, 제 1 직렬화 함수 (606) 는 병렬화 블록 (614)(P1) 의 함수들과 동등한 S1(A,B,C,D) 의 함수를 갖는다. 병렬화 블록 (614) 은 제 1 병렬화 클러스터 (610)(S11) 및 제 2 병렬화 클러스터 (612)(S12) 를 포함한다. 도 6a 내지 도 6d 에 나타낸 바와 같이, 제 1 병렬화 클러스터 (610) 및 제 2 병렬화 클러스터 (612) 는 각각 파라미터들 (A, B, C, 및 D) 의 입력들을 갖는다. 이에 따라, 제 1 직렬화 계층 (606) 은 함수 P1(S11(A,B,C,D), S12(A,B,C,D)) 와 동등할 수도 있다.

블록 (806) 에서, 프루닝은 파라미터들의 평가를 개선하기 위해 수행된다. 제 1 병렬화 클러스터 (S11)(610) 는 단지 파라미터 (A) 의 함수만 되도록 프루닝될 수도 있고, 이에 따라 제 1 병렬화 클러스터 (610) 는 S11(A) 와 동등하다. 부가적으로, 제 2 병렬화 클러스터 (S12)(612) 는 단지 파라미터들 (B 및 D) 의 함수만 되도록 프루닝될 수도 있다. 이에 따라, 제 2 병렬화 클러스터 (612) 는 S12(B,D) 와 동등하다. 부가적으로, 제 2 직렬화 계층 (608) 은 입력들이 단지 파라미터들 (C 및 D) 만 이도록 프루닝된다.

프루닝 후에, 제 1 병렬화 블록 (620) 에 대한 함수는 P1((S11(A), S12(B,D)) 이다. 마찬가지로, 제 2 직렬화 계층에 대한 함수는 S2(P1(S11(A), S12(B,D)),C,D) 이다. 프루닝 후에, 블록 (808) 에서, 계층들 및 뉴럴 네트워크에 대한 평가 시간들 (Te) 이 결정된다. 즉, 제 1 직렬화 계층 (606)(S1) 에 대한 평가 시간은 제 1 병렬화 클러스터 (610) 및 제 2 병렬화 클러스터 (612) 의 평가의 합이다 (S12). 더욱이, 뉴럴 네트워크 (F) 는 제 1 직렬화 계층 (606)(S1) 및 제 2 직렬화 계층 (608)(S2) 에 대한 평가 시간의 곱이다.

일 구성에 있어서, 블록 (810) 에서, 최적화 함수가 실행되어 액세스 시간, 메모리 액세스 시간, 및/또는 계산 시간에 기초하여 캐시하기 위해 서브 시스템들을 결정한다. 최적화 함수는 다음의 방정식에 기초할 수 있다:

방정식 (15) 에서, O 는 최적화 함수이고, N 은 제 1 직렬화 계층 (606) 과 같은, 식별된 서브 시스템들이다. Te 는 입력 파라미터들에 대한 평가 시간이다. Ta 는 메모리로부터 파라미터 액세스를 위한 평가 시간이다.

방정식 (15) 에서, S 는 각각의 서브 시스템에 대해 특정된 메모리 스토리지의 양의 측정이다. 각각의 서브 시스템에 대하여, Te 는 그 서브 시스템의 실행 시간이다. 실행 시간은 출력들을 생성하고 저장하는 것에 부가하여 서브 시스템의 입력들에 액세스하는 것을 포함한다. Ta 는 그 입력들로부터 재계산되기 보다는 메모리에 저장되었던 경우 시스템의 출력들에 액세스하기 위한 시간이다. 메모리 공간에 관심이 없는 경우, 시스템은 특정 서브 시스템으로부터의 출력들을 시스템이 캐시하여야 하는지 여부를 결정하기 위해 메모리 액세스 시간들을 여전히 계산할 수도 있다.

일 구성에서, 프루닝은 상이한 차원들에 따라 계산을 개선하기 위해 수행될 수도 있으며, 이는 계산 시간 또는 메모리 스토리지와 연관된 상이한 비용들이 있을 수도 있기 때문이다. 예를 들어, 사용자가 많은 계산 전력 및 적은 메모리 스토리지를 할당 받는 경우, 사용자는 출력들을 저장하기 보다는 서브 시스템의 출력들을 재계산하기 위해 선택할 수도 있다. 이 예에서, 계산 전력과 메모리 스토리지 사이의 트레이드 오프는 방정식 (15) 에서 "alpha" 로서 설정될 수도 있다. 다른 구성에 있어서, 시스템은 출력들에 액세스하기 위한 시간 (Ta) 이 출력들을 재계산하기 위한 시간 (Te) 보다 적은 서브 시스템들의 출력들을 캐시하기로 결정한다. 이 구성에서, 방정식 (15) 에서의 디폴트 설정들은 alpha 가 1 이고 S 가 0 이다.

도 9 는 본 개시물의 소정 양태들에 따른, 범용 프로세서 (902) 를 사용하여 위에서 언급된 수정 뉴럴 역학의 예시적인 구현 (900) 을 도시한다. 연산 네트워크 (뉴럴 네트워크) 와 연관된 변수들 (뉴럴 신호들), 시냅스 가중치들, 시스템 파라미터들, 지연들, 및 주파수 빈 정보가 메모리 블록 (904) 에 저장될 수도 있는 한편, 범용 프로세서 (902) 에서 실행되는 관련 명령들은 프로그램 메모리 (906) 로부터 로딩될 수도 있다. 본 개시물의 일 양태에 있어서, 범용 프로세서 (902) 로 로딩된 명령들은 뉴런 모델들이 원형 뉴런 역학과 매칭하도록 원형 뉴런 역학을 획득하고 및/또는 뉴런 모델의 파라미터들을 수정하기 위한 코드를 포함할 수도 있다.

도 10 은 본 개시물의 소정 양태들에 따른, 메모리 (1002) 가 상호접속 네트워크 (1004) 를 통해 연산 네트워크 (뉴럴 네트워크) 의 개별 (분산된) 프로세싱 유닛들 (뉴럴 프로세서들) (1006) 과 인터페이싱될 수 있는, 위에서 언급된 수정 뉴럴 역학의 예시적인 구현 (1000) 을 도시한다. 연산 네트워크 (뉴럴 네트워크) 와 연관된 변수들 (뉴럴 신호들), 시냅스 가중치들, 시스템 파라미터들, 지연들, 및/또는 주파수 빈 정보는 메모리 (1002) 에 저장될 수도 있고, 메모리 (1002) 로부터 상호접속 네트워크 (1004) 의 접속(들)을 통해 각각의 프로세싱 유닛 (뉴럴 프로세서) (1006) 으로 로딩될 수도 있다. 본 개시물의 일 양태에 있어서, 프로세싱 유닛 (1006) 은 원형 뉴런 역학을 획득하고 및/또는 뉴런 모델의 파라미터들을 수정하도록 구성될 수도 있다.

도 11 는 위에서 언급된 수정 뉴럴 역학의 예시적인 구현 (1100) 을 도시한다. 도 11 에 도시된 바와 같이, 일 메모리 뱅크 (1102) 는 연산 네트워크 (뉴럴 네트워크) 의 일 프로세싱 유닛 (1104) 과 직접 인터페이싱될 수도 있다. 각각의 메모리 뱅크 (1102) 는 대응 프로세싱 유닛 (뉴럴 프로세서) (1104) 와 연관된 변수들 (뉴럴 신호들), 시냅스 가중치들, 및/또는 시스템 파라미터, 지연들 및 주파수 빈 정보를 저장할 수도 있다. 본 개시물의 일 양태에 있어서, 프로세싱 유닛(들) (1104) 은 원형 뉴런 역학을 획득하고 및/또는 뉴런 모델의 파라미터들을 수정하도록 구성될 수도 있다.

도 12 은 본 개시물의 소정 양태들에 따른 뉴럴 네트워크 (1200) 의 예시적인 구현을 도시한다. 도 12 에 도시된 바와 같이, 뉴럴 네트워크 (1200) 는 상기 설명된 방법의 다양한 동작들을 수행할 수도 있는 다중 로컬 프로세싱 유닛들 (1202) 을 가질 수도 있다. 각각의 로컬 프로세싱 유닛 (1202) 은 뉴럴 네트워크의 파라미터들을 저장하는 로컬 상태 메모리 (1204) 및 로컬 파라미터 메모리 (1206) 을 포함할 수도 있다. 부가적으로, 프로세싱 유닛 (1202) 은 로컬 (뉴런) 모델 프로그램을 갖는 메모리 (1208), 로컬 학습 프로그램을 갖는 메모리 (1210), 및 로컬 접속 메모리 (1212) 를 가질 수도 있다. 더욱이, 도 12 에 도시된 바와 같이, 각각의 로컬 프로세싱 유닛 (1202) 은 로컬 프로세싱 유닛의 로컬 메모리들을 위한 구성을 제공할 수도 있는 구성 프로세싱을 위한 유닛 (1214) 과, 그리고 로컬 프로세싱 유닛들 (1202) 간의 라우팅을 제공하는 라우팅 접속 프로세싱 엘리먼트들 (1216) 과 인터페이싱될 수도 있다.

본 개시물의 소정의 양태들에 따라, 각각의 로컬 프로세싱 유닛 (1202) 은 뉴럴 네트워크의 원하는 하나 이상의 기능 피처들에 기초하여 뉴럴 네트워크의 파라미터들을 결정하도록 구성될 수도 있다. 각각의 로컬 프로세싱 유닛은 결정된 파라미터들이 추가로 적응되고, 튜닝되며, 업데이트될 때 원하는 기능 피처들 쪽으로 하나 이상의 기능 피처들을 개발할 수도 있다.

도 13 은 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법 (1300) 을 도시한다. 일 구성에서, 블록 (1302) 에서, 뉴럴 모델은 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 시스템의 서브 시스템들을 직렬화한다. 또한, 블록 (1302) 의 직렬화에 부가하여 또는 이에 대안으로, 뉴런 모델은 각각의 서브 시스템 내의 의존성들을 결정하는 것에 의해 서브 시스템들을 병렬화한다. 즉, 일 구성에서, 뉴런 모델은 블록 (1302) 의 직렬화 또는 블록 (1304) 의 병렬화 중 어느 하나를 수행할 수도 있다. 다른 구성에서, 뉴런 모델은 블록 (1302) 의 직렬화 및 블록 (1304) 의 병렬화의 양자 모두를 수행할 수도 있다. 마지막으로, 블록 (1306) 에서, 뉴런 모델은 각각의 입력 파라미터들이 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝한다.

일 구성에 있어서, 본 개시물의 양태들의 뉴럴 네트워크와 같은 뉴럴 네트워크는 뉴럴 역학을 수정하도록 구성된다. 뉴럴 역학은 병렬화하는 수단, 직렬화하는 수단, 및/또는 프루닝 (pruning) 하는 수단을 포함할 수도 있다. 일 양태에서, 병렬화하는 수단, 직렬화하는 수단, 및/또는 프루닝하는 수단은, 병렬화하는 수단, 직렬화하는 수단, 및/또는 프루닝하는 수단에 의해 인용된 기능들을 수행하도록 구성된 프로그램 메모리 (906), 메모리 블록 (904), 메모리 (1002), 상호접속 네트워크 (1004), 프로세싱 유닛들 (1006), 프로세싱 유닛 (1104), 로컬 프로세싱 유닛들 (1202), 또는 라우팅 접속 프로세싱 엘리먼트들 (1216) 일 수도 있다.

상술한 방법들의 다양한 동작들은 대응하는 기능들을 수행할 수 있는 임의의 적합한 수단에 의해 수행될 수도 있다. 그 수단은 회로, 주문형 집적회로 (ASIC), 또는 프로세서를 포함하지만 이에 한정되지 않는 다양한 하드웨어 및/또는 소프트웨어 컴포넌트(들) 및/또는 모듈(들)을 포함할 수도 있다. 일반적으로 도면들에 도시된 동작들이 존재하는 경우, 그 동작들은 유사한 넘버링을 갖는 대응하는 상대의 수단-플러스-기능 컴포넌트들을 가질 수도 있다.

본 명세서에서 사용된 바와 같이, 용어 "결정하는 것" 은 매우 다양한 액션들을 포괄한다. 예를 들어, "결정하는 것" 은 계산하는 것, 연산하는 것, 프로세싱하는 것, 도출하는 것, 조사하는 것, 검색하는 것 (예를 들어, 표, 데이터베이스, 또는 다른 데이터 구조에서 검색하는 것), 확인하는 것 등을 포함할 수도 있다. 부가적으로, "결정하는 것" 은 수신하는 것 (예를 들어, 정보를 수신하는 것), 액세스하는 것 (예를 들어, 메모리 내 데이터에 액세스하는 것) 등을 포함할 수도 있다. 또한, "결정하는 것" 은 해결하는 것, 선택하는 것, 선출하는 것, 확립하는 것 등을 포함할 수도 있다.

본 명세서에서 사용된 바와 같이, 아이템들의 리스트 "중 적어도 하나"를 지칭하는 어구는 단일 멤버들을 포함하여 그 아이템들의 임의의 조합을 지칭한다. 일 예로서, "a, b, 또는 c 중 적어도 하나" 는 a, b, c, a-b, a-c, b-c, 및 a-b-c 를 커버하도록 의도된다.

본 개시와 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들, 및 회로들은 범용 프로세서, 디지털 신호 프로세서 (DSP), 주문형 집적회로 (ASIC), 필드 프로그램가능 게이트 어레이 신호 (FPGA) 또는 다른 프로그램가능 로직 디바이스 (PLD), 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본 명세서에서 설명된 기능들을 수행하도록 설계된 이들의 임의의 조합으로 구현 또는 수행될 수도 있다. 범용 프로세서는 마이크로프로세서일 수도 있지만, 대안적으로, 그 프로세서는 임의의 상업적으로 입수가능한 프로세서, 제어기, 마이크로 제어기, 또는 상태 머신일 수도 있다. 프로세서는 또한, 컴퓨팅 디바이스들의 조합, 예를 들어, DSP 와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 이상의 마이크로프로세서들, 또는 임의의 기타 다른 구성물로서 구현될 수도 있다.

본 개시와 관련하여 설명된 방법 또는 알고리즘의 단계들은 하드웨어에서, 프로세서에 의해 실행되는 소프트웨어 모듈에서, 또는 이들 양자의 조합에서 직접 구현될 수도 있다. 소프트웨어 모듈은, 당업계에 공지된 임의의 형태의 저장 매체에 상주할 수도 있다. 사용될 수도 있는 저장 매체의 일부 예들은 랜덤 액세스 메모리 (RAM), 판독 전용 메모리 (ROM), 플래시 메모리, EPROM 메모리, EEPROM 메모리, 레지스터들, 하드 디스크, 착탈가능 디스크, CD-ROM 등을 포함한다. 소프트웨어 모듈은 단일 명령 또는 다수의 명령들을 포함할 수도 있으며, 수개의 상이한 코드 세그먼트들에 걸쳐, 상이한 프로그램들 사이에, 및 다중의 저장 매체에 걸쳐 분산될 수도 있다. 저장 매체는, 프로세서가 저장 매체로부터 정보를 판독할 수 있고 저장 매체에 정보를 기입할 수 있도록 프로세서에 커플링될 수도 있다. 대안적으로, 저장 매체는 프로세서에 통합될 수도 있다.

본 명세서에 개시된 방법들은 설명된 방법을 달성하기 위한 하나 이상의 단계들 또는 액션들을 포함한다. 그 방법 단계들 및/또는 액션들은 청구항들의 범위로부터 일탈함없이 서로 대체될 수도 있다. 즉, 단계들 또는 액션들의 특정 순서가 명시되지 않으면, 특정 단계들 및/또는 액션들의 순서 및/또는 그 사용은 청구항들의 범위로부터 일탈함없이 수정될 수도 있다.

설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합에서 구현될 수도 있다. 하드웨어에서 구현되면, 예시적인 하드웨어 구성은 디바이스에 프로세싱 시스템을 포함할 수도 있다. 프로세싱 시스템은 버스 아키텍처로 구현될 수도 있다. 버스는 프로세싱 시스템의 특정 어플리케이션 및 전체 설계 제약들에 의존하는 임의의 수의 상호접속 버스들 및 브리지들을 포함할 수도 있다. 버스는 프로세서, 머신 판독가능 매체들, 및 버스 인터페이스를 포함하는 다양한 회로들을 함께 링크시킬 수도 있다. 버스 인터페이스는, 다른 것들 중에서, 네트워크 어댑터를 버스를 통해 프로세싱 시스템에 접속시키는데 사용될 수도 있다. 네트워크 어댑터는 신호 프로세싱 기능들을 구현하는데 사용될 수도 있다. 소정 양태들에 대해, 사용자 인터페이스 (예를 들어, 키패드, 디스플레이, 마우스, 조이스틱 등) 가 또한 버스에 접속될 수도 있다. 버스는 또한, 당업계에 널리 공지되고 따라서 어떠한 추가로 설명되지 않을 타이밍 소스들, 주변기기들, 전압 레귤레이터들, 전력 관리 회로들 등과 같은 다양한 다른 회로들을 링크시킬 수도 있다.

프로세서는 버스를 관리하는 것, 및 컴퓨터 판독가능 매체 상에 저장된 소프트웨어의 실행을 포함한 일반 프로세싱을 책임질 수도 있다. 프로세서는 하나 이상의 범용 및/또는 특수목적 프로세서들로 구현될 수도 있다. 예들은 마이크로프로세서들, 마이크로 제어기들, DSP 프로세서들, 및 소프트웨어를 실행할 수 있는 다른 회로를 포함한다. 소프트웨어는, 소프트웨어, 펌웨어, 미들웨어, 마이크로코드, 하드웨어 디스크립션 언어, 또는 기타 등등으로서 지칭되든 아니든, 명령들, 데이터, 또는 이들의 임의의 조합을 의미하도록 넓게 해석될 것이다. 머신 판독가능 매체들은, 예로서, RAM (랜덤 액세스 메모리), 플래시 메모리, ROM (판독 전용 메모리), PROM (프로그램가능 판독 전용 메모리), EPROM (소거가능한 프로그램가능 판독 전용 메모리), EEPROM (전기적으로 소거가능한 프로그램가능 판독 전용 메모리), 레지스터들, 자기 디스크들, 광학 디스크들, 하드 드라이브들, 또는 임의의 다른 적합한 저장 매체, 또는 이들의 임의의 조합을 포함할 수도 있다. 컴퓨터 판독가능 매체들은 컴퓨터 프로그램 제품으로 구현될 수도 있다. 컴퓨터 프로그램 제품은 패키징 재료를 포함할 수도 있다.

하드웨어 구현에 있어서, 머신-판독가능 매체들은 프로세서와는 분리된 프로세싱 시스템의 부분일 수도 있다. 하지만, 당업자들이 용이하게 인식할 바와 같이, 머신-판독가능 매체들 또는 그 임의의 부분은 프로세싱 시스템 외부에 있을 수도 있다. 예로서, 머신-판독가능 매체들은 송신 라인, 데이터에 의해 변조된 캐리어파, 및/또는 디바이스로부터 분리된 컴퓨터 제품을 포함할 수도 있으며, 이들 모두는 버스 인터페이스를 통해 프로세서에 의해 액세스될 수도 있다. 대안적으로 또는 부가적으로, 머신-판독가능 매체들 또는 그 임의의 부분은, 캐시 및/또는 일반 레지스터 파일들로 있을 수도 있는 경우와 같이, 프로세서에 통합될 수도 있다. 논의된 다양한 컴포넌트들이 로컬 컴포넌트와 같은 특정 위치를 갖는 것으로 기재될 수도 있지만, 이들은 또한 소정 컴포넌트들이 분산된 컴퓨팅 시스템의 부분으로서 구성되는 것과 같은 다양한 방식들로 구성될 수도 있다.

프로세싱 시스템은 프로세서 기능을 제공하는 하나 이상의 마이크로프로세서들 및 머신-판독가능 매체들의 적어도 일부를 제공하는 외부 메모리를 갖는 범용 프로세싱 시스템으로서 구성될 수도 있고, 이들 모두는 외부 버스 아키텍처를 통해 다른 지원 회로와 함께 링크된다. 대안으로, 프로세싱 시스템은 본 명세서에 기재된 뉴럴 시스템들의 모델들 및 뉴런 모델들을 구현하기 위해 하나 이상의 뉴로모픽 (neuromorphic) 프로세서들을 포함할 수도 있다. 또 다른 대안으로, 프로세싱 시스템은, 단일 칩으로 집적된 프로세서, 버스 인터페이스, 사용자 인터페이스, 지원 회로, 및 머신-판독가능 매체들의 적어도 일부를 갖는 ASIC (주문형 집적회로) 로, 또는 하나 이상의 FPGA들 (필드 프로그램가능 게이트 어레이들), PLD들 (프로그램가능 로직 디바이스들), 제어기들, 상태 머신들, 게이트형 로직, 이산 하드웨어 컴포넌트들, 또는 임의의 다른 적합한 회로, 또는 본 개시 전반에 걸쳐 설명된 다양한 기능을 수행할 수 있는 회로들의 임의의 조합으로 구현될 수도 있다. 당업자는 전체 시스템에 부과된 전체 설계 제약들 및 특정 어플리케이션에 의존하여 프로세싱 시스템에 대한 설명된 기능을 최상으로 구현할 수 있는 방법을 인식할 것이다.

머신 판독가능 매체들은 다수의 소프트웨어 모듈들을 포함할 수도 있다. 소프트웨어 모듈들은, 프로세서에 의해 실행될 경우, 프로세싱 시스템으로 하여금 다양한 기능들을 수행하게 하는 명령들을 포함한다. 소프트웨어 모듈들은 송신 모듈 및 수신 모듈을 포함할 수도 있다. 각각의 소프트웨어 모듈은 단일 저장 디바이스에 상주할 수도 있거나 또는 다수의 저장 디바이스들에 걸쳐 분산될 수도 있다. 예로서, 소프트웨어 모듈은 트리거링 이벤트가 발생할 때 하드 드라이브로부터 RAM 으로 로딩될 수도 있다. 소프트웨어 모듈의 실행 동안, 프로세서는 액세스 속도를 증가시키기 위해 명령들의 일부를 캐시에 로딩할 수도 있다. 그 후, 하나 이상의 캐시 라인들은 프로세서에 의한 실행을 위해 일반 레지스터 파일에 로딩될 수도 있다. 하기에서 소프트웨어 모듈의 기능을 참조할 경우, 그 소프트웨어 모듈로부터의 명령들을 실행할 때 그러한 기능은 프로세서에 의해 구현됨이 이해될 것이다.

소프트웨어에서 구현된다면, 그 기능들은 하나 이상의 명령들 또는 코드로서 컴퓨터 판독가능 매체 상으로 저장 또는 전송될 수도 있다. 컴퓨터 판독가능 매체는, 일 장소로부터 다른 장소로의 컴퓨터 프로그램의 전송을 용이하게 하는 임의의 매체를 포함하는 컴퓨터 저장 매체 및 통신 매체 양자를 포함한다. 저장 매체는, 컴퓨터에 의해 액세스될 수 있는 임의의 가용 매체일 수도 있다. 한정이 아닌 예로서, 그러한 컴퓨터 판독가능 매체는 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장부, 자기 디스크 저장부 또는 다른 자기 저장 디바이스들, 또는 원하는 프로그램 코드를 명령들 또는 데이터 구조들의 형태로 수록 또는 저장하는데 이용될 수 있고 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다. 부가적으로, 임의의 커넥션이 컴퓨터 판독가능 매체로 적절히 명명된다. 예를 들어, 동축 케이블, 광섬유 케이블, 꼬임쌍선, 디지털 가입자 라인 (DSL), 또는 적외선 (IR), 무선, 및 마이크로파와 같은 무선 기술들을 이용하여 웹사이트, 서버, 또는 다른 원격 소스로부터 소프트웨어가 송신된다면, 동축 케이블, 광섬유 케이블, 꼬임쌍선, DSL, 또는 적외선, 무선, 및 마이크로파와 같은 무선 기술들은 매체의 정의에 포함된다. 본 명세서에서 사용된 바와 같이, 디스크 (disk) 및 디스크 (disc) 는 컴팩트 디스크 (CD), 레이저 디스크, 광학 디스크, 디지털 다기능 디스크 (DVD), 플로피 디스크 및 블루레이® 디스크를 포함하며, 여기서, 디스크(disk)들은 통상적으로 데이터를 자기적으로 재생하지만 디스크(disc)들은 레이저들을 이용하여 데이터를 광학적으로 재생한다. 따라서, 일부 양태들에 있어서, 컴퓨터 판독가능 매체는 비-일시적인 컴퓨터 판독가능 매체 (예를 들어, 유형의 매체) 를 포함할 수도 있다. 부가적으로, 다른 양태들에 대해, 컴퓨터 판독가능 매체는 일시적인 컴퓨터 판독가능 매체 (예를 들어, 신호) 를 포함할 수도 있다. 상기의 조합들이 또한, 컴퓨터 판독가능 매체의 범위 내에 포함되어야 한다.

따라서, 소정 양태들은, 본 명세서에서 제시된 동작들을 수행하기 위한 컴퓨터 프로그램 제품을 포함할 수도 있다. 예를 들어, 그러한 컴퓨터 프로그램 제품은 명령들이 저장된 (및/또는 인코딩된) 컴퓨터 판독가능 매체를 포함할 수도 있으며, 그 명령들은 본 명세서에서 설명된 동작들을 수행하기 위해 하나 이상의 프로세서들에 의해 실행가능하다. 소정 양태들에 대해, 컴퓨터 프로그램 제품은 패키징 재료를 포함할 수도 있다.

추가로, 본 명세서에서 설명된 방법들 및 기술들을 수행하는 모듈들 및/또는 다른 적절한 수단은, 적용가능할 때, 사용자 단말기 및/또는 기지국에 의해 다운로드되고/되거나 그렇지 않으면 획득될 수 있음을 인식해야 한다. 예를 들어, 그러한 디바이스는 서버에 커플링되어, 본 명세서에서 설명된 방법들을 수행하는 수단의 전송을 용이하게 할 수 있다. 대안적으로, 본 명세서에서 설명된 다양한 방법들은 저장 수단 (예를 들어, RAM, ROM, 컴팩트 디스크 (CD) 또는 플로피 디스크와 같은 물리적 저장 매체 등) 을 통해 제공될 수 있어서, 그 저장 수단을 디바이스에 커플링 또는 제공할 시, 사용자 단말기 및/또는 기지국이 다양한 방법들을 획득할 수 있다. 더욱이, 본 명세서에서 설명된 방법들 및 기술들을 디바이스에 제공하기 위한 임의의 다른 적합한 기술이 활용될 수 있다.

청구항들은 상기 예시된 정확한 구성 및 컴포넌트들에 한정되지 않음을 이해해야 한다. 다양한 수정들, 변경들 및 변이들이 청구항들의 범위로부터 일탈함없이, 상기 설명된 방법들 및 장치의 배열, 동작 및 상세들에서 행해질 수도 있다.

Claims (20)

- 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법으로서,

상기 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 상기 서브 시스템들을 직렬화하는 단계, 및 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 상기 서브 시스템들을 병렬화하는 단계, 중 적어도 하나를 수행하는 단계; 및

각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝 (pruning) 하는 단계를 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법. - 제 1 항에 있어서,

병렬화하는 단계, 직렬화하는 단계 및/또는 프루닝하는 단계는, 메모리 스토리지 요건들, 메모리 액세스 시간, 및/또는 계산 시간에 적어도 부분적으로 의존하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법. - 제 1 항에 있어서,

네트워크의 접속성 및/또는 상기 파라미터 스위프의 활동 레벨들을 모니터링하는 것에 기초하여 서브 시스템들을 정의하는 단계를 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법. - 제 3 항에 있어서,

상기 스위프의 모든 스텝에 대하여, 각각의 서브 시스템의 출력을 저장하는 단계를 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법. - 제 1 항에 있어서,

파라미터 값들의 원하는 세트를 결정하기 위해 시스템의 출력을 평가하는 단계를 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 방법. - 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치로서,

메모리 모듈; 및

상기 메모리 모듈에 커플링된 적어도 하나의 프로세서를 포함하고,

상기 적어도 하나의 프로세서는,

상기 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 상기 서브 시스템들을 직렬화하는 것, 및 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 상기 서브 시스템들을 병렬화하는 것, 중 적어도 하나를 수행하고; 그리고

각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하도록

구성되는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 6 항에 있어서,

상기 적어도 하나의 프로세서는 또한, 메모리 스토리지 요건들, 메모리 액세스 시간, 및/또는 계산 시간에 적어도 부분적으로 기초하여 병렬화, 직렬화 및/또는 프루닝하도록 구성되는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 6 항에 있어서,

상기 적어도 하나의 프로세서는 또한, 네트워크의 접속성 및/또는 상기 파라미터 스위프의 활동 레벨들을 모니터링하는 것에 적어도 부분적으로 기초하여 서브 시스템들을 정의하도록 구성되는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 8 항에 있어서,

상기 적어도 하나의 프로세서는 또한, 상기 스위프의 모든 스텝에 대하여, 각각의 서브 시스템의 출력을 저장하도록 구성되는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 6 항에 있어서,

상기 적어도 하나의 프로세서는 또한, 파라미터 값들의 원하는 세트를 결정하기 위해 시스템의 출력을 평가하도록 구성되는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치로서,

상기 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 상기 서브 시스템들을 직렬화하는 수단, 및 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 상기 서브 시스템들을 병렬화하는 수단, 중 적어도 하나; 및

각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하는 수단을 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 11 항에 있어서,

상기 병렬화하는 수단, 직렬화하는 수단 및/또는 프루닝하는 수단은, 메모리 스토리지 요건들, 메모리 액세스 시간, 및/또는 계산 시간에 적어도 부분적으로 기초하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 11 항에 있어서,

네트워크의 접속성 및/또는 상기 파라미터 스위프의 활동 레벨들을 모니터링하는 것에 적어도 부분적으로 기초하여 서브 시스템들을 정의하는 수단을 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 13 항에 있어서,

상기 스위프의 모든 스텝에 대하여, 각각의 서브 시스템의 출력을 저장하는 수단을 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 제 11 항에 있어서,

파라미터 값들의 원하는 세트를 결정하기 위해 시스템의 출력을 평가하는 수단을 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 장치. - 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품으로서,

프로그램 코드가 기록된 비일시적 컴퓨터 판독가능 매체를 포함하고,

상기 프로그램 코드는,

상기 시스템의 서브 시스템들 사이의 단방향 의존성들을 결정하는 것에 의해 상기 서브 시스템들을 직렬화하는 것, 및 각각의 서브 시스템 내의 독립성들을 결정하는 것에 의해 상기 서브 시스템들을 병렬화하는 것, 중 적어도 하나를 수행하기 위한 프로그램 코드; 및

각각의 입력 파라미터가 각각의 서브 시스템에 영향을 미치는지 여부에 기초하여 각각의 서브 시스템의 입력 파라미터들을 프루닝하기 위한 프로그램 코드를 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품. - 제 16 항에 있어서,

상기 병렬화, 직렬화 및/또는 프루닝하기 위한 코드는, 메모리 스토리지 요건들, 메모리 액세스 시간, 및/또는 계산 시간에 적어도 부분적으로 기초하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품. - 제 16 항에 있어서,

상기 프로그램 코드는, 네트워크의 접속성 및/또는 상기 파라미터 스위프의 활동 레벨들을 모니터링하는 것에 적어도 부분적으로 기초하여 서브 시스템들을 정의하기 위한 프로그램 코드를 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품. - 제 18 항에 있어서,

상기 프로그램 코드는, 상기 스위프의 모든 스텝에 대하여, 각각의 서브 시스템의 출력을 저장하기 위한 프로그램 코드들 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품. - 제 16 항에 있어서,

상기 프로그램 코드는, 파라미터 값들의 원하는 세트를 결정하기 위해 시스템의 출력을 평가하기 위한 프로그램 코드를 더 포함하는, 단방향 의존성들로 서브 시스템들을 갖는 시스템에 걸쳐 파라미터 스위프를 수행하기 위한 컴퓨터 프로그램 제품.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/065,388 US9721204B2 (en) | 2013-10-28 | 2013-10-28 | Evaluation of a system including separable sub-systems over a multidimensional range |

| US14/065,388 | 2013-10-28 | ||

| PCT/US2014/061220 WO2015065738A2 (en) | 2013-10-28 | 2014-10-17 | Evaluation of a system including separable sub-systems over a multidimensional range |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160076531A true KR20160076531A (ko) | 2016-06-30 |

Family

ID=51897437

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167013660A KR20160076531A (ko) | 2013-10-28 | 2014-10-17 | 다차원 범위에 걸쳐 분리가능한 서브 시스템들을 포함하는 시스템의 평가 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US9721204B2 (ko) |

| EP (1) | EP3063707A2 (ko) |

| JP (1) | JP2016538633A (ko) |

| KR (1) | KR20160076531A (ko) |

| CN (1) | CN105580031B (ko) |

| CA (1) | CA2926649A1 (ko) |

| TW (1) | TW201525883A (ko) |

| WO (1) | WO2015065738A2 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102624947B1 (ko) * | 2023-11-28 | 2024-01-15 | 주식회사 티알씨일렉트릭 | 전동기 역설계 장치 및 방법 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10417554B2 (en) * | 2014-05-22 | 2019-09-17 | Lee J. Scheffler | Methods and systems for neural and cognitive processing |

| US10515312B1 (en) * | 2015-12-30 | 2019-12-24 | Amazon Technologies, Inc. | Neural network model compaction using selective unit removal |

| CN106203621B (zh) * | 2016-07-11 | 2019-04-30 | 北京深鉴智能科技有限公司 | 用于卷积神经网络计算的处理器 |

| US11315018B2 (en) | 2016-10-21 | 2022-04-26 | Nvidia Corporation | Systems and methods for pruning neural networks for resource efficient inference |

| EP3340129B1 (en) * | 2016-12-21 | 2019-01-30 | Axis AB | Artificial neural network class-based pruning |

| US11188820B2 (en) * | 2017-09-08 | 2021-11-30 | International Business Machines Corporation | Deep neural network performance analysis on shared memory accelerator systems |

| US11948351B2 (en) * | 2018-01-17 | 2024-04-02 | Signify Holding B.V. | System and method for object recognition using neural networks |

| CN110570616B (zh) * | 2019-09-10 | 2020-09-25 | 淮阴工学院 | 一种基于物联网的多点火灾预警系统 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69128996T2 (de) | 1990-10-10 | 1998-09-10 | Honeywell Inc | Identifizierung eines Prozesssystems |

| CA2060554A1 (en) | 1991-04-18 | 1992-10-19 | Shawn Michael Austvold | Apparatus and method for facilitating use of a neural network |

| JP3182112B2 (ja) * | 1997-04-28 | 2001-07-03 | 東京電力株式会社 | 建物外観の色彩決定支援システム |

| JP2004094437A (ja) * | 2002-08-30 | 2004-03-25 | Fuji Electric Holdings Co Ltd | データ予測方法及びデータ予測システム |

| US7496546B2 (en) * | 2003-03-24 | 2009-02-24 | Riken | Interconnecting neural network system, interconnecting neural network structure construction method, self-organizing neural network structure construction method, and construction programs therefor |

| US20060224533A1 (en) | 2005-03-14 | 2006-10-05 | Thaler Stephen L | Neural network development and data analysis tool |

| US7502763B2 (en) | 2005-07-29 | 2009-03-10 | The Florida International University Board Of Trustees | Artificial neural network design and evaluation tool |

| US8103606B2 (en) * | 2006-12-08 | 2012-01-24 | Medhat Moussa | Architecture, system and method for artificial neural network implementation |

| WO2008112921A1 (en) | 2007-03-14 | 2008-09-18 | Halliburton Energy Services, Inc. | Neural-network based surrogate model construction methods and applications thereof |

| CN101893541A (zh) * | 2010-06-09 | 2010-11-24 | 哈尔滨工业大学 | 建立纤维增强树脂基复合材料孔隙问题的表征与评价模型的方法 |

-

2013

- 2013-10-28 US US14/065,388 patent/US9721204B2/en active Active

-

2014

- 2014-10-17 CN CN201480052142.0A patent/CN105580031B/zh not_active Expired - Fee Related

- 2014-10-17 KR KR1020167013660A patent/KR20160076531A/ko not_active Application Discontinuation

- 2014-10-17 CA CA2926649A patent/CA2926649A1/en not_active Abandoned

- 2014-10-17 WO PCT/US2014/061220 patent/WO2015065738A2/en active Application Filing

- 2014-10-17 JP JP2016526188A patent/JP2016538633A/ja active Pending

- 2014-10-17 EP EP14796943.0A patent/EP3063707A2/en not_active Withdrawn

- 2014-10-23 TW TW103136675A patent/TW201525883A/zh unknown

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102624947B1 (ko) * | 2023-11-28 | 2024-01-15 | 주식회사 티알씨일렉트릭 | 전동기 역설계 장치 및 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN105580031A (zh) | 2016-05-11 |

| EP3063707A2 (en) | 2016-09-07 |

| CN105580031B (zh) | 2018-01-16 |

| US9721204B2 (en) | 2017-08-01 |

| CA2926649A1 (en) | 2015-05-07 |

| JP2016538633A (ja) | 2016-12-08 |

| US20150120632A1 (en) | 2015-04-30 |

| TW201525883A (zh) | 2015-07-01 |

| WO2015065738A2 (en) | 2015-05-07 |

| WO2015065738A3 (en) | 2015-07-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101793011B1 (ko) | 스파이킹 네트워크들의 효율적인 하드웨어 구현 | |

| US9886663B2 (en) | Compiling network descriptions to multiple platforms | |

| KR20160076531A (ko) | 다차원 범위에 걸쳐 분리가능한 서브 시스템들을 포함하는 시스템의 평가 | |

| US9558442B2 (en) | Monitoring neural networks with shadow networks | |

| US9330355B2 (en) | Computed synapses for neuromorphic systems | |

| US20150206050A1 (en) | Configuring neural network for low spiking rate | |

| KR101700145B1 (ko) | 뉴럴 역학을 수정하기 위한 자동화 방법 | |

| KR20170031695A (ko) | 신경망들에서의 콘볼루션 동작의 분해 | |

| KR20160076520A (ko) | 인과적 현출성 시간 추론 | |

| KR20160136381A (ko) | 신경 네트워크들에서의 차분 인코딩 | |

| US9600762B2 (en) | Defining dynamics of multiple neurons | |

| KR20160123309A (ko) | 확률적 스파이킹 베이지안망들에 대한 이벤트-기반 추론 및 학습 | |

| KR20160084401A (ko) | 스파이킹 뉴럴 네트워크들에서 리플레이를 사용한 시냅스 학습의 구현 | |

| KR20160145636A (ko) | 스파이킹 뉴럴 네트워크에서의 글로벌 스칼라 값들에 의한 가소성 조절 | |

| US10552734B2 (en) | Dynamic spatial target selection | |

| US20150278685A1 (en) | Probabilistic representation of large sequences using spiking neural network | |

| KR101825937B1 (ko) | 가소성 시냅스 관리 | |

| KR101782760B1 (ko) | 시냅스 지연의 동적 할당 및 검사 | |

| KR20160124791A (ko) | 좌표 변환을 위한 위상 코딩 | |

| KR20160123312A (ko) | 스파이킹 뉴럴 네트워크에서의 청각 소스 분리 | |

| KR20160132850A (ko) | 뉴로모픽 모델 개발을 위한 콘텍스트 실시간 피드백 | |

| US20150242742A1 (en) | Imbalanced cross-inhibitory mechanism for spatial target selection |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Withdrawal due to no request for examination |