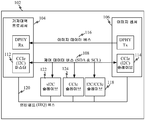

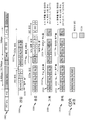

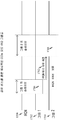

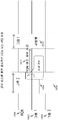

KR20160066032A - 공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 - Google Patents

공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 Download PDFInfo

- Publication number

- KR20160066032A KR20160066032A KR1020167010854A KR20167010854A KR20160066032A KR 20160066032 A KR20160066032 A KR 20160066032A KR 1020167010854 A KR1020167010854 A KR 1020167010854A KR 20167010854 A KR20167010854 A KR 20167010854A KR 20160066032 A KR20160066032 A KR 20160066032A

- Authority

- KR

- South Korea

- Prior art keywords

- shared bus

- bus

- line

- protocol mode

- mode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

- G06F13/4291—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus using a clocked protocol

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/362—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control

- G06F13/364—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control using independent requests or grants, e.g. using separated request and grant lines

-

- Y02B60/1228—

-

- Y02B60/1235—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Information Transfer Systems (AREA)

- Bus Control (AREA)

- Small-Scale Networks (AREA)

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361888475P | 2013-10-08 | 2013-10-08 | |

| US61/888,475 | 2013-10-08 | ||

| US201461927102P | 2014-01-14 | 2014-01-14 | |

| US61/927,102 | 2014-01-14 | ||

| US201461974910P | 2014-04-03 | 2014-04-03 | |

| US61/974,910 | 2014-04-03 | ||

| PCT/US2014/059776 WO2015054433A1 (en) | 2013-10-08 | 2014-10-08 | Coexistence of i2c slave devices and camera control interface extension devices on a shared control data bus |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160066032A true KR20160066032A (ko) | 2016-06-09 |

Family

ID=51790888

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167010854A Withdrawn KR20160066032A (ko) | 2013-10-08 | 2014-10-08 | 공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20150100713A1 (enExample) |

| EP (1) | EP3055779B1 (enExample) |

| JP (1) | JP2016538624A (enExample) |

| KR (1) | KR20160066032A (enExample) |

| CN (1) | CN105612507A (enExample) |

| WO (1) | WO2015054433A1 (enExample) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9921981B2 (en) * | 2013-08-24 | 2018-03-20 | Qualcomm Incorporated | Method to minimize the number of IRQ lines from peripherals to one wire |

| US9519603B2 (en) | 2013-09-09 | 2016-12-13 | Qualcomm Incorporated | Method and apparatus to enable multiple masters to operate in a single master bus architecture |

| US9996488B2 (en) | 2013-09-09 | 2018-06-12 | Qualcomm Incorporated | I3C high data rate (HDR) always-on image sensor 8-bit operation indicator and buffer over threshold indicator |

| US10353837B2 (en) | 2013-09-09 | 2019-07-16 | Qualcomm Incorporated | Method and apparatus to enable multiple masters to operate in a single master bus architecture |

| US9690725B2 (en) | 2014-01-14 | 2017-06-27 | Qualcomm Incorporated | Camera control interface extension with in-band interrupt |

| US9678828B2 (en) | 2013-10-09 | 2017-06-13 | QUAULCOMM Incorporated | Error detection capability over CCIe protocol |

| US9684624B2 (en) | 2014-01-14 | 2017-06-20 | Qualcomm Incorporated | Receive clock calibration for a serial bus |

| US10417172B2 (en) | 2014-04-28 | 2019-09-17 | Qualcomm Incorporated | Sensors global bus |

| US9734121B2 (en) | 2014-04-28 | 2017-08-15 | Qualcomm Incorporated | Sensors global bus |

| US10067895B2 (en) * | 2015-06-03 | 2018-09-04 | Lexmark International, Inc. | Systems and methods for asynchronous toggling of I2C data line |

| US9727506B2 (en) * | 2015-10-01 | 2017-08-08 | Sony Corporation | Communication system, communication system control method, and program |

| KR102500821B1 (ko) * | 2015-12-29 | 2023-02-17 | 삼성전자주식회사 | 복수의 회로들 및 복수의 회로들을 연결하는 버스를 포함하는 반도체 장치 및 반도체 장치의 동작 방법 |

| EP3411956A1 (en) | 2016-02-01 | 2018-12-12 | Qualcomm Incorporated | Programmable distributed data processing in a serial link |

| US9979432B2 (en) | 2016-02-01 | 2018-05-22 | Qualcomm Incorporated | Programmable distributed data processing in a serial link |

| US10159053B2 (en) | 2016-02-02 | 2018-12-18 | Qualcomm Incorporated | Low-latency low-uncertainty timer synchronization mechanism across multiple devices |

| US10031882B2 (en) | 2016-03-31 | 2018-07-24 | Intel Corporation | Sensor bus communication system |

| TWI625630B (zh) * | 2016-08-02 | 2018-06-01 | 緯穎科技服務股份有限公司 | 電腦系統及匯流排仲裁方法 |

| US9881664B1 (en) * | 2017-01-12 | 2018-01-30 | Cadence Design Systems, Inc. | Per-group delay line architecture to de-skew input/output timing between a high bandwidth memory (HBM) physical (PHY) interface and the HBM device |

| US10713199B2 (en) * | 2017-06-27 | 2020-07-14 | Qualcomm Incorporated | High bandwidth soundwire master with multiple primary data lanes |

| US10614009B2 (en) * | 2018-03-16 | 2020-04-07 | Qualcomm Incorporated | Asynchronous interrupt with synchronous polling and inhibit options on an RFFE bus |

| US10496562B1 (en) | 2018-08-13 | 2019-12-03 | Qualcomm Incorporated | Low latency virtual general purpose input/output over I3C |

| US20200065274A1 (en) * | 2018-08-23 | 2020-02-27 | Qualcomm Incorporated | Always-on ibi handling |

| US10725949B2 (en) * | 2018-08-28 | 2020-07-28 | Qualcomm Incorporated | Slave-to-slave direct communication |

| US11030133B2 (en) * | 2018-08-30 | 2021-06-08 | Qualcomm Incorporated | Aggregated in-band interrupt based on responses from slave devices on a serial data bus line |

| EP3900285B1 (en) * | 2018-11-14 | 2024-01-03 | Sonova AG | Operating more than one wireless communication protocol with a coexistence window |

| WO2021010969A1 (en) | 2019-07-15 | 2021-01-21 | Hewlett-Packard Development Company L.P. | Communication bus with isolation circuit |

| US11662846B2 (en) | 2019-09-26 | 2023-05-30 | Chongqing Boe Optoelectronics Technology Co., Ltd. | Touch circuit and driving method thereof, and driving system for a touch display device |

| CN110531899B (zh) * | 2019-09-26 | 2024-03-05 | 京东方科技集团股份有限公司 | 用于笔记本电脑的驱动系统 |

| JP7255777B2 (ja) * | 2019-12-16 | 2023-04-11 | 島津システムソリューションズ株式会社 | データ処理装置 |

| CN111835610B (zh) * | 2020-05-29 | 2022-05-03 | 中车株洲电力机车研究所有限公司 | 数据共享方法、系统、存储介质及电子设备 |

| US11088815B1 (en) * | 2020-10-02 | 2021-08-10 | Qualcomm Incorporated | Techniques for timed-trigger and interrupt coexistence |

| US11995012B2 (en) | 2022-03-15 | 2024-05-28 | Samsung Electronics Co., Ltd. | High speed interface for multi image sensor device |

| CN115632900B (zh) * | 2022-08-31 | 2023-09-01 | 超聚变数字技术有限公司 | 一种计算设备 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04123692A (ja) * | 1990-09-14 | 1992-04-23 | Matsushita Electric Works Ltd | 時分割多重伝送システムの割込処理方式 |

| US5376928A (en) * | 1992-09-18 | 1994-12-27 | Thomson Consumer Electronics, Inc. | Exchanging data and clock lines on multiple format data buses |

| DE69515147T2 (de) * | 1994-07-15 | 2000-09-21 | Thomson Consumer Electronics, Inc. | Mehrfachprotokoll-Datenbussystem |

| US6111437A (en) * | 1998-05-29 | 2000-08-29 | Lucent Technologies Inc. | Wide common-mode differential receiver with precision input referred offset |

| US6253268B1 (en) * | 1999-01-15 | 2001-06-26 | Telefonaktiebolaget L M Ericsson (Publ) | Method and system for multiplexing a second interface on an I2C interface |

| US6912606B2 (en) * | 2001-06-08 | 2005-06-28 | Sycamore Networks, Inc. | Generic serial bus architecture |

| US7089338B1 (en) * | 2002-07-17 | 2006-08-08 | Cypress Semiconductor Corp. | Method and apparatus for interrupt signaling in a communication network |

| US20070088874A1 (en) * | 2005-10-14 | 2007-04-19 | Hewlett-Packard Development Company, L.P. | Offload engine as processor peripheral |

| JP5272704B2 (ja) * | 2008-12-17 | 2013-08-28 | 富士ゼロックス株式会社 | 情報伝送システム、情報送信装置及び情報受信装置 |

| CN103764934B (zh) * | 2011-03-16 | 2017-11-24 | 阿萨阿布洛伊澳大利亚有限公司 | 用于窗或门的链卷绕器 |

| US8898358B2 (en) * | 2012-07-04 | 2014-11-25 | International Business Machines Corporation | Multi-protocol communication on an I2C bus |

-

2014

- 2014-10-08 WO PCT/US2014/059776 patent/WO2015054433A1/en not_active Ceased

- 2014-10-08 US US14/510,069 patent/US20150100713A1/en not_active Abandoned

- 2014-10-08 EP EP14787359.0A patent/EP3055779B1/en not_active Not-in-force

- 2014-10-08 JP JP2016520667A patent/JP2016538624A/ja not_active Ceased

- 2014-10-08 CN CN201480055818.1A patent/CN105612507A/zh active Pending

- 2014-10-08 KR KR1020167010854A patent/KR20160066032A/ko not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| EP3055779B1 (en) | 2017-08-02 |

| WO2015054433A1 (en) | 2015-04-16 |

| JP2016538624A (ja) | 2016-12-08 |

| CN105612507A (zh) | 2016-05-25 |

| EP3055779A1 (en) | 2016-08-17 |

| US20150100713A1 (en) | 2015-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20160066032A (ko) | 공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 | |

| EP3095038B1 (en) | Camera control interface extension with in-band interrupt | |

| US9684624B2 (en) | Receive clock calibration for a serial bus | |

| EP3254203B1 (en) | Receive clock calibration for a serial bus | |

| US10353837B2 (en) | Method and apparatus to enable multiple masters to operate in a single master bus architecture | |

| JP6190068B2 (ja) | 複数のマスタがシングルマスタバスアーキテクチャにおいて動作できるようにする方法および装置 | |

| US20150095537A1 (en) | Camera control interface sleep and wake up signaling | |

| KR20160147842A (ko) | 센서 글로벌 버스 | |

| JP2016533608A (ja) | カメラ制御インターフェースのスレーブデバイス間通信 | |

| US20150234774A1 (en) | Coexistence of legacy and next generation devices over a shared multi-mode bus | |

| KR20170126904A (ko) | 공유 멀티 모드 버스 상에서 레거시 및 차세대 디바이스들의 공존을 위한 페어웰 리셋 및 재시작 방법 | |

| US10139875B2 (en) | Farewell reset and restart method for coexistence of legacy and next generation devices over a shared multi-mode bus | |

| US9990330B2 (en) | Simultaneous edge toggling immunity circuit for multi-mode bus | |

| WO2015126983A1 (en) | Technique to avoid metastability condition and avoid unintentional state changes of legacy i2c devices on a multi-mode bus | |

| JPH03174643A (ja) | 直列データ母線用アプリケーシヨン特有集積回路 | |

| WO2017172269A1 (en) | Method and apparatus to enable multiple masters to operate in a single master bus architecture | |

| KR20010004694A (ko) | 통신 장치의 보드간 데이터 송수신 장치 및 그를 이용한 데이터 송수신 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20160425 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |