KR20160066032A - 공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 - Google Patents

공유 제어 데이터 버스에서의 i2c 슬레이브 디바이스들과 카메라 제어 인터페이스 확장 디바이스들의 공존 Download PDFInfo

- Publication number

- KR20160066032A KR20160066032A KR1020167010854A KR20167010854A KR20160066032A KR 20160066032 A KR20160066032 A KR 20160066032A KR 1020167010854 A KR1020167010854 A KR 1020167010854A KR 20167010854 A KR20167010854 A KR 20167010854A KR 20160066032 A KR20160066032 A KR 20160066032A

- Authority

- KR

- South Korea

- Prior art keywords

- shared bus

- bus

- line

- protocol mode

- mode

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

- G06F13/4291—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus using a clocked protocol

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/362—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control

- G06F13/364—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control using independent requests or grants, e.g. using separated request and grant lines

-

- Y02B60/1228—

-

- Y02B60/1235—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Information Transfer Systems (AREA)

- Small-Scale Networks (AREA)

- Bus Control (AREA)

Abstract

복수의 슬레이브 디바이스들은 제어 데이터 버스에 대한 슬레이브 디바이스들의 액세스를 관리하는 적어도 하나의 마스터 디바이스와 함께 제어 데이터 버스에 연결된다. 적어도 하나의 슬레이브 디바이스는 sI2C 프로토콜 동작의 모드로 동작하고, 적어도 하나의 다른 슬레이브 디바이스는 CCIe 동작의 모드로 동작한다. sI2C 프로토콜 모드를 이용하는 적어도 하나의 슬레이브 디바이스들은 인터럽트 요청들을 위해 제어 데이터 버스를 이용한다. CCIe 통신들의 무결성을 유지하기 위해, sI2C 프로토콜 모드를 이용하는 슬레이브 디바이스들은 제어 데이터 버스가 CCIe 모드에 따라 동작하는 경우 IRQ 들을 발행하는 것을 디스에이블한다.

Description

관련 출원들에 대한 상호-참조

본 특허 출원은 "Coexistent of I2C Slave Devices and Camera Control Interface Extension Devices on a Shared Control Data Bus" 라는 발명의 명칭으로 2013 년 10 월 8 일에 출원된 가출원 제 61/888,475호, 및 "Coexistent of I2C Slave Devices and Camera Control Interface Extension Devices on a Shared Control Data Bus" 라는 발명의 명칭으로 2014 년 4 월 3 일에 출원된 가출원 제 61/974,910호, 및 "Camera Control Interface Extension With In-Band Interrupt" 라는 발명의 명칭으로 2014 년 1 월 14 일에 출원된 가출원 제 61/927,102 호의 우선권을 주장하며, 이 모두는 본원의 양수인에게 양도되고 본원에 참조로서 명시적으로 포함된다.

기술분야

본 개시물은 공유 버스를 통한 다중모드 동작들을 인에이블하는 것에 관한 것으로, 좀더 구체적으로, 단일의 버스를 공유하도록 상이한 프로토콜들을 갖는 디바이스들을 인에이블하는 것에 관한 것이다.

인터 집적 회로 (Inter Integrated Circuit) (이하 "I2C", 그리고 I2C 라고도 지칭됨) 는 저속 주변기기들을 마더보드, 임베디드 시스템, 휴대전화, 또는 다른 전자 디바이스들에 연결하는데 이용되는 다중-마스터 직렬 단일-종단 버스이다. I2C 버스는 7-비트 어드레싱을 갖는 클록 (SCL) 및 데이터 (SDA) 라인들을 포함한다. 버스는 노드들 또는 디바이스들: 마스터 디바이스 및 슬레이브 디바이스에 대해 2 개의 역할들을 갖는다. 마스터 노드/디바이스는 클록을 생성하고 슬레이브 노드/디바이스와 통신을 개시하는 노드/디바이스이다. 슬레이브 노드/디바이스는 마스터에 의해 어드레싱되는 경우 클록을 수신하고 응답하는 노드이다. I2C 버스는 다중-마스터 버스인데, 이는 임의의 개수의 마스터 디바이스들이 존재할 수 있음을 의미한다. 또한, 마스터 및 슬레이브 역할들은 (STOP 이 전송된 후에) 메시지들 사이에서 변화될 수도 있다. I2C 는 메시지들의 기본 유형들을 정의하며, 그것들의 각각은 START 로 시작하고 STOP 으로 종료한다.

이러한 카메라 구현의 맥락에서는, 센서로부터 이미지를 캡쳐하여 그러한 이미지 데이터를 기저대역 프로세서로 메모리에 송신하는데 단방향 송신들이 이용될 수도 있고, 한편 기저대역 프로세서와 센서 뿐만 아니라 다른 주변 디바이스들 사이에 제어 데이터가 교환될 수도 있다. 일 예에서, 카메라 제어 인터페이스 (Camera Control Interface; CCI) 프로토콜이 기저대역 프로세서와 이미지 센서 (및/또는 하나 이상의 슬레이브 디바이스들) 사이의 그러한 제어 데이터로 이용될 수도 있다. 일 예에서, CCI 프로토콜은 이미지 센서와 기저대역 프로세서 사이의 I2C 직렬 버스를 통해 구현될 수도 있다.

기술이 진화함에 따라, I2C 버스에서의 "핫 플러그 (hot plug)" 기능에 대한 필요가 있다. "핫 플러그" 는, 슬레이브 디바이스와 같은 디바이스들이 이미 활성인 버스에 플러깅될 수도 있음 (즉, 버스를 셧 다운 시키지 않음) 을 의미한다. 이러한 핫 플러그 기능은 서브세트 I2C (즉, sI2C) 라고 불리는 것으로 달성된다. sI2C 는 (SCL 및 SDA 와 함께) 슬레이브 디바이스들이 인터럽트 요청 (interrupt request; IRQ) 들을 수행하는 수단으로서 제어 데이터 버스를 활용한다. 또한, CCI 프로토콜의 속도를 증가시키려는 욕구로 인해, CCI 프로토콜을 통해 속도를 증가시키는 CCI 확장 (CCI extension; CCIe) 프로토콜이 본원에서 설명된다. 그러나, SDA 를 이용하여 IRQ 들을 수행하는 슬레이브 디바이스들은 전용 IRQ 라인을 제공하는 CCIe 프로토콜과 호환가능하지 않다.

따라서, CCI 프로토콜을 통해 속도를 증가시키고 동시에 sI2C 프로토콜 슬레이브 디바이스들이 CCIe 디바이스들과 공존하고 CCIe 버스에 핫 플러깅가능하게 하는 방식이 필요하다.

공유 버스, 제 1 슬레이브 디바이스, 제 2 슬레이브 디바이스, 및/또는 마스터 디바이스를 포함하는 디바이스가 제공된다. 제 1 슬레이브 디바이스는 공유 버스에 연결될 수도 있고, (a) 공유 버스를 통해 대역-내 인터럽트 요청들을 발행하는 것을 포함하는 제 1 프로토콜 모드에 따라 동작하고; (b) 공유 버스가 제 2 프로토콜 모드로 스위칭하고 있다는 것을 나타내는 진입 호에 대해 공유 버스를 모니터링하고; 및/또는 (c) 진입 호의 검출 시에, 제 1 슬레이브 디바이스가 공유 버스를 통해 대역-내 인터럽트 요청들을 하는 것을 디스에이블하도록 구성된다.

제 2 슬레이브 디바이스는 공유 버스에 연결될 수도 있고, (a) 인터럽트 버스를 통해 측파-대역 인터럽트 요청들 또는 공유 버스를 통해 대역-내 인터럽트 요청을 발행하는 것을 포함하여 제 2 프로토콜 모드에 따라 동작하고; 및/또는 (b) 공유 버스를 통해 진입 호를 검출하도록 구성된다 (진입 호는 제 2 프로토콜 모드에 따라 송신된다).

마스터 디바이스는 공유 버스에 연결될 수도 있고, (a) 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두에 따라 동작하고; (b) 공유 버스를 통해 통신들을 관리하고; (c) 공유 버스가 제 2 프로토콜 모드로 스위칭되는 것을 나타내는 진입 호를 공유 버스를 통해 전송하고 (여기서 진입 호는 제 1 프로토콜 모드에 따라 전송된다); (d) 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두에 따라 슬레이브 디바이스들로부터의 인터럽트 요청들을 검출하고; 및/또는 (e) 요청하는 슬레이브 디바이스가 공유 버스에 액세스하는 것을 승인함으로써 인터럽트 요청들에 응답하도록 구성된다.

마스터 디바이스는 공유 버스가 제 1 프로토콜 모드로 스위칭하는 것을 나타내는 종료 호 (exit call) 를 공유 버스를 통해 전송하도록 더 구성될 수도 있으며, 여기서 종료 호는 제 2 프로토콜 모드 및 제 1 프로토콜 모드 양자 모두에 따라 전송된다.

대역-내 인터럽트들에 있어서, 제 2 프로토콜은 공유 버스를 통해 심볼들이 송신되는 인터럽트 기간을 정의하며, 그 동안에 공유 버스에 연결된 하나 이상의 슬레이브 디바이스들은 공유 버스의 제 1 라인에 대한 인터럽트 요청을 어써트할 (assert) 수 있고, 한편 공유 버스의 제 2 라인은 하트비트 (heartbeat) 송신을 위해 마스터 디바이스에 의해 이용된다. 일 구현에서, 마스터 디바이스 및 제 2 슬레이브 디바이스는 인터럽트 기간 중에 공유 버스의 제 1 라인을 내부적으로 마스킹하도록 구성될 수도 있다.

마스터 디바이스는 공유 버스로 제 2 프로토콜 모드에 따라 동작하는 인터럽트 그룹 질의 호를 모든 슬레이브 디바이스들에 전송하도록 구성될 수도 있으며, 여기서 그러한 인터럽트 그룹 질의 호는 임의의 어써트하는 슬레이브 디바이스들이 응답할 수 있는 슬롯들을 제공한다.

제 2 슬레이브 디바이스는 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우 제 2 프로토콜 모드에 따라 공유 버스를 통해 데이터 또는 커맨드들을 수신하도록 더 구성될 수도 있다.

제 1 슬레이브 디바이스는 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 동안 전용 인터럽트 라인 또는 공유 버스와 별개인 버스를 통해 인터럽트 요청을 전송하도록 더 구성될 수도 있다.

디바이스는 또한 전용 라인을 통해 제 1 슬레이브 디바이스로부터 인터럽트 요청들을 수신하고 전용 인터럽트 버스 또는 제 2 프로토콜에 따른 버스를 통해 수신된 인터럽트 요청을 전송하도록 구성된 인터럽트 라우터 슬레이브 디바이스를 포함할 수도 있다.

일 예에서, 공유 버스는 제 1 라인 및 제 2 라인을 포함할 수도 있다. 공유 버스가 제 1 프로토콜 모드에 따라 동작하는 경우, 제 1 라인은 데이터 송신들을 위해 이용되고 제 2 라인은 제 1 클록 신호를 위해 이용된다. 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우, 제 1 라인 및 제 2 라인 양자 모두는 데이터 송신들을 위해 이용되고, 한편 제 2 클록 신호는 데이터 송신들과 함께 심볼-투-심볼 전환들에 임베딩된다.

다중-모드 마스터 디바이스는 제 1 버스 인터페이스, 제 2 버스 인터페이스, 및 프로세싱 회로를 포함할 수도 있다. 제 1 버스 인터페이스는 공유 제어 데이터 버스에 연결된 다른 디바이스들에 연결하는 역할을 할 수도 있으며, 데이터 버스는 제 1 프로토콜 모드 또는 제 2 프로토콜 모드로 동작하도록 동적으로 구성된다. 제 2 버스 인터페이스는 적어도 다른 디바이스들의 서브세트에 의해 이용되고 제 2 프로토콜 모드에서 전용 인터럽트 라인을 통해 인터럽트 요청들을 발행하는 전용 인터럽트 라인에 연결하는 역할을 할 수도 있다. 프로세싱 회로는 (a) 복수의 다른 디바이스들이 연결되는 공유 버스를 통한 데이터 전송들을 관리하고 (여기서 적어도 다른 디바이스들의 제 1 서브세트는 제 1 프로토콜 모드에 따라 동작하고 다른 디바이스들의 제 2 서브세트는 제 1 프로토콜 모드와 호환불가능한 제 2 프로토콜 모드에 따라 동작한다); (b) (1) 공유 버스가 제 2 프로토콜 모드에 따라 동작할 것임을 나타내는 진입 호를 공유 버스를 통해 전송하고, 및/또는 (2) 공유 버스가 제 1 프로토콜 모드에 따라 동작할 것임을 나타내는 종료 호를 공유 버스를 통해 전송함으로써, 제 1 프로토콜과 제 2 프로토콜 모드 사이에서 공유 버스의 동작을 동적으로 스위칭하도록 구성될 수도 있다.

마스터 디바이스는 (a) 공유 버스가 제 1 프로토콜 모드에 따라 동작하는 경우 공유 버스를 통해 디바이스들의 제 1 서브세트로부터 인터럽트 요청들을 수신하고; (b) 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우 전용 인터럽트 버스를 통해 디바이스들의 제 2 서브세트로부터 인터럽트 요청들을 수신하고; 및/또는 (c) 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우 통해 전용 인터럽트 버스를 통해 디바이스들의 제 1 서브세트로부터 인터럽트 요청들을 수신하도록 더 구성될 수도 있다. 일 구현에서, 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우 디바이스들의 제 1 서브세트로부터 어떠한 인터럽트 요청들도 수신되지 않는다.

공유 버스는 제 1 라인 및 제 2 라인을 포함한다. 공유 버스가 제 1 프로토콜 모드에 따라 동작하는 경우, 제 1 라인은 데이터 송신들을 위해 이용되고 제 2 라인은 제 1 클록 신호를 위해 이용된다. 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우, 제 1 라인 및 제 2 라인 양자 모두는 데이터 송신들을 위해 이용되고, 한편 제 2 클록 신호는 데이터 송신들과 함께 심볼-투-심볼 전환들에 임베딩된다.

제 2 프로토콜은 공유 버스를 통해 심볼들이 송신되는 인터럽트 기간을 정의할 수도 있으며, 그 기간 중에 다른 디바이스들의 제 2 서브세트는 공유 버스의 제 1 라인에 대해 인터럽트 요청을 어써트할 수도 있고 한편 공유 버스의 제 2 라인은 하트비트 송신을 위해 마스터 디바이스에 의해 이용된다.

마스터 디바이스는 또한 인터럽트 기간 중에 공유 버스의 제 1 라인을 내부적으로 마스킹하도록 구성될 수도 있다.

일 구현에서, 제 2 프로토콜 모드에 따라 동작하는 동안에 대역-내 인터럽트 요청에 응답하여, 마스터 디바이스는 공유 버스로 제 2 프로토콜 모드에 따라 동작하는 모든 슬레이브 디바이스들에 인터럽트 그룹 질의 호를 전송할 수도 있으며, 여기서 그러한 인터럽트 그룹 질의 호는 임의의 어써트하는 슬레이브 디바이스들이 응답할 수 있는 슬롯들을 제공한다.

슬레이브 디바이스는 버스 인터페이스 및 프로세싱 회로를 포함할 수도 있다. 버스 인터페이스는 복수의 다른 디바이스들과 공유되는 공유 버스에 연결하는 역할을 할 수도 있으며, 여기서 적어도 다른 디바이스들의 제 1 서브세트는 제 1 프로토콜 모드에 따라 동작하고 슬레이브 디바이스는 제 2 프로토콜 모드에 따라 동작한다.

프로세싱 회로는 (a) 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터 공유 버스를 통해 진입 호를 검출하고 (진입 호는 공유 버스가 제 2 프로토콜 모드에 따라 동작할 것임을 나타낸다); (b) 공유 버스를 통한 대역-내 또는 마스터 디바이스에 대한 별도의 경로를 통한 측파-대역 인터럽트 요청 (IRQ) 을 전송하고; (c) 제 2 프로토콜 모드에 따라 공유 버스를 통해 통신하고; (d) 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링하고; 및/또는 (c) 마스터 디바이스로부터의 종료 호의 검출 시에 슬레이브 디바이스가 공유 버스를 통해 통신하는 것을 디스에이블하도록 구성될 수도 있다. 종료 호는 공유 버스가 제 1 프로토콜 모드에 따라 동작할 것임을 슬레이브 디바이스에 나타내는 역할을 할 수도 있다.

공유 버스는 제 1 라인 및 제 2 라인을 포함할 수도 있다. 공유 버스가 제 1 프로토콜 모드에 따라 동작하는 경우, 제 1 라인은 데이터 송신들을 위해 이용되고 제 2 라인은 제 1 클록 신호를 위해 이용된다. 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우, 제 1 라인 및 제 2 라인 양자 모두는 데이터 송신들을 위해 이용되고, 한편 제 2 클록 신호는 데이터 송신들과 함께 심볼-투-심볼 전환들에 임베딩된다.

슬레이브 디바이스는 버스 인터페이스 및 프로세싱 회로를 포함할 수도 있다. 버스 인터페이스는 복수의 다른 디바이스들과 공유되는 공유 버스에 연결하는 역할을 할 수도 있으며, 여기서 슬레이브 디바이스는 제 1 프로토콜 모드에 따라 동작하고 적어도 다른 디바이스들의 제 1 서브세트는 제 2 프로토콜 모드에 따라 동작한다. 프로세싱 회로는 버스 인터페이스에 연결하는 역할을 할 수도 있고, (a) 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터의 진입 호를 공유 버스를 통해 검출하고 (진입 호는 공유 버스가 제 2 프로토콜 모드에 따라 동작할 것임을 나타낸다); 및/또는 (b) 진입 호의 검출 시에 슬레이브 디바이스가 공유 버스를 통해 대역-내 인터럽트 요청들을 하는 것을 디스에이블하도록 구성될 수도 있다.

프로세싱 회로는 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링하도록 더 구성되며, 종료 호는 공유 버스가 제 1 프로토콜 모드에 따라 동작할 것임을 나타낸다. 공유 버스는 제 1 라인 및 제 2 라인을 포함하며, 공유 버스가 제 1 프로토콜 모드에 따라 동작하는 경우, 제 1 라인은 데이터 송신들에 이용되고 제 2 라인은 제 1 클록 신호에 이용되며, 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우, 제 1 라인 및 제 2 라인 양자 모두는 데이터 송신들에 이용되고 한편 제 2 클록 신호는 데이터 송신들과 함께 심볼-투-심볼 전환들에 임베딩된다.

인터럽트 요청 라우터 슬레이브 디바이스는 제 1 버스 인터페이스, 제 2 버스 인터페이스, 제 3 버스 인터페이스, 및 프로세싱 회로를 포함할 수도 있다. 제 1 버스 인터페이스는 공유 제어 데이터 버스에 연결하는 역할을 할 수도 있으며, 데이터 버스는 제 1 프로토콜 모드 또는 제 2 프로토콜 모드로 동작하도록 동적으로 구성된다. 제 2 버스 인터페이스는 공유 버스에 연결된 다른 슬레이브 디바이스의 적어도 제 1 서브세트에 연결하는 역할을 할 수도 있으며, 다른 슬레이브 디바이스들의 서브세트는 공유 제어 데이터 버스를 통한 대역-내 인터럽트 요청들을 포함하는 제 1 프로토콜 모드에 따라 동작한다. 제 3 버스 인터페이스는 공유 버스를 관리하는 마스터 디바이스에 인터럽트 요청을 발행하는 제 2 프로토콜 모드에서 이용되는 전용 인터럽트 라인에 연결하는 역할을 할 수도 있다. 프로세싱 회로는 (a) 슬레이브 디바이스들의 제 1 서브세트 내의 슬레이브 디바이스로부터 제 2 버스 인터페이스를 통해 인터럽트 요청을 수신하고; 및/또는 (b) 제 3 버스 인터페이스를 통해 마스터 디바이스로 수신된 인터럽트 요청을 라우팅하도록 구성될 수도 있다.

다양한 특징들, 속성, 및 이점들은 도면들과 연계하는 경우 하기에서 제시되는 상세한 설명으로부터 자명할 수도 있으며, 도면들에서 유사한 참조 문자들은 도면전체에 걸쳐 상응하는 부분을 식별한다.

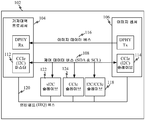

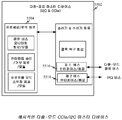

도 1 은 기저대역 프로세서 및 이미지 센서를 구비하고 이미지 데이터 버스 및 다중-모드 제어 데이터 버스를 구현하는 디바이스를 도시하는 블록도이다.

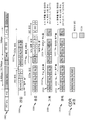

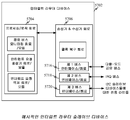

도 2 는 공유 I2C 버스 (예를 들어, 제어 데이터 버스) 를 통한 I2C 모드 (예를 들어, 레거시 CCI 또는 제 1 모드) 와 CCIe 모드 (예를 들어, 제 2 모드) 의 예시적인 공존을 도시하는 블록도이다.

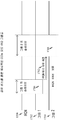

도 3 은 하나 이상의 sI2C 슬레이브 디바이스들, 다중-모드 I2C 및 CCIe 마스터 디바이스, 하나 이상의 I2C 슬레이브 디바이스들, 및 하나 이상의 CCIe 슬레이브 디바이스들을 포함하는 공통 I2C 버스를 통한 I2C 모드 (즉, 레거시 CCI) 와 CCIe 모드의 공존을 도시하는 블록도이다.

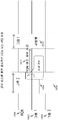

도 4 는 클록이 데이터 심볼들 내에 임베딩됨으로써, 데이터 송신들을 위해 I2C 와이어들 (즉, SDA 라인 및 SCL 라인) 양자 모두의 이용을 가능하게 할 수도 있는 방법을 도시한다.

도 5 는 송신기에서 데이터 비트들을 트랜스코딩된 심볼들로 트랜스코딩하여 트랜스코딩된 심볼들 내에 클록 신호를 임베딩하는 일 예시적인 방법을 도시하는 블록도이다.

도 6 은 전환 수들과 순차 심볼들 사이의 일 예시적인 변환을 도시한다.

도 7 은 전환 수들과 순차 심볼들 사이의 일 예시적인 변환을 더 도시한다.

도 8 은 I2C 1 바이트 기록 데이터 동작의 타이밍도를 도시한다.

도 9 는, sI2C 프로토콜에 따른, sI2C 1 바이트 기록 데이터 동작의 타이밍 도를 도시하며, 여기서 최상위 비트 (most significant bit; MSB) 는 일 (1) 이다.

도 10 은 CCIe 프로토콜의 일 예를 도시한다.

도 11 은 공유 버스를 통해 sI2C-호환가능한 슬레이브 디바이스에 의해 전송되는 일 예시적인 대역-내 인터럽트 신호 (IRQ) 의 도면을 도시한다.

도 12 는 sI2C 슬레이브 디바이스가 혼합된 프로토콜 모드 환경 (예를 들어, 여기서 공유 버스는 구별되는 통신 프로토콜들에 따라 또는 구별되는 통신 프로토콜들 사이에서 동적으로 스위칭하도록 동작할 수 있다) 에서 인터럽트 신호 (IRQ) 를 발행하는 추가적인 방식을 도시한다.

도 13 은 송신기와 수신기 회로 및 프로세싱/로직 회로를 포함하는 일 예시적인 슬레이브 디바이스를 도시한다.

도 14 는 단일-모드 슬레이브 디바이스가 다수의 통신 모드들 사이에서 스위칭하는 공유 데이터 버스에서 공존하는 것을 가능하게 하는 방법을 도시한다.

도 15 는 공유 제어 데이터 버스 및 공유 인터럽트 버스/요청에 연결되는 마스터 디바이스 및 복수의 슬레이브 디바이스들을 구비하는 시스템을 도시하는 블록도이다.

도 16 은 도 15 에서의 복수의 슬레이브 디바이스들이 인터럽트들을 발행할 목적으로 논리적으로 그룹화될 수도 있는 방법을 도시하는 블록도이다.

도 17 은 IRQ 신호들이 IRQ 라인 또는 버스를 통해 조정될 수도 있는 방법의 제 1 예를 도시한다.

도 18 은 IRQ 신호들이 IRQ 라인 또는 버스를 통해 조정될 수도 있는 방법의 제 2 예를 도시한다.

도 19 는 일 예에서 실현가능한 가장 짧은 IRQ 신호 길이를 도시한다.

도 20 은 일 예시적인 시스템을 도시하는 블록도이며, 여기서 인터럽트 버스는 대역-내 인터럽트들에 유리하게 제거되었다.

도 21 은 I2C 1 바이트 기록 데이터 동작의 일 예시적인 타이밍도를 도시한다.

도 22 는 일 예시적인 CCIe 송신을 도시하며, 여기서 데이터 비트들은 SDA 라인 및 SCL 라인을 통한 송신을 위해 12 개의 심볼들로 트랜스코딩되었다.

도 23 은, 충돌들을 피하기 위해, 마스터 디바이스가 제어 데이터 버스를 구동하는 동안에 슬레이브 디바이스가 IRQ 를 어써트하기 위해 제어 데이터 버스를 구동하도록 허용되어서는 안되는 것을 도시한다.

도 24 는 도 23 의 충돌들에 대한 가능성을 피하기 위한 해결책을 도시한다.

도 25 는 슬레이브 디바이스가 SDA 라인으로 대역-내 IRQ 를 전송하는 경우, 잘못된 클록이 검출되는 것을 야기할 수도 있음을 도시한다.

도 26 은 도 25 에 도시된 추가적인 수신기 클록 펄스 및 동기화 손실을 피하기 위한 해결책을 도시한다.

도 27 은 I2C 모드 및 CCIe 모드 양자 모두를 지원하는 동안에 대역-내 IRQ 기간을 구현하는 하나의 접근법을 도시한다.

도 28 은 비트 19 (즉, 비트 0 인 제 1 비트에서 시작하여 비트를 세는 경우 20 번째 비트) 를 도시한다.

도 29 는 비트 19 가 수들 2221_2201_20023 내지 2222_2222_22223 에 걸칠 수도 있고, 수들의 범위가 도 29 의 좌측에서 6 개의 세부부분들로 다시 나눠질 수도 있음을 도시한다.

도 30 은 하트비트를 정의하는데 이용될 수도 있는 비트 19 수 공간 내의 범위를 도시한다.

도 31 은 하트비트 클록이 공유 제어 데이터 버스의 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 방법의 일 예를 도시한다.

도 32 는 하트비트 클록이 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 다른 예를 도시한다.

도 33 은 전환 수의 심볼 수로의 변환의 일 예를 도시한다.

도 34 는 도 33 의 심볼 수의 전환 수로의 변환으로 더 확장된다.

도 35 는 SDA 라인이 마스킹되는 대역-내 IRQ 기간 중의 조건을 도시한다.

도 36 은 도 32 및 도 35 의 SDA 마스크의 부작용을 도시한다.

도 37 은 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BD6~0x81BF0 (즉, 27 개의 어드레스들) 을 점유하는 것을 도시한다.

도 38 은 CCIe 모드 송신들에 대해 도 37 에서 이용되는 삼진 수의 비트 19 가 맵핑될 수도 있는 일 예를 도시한다.

도 39 는 CCIe 모드에서 제어 데이터 버스를 통한 대역-내 IRQ 를 구현하는 대인적인 기법을 도시한다.

도 40 은 SDA 라인이 마스킹되는 도 39 의 대역-내 IRQ 기간 중의 조건을 도시한다.

도 41 은 도 39 및 도 40 의 SDA 마스크의 부작용을 도시한다.

도 42 는 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BBB~0x81BD5 (즉, 27 개의 어드레스들) 를 점유하는 것을 도시한다.

도 43 은 마스터 디바이스가 활성 모드이고 전력 절감 모드인 경우에 하트비트들이 송신될 수도 있는 방법을 도시한다.

도 44 는 결합 동기화 워드 및 하트비트를 도시한다.

도 45 는 CCIe 프로토콜의 비트 19 내에서의 동기화 및 하트비트 맵핑을 도시한다.

도 46 은 일 예시적인 CCIe 프로토콜 내에서의 인터럽트 그룹 질의 일반 호를 도시한다.

도 47 은 그룹 질의 호에 대한 응답을 도시한다. 이러한 예에서, 하나 이상의 응답 기간들 (즉, 질의 워드들) 은 SCL 라인에 하트비트를 전송하고 SDA 마스크를 이용함으로써 SDA 라인에 대해 정의될 수도 있다.

도 48 은 플렉시블한 IRQ 그룹 질의 일반 호의 길이를 확인하기 위해 (즉, 워드 카운트) IRQ 그룹 질의 일반 호의 끝을 나타내는데 이용될 수도 있는 일 예시적인 "종결 워드" 를 도시한다.

도 49 는 DDR 클록 판독 일반 호가 구현될 수도 있는 일 예를 도시한다.

도 50 은 전역 클록 판독 워드에 대한 일 예시적인 타이밍도를 도시한다.

도 51 은 디바이스 내의 공유 버스에서의 I2C-호환가능한 디바이스와 CCIe-호환가능한 디바이스의 공존을 도시하며, 여기서 모든 마스터/슬레이브 디바이스들은 공유 버스를 통한 대역-내 인터럽트들을 이용한다.

도 52 는 공유 버스를 통한 도 51 의 마스터/슬레이브 디바이스들의 공존을 도시한다.

도 53 은 공유 버스를 통해 CCIe-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 I2C-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통해 대역-내 인터럽트들을 이용할 수도 있다.

도 54 는 공유 버스를 통해 I2C-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 CCIe-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통해 대역-내 인터럽트들을 이용할 수 있다.

도 55 는 일 예시적인 다중-모드 마스터 디바이스를 도시한다.

도 56 은 일 예시적인 슬레이브 디바이스를 도시한다.

도 57 은 일 예시적인 인터럽트 요청 라우터 슬레이브 디바이스를 도시한다.

도 1 은 기저대역 프로세서 및 이미지 센서를 구비하고 이미지 데이터 버스 및 다중-모드 제어 데이터 버스를 구현하는 디바이스를 도시하는 블록도이다.

도 2 는 공유 I2C 버스 (예를 들어, 제어 데이터 버스) 를 통한 I2C 모드 (예를 들어, 레거시 CCI 또는 제 1 모드) 와 CCIe 모드 (예를 들어, 제 2 모드) 의 예시적인 공존을 도시하는 블록도이다.

도 3 은 하나 이상의 sI2C 슬레이브 디바이스들, 다중-모드 I2C 및 CCIe 마스터 디바이스, 하나 이상의 I2C 슬레이브 디바이스들, 및 하나 이상의 CCIe 슬레이브 디바이스들을 포함하는 공통 I2C 버스를 통한 I2C 모드 (즉, 레거시 CCI) 와 CCIe 모드의 공존을 도시하는 블록도이다.

도 4 는 클록이 데이터 심볼들 내에 임베딩됨으로써, 데이터 송신들을 위해 I2C 와이어들 (즉, SDA 라인 및 SCL 라인) 양자 모두의 이용을 가능하게 할 수도 있는 방법을 도시한다.

도 5 는 송신기에서 데이터 비트들을 트랜스코딩된 심볼들로 트랜스코딩하여 트랜스코딩된 심볼들 내에 클록 신호를 임베딩하는 일 예시적인 방법을 도시하는 블록도이다.

도 6 은 전환 수들과 순차 심볼들 사이의 일 예시적인 변환을 도시한다.

도 7 은 전환 수들과 순차 심볼들 사이의 일 예시적인 변환을 더 도시한다.

도 8 은 I2C 1 바이트 기록 데이터 동작의 타이밍도를 도시한다.

도 9 는, sI2C 프로토콜에 따른, sI2C 1 바이트 기록 데이터 동작의 타이밍 도를 도시하며, 여기서 최상위 비트 (most significant bit; MSB) 는 일 (1) 이다.

도 10 은 CCIe 프로토콜의 일 예를 도시한다.

도 11 은 공유 버스를 통해 sI2C-호환가능한 슬레이브 디바이스에 의해 전송되는 일 예시적인 대역-내 인터럽트 신호 (IRQ) 의 도면을 도시한다.

도 12 는 sI2C 슬레이브 디바이스가 혼합된 프로토콜 모드 환경 (예를 들어, 여기서 공유 버스는 구별되는 통신 프로토콜들에 따라 또는 구별되는 통신 프로토콜들 사이에서 동적으로 스위칭하도록 동작할 수 있다) 에서 인터럽트 신호 (IRQ) 를 발행하는 추가적인 방식을 도시한다.

도 13 은 송신기와 수신기 회로 및 프로세싱/로직 회로를 포함하는 일 예시적인 슬레이브 디바이스를 도시한다.

도 14 는 단일-모드 슬레이브 디바이스가 다수의 통신 모드들 사이에서 스위칭하는 공유 데이터 버스에서 공존하는 것을 가능하게 하는 방법을 도시한다.

도 15 는 공유 제어 데이터 버스 및 공유 인터럽트 버스/요청에 연결되는 마스터 디바이스 및 복수의 슬레이브 디바이스들을 구비하는 시스템을 도시하는 블록도이다.

도 16 은 도 15 에서의 복수의 슬레이브 디바이스들이 인터럽트들을 발행할 목적으로 논리적으로 그룹화될 수도 있는 방법을 도시하는 블록도이다.

도 17 은 IRQ 신호들이 IRQ 라인 또는 버스를 통해 조정될 수도 있는 방법의 제 1 예를 도시한다.

도 18 은 IRQ 신호들이 IRQ 라인 또는 버스를 통해 조정될 수도 있는 방법의 제 2 예를 도시한다.

도 19 는 일 예에서 실현가능한 가장 짧은 IRQ 신호 길이를 도시한다.

도 20 은 일 예시적인 시스템을 도시하는 블록도이며, 여기서 인터럽트 버스는 대역-내 인터럽트들에 유리하게 제거되었다.

도 21 은 I2C 1 바이트 기록 데이터 동작의 일 예시적인 타이밍도를 도시한다.

도 22 는 일 예시적인 CCIe 송신을 도시하며, 여기서 데이터 비트들은 SDA 라인 및 SCL 라인을 통한 송신을 위해 12 개의 심볼들로 트랜스코딩되었다.

도 23 은, 충돌들을 피하기 위해, 마스터 디바이스가 제어 데이터 버스를 구동하는 동안에 슬레이브 디바이스가 IRQ 를 어써트하기 위해 제어 데이터 버스를 구동하도록 허용되어서는 안되는 것을 도시한다.

도 24 는 도 23 의 충돌들에 대한 가능성을 피하기 위한 해결책을 도시한다.

도 25 는 슬레이브 디바이스가 SDA 라인으로 대역-내 IRQ 를 전송하는 경우, 잘못된 클록이 검출되는 것을 야기할 수도 있음을 도시한다.

도 26 은 도 25 에 도시된 추가적인 수신기 클록 펄스 및 동기화 손실을 피하기 위한 해결책을 도시한다.

도 27 은 I2C 모드 및 CCIe 모드 양자 모두를 지원하는 동안에 대역-내 IRQ 기간을 구현하는 하나의 접근법을 도시한다.

도 28 은 비트 19 (즉, 비트 0 인 제 1 비트에서 시작하여 비트를 세는 경우 20 번째 비트) 를 도시한다.

도 29 는 비트 19 가 수들 2221_2201_20023 내지 2222_2222_22223 에 걸칠 수도 있고, 수들의 범위가 도 29 의 좌측에서 6 개의 세부부분들로 다시 나눠질 수도 있음을 도시한다.

도 30 은 하트비트를 정의하는데 이용될 수도 있는 비트 19 수 공간 내의 범위를 도시한다.

도 31 은 하트비트 클록이 공유 제어 데이터 버스의 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 방법의 일 예를 도시한다.

도 32 는 하트비트 클록이 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 다른 예를 도시한다.

도 33 은 전환 수의 심볼 수로의 변환의 일 예를 도시한다.

도 34 는 도 33 의 심볼 수의 전환 수로의 변환으로 더 확장된다.

도 35 는 SDA 라인이 마스킹되는 대역-내 IRQ 기간 중의 조건을 도시한다.

도 36 은 도 32 및 도 35 의 SDA 마스크의 부작용을 도시한다.

도 37 은 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BD6~0x81BF0 (즉, 27 개의 어드레스들) 을 점유하는 것을 도시한다.

도 38 은 CCIe 모드 송신들에 대해 도 37 에서 이용되는 삼진 수의 비트 19 가 맵핑될 수도 있는 일 예를 도시한다.

도 39 는 CCIe 모드에서 제어 데이터 버스를 통한 대역-내 IRQ 를 구현하는 대인적인 기법을 도시한다.

도 40 은 SDA 라인이 마스킹되는 도 39 의 대역-내 IRQ 기간 중의 조건을 도시한다.

도 41 은 도 39 및 도 40 의 SDA 마스크의 부작용을 도시한다.

도 42 는 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BBB~0x81BD5 (즉, 27 개의 어드레스들) 를 점유하는 것을 도시한다.

도 43 은 마스터 디바이스가 활성 모드이고 전력 절감 모드인 경우에 하트비트들이 송신될 수도 있는 방법을 도시한다.

도 44 는 결합 동기화 워드 및 하트비트를 도시한다.

도 45 는 CCIe 프로토콜의 비트 19 내에서의 동기화 및 하트비트 맵핑을 도시한다.

도 46 은 일 예시적인 CCIe 프로토콜 내에서의 인터럽트 그룹 질의 일반 호를 도시한다.

도 47 은 그룹 질의 호에 대한 응답을 도시한다. 이러한 예에서, 하나 이상의 응답 기간들 (즉, 질의 워드들) 은 SCL 라인에 하트비트를 전송하고 SDA 마스크를 이용함으로써 SDA 라인에 대해 정의될 수도 있다.

도 48 은 플렉시블한 IRQ 그룹 질의 일반 호의 길이를 확인하기 위해 (즉, 워드 카운트) IRQ 그룹 질의 일반 호의 끝을 나타내는데 이용될 수도 있는 일 예시적인 "종결 워드" 를 도시한다.

도 49 는 DDR 클록 판독 일반 호가 구현될 수도 있는 일 예를 도시한다.

도 50 은 전역 클록 판독 워드에 대한 일 예시적인 타이밍도를 도시한다.

도 51 은 디바이스 내의 공유 버스에서의 I2C-호환가능한 디바이스와 CCIe-호환가능한 디바이스의 공존을 도시하며, 여기서 모든 마스터/슬레이브 디바이스들은 공유 버스를 통한 대역-내 인터럽트들을 이용한다.

도 52 는 공유 버스를 통한 도 51 의 마스터/슬레이브 디바이스들의 공존을 도시한다.

도 53 은 공유 버스를 통해 CCIe-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 I2C-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통해 대역-내 인터럽트들을 이용할 수도 있다.

도 54 는 공유 버스를 통해 I2C-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 CCIe-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통해 대역-내 인터럽트들을 이용할 수 있다.

도 55 는 일 예시적인 다중-모드 마스터 디바이스를 도시한다.

도 56 은 일 예시적인 슬레이브 디바이스를 도시한다.

도 57 은 일 예시적인 인터럽트 요청 라우터 슬레이브 디바이스를 도시한다.

다음의 설명에서, 실시형태들의 완전한 이해를 제공하기 위해 특정 세부사항들이 주어진다. 그러나, 실시형태들은 이러한 특정 세부사항들이 없이 실시될 수도 있음이 당업자에 의해 이해될 것이다. 예를 들어, 실시형태들을 불필요한 세부사항으로 불명확하게 하지 않기 위해 회로들은 블록도들로 도시될 수도 있다. 다른 경우들에서, 실시형태들을 불명확하게 하지 않기 위해 공지의 회로들, 구조들, 및 기술들은 도시되지 않을 수도 있다.

개관

제 1 피쳐는 다수의 동작의 모드들에 따라 공통/공유 버스 (예를 들어, 제어 데이터 버스) 로 디바이스들을 동시에 동작시키는 방식을 제공한다. 복수의 슬레이브 디바이스들은 제어 데이터 버스에 대한 액세스를 제어하는 적어도 하나의 마스터 디바이스와 함께 제어 데이터 버스에 연결될 수도 있다. 적어도 제 1 슬레이브 디바이스는 서브세트 I2C (subset I2C; sI2C) 프로토콜 동작의 모드에서 동작할 수도 있고, 적어도 제 2 슬레이브 디바이스는 카메라 제어 인터페이스 확장 (camera control interface extension; CCIe) 동작의 모드에서 동작할 수도 있다. sI2C 모드 (즉, 제 1 모드) 및 CCIe 모드 (즉, 제 2 모드) 의 이용은 예시적인 모드들 및 (예를 들어, 상이한 통신 표준들에 대한) 다른 동작 모드들임에 유의한다. sI2C 프로토콜 모드 (예를 들어, 제 1 모드) 에서 동작하는 제 1 슬레이브 디바이스 (예를 들어, sI2C-호환가능한 슬레이브 디바이스) 는 인터럽트 요청들 또는 (예를 들어, 대역-내 IRQ 들이라고 지칭되는) IRQ 들을 위해 제어 데이터 버스를 이용할 수도 있다. 일 예에서, 그러한 IRQ 들은 공유 버스를 이용하기를 원한다는 것을 마스터 디바이스에 나타내기 위해 제 1 슬레이브 디바이스에 의해 발행될 수도 있다. 그에 반해, 제 2 슬레이브 디바이스 (CCIe 슬레이브 디바이스) 는 CCIe 모드 (예를 들어, 제 2 모드) 에서 동작하고 IRQ 들을 위해 전용 IRQ 라인을 이용한다. 공유 버스를 통한 CCIe 통신들의 무결성을 유지하기 위해, sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스는 공유 제어 데이터 버스를 통해 CCIe 통신이 시작될 시에 그것의 IRQ 능력을 디스에이블한다 (예를 들어, 대역-내 IRQ 들을 발행하지 않는다). 즉, 공유 제어 데이터 버스가 이용되는 CCIe 통신들에 대해 이용되는 동안에, sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스는 공유 버스를 통해 인터럽트들을 전송하는 것이 금지된다.

sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스가 CCIe 통신들을 이해하지는 않을 지라도, CCIe 모드로의 진입은 마스터 디바이스에 의해 개시된다. sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스는 이러한 CCIe 진입 공지를 이해하고, 공유 제어 데이터 버스를 이용하는 것을 중지할 수도 있다. 또한, 공유 제어 데이터 버스를 통해 CCIe 진입 통지 (즉, sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스가 이해하는, I2C 프로토콜에서의 메시지) 를 전송한 후에, CCIe 모드에서 동작하는 마스터 디바이스는 CCIe 통신들을 위해 공유 버스를 이용하는 것을 종료 또는 중단을 공지하는 (예를 들어, CCIe 프로토콜 및 I2C 프로토콜에서) 종료/중단 메시지를 전송한다. sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스는 공유 버스가 CCIe 모드 통신들에 이용되는 동안에 공유 버스를 통해 IRQ 들을 전송하는 그 자체의 능력을 디스에이블한다.

sI2C 프로토콜 모드에서 동작하는 제 1 슬레이브 디바이스 (예를 들어, "sI2C 슬레이브 디바이스") 의 관점에서, 제 1 슬레이브 디바이스는 CCIe 모드로의 진입을 공지하는 이해가능한 I2C 프로토콜 메시지를 수신하고 즉시 그 자신이 공유 제어 데이터 버스를 통해 대역-내 IRQ 들을 전송하는 것을 디스에이블한다. 제 1 슬레이브 디바이스는 그 다음에 (sI2C 프로토콜 모드에서 동작하는) 제 1 슬레이브 디바이스가 이해할 수 없는 하나 이상의 CCIe 통신들을 수신하고/하거나 무시할 수도 있다. 나중에, 제 1 슬레이브 디바이스는 공유 버스를 통해 CCIe 모드의 종료 또는 끝을 공지하는 이해가능한 I2C 프로토콜 메시지를 수신하고, 제 1 슬레이브 디바이스는 그 자신이 대역-내 IRQ 들을 전송하는 것을 인에이블한다. sI2C 슬레이브 디바이스에 의한 대역-내 IRQ 들을 전송하는 것에 대한 이러한 자체적-디스에이블링 및 인에이블링은 CCIe 모드인 슬레이브 디바이스가 동일한 공유 제어 데이터 버스에서 CCIe 프로토콜로 통신하는 동안에 대역-내 IRQ 를 수행하는 sI2C 슬레이브 디바이스로부터의 공유 제어 데이터 버스를 통한 데이터 충돌을 방지한다.

제 2 피쳐는 sI2C 슬레이브 디바이스의 CCIe-인에이블드 버스 (즉, 공유 제어 데이터 버스) 로의 (핫 스왑핑이라고도 불리는) 핫 플러깅을 가능하게 하는 것을 제공한다. 좀더 일반적으로, 이러한 제 2 피쳐는 제 1 프로토콜 모드 (예를 들어, sI2C 호환가능한 통신 프로토콜) 에 따라 동작하는 슬레이브 디바이스가 상이한 제 2 프로토콜 모드 (예를 들어, CCIe 모드) 에 따라 동작하는 버스에 동적으로 플러깅되거나 추가되는 것을 가능하게 한다. sI2C 슬레이브 디바이스가 CCIe 디바이스들과 함께 CCIe 인에이블드 공유 제어 데이터 버스에 공존하는 것을 인에이블함으로써, 핫 플러그 기능이 CCIe 인에이블드 공유 버스에서 동작하는 디바이스들에 대해 구현된다.

제 3 피쳐는 sI2C 슬레이브 디바이스가 인터럽트 (IRQ) 를 발행하는 추가적인 방식을 추가하는 것을 제공한다. 대역-내 인터럽트들 (IRQ 들) 을 발행하기 위해 sI2C 슬레이브 디바이스가 공유 버스 (예를 들어, 제어 데이터 버스) 를 이용하는 것과 더불어, sI2C 슬레이브 디바이스를 IRQ 라우터 CCIe-호환가능한 슬레이브 디바이스에 연결하기 위해 별도의 라인 (예를 들어, sI2C 디바이스들에 대한 전용 IRQ 버스 또는 라인) 이 활용될 수도 있다. IRQ 라우터 CCIe-호환가능한 슬레이브 디바이스는 sI2C 프로토콜 인터럽트 (IRQ) 들을 수신하고 CCIe IRQ 버스 또는 라인으로 sI2C 프로토콜 IRQ 를 라우팅한다. 일 예에서, sI2C 슬레이브 디바이스는 CCIe 모드로의 진입을 위해 공유 버스를 모니터링할 수도 있다. 그러나, sI2C 슬레이브 디바이스가 IRQ 를 수행하는 능력을 디스에이블하는 대신에, 내부 로직이 IRQ 의 출력을 공유 버스로부터 sI2C 슬레이브 디바이스를 IRQ 라우터 CCIe-호환가능한 슬레이브로 연결하는 라인으로 스위칭한다. 나중에, 공유 버스가 CCIe 모드에 따라 동작하는 동안에 종료 신호를 감지하면, sI2C 슬레이브 디바이스는 대역-내 IRQ 들을 발행하기 위해 다시 공유 버스를 이용하기 시작할 수도 있다. 이에 따라, sI2C 슬레이브 디바이스들 및 CCIe 모드인 슬레이브 디바이스들 양자 모두가 데이터 충돌들 없이 CCIe 인에이블드 버스에 공존할 수 있다. IRQ 라우터 CCIe-호환가능한 슬레이브 디바이스는 전용 IRQ 라인 또는 CCIe 모드로 동작하는 버스로 sI2C 슬레이브 디바이스들로부터 수신된 모든 IRQ 들을 라우팅한다.

제 4 피쳐는 sI2C-호환가능한 디바이스들 및 CCIe-디바이스들이 두 가지 유형의 디바이스들이 대역-내 인터럽트 요청 (IRQ) 들을 이용하면서 동일한 공유 버스를 통해 공존하는 것을 제공한다.

공유 버스를 통해 상이한 통신 프로토콜들을 이용하는 예시적인

디바이스들의

공존

도 1 은 기저대역 프로세서 (104) 및 이미지 센서 (106) 를 구비하고 이미지 데이터 버스 (116) 및 다중-모드 제어 데이터 버스 (108) 를 구현하는 디바이스 (102) 를 도시하는 블록도이다. 도 1 이 카메라 디바이스 내의 다중-모드 제어 데이터 버스 (108) 를 도시하나, 이러한 제어 데이터 버스 (108) 는 다양한 상이한 디바이스들 및/또는 시스템들에 구현될 수도 있다는 것이 명확할 것이다. 이미지 데이터는 이미지 데이터 버스 (116) (예를 들어, 고속 차동 DPHY 링크) 를 통해 이미지 센서 (106) 로부터 기저대역 프로세서 (104) 로 전송될 수도 있다. 일 예에서, 제어 데이터 버스 (108) 는 2 개의 와이어들인, 클록 라인 (SCL) 및 직렬 데이터 라인 (SDA) 을 포함하는 I2C 버스일 수도 있다. 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (108)) 를 통한 모든 데이터 전송들을 동기화하는데 이용될 수도 있다. 데이터 라인 (SDA) 및 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (108)) 상의 모든 디바이스들 (112, 114, 118, 122, 및 124) 에 연결된다. 디바이스들 (112, 114, 및 118) 중 일부 또는 전부는 일 라인 인터럽트 (IRQ) 버스 (120) 와 또한 연결될 수도 있다. 슬레이브 디바이스들 (114, 118, 122, 및 124) 은 상이한 프로토콜 모드를 가질 수도 있다 (예를 들어, 상이한 프로토콜들을 이용하여 동작할 수도 있다). 예를 들어, 제 1 슬레이브 디바이스 (122) 는 (예를 들어, sI2C 프로토콜에 따라 통신하는) sI2C-호환가능한 슬레이브 디바이스일 수도 있으며, 제 2 슬레이브 디바이스 (124) 는 (예를 들어, CCIe 프로토콜에 따라 통신하는) CCIe-호환가능한 슬레이브 디바이스일 수도 있고, 제 3 슬레이브 디바이스 (118) 는 (예를 들어, I2C/sI2C 및 CCIe 프로토콜들에 따라 통신하는) 다중-모드 동작이 가능할 수도 있다. 일 예에서, 공유 제어 데이터 버스 (108) 를 통해 기저대역 프로세서 (104) 와 이미지 센서 (106) 뿐만 아니라 슬레이브 디바이스들 (118, 122, 124) 사이에 제어 데이터가 교환될 수도 있다. I2C 통신들/시그널링을 위한 표준 클록 (SCL) 속도는 최대 100KHz 이다. I2C 고속 모드에서의 표준 클록 (SCL) 속도는 최대 400KHz 이고, I2C 고속 모드 플러스 (Fm+) 에서는 최대 1 MHz 이다. I2C 버스를 통한 이러한 동작 모드들은 카메라 애플리케이션들에 이용되는 경우 카메라 제어 인터페이스 (camera control interface; CCI) 모드라고 지칭될 수도 있다.

일 양상에 따르면, 카메라 동작을 지원하기 위해 다중-모드 제어 데이터 버스 (108) 를 통한 향상된 동작의 모드 (즉, 1 MHz 보다 큼) 가 구현될 수도 있다. 이러한 I2C 버스를 통한 향상된 동작의 모드는 카메라 애플리케이션들에 이용되는 경우 카메라 제어 인터페이스 확장 (camera control interface extension; CCIe) 모드라고 지칭될 수도 있다. 이러한 예에서, 기저대역 프로세서 (104) 는 마스터 디바이스/노드 (112) 를 포함하고, 이미지 센서 (106) 는 슬레이브 디바이스/노드 (114) 를 포함하며, 마스터 디바이스 (112) 및 슬레이브 디바이스 (114) 모드 양자 모두는 제어 데이터 버스 (108) 에 연결된 다른 레거시 I2C 디바이스들의 적절한 동작에 영향을 주지 않으면서 제어 데이터 버스 (108) 를 통해 카메라 제어 인터페이스 확장 (CCIe) 모드에 따라 동작한다. 일 양상에 따르면, 제어 데이터 버스 (108) 를 통한 이러한 향상된 동작의 모드는 CCIe 디바이스들과 임의의 레거시 I2C 슬레이브 디바이스들 사이에 임의의 브릿지 디바이스 없이 구현될 수도 있다. 일 양상에 따르면, 레거시 I2C 디바이스들은 제 1 클록, 제 1 버스 속도, 및/또는 제 1 신호 프로토콜을 갖는 제 1 모드로 동작할 수도 있고, 한편 CCIe-가능 디바이스들은 제 2 클록, 제 2 버스 속도, 및/또는 제 2 프로토콜을 갖는 제 2 모드로 동작할 수도 있다. 제 1 클록, 제 1 버스 속도, 및/또는 제 1 신호 프로토콜은 제 2 클록, 제 2 버스, 및/또는 제 2 프로토콜과는 다른 것일 수도 있다. 예를 들어, 제 2 클록 및/또는 제 2 버스 속도는 각각 제 1 클록의 속도 및/또는 제 1 버스 속도보다 빠르거나 클 수도 있다.

일 양상에 따르면, 모든 슬레이브 디바이스들 (118 및 124) 이 CCIe-가능 디바이스들인 경우, 동작의 제 1 모드와 제 2 모드 사이에서 스위칭할 필요가 없다. 즉, 제어 데이터 버스 (108) 를 통한 모든 시그널링 및/또는 통신들은 제 2 모드에 따라 (예를 들어, 제 2 클록, 제 2 버스 속도, 및/또는 제 2 프로토콜로) 수행될 수도 있다. 예를 들어, 제 2 모드가 제 1 모드의 제 1 레이트보다 큰 비트 레이트를 제공할 수도 있기 때문에, 제 1 모드와 제 2 모드 사이에서 왔다갔다하며 스위칭할 필요가 없다. 사실, 제 1 모드와 호환가능한 레거시 디바이스들이 맞춰질 필요가 없기 때문에, 제 2 모드보다 높은/큰 비트 레이트를 제공하는 동작의 제 3 모드가 구현될 수도 있다.

다른 양상에 따르면, 적어도 제 1 슬레이브 디바이스 (122) 는 sI2C 호환가능하여 제 1 슬레이브 디바이스 (122) 가 핫 플러깅가능하도록 한다. sI2C 슬레이브 디바이스 (122) 는 제어 데이터 버스 (108) 상의 임의의 다른 디바이스가 제어 데이터 버스 (108) 를 통해 (I2C 프로토콜 포맷으로) CCIe 진입 메시지를 전송할 때마다 제어 데이터 버스 (108) 를 통해 대역-내 IRQ 들을 전송하는 그 자신의 능력을 디스에이블한다. IRQ 디스에이블드 슬레이브 디바이스 (122) 는 전적으로 디스에이블되거나 부분적으로 디스에이블될 수도 있다. 전적으로 디스에이블된 경우, sI2C 슬레이브 디바이스 (122) 는 제어 데이터 버스 (108) 를 통해 대역-내 IRQ 들을 전송하지 않는다. 일부 구현들에서, 부분적으로 디스에이블된 경우, 제어 데이터 버스 (108) 를 통해 대역-내 IRQ 를 전송하기 보다는, sI2C 슬레이브 디바이스 (122) 는 sI2C 슬레이브 디바이스 (122) 로부터 전용 IRQ 버스 또는 라인으로 측파-대역 IRQ 들을 라우팅하는 역할을 할 수도 있는 IRQ 라우터 CCIe 슬레이브 디바이스에 대한 접속을 통해 측파-대역 IRQ 들을 전송할 수도 있다.

도 2 는 공유 I2C 버스 (206) (예를 들어, 제어 데이터 버스) 를 통한 I2C 모드 (202) (예를 들어, 레거시 CCI 또는 제 1 모드) 와 CCIe 모드 (204) (예를 들어, 제 2 모드) 의 예시적인 공존을 도시하는 블록도이다. 버스 (206) 에 대한 액세스를 관리하는 마스터 디바이스 (208) 는 I2C 모드 (예를 들어, 제 1 모드) 및 CCIe 모드 (예를 들어, 제 2 모드) 에 따라 동작할 수도 있다.

I2C 모드 (202) 에서, CCIe-가능 마스터 디바이스 (208) 는 완전한 CCI 또는 I2C Fm+ 능력을 지원할 수도 있는 반면, CCIe-가능 슬레이브 디바이스 (210) 는 완전한 I2C 능력을 지원하지 않을 수도 있다. I2C 모드에서, CCIe 마스터 (208) 는 최대 1Mbps 링크 레이트로 CCI 또는 I2C Fm+ 프로토콜을 이용하여 I2C 버스 (206) 로 슬레이브들 (210a, 210b, 210c, 210d) 과 통신한다.

CCI 표준 동작과 마찬가지로, CCIe 동작 (204) 은 단일의 마스터 디바이스 동작만을 지원한다 (예를 들어, 다수의 마스터들은 지원되지 않는다). CCIe 모드 (204) 에서 (예를 들어, 버스 (206) 는 CCIe 프로토콜 통신들에 이용된다), CCIe 마스터 디바이스 (208) 는, 예를 들어, 6.4 Mbps 또는 16.7 Mbps 로 제어 데이터 버스 (206) 상에서 CCIe-가능 슬레이브 디바이스들 (212a 및 212b) 과만 통신한다.

시작에서, 디폴트로, 버스 (206) 는 레거시 I2C 모드 (202) 로 동작할 수도 있다 (예를 들어, 버스 (206) 는 CCIe 프로토콜 통신들에 이용된다). CCIe 마스터 (208) 가 CCIe 슬레이브 (212a 및/또는 212b) 에 액세스하길 원하는 경우, I2C 일반 호에 의해 I2C 모드 (202) 로부터 CCIe 모드 (204) 로 스위칭한다.

CCIe 모드 (204) 에서, CCIe 마스터 (208) 가 I2C 슬레이브들 (210a, 210b, 210c, 및/또는 210d) 에 액세스하길 원하는 경우, CCIe "종료" 프로토콜과 I2C 일반 호의 조합에 의해 CCIe 모드 (204) 로부터 다시 I2C 모드 (202) 로 스위칭한다.

도 3 은 하나 이상의 sI2C 슬레이브 디바이스들 (308a 및 308b), 다중-모드 I2C 및 CCIe 마스터 디바이스 (304), 하나 이상의 I2C 슬레이브 디바이스들 (312a 및 312b), 및 하나 이상의 CCIe 슬레이브 디바이스들 (310a 및 310b) 을 포함하는 공통 I2C 버스 (306) 를 통한 I2C 모드 (302) (즉, 레거시 CCI) 와 CCIe 모드 (304) 의 공존을 도시하는 블록도이다. 도 2 에 대하여 설명된 다양한 특징들 및 동작들은 도 3 에 대해 적용가능할 수도 있고 간결성의 면에서 반복되지 않는다. 일 양상에서, sI2C 슬레이브 디바이스들 (308a 및 308b) 은 sI2C 프로토콜 모드 동작만을 할 수 있다 (여기서, 전부가 아니라면, 대부분의 I2C 통신들은 sI2C 슬레이브 디바이스들 (308a 및 308b) 에 의해 이해가능하고, 만약 있다면, 몇몇 CCIe 통신들은 sI2C 슬레이브 디바이스들 (308a 및 308b) 에 의해 이해가능하다). 즉, sI2C 슬레이브 디바이스들 (308a 및 308b) 은 sI2C 모드로 동작하는데 반해, CCIe 슬레이브 디바이스들 (310a 및 310b) 은 CCIe 모드로 동작한다. sI2C 슬레이브 디바이스들 (308a 및 308b) 은 임의의 디바이스가 제어 데이터 버스 (306) 를 통해 (I2C 프로토콜 포맷으로) CCIe 진입 메시지들을 전송할 때마다 제어 데이터 버스 (306) 를 통해 IRQ 들을 전송하는 그것들의 자체 능력을 디스에이블한다.

공유 버스를 통해 비트

레이트들을

증가시키기 위한 예시적인 통신 프로토콜 및 인코딩 방법

도 4 는 클록이 데이터 심볼들 내에 임베딩됨으로써, 데이터 송신들을 위해 I2C 와이어들 (즉, SDA 라인 및 SCL 라인) 양자 모두의 이용을 가능하게 할 수도 있는 방법을 도시한다. 일 예에서, 이러한 클록의 임베딩은 전환 클록 트랜스코딩에 의해 달성될 수도 있다. 예를 들어, 물리적 링크 (와이어들) 를 통해 송신될 데이터 (404) 는 송신된 심볼들 (406) 의 매 심볼 사이클마다 상태를 변화시키도록 트랜스코딩된다. 결과적으로, 원래의 클록 (402) 은 매 심볼 사이클마다 심볼 상태들의 변화로 임베?된다. 수신기는 (송신된 심볼들 (406) 에서의) 각각의 심볼에서의 상태 전환으로부터 클록 정보 (408) 를 복구하고, 그 다음에 송신된 심볼들 (406) 의 트랜스코딩을 역으로 하여 원래의 데이터 (410) 를 획득한다. 이는 I2C 버스 (도 1 에서의 제어 데이터 버스 (108), SDA 라인 및 SCL 라인) 와이어들 양자 모두가 데이터 정보를 전송하는데 이용되는 것을 가능하게 한다. 또한, 클록과 데이터 신호들 사이에 설정 및 대기 시간을 가질 필요가 없기 때문에 심볼 레이트는 두 배로 될 수도 있다.

도 5 는 송신기에서 데이터 비트들을 트랜스코딩된 심볼들로 트랜스코딩하여 트랜스코딩된 심볼들 내에 클록 신호를 임베딩하는 일 예시적인 방법을 도시하는 블록도이다. 송신기 (502) 에서, 데이터 비트들 (504) 의 시퀀스는 삼진 (밑 3) 수 (즉, "전환 수") 로 변환되고, 삼진 수들은 그 다음에 클록 라인 (SCL) (512) 및 데이터 라인 (SDA) (514) 을 통해 송신되는 (순차적) 심볼들로 변환된다.

일 예에서, 이진 데이터의 원래의 20 개의 비트들은 비트-투-전환 수 변환기 블록 (508) 으로 입력되어 12 개의 숫자의 삼진 수로 변환된다. 12 개의 숫자의 삼진 수의 각각의 숫자는 "전환 수" 를 표현한다. 2 개의 연속하는 전환 수들은 동일한 수들을 가질 수도 있다 (즉, 연속하는 삼진 수의 숫자들은 동일할 수도 있다). 각각의 전환 수는 2 개의 연속하는 순차 심볼들이 동일한 값들을 갖지 않도록 전환-투-심볼 블록 (510) 에서 순차 심볼로 변환된다. 전환이 모든 순차 심볼에서 보장되기 때문에, 그러한 순차 심볼 전환은 클록 신호를 임베딩하는 역할을 할 수도 있다.

각각의 순차 심볼 (516) 은 그 다음에 2 개의 와이어의 물리적 링크를 통해 전송된다 (예를 들어, I2C 버스는 SCL 라인 (512) 및 SDA 라인 (514) 을 포함한다).

도 6 은 전환 수들 (602) 과 순차 심볼들 (604) 사이의 일 예시적인 변환을 도시한다. 전환 수라고도 지칭되는, 밑이 3 인 수인, 삼진 수의 개개의 숫자는 세 개의 (3) 가능한 숫자들 또는 상태들 (0, 1, 또는 2) 중 하나를 가질 수도 있다. 삼진 수의 2 개의 연속하는 숫자들에서 동일한 숫자가 나올 수도 있으나, 2 개의 연속하는 순차 심볼들은 동일한 값을 갖지 않는다. 전환 수와 순차 심볼 사이의 변환은 연속하는 전환 수들이 동일할지라도 순차 심볼이 (순차 심볼로부터 순차 심볼로) 항상 변화하는 것을 보장한다.

도 7 은 전환 수들과 순차 심볼들 사이의 일 예시적인 변환을 더 도시한다. 송신기 측 (TX: T 에서 S 로) (702) 에서, 전환 수 (T) 는 순차 심볼 (S) 로 변환될 수도 있다. 예를 들어, 현재의 순차 심볼 (Cs) 은 이전의 순차 심볼 (Ps) 및 현재의 전환 수 (T) 의 함수인 임시 전환 수 (Ttmp) 에 기초하여 기초하여 획득될 수도 있다. 임시 전환 수 (Ttmp) 는 현재의 전환 수 (T) 를 제로와 비교함으로써 획득될 수도 있고, T = 제로인 경우, 임시 전환 수 (Ttmp) 는 3 과 동일하게 된다, 그렇지 않으면 (T 가 제로와 동일하지 않은 경우) Ttmp 은 T 와 동일하게 된다 (즉, Ttmp= T = 0 ? 3 : T). 현재의 순차 심볼은 현재의 순차 심볼 (Cs) 더하기 이전의 순차 심볼 (Ps) 더하기 임시 전환 수 (Ttmp) 의 합 (즉, Cs= Ps+ Ttmp) 으로서 획득될 수도 있다.

수신기 측 (RX: S 에서 T) (704) 에서, 변환 동작은 역으로 되어 현재의 순차 심볼 (Cs) 및 이전의 순차 심볼 (Ps) 로부터 전환 수를 획득한다. 임시 전환 수 (Ttmp) 는 현재의 순차 심볼 (Cs) 더하기 4 빼기 이전의 심볼 (Ps) 의 합 (즉, Ttmp= Cs+ 4 - Ps) 으로서 획득될 수도 있다. 현재의 전환 수 (T) 는 임시적 변환 수 (Ttmp) 와 동일하나, 임시적 변환 수 (Ttmp) 는 삼 (3) 과 비교되고, Ttmp= 3 인 경우, 임시적 변환 수 (Ttmp) 는 제로 (0) 와 동일하게 되며, 그렇지 않으면 (Ttmp 가 3 과 동일하지 않으면) T 는 Ttmp 과 동일하게 된다 (즉, T = Ttmp= 3 ? 0 : T).

테이블 (706) 은 전환 수들과 순차 심볼들 사이의 변환을 도시한다.

다시 도 6 을 참조하면, 전환 수들과 순차 심볼들 사이의 변환의 일 예가 도시된다. 예를 들어, 제 1 사이클 (606) 에서, 현재의 전환 수 (Ta) 는 2 이고, 따라서 Ttmp 도 2 이며, 이전의 순차 심볼 (Ps) 은 1 이며, 새로운 현재의 순차 심볼 (Cs) 은 이제 3 이다.

제 2 사이클 (608) 에서, 전환 수 (Tb) 는 1 이다. 전환 수 (Tb) 가 제로와 동일하지 않기 때문에, 임시 전환 수 (Ttmp) 는 전환 수 (Tb) 값 1 과 동일하지 않다. 현재의 순차 심볼 (Cs) 은 이전의 순차 심볼 (Ps) 값 3 을 임시 전환 수 (Ttmp) 1 에 추가함으로써 획득된다. 추가 연산의 결과가 3 보다 큰 4 와 동일하기 때문에, 롤 오버 수 0 이 현재의 순차 심볼 (Cs) 이 된다.

제 3 사이클 (610) 에서, 현재의 전환 수 (T) 는 1 이다. 전환 수 (T) 가 1 이기 때문에, 임시 전환 수 (Ttmp) 도 1 이다. 현재의 순차 심볼 (Cs) 은 이전의 순차 심볼 (Ps) 값 0 을 임시 전환 수 (Ttmp) 1 에 추가함으로써 획득된다. 추가 연산의 결과가 3 보다 크지 않은 1 과 동일하기 때문에, 현재의 심볼 (Cs) 은 1 과 동일하다.

제 4 사이클 (612) 에서, 현재의 전환 수 (T) 는 0 이다. 전환 수 (T) 가 0 이기 때문에, 임시 전환 수 (Ttmp) 는 3 이다.

현재의 순차 심볼 (Cs) 은 이전의 순차 심볼 (Ps) 값 1 을 임시 전환 수 (Ttmp) 3 에 추가함으로써 획득된다. 추가 연산의 결과가 3 보다 큰 4 와 동일하기 때문에, 롤 오버 수 0 이 현재의 순차 심볼 (Cs) 이 된다.

2 개의 연속하는 삼진 숫자들 (Tb 및 Tc) 이 동일한 수들을 가질지라도, 이러한 변환은 2 개의 연속하는 순차 심볼들이 상이한 상태 값들을 갖는 것을 보장한다는 것에 유의한다. 이로 인해, 순차 심볼들 (604) 에서의 보장된 전환은 클록 신호를 임베딩하는 역할을 함으로써, 데이터 송신들을 위해 I2C 버스에서 클록 라인 (SCL) 을 자유롭게 한다.

다시 도 5 를 참조하면, 수신기 (520) 에서, 프로세스는 역으로 되어 트랜스코딩된 심볼들을 다시 비트들로 변환하고, 그 프로세서에서, 심볼 전환으로부터 클록 신호가 추출된다. 수신기 (520) 는 2 개의 와이어의 물리적 링크 (예를 들어, SCL 라인 (524) 및 SDA 라인 (526) 을 포함하는 I2C 버스) 를 통해 순차 심볼들 (522) 의 시퀀스를 수신한다. 수신된 순차 심볼들 (522) 은 클록-데이터 복구 (clock-data recovery; CDR) 블록 (528) 에 입력되어 클록 타이밍을 복구하고 트랜스코딩된 심볼들 (S) 을 샘플링한다. 심볼-투-전환 수 변환기 블록 (530) 은 그 다음에 트랜스코딩된 (순차) 심볼들을 전환 수, 즉, 하나의 삼진 숫자의 수로 변환한다. 그 다음에, 전환 수-투-비트들 변환기 (532) 는 12 개의 전환 수들을 변환하여 12 개의 숫자의 삼진 수로부터 20 비트의 원래의 데이터를 복원한다.

본원에서 예시된 이러한 기법은 I2C 표준 버스가 제공하는 것을 능가하여 제어 버스 (108) (도 1) 링크 레이트를 증가시키는데 이용될 수도 있고 여기서는 CCIe 모드라고 지칭된다. 일 예에서, 제어 데이터 버스 (108) 에 연결된 마스터 노드/디바이스 및/또는 슬레이브 노드/디바이스는 표준 I2C 버스를 이용하여 가능한 것보다 높은 비트 레이트들을 동일한 제어 데이터 버스를 통해 달성하기 위해 (도 4 및 도 5 에 도시된 바와 같이) 심볼 송신들 내에 클록 신호를 임베딩하는 송신기들 및/또는 수신기들을 구현할 수도 있다.

공유 버스에서

I2C

,

sI2C

, 및

CCIe

디바이스들을

지원하는 예시적인 방법

하나의 피쳐는 동시에 I2C 디바이스들 및 CCIe 디바이스들 양자 모두를 지원하는 공유 버스를 구현하는 것을 제공하는 것이다. 도 1 내지 도 7 에서 언급된 바와 같이, 심볼 송신들 내 (I2C 버스에 대한 SCL 라인) 에 클록 신호를 임베딩함으로써 데이터 송신들을 위해 클록 라인 (SCL 라인) 의 이용을 가능하게 하는 것이 가능하다. 이는, 예를 들어, 통상적인 I2C 모드 버스들보다 높은 비트 레이트들을 갖는 CCIe 동작의 모드를 가능하게 할 수도 있다.

그러나, 한 가지 과제는 동시에 동일한 공유 버스로 레거시 I2C-호환가능한 디바이스들 및 CCIe-호환가능한 디바이스들 양자 모두의 동작을 가능하게 하는 것이다. I2C 프로토콜 및 CCIe 프로토콜의 요구사항들에 관한 일부 세부사항들이 이러한 모드들에 따라 동작하는 디바이스들을 지원하기 위한 방식을 마련하는데 유용할 수도 있다.

I2C 표준은 모든 I2C 호환가능한 슬레이브 디바이스들이 (예를 들어, SCL 라인이 공유 버스에서 하이 (high) 인 동안에 SDA 라인에서 하이-투-로우 전환에 의해 나타내어지는) START 조건의 수신 시에 그것들의 버스 로직을 리셋해야할 것을 요구한다.

도 8 은 I2C 1 바이트 기록 데이터 동작의 타이밍도를 도시한다. I2C 마스터 디바이스는 어떤 슬레이브 디바이스를 I2C 버스로 마스터 디바이스가 액세스하기를 원하는지를 나타내기 위해 SDA 라인 (802) 으로 7-비트 슬레이브 ID 를, 그리고 기록 동작을 나타내기 위해 1 비트를 전송한다. ID 가 7-비트 슬레이브 ID 와 매칭하는 슬레이브 디바이스만이 의도한 액션들을 야기할 수 있다. I2C 슬레이브 디바이스가 그 자체의 ID 를 검출하기 위해, 마스터 디바이스는 SDA 라인으로 적어도 8-비트 (또는 SCL 라인 (804) 으로 8 클록 펄스) 를 전송해야 한다. 따라서, 이는 CCIe 모드로 공유 버스를 동작시키는 경우에 레거시 I2C 슬레이브 디바이스들이 공유 버스를 통한 임의의 CCIe 동작들에 반응하는 것을 방지하도록 활용될 수 있다. 특히, CCIe 프로토콜이 시작 (S) 표시자들 사이에 7-비트 미만을 전송하면, (적어도 7-비트들을 예상하는) 레거시 I2C 슬레이브 디바이스들은 이를 불완전한 슬레이브 식별자 (slave identifier; SID) 로 취급하고 그것의 로직을 리셋한다.

도 9 는, sI2C 프로토콜에 따른, sI2C 1 바이트 기록 데이터 동작의 타이밍도를 도시하며, 여기서 최상위 비트 (MSB) 는 일 (1) 이다. 이러한 예에서, SDA 라인 (902) 을 통한 I2C 송신은 슬레이브 식별자 (SID) (904) 의 최상위 비트에 일 (1) 을 포함할 수도 있다. MSB 가 일 (1) 인 것은 sI2C 슬레이브 디바이스들의 핫 플러깅 및 스와핑을 가능하게 하는데, 단지 MSB 를 검사함으로써 마스터 디바이스가 새롭게 추가된 슬레이브 디바이스가 슬레이브 디바이스인 것을 쉽게 알 수 있기 때문이다.

도 10 은 CCIe 프로토콜의 일 예를 도시한다. 블록들은 CCle 특정 타이밍 및 시그널링 뿐만 아니라 레거시 I2C 타이밍 및 시그널링을 나타낸다. 1002 에 도시된 바와 같이, CCle 모드로 진입하고 CCle 모드로부터 빠져나오기 위한 프로토콜들이 있다. CCle 모드로의 진입이 실행되면, 공유 버스 모드는 CCle 모드에서의 종료가 실행될 때까지 CCle 모드에 머문다. 이러한 예에서, CCle 모드로의 진입은 I2C 모드 중에 일반 호의 일부로서 CCle 모드 진입 시퀀스 (1004) 에 의해 달성된다. I2C-호환가능한 디바이스들에 CCle 모드로의 진입을 공지하기 위해, CCle 모드로 동작하는 마스터 디바이스는 CCle 모드 (1032) 로의 진입을 공지하는 I2C 일반 호 (1030) 를 공유 버스를 통해 전송할 수도 있다. 유사하게, CCle 모드로부터의 종료 (1006) 를 공지하기 위해, 마스터 디바이스는 일반 호의 일부로서 CCle 모드 종료 시퀀스 (1034) 를 전송할 수도 있다. 일반 호 내의 이러한 진입/종료 시퀀스들 (1030 및 1034) 은 각각 I2C 모드로부터 CCle 모드로 그리고 CCle 모드로부터 I2C 모드로 스위칭하기 위해 CCle-인에이블드 디바이스들에 의해 이용된다. 이러한 일반 호들 (1030 및 1034) 은 또한 공유 버스가 CCle 모드로 스위칭되는 때를 I2C-전용 슬레이브 디바이스들이 알게 되고 인터럽트들을 발행하는 것 또는 그렇지 않으면 공유 버스를 통해 송신하는 것을 보류하는 것을 가능하게 한다.

기록 데이터 프로토콜 (1008) 은 슬레이브 식별자 (SID) (1018) 에 의해 식별된 슬레이브 노드/디바이스에 임의의 수의 주소 워드들 (1014) 및 데이터 워드들 (1016) 을 전송한다. 유사하게, 판독 데이터 프로토콜 (1010) 은 슬레이브 식별자 (SID) 에 의해 식별된 슬레이브 노드/디바이스로부터의 복수의 데이터 워드들 (1022) 을 판독할 수 있고, 한편 주소 워드들 (1020) 의 수는 여전히 임의적이다.

마지막 한 가지 특수 프로토콜은 클록 데이터 복구 (clock data recovery; CDR) 교정 (1012) 이며, 이는 (마스터 디바이스 그 자체를 포함하는) 나타내어진 CCle 디바이스가 링크 레이트를 최소화하도록 그것의 클록-데이터 복구 로직을 교정하기 위한 시퀀스를 시작하게 하기 위해 CCle 마스터 디바이스에 의해 이용될 수도 있다. 이러한 목적으로, CCle 마스터 디바이스는 또한 그 자체의 슬레이브 ID 를 갖는다.

임의의 CCle 워드들은 19-비트 정보를 반송하는 12-심볼들로 전송될 수도 있다. CDR 교정 프로토콜 (1012) 을 제외하고, 19-비트들 중 16 비트들은 데이터 정보일 수도 있고, 한편 19-비트들 중 3 비트들은 제어 정보와 같은 다른 정보에 이용된다.

도 11 은 공유 버스를 통해 sI2C-호환가능한 슬레이브 디바이스에 의해 전송되는 일 예시적인 대역-내 인터럽트 신호 (IRQ) (1102) 의 도면을 도시한다. 슬레이브 디바이스는 마스터 디바이스가 검출한 공유 버스의 SDA 라인 (1104) 을 풀 다운하거나 (pull down) 그라운딩하고 (ground) (1106) 그 다음에 요청하는 슬레이브 디바이스로 SDA 라인 (1104) 을 릴리스한다 (release). 슬레이브 디바이스는 그러면 그것의 IRQ 신호 (1102) 를 송신할 수 있다. IRQ 신호의 종료 시에, 마스터 디바이스는 일 시간의 기간 동안 SDA 라인 (1104) 을 로우 (low) 로 홀딩함으로써 인터럽트 신호의 수신을 확인응답할 (acknowledge) 수도 있다.

다시 도 10 을 참조하면, I2C-호환가능한 슬레이브 디바이스처럼, sI2C 슬레이브 디바이스는 CCIe 모드로의 진입을 공지하는 이해가능한 I2C 프로토콜 메시지 (1030) 를 수신하고 그 자신이 대역-내 IRQ 들 (즉, 공유 버스를 통한 인터럽트 신호들) 을 전송하는 것을 즉시 디스에이블할 수도 있다. sI2C 슬레이브 디바이스는 그리고 나서 sI2C 슬레이브 디바이스가 이해하지 못하고 무시하는 CCIe 통신 (1032) 을 수신할 수도 있다. 최후로, sI2C 슬레이브 디바이스는 CCIe 모드로부터의 종료를 공지하는 이해할 수 있는 I2C 프로토콜 메시지 (1034) 를 수신할 수도 있고, sI2C 슬레이브 디바이스는 그 자신이 다시 대역-내 IRQ 들을 전송하는 것을 인에이블한다.

도 12 는 sI2C 슬레이브 디바이스가 혼합된 프로토콜 모드 환경 (예를 들어, 여기서 공유 버스는 구별되는 통신 프로토콜들에 따라 또는 구별되는 통신 프로토콜들 사이에서 동적으로 스위칭하도록 동작할 수 있다) 에서 인터럽트 신호 (IRQ) 를 발행하는 추가적인 방식을 도시한다. 이전에 언급된 바와 같이, 공유 버스 (1204) 는 CCIe 모드로 마스터 디바이스 (1208) 에 의해 관리되고, sI2C-호환가능한 슬레이브 디바이스들 (1210a 및 1210b) 은 공유 버스 (1204) 를 통해 대역-내 인터럽트 신호들을 전송하거나 발행하는 것을 중지할 수도 있다. 그러나, 이러한 대안적인 접근법에서, 이러한 sI2C-호환가능한 슬레이브 디바이스들 (1210a 및 1210b) 은 하나 이상의 별도의 라인들 (1212 및 1214) 을 통해 IRQ 라우터 CCle 슬레이브 디바이스 (1216) 에 연결될 수도 있다. 공유 버스 (1204) 가 CCIe 모드로 동작하는 경우, sI2C-호환가능한 슬레이브 디바이스들 (1210) 은 대신에 IRQ 라우터 CCIe 슬레이브 디바이스 (1216) 에 그것들의 인터럽트 신호들을 전송하도록 구성될 수도 있다. IRQ 라우터 CCIe 슬레이브 디바이스 (1216) 는 sI2C 프로토콜 인터럽트 신호들을 수신하여 인터럽트가 마스터 디바이스 (1208) 에 의해 프로세싱될 수도 있도록 CCle IRQ 버스 또는 라인 (1206) 으로 인터럽트를 라우팅한다. 마스터 디바이스 (1208) 는 그 다음에 공유 버스 (1204) 를 I2C 모드로 스위칭할지 여부를 결정하고 요청하는 I2C-호환가능한 슬레이브 디바이스의 인터럽트 요청을 승인할 수도 있다.

결과적으로, 공유 버스 (1204) 가 CCIe 모드로 동작할 수도 있는 동안에, sI2C-호환가능한 슬레이브 디바이스들 (1210) 이 인터럽트 신호를 발행하는 (예를 들어, 공유 버스 (1204) 의 서비스 또는 이용을 요청하는) 그것들의 능력을 디스에이블하는 대신에, 각각의 sI2C-호환가능한 슬레이브 디바이스 (1210) 내의 내부 로직이 공유 버스 (1204) 로부터 sI2C 슬레이브 디바이스들 (1210) 을 IRQ 라우터 CCIe 슬레이브 디바이스 (1216) 로 연결하는 별도의 라인 (1212 또는 1214) 으로 인터럽트 신호의 출력을 스위칭할 수도 있다. 또한, 공유 버스 (1204) 를 통해 CCIe 모드로부터 종료 코드를 검출할 시에, sI2C-호환가능한 슬레이브 디바이스들 (1210) 은 인터럽트 신호들을 발행하기 위해 공유 버스 (1204) 를 이용하는 것으로 다시 스위칭한다. 이에 따라, sI2C-호환가능한 슬레이브 디바이스들 (1210) 및 CCle-호환가능한 슬레이브 디바이스들 (1218) 은 데이터 충돌들 없이 공유 버스 (1204) 가 CCIe 모드로 동작하는 동안에 공존할 수 있다.

다중-

모드

공유 제어 데이터 버스를 통한 예시적인 단일-

모드

슬레이브

디바이스

동작

도 13 은 송신기와 수신기 회로 (1306) 및 프로세싱/로직 회로 (1304) 를 포함하는 일 예시적인 슬레이브 디바이스 (1302) 를 도시한다. 송신기 및 수신기 회로 (1306) 는 프로세싱 회로 (1304) 에 연결되어 프로세싱/로직 회로 (1304) 및 하나 이상의 버스들로 그리고 그로부터 데이터를 송신할 수도 있다. 송신기 및 수신기 회로 (1306) 는, 예를 들어, 제 1 라인 및 제 2 라인을 포함할 수도 있는 다중-모드 공유 버스 (1320) 에 연결될 수도 있다. 동작의 제 1 모드 (예를 들어, I2C 모드) 에서, 송신기 및 수신기 회로 (1306) 는 데이터 송신들을 위해 제 1 라인을 그리고 제 1 클록 신호를 위해 제 2 라인을 이용하도록 구성될 수도 있다. 동작의 제 2 모드 (예를 들어, CCIe 모드) 에서, 송신기 및 수신기 회로 (1306) 는 데이터 송신들의 심볼 송신들 내에 제 2 클록 신호를 임베딩하면서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자 모두를 이용하도록 구성될 수도 있다. 다중-모드 공유 버스는 I2C-호환가능한 버스 및/또는 CCle-호환가능한 버스일 수도 있다. 동작의 제 3 모드에서, 송신기 및 수신기 회로 (1306) 는 제 2 모드와 유사하게 동작하나 제 1 모드-전용 레거시 디바이스들 (예를 들어, I2C-호환가능한 레거시 디바이스들) 에 대한 동시 지원은 없다.

슬레이브 디바이스 (1302) 는 다중-모드 공유 버스 (1320) 에 연결된 다른 디바이스들의 세트와 공존할 수도 있으나, 동작의 제 1 모드 및 제 2 모드 양자 모두 중에 적어도 제 1 라인 및/또는 제 2 라인을 끊임없이 모니터링하면서 제 1 모드에서만 동작한다. 동작의 제 1 모드에서, 슬레이브 디바이스 (1302) 는 공유 버스 (1320) 의 제 1 라인을 통해 다른 디바이스로 데이터를 송신할 수도 있다. 동작의 제 2 모드에서, 공유 버스 (1320) 의 제 1 라인 및 제 2 라인은 양자 모두는 제 2 모드를 지원하는 다른 디바이스들에 대해 제 2 모드에 따라 데이터를 송신할 수도 있다.

다양한 예들에서, 공유 버스 (1320) 에 연결된 디바이스들은 다수의 상이한 동작의 모드들 (예를 들어, 구별되는 통신 프로토콜들) 을 지원할 수도 있다. 예를 들어, 제 1 슬레이브 디바이스는 sI2C-호환가능한 슬레이브 디바이스일 수도 있으며, 제 2 슬레이브 디바이스는 CCIe-호환가능한 슬레이브 디바이스일 수도 있고, 제 3 슬레이브 디바이스는 다수의 모드들 (예를 들어, I2C-호환가능한 모드 및 CCIe-호환가능한 모드들) 이 가능할 수도 있다.

동작의 제 1 모드는 공유 버스 (1320) 를 통한 데이터 송신들을 위해 제 1 프로토콜을 구현할 수도 있고, 제 2 모드는 공유 버스 (1320) 를 통한 데이터 송신들을 위해 제 2 프로토콜을 구현한다.

일 예에서, 슬레이브 디바이스 (1302) 는 sI2C-호환가능한 슬레이브 디바이스일 수도 있다. 프로세싱 회로 (1304) 는, 공유 버스 (1320) 가 제 1 모드에 따라 동작하는 경우에, 공유 버스 (1320) 를 통한 통신들을 모니터링하는 역할을 하는 공유 버스 모니터링 회로/모듈 (1310) 을 포함할 수도 있다. 공유 버스 (1320) 가 제 2 모드에 따라 동작하는 동안에, 공유 버스 모니터링 회로/모듈 (1310) 은 버스가 제 1 모드로 다시 스위칭한다는 것을 나타내는 종료 호 (exit call) /커맨드를 모니터링하는 역할을 한다. 인터럽트 요청 생성기 회로/모듈 (1312) 은 인터럽트 신호를 생성하는 역할을 할 수도 있다. 인터럽트 요청 억제 회로/모듈 (1314) 은 슬레이브 디바이스 (1302) 가 인터럽트 요청을 생성하고/하거나 발행하는 것을 보류해야 하는 경우를 확인하는 역할을 할 수도 있다. 예를 들어, 공유 버스 (1320) 가 제 2 모드에 따라 동작한다고 공유 버스 모니터링 회로/모듈 (1310) 이 검출하면, 인터럽트 요청 억제 회로/모듈 (1314) 은 공유 버스 (1322) 를 통해 인터럽트들이 발행되는 것을 방지할 수도 있다.

송신기 및 수신기 회로 (1306) 는 (송신된 데이터로부터 클록 신호를 복구하기 위한) 클록 복구 회로 (1308) 를 포함할 수도 있다. 선택적/대안적 접근법에서, IRQ 스위칭 회로 (1316) 는 공유 버스 (1320) 가 제 2 모드로 동작하는 경우에 슬레이브 디바이스 (1302) 가 별도의 라인을 통해 인터럽트 라우터 디바이스 (1322) 에 인터럽트 요청을 발행하는 것을 가능하게 할 수도 있다.

도 14 는 단일-모드 슬레이브 디바이스가 다수의 통신 모드들 사이에서 스위칭하는 공유 데이터 버스에서 공존하는 것을 가능하게 하는 방법을 도시한다. 슬레이브 디바이스는 공유 데이터 버스 (1402) 를 통해 대역-내 인터럽트 요청들을 포함하는 제 1 프로토콜 모드로 동작할 수도 있다. 슬레이브 디바이스는 그 다음에 공유 데이터 버스가 공유 데이터 버스 (1404) 를 통한 대역-내 인터럽트 요청들을 가능하게 하지 않는 제 2 프로토콜 모드에 따라 동작하도록 스위칭한다는 것을 나타내는 진입 호에 대해 공유 데이터 버스를 모니터링할 수도 있다. 진입 호를 검출할 시에, 슬레이브 디바이스는 공유 데이터 버스 (1406) 를 통해 임의의 대역-내 인터럽트 요청들을 발행하는 것을 디스에이블한다. 선택적으로, 슬레이브 디바이스는 별도의 라인 (1408) 을 통해 인터럽트 요청 라우터로 인터럽트 요청들을 전송하도록 스위칭할 수도 있다. 슬레이브 디바이스는 제 2 프로토콜 모드 (1410) 로부터의 종료 호에 대해 공유 데이터 버스를 모니터링할 수도 있다. 종료 호를 수신할 시에, 슬레이브 디바이스는 공유 데이터 버스 (1412) 를 통한 대역-내 인터럽트 요청들을 인에이블한다.

대역-내

IRQ

를 갖는 공유 제어 데이터 버스에서의

I2C

슬레이브

디바이스들과

카메라 제어 인터페이스 확장

디바이스들의

공존

이전의 논의는 전용 인터럽트 버스를 이용하여 EC-호환가능한 슬레이브 디바이스들과 CCIe-호환가능한 디바이스들 사이에서 IRQ 들을 라우팅하는 것에 대해 제공되었다. 다음의 논의는 양자 모두 공유 제어 데이터 버스를 통한 대역-내 인터럽트들을 이용하는 EC-호환가능한 디바이스들 및 CCIe-호환가능한 디바이스들을 제공한다.

제 1 피쳐는 공유 버스에 연결된 모든 디바이스들에 대한 전용 인터럽트 라인들 및 핀들을 제거하는 것을 제공한다. 대신에, 모든 디바이스들이 공유 제어 데이터 버스를 이용하여 인터럽트 요청들을 발행함으로써, 공유 제어 데이터 버스에 연결된 슬레이브 디바이스들이 공유 제어 데이터 버스를 통해 데이터를 송신하는 것을 가능하게 한다.

제 2 피쳐는, 버스의 제 2 라인이 하트비트 송신을 위해 마스터 디바이스에 의해 이용되는 동안에, 버스에 연결된 하나 이상의 슬레이브 디바이스들이 버스의 제 1 라인으로 인터럽트 요청을 어써트할 수 있는, 공유 제어 데이터 버스를 통해 송신된 심볼들 내의 인터럽트 기간을 정의하는 것을 제공하며, 여기서 그러한 하트비트 송신은 하나 이상의 슬레이브 디바이스들을 동기화하는 역할을 한다.

제 3 피쳐는, 공유 버스를 통해 수신된 트랜스코딩된 데이터 비트들을 디코딩할 목적으로, 인터럽트 기간 중에 수신기 디바이스에서, 공유 버스의 제 1 라인을 내부적으로 마스킹하는 것을 제공한다. 예를 들어, 마스터 디바이스 및 슬레이브 디바이스들은 로컬로 (내부적으로) 생성된 마스크 신호를 이용함으로써 클록 데이터 복구 회로 (CDR) 에 대해 제 1 라인 입력을 마스킹할 수도 있다.

제 4 피쳐는 슬레이브 디바이스가 인터럽트 요청을 어써트했는지 여부를 확인하기 위해 인터럽트 기간 중에 마스터 디바이스가 공유 제어 데이터 버스의 제 1 라인을 모니터링하는 것을 제공한다.

제 5 피쳐는, 공유 제어 데이터 버스의 제 1 라인을 통해 인터럽트 요청을 검출할 시에, 어써트하는/요청하는 슬레이브 디바이스를 식별하기 위해 마스터 디바이스가 공유 제어 데이터 버스를 통해 슬레이브 디바이스들을 스캔하는 것을 제공한다.

전용

IRQ

라인을 이용한 인터럽트 메커니즘

도 15 는 공유 제어 데이터 버스 (1504) 및 공유 인터럽트 버스/요청 (1506) 에 연결되는 마스터 디바이스 (1508) 및 복수의 슬레이브 디바이스들 (1510a-1510e) 을 구비하는 시스템 (1502) 을 도시하는 블록도이다. 일 예에서, 제어 데이터 버스 (1504) 는 2 개의 와이어들인, 클록 라인 (SCL) 및 직렬 데이터 라인 (SDA) 을 포함하는 I2C 버스일 수도 있다. 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (1504)) 를 통한 모든 데이터 전송들을 동기화하는데 이용될 수도 있다. 데이터 라인 (SDA) 및 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (1504)) 상의 모든 디바이스들 (1508 및 1510a-1510e) 에 연결된다. CCIe 모드에서 이용되는 경우, 제어 데이터 버스 (1504) 의 SDA 라인 및 SCL 라인 양자 모두는 데이터 송신들을 위해 이용된다.

일 양상에 따르면, 공유 인터럽트 버스 (1606) 는 슬레이브 디바이스들 (1610a-1610e) 뿐만 아니라 마스터 디바이스 (1608) 에 연결된 단일 라인일 수도 있다. 이러한 공유 인터럽트 버스 (1506) 는 이용되지 않는 경우에 풀 업될 (pull up) (예를 들어, 풀 하이 (pull high)) 수도 있고, 슬레이브 디바이스가 인터럽트 요청 (IRQ) 신호를 어써트하는 경우에 풀 로우될 (pull low) (예를 들어, 그라운딩될) 수도 있다. 즉, 각각의 슬레이브 디바이스 (1510a-1510e) 는 마스터 디바이스 (1508) 에 IRQ 신호 (예를 들어, 요청) 를 전송함으로써 공유 제어 데이터 버스 (1504) 로 송신하기 위해 액세스를 독립적으로 요청할 수도 있다.

일부 예들에서, 단일 라인 IRQ 버스는 (예를 들어, 마스터 디바이스 또는 임의의 다른 디바이스에 의해 관리되지 않는) 비동기 버스일 수도 있다. 이는 슬레이브 디바이스들이 언제라도 IRQ 신호를 일방적으로 어써트할 수 있음을 의미한다.

다른 예에서, 단일 라인 IRQ 버스는 슬레이브 디바이스들로부터 마스터 디바이스로의 일방적 신호 송신들에 전용될 수도 있다. 즉, 단일 라인 IRQ 버스는 IRQ 신호들에만 이용되고 다른 유형의 신호들에는 이용되지 않을 수도 있다.

일 예에서, 제어 데이터 버스 (1504) 는 카메라 제어 인터페이스 (CCI) 또는 CCI 확장 호환가능한 버스일 수도 있다.

다른 예에서, 제어 데이터 버스 (1504) 는 슬레이브 디바이스들과 마스터 디바이스 사이의 양방향 버스일 수도 있다.

도 16 은 도 15 에서의 복수의 슬레이브 디바이스들 (1510a-1510e) 이 인터럽트들을 발행할 목적으로 논리적으로 그룹화될 수도 있는 방법을 도시하는 블록도이다. 이러한 예에서, 제 1 복수의 슬레이브 디바이스들 (1510a 및 1510b) 은 제 1 그룹 (1602) 에 있을 수도 있고, 제 2 복수의 슬레이브 디바이스들 (1510c 및 15l0d) 은 제 2 그룹 (1604) 에 있을 수도 있다. 그러한 그룹화들은, 예를 들어, 사전-구성되거나 마스터 디바이스 (1508) 에 의해 부트-업 시에 (예를 들어, 열거하여) 동적으로 정의될 수도 있다. 그러한 그룹화들은 용인할 수 없는 지연들 없이 어느 슬레이브 디바이스가 IRQ 버스 (1506) 를 통해 IRQ 신호를 트리거링했는지를 마스터 디바이스 (1508) 가 보다 빠르게 식별하는 것을 가능하게 한다.

슬레이브 디바이스의의 각각의 그룹 (1602 및 1604) 은 구별되는 IRQ 신호를 가질 수도 있다. 예를 들어, 제 1 그룹 (1602) 은 제 1 기간을 갖는 제 1 신호를 이용할 수도 있고, 제 2 그룹 (1604) 은 제 2 기간을 갖는 제 2 신호를 이용할 수도 있는 등이다. 예를 들어, "기간" 은 IRQ 버스 (1506) 가 어써트하는 슬레이브 디바이스에 의해 풀 로우되는 시간의 길이일 수도 있다. 다른 형태들의 신호 구별, 예를 들어, 슬레이브 디바이스들의 상이한 그룹들에 의해 이용되는 IRQ 신호들에 대한 상이한 전압 레벨들 등이 이용될 수도 있음에 유의한다. 일 구현에서, 각각의 "그룹" 은 단일의 슬레이브 디바이스를 포함할 수도 있다. 다른 구현들에서, 각각의 "그룹" 은 2 개, 3 개, 및/또는 4 개의 슬레이브 디바이스들 또는 그 이상을 포함할 수도 있다. 그룹당 슬레이브 디바이스들의 개수는 어써트하는 슬레이브 디바이스를 질의하고 식별하는데 얼마나 시간이 걸리는지의 함수일 수도 있다. 예를 들어, IRQ 버스 (1506) 에 연결된 많은 수의 슬레이브 디바이스들이 마스터 디바이스 (1508) 에 의해 질의되어야 한다면, 이는 용인할 수 없는 긴 지연을 야기할 수도 있다. 결과적으로, 슬레이브 디바이스들을 그룹화하는 것 및 각각의 그룹에 대해 구별되는 IRQ 신호들을 이용하는 것은 마스터 디바이스 (1508) 가 상대적을 짧은 시간 또는 용인가능한 시간의 기간 내에 어써트하는 슬레이브 디바이스를 식별하는 것을 가능하게 한다.

마스터 디바이스 (1508) 는 공유된 단일 라인 IRQ 버스 (1506) 에서 IRQ 신호의 발생을 검출하고 그룹 내의 각각의 슬레이브 디바이스에 질의하여 어느 슬레이브 디바이스가 IRQ 신호를 트리거링했는지 또는 어써트했는지를 식별한다. 예를 들어, IRQ 신호가 그룹-2 (1604) 슬레이브 디바이스를 식별한다면, 마스터 디바이스 (1508) 는 그룹-2 (1604) 내의 제 1 슬레이브 디바이스 (1510c) 에 (제어 데이터 버스 (1504) 를 통해) 레지스터 상태 요청을 전송할 수도 있다. 제 1 슬레이브 디바이스 (1510c) 상태 응답이 어써트하는 슬레이브 디바이스가 아니라고 나타내면, 마스터 디바이스 (108) 는 그룹-2 (1604) 내의 제 2 슬레이브 디바이스 (1510d) 에 (제어 데이터 버스 (1504) 를 통해) 다른 레지스터 상태 요청을 전송할 수도 있다. 이러한 프로세스는 IRQ 신호를 어써트한 슬레이브 디바이스가 식별될 때까지 그룹-2 (1604) 내의 모든 슬레이브 디바이스들에 대해 반복된다.

대안적인 접근법에서, 마스터 디바이스 (1508) 는 제 1 슬레이브 디바이스 (1510c) 가 IRQ 신호의 발행자로 식별될지라도 그룹-2 (1604) 내의 모든 슬레이브 디바이스들에 걸쳐 스캔할 수도 있다. 예를 들어, 동일한 그룹 내의 하나를 초과하는 슬레이브 디바이스가 동시에 IRQ 신호를 발행하는 것이 가능하다. 결과적으로, 마스터 디바이스는 한번에 그룹 내의 디바이스들로부터의 모든 IRQ 요청들을 알게 될 수도 있고 그것들을 하나씩 처리할 수도 있다. 일 구현에서, 단일 그룹에서의 다수의 디바이스들로부터의 동시에 발생하는 또는 중첩하는 IRQ 요청들은 긴급성, 중요성, 및/또는 우선순위의 순서로 마스터 디바이스 (1608) 에 의해 처리될 수도 있다.

도 17 은 IRQ 신호들이 IRQ 라인 또는 버스를 통해 조정될 수도 있는 방법의 제 1 예를 도시한다. 이러한 예에서, 상이한 슬레이브 디바이스 그룹들 (1702 및 1704) 이 정의될 수도 있으며, 각각의 슬레이브 디바이스 그룹 (1702 및 1704) 은 상이한 폭들의 인터럽트들 (1706 및 1708) 을 갖는다. IRQN 라인 (1506) 로우를 슬레이브 디바이스가 검출하는 경우, IRQN 라인 로우를 어써트하기 전에 IRQN 라인 (1506) 이 하이 플러스 최소 버스 자유 시간 (1702) 이 될 때까지 대기한다. 이러한 예에서, 제 1 인터럽트 (1706) 는 제 1 그룹 (1702) 내의 슬레이브 디바이스에 의해 어써트되며, 뒤이어 제 2 인터럽트 요청 (1708) 은 제 2 그룹 (1704) 내의 다른 슬레이브 디바이스에 의해 어써트된다.

도 18 은 IRQ 신호들이 IRQ 라인 또는 버스 (1506) 를 통해 조정될 수도 있는 방법의 제 2 예를 도시한다. 2 개의 슬레이브 디바이스들이 동시에 (또는 중첩하는 시간들에) (인터럽트 요청을 나타내기 위해) IRQN 라인 로우를 어써트하는 경우, 가장 긴 IRQN 로우 기간을 갖는 슬레이브 그룹이 이긴다. 이러한 예에서, 공유 인터럽트 버스 (1506) 를 통해, 제 1 인터럽트 신호 (1806) 는 제 1 그룹 (1802) 내의 제 1 슬레이브 디바이스에 의해 어써트/발행되었고, 한편, 동시에 또는 같은 시기에 (예를 들어, 중첩하는 시간에), 제 2 그룹 (1804) 에서의 제 2 슬레이브 디바이스는 제 2 인터럽트 신호 (1808) 를 어써트/발행하였다. 제 2 인터럽트 신호 (1808) 가 제 1 인터럽트 신호 (1806) 보다 길기 때문에, 제 1 그룹 (1802) 에서의 제 1 슬레이브 디바이스는 조정을 상실한다. 즉, 제 2 인터럽트 신호 (1808) 는 인터럽트 버스 (1506) 상에서 인식되나 제 1 인터럽트 신호 (1806) 는 인식되지 않는다. 요청하는 제 1 슬레이브 디바이스는 제 1 인터럽트 신호 (1806) 의 끝에서 인터럽트 버스 (1506) 를 릴리스하는 경우 조정의 손실을 검출할 수도 있으나, 인터럽트 버스 (1506) 는 하이로 돌아가야할 때 (예를 들어 풀링 하이될 때) 로우로 유지된다 (예를 들어, 그라운드로 풀링됨). 결과적으로, 제 1 슬레이브 디바이스는 추후에 (예를 들어, 제 2 인터럽트 신호 (1808) 종료 시에 인터럽트 버스 (1506) 가 일 시간의 양 (1812) 동안 다시 풀 업된 후에) 그것의 인터럽트 신호 (1810) 를 재발행한다.

도 19 는 일 예에서 실현가능한 가장 짧은 IRQ 신호 길이를 도시한다. 이러한 예는, 인터럽트 라인 (1902) 에 대해, IRQ 신호 (1904) 가 최근에 VDD 레벨의 70% 인 경우 (예를 들어, 하이 상태) "하이" 상태가 검출될 수 있고 IRQ 신호 (1904) 가 최근에 VDD 레벨의 30% 인 경우 "로우" 상태가 검출될 수 있다고 가정한다. 수신기 입력 레벨들에 의존하여 IRQ 신호 (1902) 가 VDD 레벨의 30% 내지 70% 사이의 어딘가에 있는 경우 하이 또는 로우 상태가 검출될 수도 있음에 유의한다. 여기서, TRF max 는 최대 하강-상승 시간이고 TLOW 은 의도한 로우 시간이다. tLOW 제한의 주요 목적은 마스터 디바이스가 슬레이브 디바이스들의 상이한 그룹들로부터의 IRQ 신호들 사이를 구별할 수 있는 것이다. 또한, 마스터 디바이스의 관점에서, IRQ 신호 (1904) 가 로우 상태로 검출되는 것이 보장되도록 2TRF max 는 TLOW 보다 적어야 한다 (즉, 2TRF max < TLOW).

제 IRQ 신호 길이 (기간) tLOW 는 TLOW-TFR 보다 크고 2TLOW+TFR 보다 작다 (즉, TLOW-TFR < tLOW < 2TLOW+TFR). 유사하게, 제 2 IRQ 신호 길이 (기간) tLOW' 는 2TLOW-TFR 보다 크고 2TLOW+TFR 보다 작다 (즉, 2TLOW-TRF < tLOW < 2TLOW+TFR).

제 1 슬레이브 디바이스가 IRQ 신호 로우를 어써트한 후에, 제 2 슬레이브 디바이스는 적어도 TFR max 의 길이어야 하는 TFR max 에서 tLOW min 까지의 일 시간의 기간 동안 IRQ 신호 로우를 검출하지 않을 수도 있음에 유의한다. 따라서, TLOW > 3 TFR max 이고 tLOW min > 2TFR max 이다.

(예를 들어, 전용 IRQ 버스/라인을 통한) 측파-대역 IRQ 는 인터럽트 지연의 면에서 (예를 들어, 공유 제어 데이터 버스를 통한) 대역-내 IRQ 를 통해 확실한 이점을 갖는다. 측파-대역 IRQ 들은 인터럽트 신호들의 검출 시에 매우 짧은 지연들을 요구하는 일부 구현들에서 바람직할 수도 있다.

공유 버스를 통한 대역-내 인터럽트 메커니즘

도 15 내지 도 19 에 도시된 측파-대역 IRQ 방법은 각각의 슬레이브 디바이스 및 마스터 디바이스에 대해 추가적인 핀의 이용을 요구한다. 슬레이브 디바이스들은 특히 이용가능한 사이즈/공간이 종종 제한되고, 측파-대역 인터럽트들의 이용 또는 전용 인터럽트 라인/버스의 요구조건을 없애는 것이 바람직할 것이다. 따라서, 측파-대역 IRQ 방법에 대한 대안은 공유 제어 데이터 버스를 통해 대역-내 IRQ 들을 전송하는 것이다.

도 20 은 일 예시적인 시스템 (2002) 을 도시하는 블록도이며, 여기서 인터럽트 버스는 대역-내 인터럽트들에 유리하게 제거되었다. 시스템 (2002) 은 공유 제어 데이터 버스 (2004) 에 연결된 마스터 디바이스 (2008) 및 복수의 슬레이브 디바이스들 (2010a-2010e) 을 포함할 수도 있다. 일 예에서, 제어 데이터 버스 (2004) 는 2 개의 와이어들인, 클록 라인 (SCL) 및 직렬 데이터 라인 (SDA) 을 포함하는 I2C 버스일 수도 있다. 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (2004)) 를 통한 모든 데이터 전송들을 동기화하는데 이용될 수도 있다. 데이터 라인 (SDA) 및 클록 라인 (SCL) 은 I2C 버스 (제어 데이터 버스 (2004)) 상의 모든 디바이스들 (2008 및 2010a-2010e) 에 연결된다. 도 15 및 도 16 에 대하여, 이러한 시스템 (2002) 은 별도의 인터럽트 라인 또는 버스를 갖지 않는다. 대신에, 인터럽트들은 공유 제어 데이터 버스 (2004) 를 통해 대역-내로 전송된다.

일 피쳐는 동시에 I2C 디바이스들 및 카메라 제어 인터페이스 확장 (CCIe) 디바이스들 양자 모두를 지원하는 공유 제어 데이터 버스를 구현하는 것을 제공한다 (예를 들어, CCIe 모드와 I2C 모드 사이에서 공유 버스를 동적으로 스위칭한다).

공유 버스를 통한 예시적인

CCIe

및

I2C

송신들

도 21 은 I2C 1 바이트 기록 데이터 동작의 일 예시적인 타이밍도를 도시한다. 이러한 예에서, 공유 제어 데이터 버스 (2004) (도 20) 는 직렬 데이터 라인 (SDA) (2102) 및 직렬 클록 라인 (SCL) (2104) 을 포함한다. 도 21 에 도시된 송신 기법은 "I2C 모드" 라고 지칭될 수도 있다. SCL 라인 (2104) 은 마스터 디바이스로부터 슬레이브 디바이스들로 클록을 전송하는데 이용되고, 한편 SDA 라인 (2102) 은 데이터 비트들을 송신한다. I2C 마스터 디바이스는 어떤 슬레이브 디바이스를 I2C 버스로 마스터 디바이스가 액세스하기를 원하는지를 나타내기 위해 SDA 라인 (2102) 으로 7-비트 슬레이브 ID (2208) 를, 그리고 기록 동작을 나타내기 위해 1 비트를 전송한다. ID 가 7-비트 슬레이브 ID (2108) 와 매칭하는 슬레이브 디바이스만이 의도한 액션들을 야기할 수 있다. I2C 슬레이브 디바이스가 그 자체의 ID 를 검출하기 위해, 마스터 디바이스는 SDA 라인으로 적어도 8-비트들 (또는 SCL 라인 (2104) 으로 8 클록 펄스들) 을 전송해야 한다.

I2C 표준은 모든 I2C 호환가능한 슬레이브 디바이스들이 (예를 들어, SCL 라인이 하이인 동안에 SDA 라인에서 하이-투-로우 전환에 의해 나타내어지는) START 조건 (2106) 의 수신 시에 그것들의 버스 로직을 리셋하는 것을 요구한다.

CCIe 프로토콜은 데이터 송신들을 위해 SDA 라인 (2102) 및 SCL 라인 (2104) 양자 모두를 이용하는 한편 데이터 송신들 내에 클록 신호를 임베딩한다. 예를 들어, 데이터 비트들은 복수의 심볼들 내에 트랜스코딩될 수도 있으며, 복수의 심볼들은 그 다음에 라인들을 통해 송신된다. 심볼 전환들 내에 클록 신호를 임베딩함으로써 (도 21 에서 I2C 버스에 대한 SCL 라인), SDA 라인 (2102) 및 SCL 라인 (2104) 양자 모두는 데이터 송신에 이용될 수도 있다.

도 22 는 일 예시적인 CCIe 송신을 도시하며, 여기서 데이터 비트들은 SDA 라인 (2102) 및 SCL 라인 (2104) 을 통한 송신을 위해 12 개의 심볼들로 트랜스코딩되었다. 도 22 에 도시된 송신 기법은 "CCIe 모드" 라고 지칭될 수도 있다.

CCIe 모드는 푸쉬-풀 구동기들에 의해 구동되는 소스 동기식이다. 공유 제어 데이터 버스를 통해 누가 데이터를 전송하든지 데이터에 임베딩된 클록 정보도 전송한다. 결과적으로, 제어 데이터 버스 상에서 하나의 디바이스만이 임의의 일 시점에 버스를 구동할 수 있게 된다.

동일한 버스를 통해 레거시 I2C 디바이스들 및 CCIe 디바이스들 양자 모두를 지원하기 위해, CCIe 모드 동작들은 동일한 START 조건 (2200, 2202, 2204) 을 이용하며, 이는 레거시 I2C 슬레이브 디바이스들이 임의의 CCIe 동작들에 반응하는 것 (예를 들어, CCIe 모드 중에 START 조건이 레거시 I2C 슬레이브 디바이스들로 하여금 리셋하게 하는 것) 을 방지한다. 이러한 예에서, START 조건 (2200, 2202, 및 2204) (즉, SCL 라인 (2104) 이 하이인 동안에 SDA 라인 (2102) 상에서 하이에서 로우로의 전환으로 나타내어짐) 은 완전한 슬레이브 ID (즉, 총 7 비트들) 가 송신되기 전에 검출되며, 따라서 이는 불완전한 슬레이브 ID (7 비트들보다 적음) 이다. 마스터 디바이스가 6 SCL 펄스들을 전송하여 START 조건 (2200, 2202, 또는 2204) 을 발행하면, 모든 레거시 I2C 슬레이브 디바이스들은 데이터를 I2C 슬레이브 ID 로 인식하기 전에 그것들의 버스 로직을 리셋한다. (예를 들어, 매 2 개의 심볼들마다 대응하는) 6-비트 시퀀스들이 2 개의 조건들 (2200, 2202, 및 2204) 사이에서 전송되기 때문에, 이러한 6-비트 시퀀스들은 임의의 슬레이브 디바이스들에 의해 유효한 슬레이브 ID 로 디코딩되지 않는다. 결과적으로, 레거시 I2C 슬레이브 디바이스들은 불완전한 슬레이브 ID 들에 대해서는 반응하지 않을 것이다.

이러한 시스템에서, 마스터 디바이스는 공유 버스에 대한 액세스를 제어한다. 그래서, 제어 데이터 버스를 통해 송신하기를 원하는 임의의 디바이스는, 예를 들어, 인터럽트 요청을 발행함으로써 마스터 디바이스로부터의 그러한 액세스를 요청해야 한다. 인터럽트들을 발행하기 위한 선행 기술의 메커니즘들은 전용 인터럽트 라인들 또는 전용 인터럽트 버스에 의존했다. 그러나, 그러한 전용 인터럽트 라인들 또는 버스는 그러한 인터럽트 라인 또는 버스를 수용하기 위해 디바이스들이 적어도 하나의 추가적인 핀을 포함해야 하는 것을 의미한다. 그러한 전용 인터럽트 핀 및 라인들/버스의 필요성을 제거하기 위해, CCIe 내의 대역-내 인터럽트들에 대한 메커니즘이 필요하다.

대역-내 인터럽트들의 이용은 또한 버스 경합 또는 충돌들을 피해야 한다. 예를 들어, 도 23 에 도시된 바와 같이, 충돌들을 피하기 위해, 마스터 디바이스가 제어 데이터 버스를 구동하는 동안에 슬레이브 디바이스가 (예를 들어, SDA 라인 (2102) 또는 SCL 라인 (2104) 으로) IRQ 를 어써트하기 위해 제어 데이터 버스를 구동하도록 허용되어서는 안된다.

도 24 는 도 23 의 충돌들에 대한 가능성을 피하기 위한 해결책을 도시한다. 이러한 접근법에서, CCIe 프로토콜은 대역-내 IRQ 가 발행될 수도 있는 경우를 정의한다. 본원에서 예시된 바와 같이, 마스터 디바이스는 대역-인터럽트를 발행하기 위해 슬레이브가 SDA 라인 (2104) 을 구동하는 것을 가능하게 하도록 하는 시간의 기간이 정의된 동안에 SCL (2102) 상에서 클록을 구동할 수도 있다. 특히, CCIe-호환가능한 슬레이브 디바이스들은 우선 SDA 라인 (2104) 이 이용 중인지 (예를 들어, 로우로 풀링되었는지) 여부를 검사하고, 그런 경우에만, SDA 라인 (2104) 을 로우로 풀링함으로써 인터럽트 요청을 발행한다.

도 25 에 도시된 다른 문제는, 슬레이브 디바이스가 SDA 라인 상으로 대역-내 IRQ 를 전송하는 경우, 잘못된 클록이 검출되는 것을 야기할 수도 있다는 것이다. 즉, CCIe 모드에서, 수신기 클록 (RXCLK) 을 생성하기 위해 심볼 전환들이 이용된다. 이는 모든 수신하는 디바이스들이 공유 버스의 상태 전환로부터 클록 타이밍을 복구하는 것을 의미한다. SDA 및 SCL 라인들의 상태 변화인 상태 전환은 SDA 라인과 SCL 라인 사이에서 타이밍 정렬되어야 한다. CCIe 클록 데이터 복구 (CDR) 회로가 SDA 라인과 SCL 라인 사이의 일부 왜곡들을 용인할 수는 있으나, CDR 의 용인치보다 큰 왜곡은 CDR 로 하여금 추가적인 수신기 클록 펄스 (2502) 를 생성하게 하여 CCIe 워드 경계에 대한 동기화 손실을 초래할 것이다.

도 26 은 도 25 에 도시된 추가적인 수신기 클록 펄스 및 동기화 손실을 피하기 위한 해결책을 도시한다. 대역-내 IRQ 에 이용되는 신호는 각각의 디바이스 (예를 들어, 마스터 디바이스 및 슬레이브 디바이스들) 에 의해 클록 데이터 복구 회로 입력에서 마스킹되어야 한다. 예를 들어, 각각의 CDR 회로는 대역-내 IRQ 송신들 중에 SDA 라인 (2104) 또는 SCL 라인 (어느 것이든 대역-내 IRQ 에 이용되는 라인) 을 마스킹한다 (2602). 예를 들어, 마스터 디바이스가 슬레이브 디바이스로 하여금 특정 대역-내 IRQ 프로토콜 (2604) 을 갖는 SDA 라인 (2104) 을 구동하게 하면, 제어 데이터 버스 상의 모든 디바이스들은 잘못된/추가적인 RXCLK 펄스들이 검출되는 것을 방지하기 위해 해당 시간 중에 그것들의 SDA 라인 입력을 마스킹해야 한다. 일 예에서, 각각의 디바이스는 대역-내 IRQ 기간 중에 CDR 회로 내의 값을 1 로 유지하기 위해 SDA 라인을 게이팅해야 한다.

도 27 은 I2C 모드 및 CCIe 모드 양자 모두를 지원하는 동안에 대역-내 IRQ 기간을 구현하는 하나의 접근법을 도시한다. 이러한 접근법에서, 종료 표시자 (2702 및 2704) 는 공유 버스가 CCIe 모드로부터 I2C 모드로 스위칭한다는 것을 나타내기 위해 CCIe 모드 뿐만 아니라 I2C 모드에서 전송된다. 그 후에, sI2C 슬레이브 디바이스는 I2C 모드에 있는 동안에 대역-내 IRQ (2706) 를 발행할 수도 있다. 대역-내 IRQ 가 발행된 후에, I2C 모드에 있는 동안에 마스터 디바이스가 진입 호 (2708) 를 발행하는 경우 공유 버스는 CCIe 모드로 다시 되돌아갈 수도 있다.

CCIe

모드

내에서

하트비트

클록의 예시적인

임베딩

/인코딩

일 예에 따르면, "하트비트" 는 2-라인 제어 데이터 버스를 통한 송신을 위해 데이터 비트들을 인코딩하는데 이용되는 삼진 수 공간 내에 인코딩되거나 임베딩될 수도 있다.

도 5 를 참조하면, 도시된 트랜스코딩 방법은 20 비트들을 삼진 수로 인코딩하는 단계를 포함하며, 삼진 수는 그 다음에 12 개의 심볼들로 변환된다. 이러한 인코딩의 이용은 20 비트 내에 추가의 또는 여분의 비트를 제공하며, 이는 CCIe 프로토콜 내에서 커맨드들을 전송하는데 이용될 수도 있다.

도 28 은 비트 19 (즉, 비트 0 인 제 1 비트에서 시작하여 비트를 세는 경우 20 번째 비트) 를 도시한다. 다시 말해서, 컴퓨터 과학에서 통상적인 바와 같이, 비트 측면에서 세는 것은 제로에서 시작하고, 비트 19 는 20 번째 비트이다. 여기서, 비트들 (0-18) 은 0000_0000_00003 내지 2221_2201_20013 의 삼진 수의 범위 내에서 표현된다. 2221_2201_20023 내지 2222_2222_22223 의 범위 내의 삼진 수들은 데이터 송신에 이용되지 않는다. 결과적으로, 삼진 수 범위 2221_2201_20023 내지 2222_2222_22223 이 비트 19 (즉, 20 번째 비트) 를 표현하는데 이용된다. 다시 말해서, 2221_2201_20023 삼진수는 1000_0000_0000_0000_0000 이진수 (0x80000 16진수) 이고, 2222_2222_22223 삼진수 (0x81BF0) 는 가능한 가장 큰 12 개의 숫자의 삼진 수이다. 이는 하트비트가 송신될 수도 있는 이러한 20 번째 비트 (비트 19) 의 수 공간 내에 있다.

도 29 는 비트 19 가 수들 2221_2201_20023 내지 2222_2222_22223 에 걸칠 수도 있고, 수들의 범위가 도 29 의 좌측에서 6 개의 세부부분들로 다시 나눠질 수도 있음을 도시한다. CCIe 는 다중-마스터 제어 데이터 버스 아키텍쳐이고, 제어 데이터 버스의 관리는 마스터 디바이스로부터 다른 마스터 디바이스로 전송된다. 결과적으로, (하위범위 2222_1121_02103 내지 2222_2112_11213 내의) "마스터 버스 요청" 커맨드 뿐만 아니라 (하위범위 2222_2220_00023 내지 2222_2221_12103 내의) "마스터 핸드오버" 가 이용가능하다.

도 30 은 하트비트를 정의하는데 이용될 수도 있는 비트 19 수 공간 내의 범위를 도시한다.

도 31 은 하트비트 클록이 공유 제어 데이터 버스의 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 방법의 일 예를 도시한다. 수신기 클록 (RXCLK) (3108) 은 제어 데이터 버스 (예를 들어, SDA 라인 (3110) 및 SCL 라인 (3112)) 를 통해 송신된 심볼들의 상태 전환로부터 추출될 수도 있다. 이러한 예는 송신 또는 인코딩 전에 및/또는 수신 및 디코딩 후에 하트비트 클록이 보일 수도 있는 방법을 예시할 수도 있다. 인지할 수 있는 바와 같이, 하트비트 클록의 제 1 부분 (3102) 은 SDA 라인 상으로 송신되고, 한편 하트비트 클록의 제 2 부분 (3104) 은 SCL 라인 상으로 송신된다. 이러한 방식으로, 하트비트 클록의 부분을 SCL 라인으로 이동시킴으로써 SDA 라인 상에 공간 (3106) 이 생성된다.

CCIe

디바이스들에

대한

제 1

예시적인 대역-내

IRQ

기법

도 32 는 하트비트 클록이 SDA 라인 및 SCL 라인을 통해 송신될 수도 있는 다른 예를 도시한다. 이러한 예에서, 하트비트 클록은 하트비트 클록의 제 1 부분 (3202) 이 SDA 라인 상으로 송신되고, 한편 하트비트 클록의 제 2 부분 (3204) 은 SCL 라인을 통해 송신됨으로써, SDA 라인 상에 대역-내 IRQ 를 위한 보다 큰 공간 (3206) 을 생성하는 것을 포함한다.

프로토콜에 따르면, 수신하는 슬레이브 디바이스는, 예를 들어, 시작 (S) 표시자 (3212) 후에 제 n RXCLK (3214) 를 검출할 수도 있다. 제 n RXCLK (3214) 는 내부 SDA 마스크 (3224) 를 트리거링하여 (예를 들어, 수신하는 슬레이브 디바이스 내에서) SDA 라인 (3226) 을 내부적으로 마스킹할 수도 있다.

n+1 RXCLK (3216) 에서, 슬레이브 디바이스는 SDA 라인을 로우로 풀링함으로써 IRQ 를 트리거링할 수도 있다. SDA 라인은 (슬레이브 디바이스에 의해) 로우로 풀링되는 경우 대역-내 IRQ 를 나타내는 역할을 하도록, 마스터 디바이스에 의해 약하게 하이로 풀링된다. 즉, SDA 라인을 하이로 약하게 풀링함으로써, 이는 슬레이브 디바이스가 인터럽트 신호를 어써트하기 위해 SDA 라인을 로우로 풀링하는 것을 가능하게 한다.

n+2 RXCLK (3218) 에서, 마스터 디바이스는 SDA 라인을 샘플링하여 대역-내 IRQ 가 어써트되었는지 여부를 확인할 수도 있다.

n+3 RXCLK (3220) 에서, 슬레이브 디바이스는 SDA 라인을 릴리스할 수도 있다 (예를 들어, 대역-내 IRQ 를 디-어써트한다).

n+3 RXCLK 와 n+4 RXCLK 사이에서, 마스터 디바이스는 SDA 구동기를 리-인에이블하고 SDA 라인을 하이로 구동하기 시작한다. 이것이 수신기 디바이스 (예를 들어, 슬레이브 디바이스) 가 n+4 RXCLK 에서 SDA 마스크를 안전하게 릴리스할 수 있는 이유이다.

n+4 RXCLK (3222) 에서, 슬레이브 디바이스는 SDA 마스크 (3224) 를 릴리스할 수도 있다.

이러한 방식으로, IRQ 는 SDA 라인에 대해 정의된 IRQ 기간 (3506) 중에 슬레이브 디바이스에 의해 송신될 수도 있다.

도 33 은 전환 수의 심볼 수로의 변환의 일 예를 도시한다.

심볼 (S) 은 CCIe 모드에서 제어 데이터 버스 (예를 들어, SDA 라인 및 SCL 라인) 를 통해 전송된다. 일 예에서, 각각의 심볼은 2 비트로 이루어질 수도 있으며, LSB 는 SCL 라인에 할당되고 MSB 는 SDA 라인에 할당된다.

일 예에서, 각각의 삼진 전환 수 (T) 는 다음과 같이 정의된다:

S 가 심볼 순서 서클에서 1 상태만큼 시계방향으로 이전의 상태로부터 현재의 상태로 전환하는 경우 T=l;

S 가 심볼 순서 서클에서 2 상태들만큼 시계방향으로 이전의 상태로부터 현재의 상태로 전환하는 경우 T=2;

S 가 심볼 순서 서클에서 3 상태들만큼 시계방향으로 이전의 상태로부터 현재의 상태로 전환하는 경우 T=0;

CCIe 모드에서 데이터 제어 버스를 통한 통상적인 데이터 송신들은 임의의 전환 수를 사용할 수도 있다.

도 34 는 도 33 의 심볼 수의 전환 수로의 변환에 대해 더 확장된다. 변환은 다음과 같이 정의될 수도 있다:

S 가 심볼 순서 서클에서 1 상태만큼 시계방향으로 이전의 상태로부터 현재의 상태로 전환하는 경우 T=l;

S 가 심볼 순서 서클에 걸쳐 이전의 상태로부터 현재의 상태로 전환하는 경우 T=2;

S 가 심볼 순서 서클에서 1 상태들만큼 시계반대방향으로 이전의 상태로부터 현재의 상태로 전환하는 경우 T=0;

T=0 또는 1 인 경우에 SCL 라인 토글은 항상 일어나지만, SCL 라인은 T=2 인 경우에는 토글되지 않는다.

도 35 는 SDA 라인 (3502) 이 마스킹되는 대역-내 IRQ 기간 중의 조건을 도시한다. 전환 수 T = 2 가 전송되는 경우 SCL 라인 (3504) 은 토글하지 않고, SDA 라인 (3502) 이 마스킹되는 경우 (3508) SDA 라인 (3502) 은 그것의 실제 상태와 상관없이 항상 하이로 보이기 때문에, 심볼 전환이 없다. 결과적으로, SDA 마스크 기간 (3510) 중에 T=2 가 전송되면 생성되는 클록 RXCLK (3506) 가 없다. 그 때문에, SDA 마스크=1 인 동안에 T=2 는 금지된다.

도 36 은 도 32 및 도 35 의 SDA 마스크의 부작용을 도시한다. T 가 2 와 같지 않을지라도, SDA 라인은 대역-내 IRQ 기간 중에 항상 로직 1 상태로 보이고, SDA 라인에 대해 로직 0 을 초래하는 임의의 전환 T 값들은 SDA 비트가 항상 1 인 것으로 가정하는 T[2:0]=010 으로 에일리어싱 (aliase) 된다.

도 37 은 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BD6~0x81BF0 (즉, 27 개의 어드레스들) 을 점유하는 것을 도시한다. T=2 가 금지되고 임의의 다른 T 조합들이 T=010 으로 에일리어싱된다는 사실은 대역-내 IRQ 를 지원하는 하트비트 워드가 비트 19 영역의 1 개의 어드레스를 점유할 뿐만 아니라, 실제로 27 개의 어드레스들을 점유한다는 것을 의미한다. 이러한 특정 하트비트 패턴의 이용은 81BF0 hex 인 삼진 수 2222_2222_2222 의 이용을 금지하고, 2 개 워드의 CCIe 동기화의 제 1 워드로서 매우 유용하다. 삼진 수 2222_2222_2222 없이, 절대적 동기화는 쉽지 않거나 불가능할 수도 있다.

도 38 은 CCIe 모드 송신들에 대해 도 37 에서 이용되는 삼진 수의 비트 19 가 맵핑될 수도 있는 일 예를 도시한다. 이러한 예에서, 하트비트는 삼진 수 2222_2222_20103 에 할당될 수도 있다. 이러한 예에서, 2222_2222_2xxx3 의 범위 내의 삼진 수가 검출되는 한, 이는 하트비트 및/또는 대역-내 IRQ (예를 들어, 0x81BD9 hex) 로 해석될 수도 있음에 유의한다.

CCIe

디바이스들에

대한

제 2

예시적인 대역-내

IRQ

기법

도 39 는 CCIe 모드에서 제어 데이터 버스를 통한 대역-내 IRQ 를 구현하는 대인적인 기법을 도시한다. 이러한 예는 대역-내 IRQ 를 수행하기 위해 도 32 에서 필요로 하는 수신기 클록 (RXCLK) 사이클들의 수를 감소시킨다.

대역-내 IRQ 기간 (3906) 을 제공하기 위한 이러한 프로토콜에 따르면, 수신하는 슬레이브 디바이스는, 예를 들어, 시작 (S) 표시자 (3912) 후에 제 n RXCLK (3914) 를 검출할 수도 있다. 제 n RXCLK (3914) 는 내부 SDA 마스크 (3924) 를 트리거링하여 (예를 들어, 수신하는 슬레이브 디바이스 내에서) SDA 라인을 내부적으로 마스킹할 수도 있다.

n+1 RXCLK (3916) 에서, 슬레이브 디바이스는 SDA 라인을 로우로 풀링함으로써 IRQ 를 트리거링할 수도 있다. SDA 라인은 (슬레이브 디바이스에 의해) 로우로 풀링되는 경우 대역-내 IRQ 를 나타내는 역할을 하도록, 마스터 디바이스에 의해 약하게 하이로 풀링된다.

다음 클록 사이클까지 기다리기 보다는, n+1 RXCLK (3916) 사이에 그러나 n+2 RXCLK (3918) 전에, 마스터 디바이스는 로우인지 및/또는 로우로 되어 가는 경우인지를 확인하기 위해 SDA 라인을 모니터링할 수도 있으며, 로우는 대역-내 IRQ 가 어써트되었음을 의미한다. 그러한 마스터 디바이스에 의한 SDA 라인의 모니터링은 슬레이브 디바이스들로부터의 임의의 IRQ 요청들을 비동기적으로 검출하기 위해 IRQ 기간 중에만 수행된다는 것에 유의한다.

n+2 RXCLK (3918) 에서, 슬레이브 디바이스는 SDA 라인을 릴리스할 수도 있다 (예를 들어, 대역-내 IRQ 를 디-어써트한다).

n+2 RXCLK 와 n+3 RXCLK 사이에서, 마스터 디바이스는 SDA 구동기를 리-인에이블하고 SDA 라인을 하이로 구동하기 시작한다. 결과적으로, 수신기 (어써트하는 슬레이브 디바이스) 는 n+3 RXCLK 에서 SDA 마스크를 안전하게 릴리스할 수 있다.

n+3 RXCLK (3920) 에서, 슬레이브 디바이스는 SDA 마스크 (3924) 를 릴리스할 수도 있다. 이러한 방식으로, 대역-내 IRQ 는 SDA 라인에 대해 정의된 IRQ 기간 (3906) 중에 슬레이브 디바이스에 의해 송신될 수도 있다.

도 40 은 SDA 라인이 마스킹되는 도 39 의 대역-내 IRQ 기간 중의 조건을 도시한다. 전환 수 T = 2 가 전송되는 경우 SCL 라인 (4004) 이 토글하지 않고, SDA 라인 (4002) 이 마스킹된 경우 (4008) SDA 라인 (4002) 는 그것의 실제 상태와 상관없이 항상 하이로 보이기 때문에, 심볼 전환이 없다. 결과적으로, SDA 마스크 기간 (4010) 중에 T=2 가 전송되면 생성되는 수신기 RXCLK (4006) 가 없다. 그 때문에, SDA 마스크=1 인 동안에 T=2 는 금지된다.

도 41 은 도 39 및 도 40 의 SDA 마스크의 부작용을 도시한다. T 가 2 와 같지 않을지라도, SDA 라인은 대역-내 IRQ 기간 중에 항상 로직 1 상태로 보이기 때문에, SDA 라인에 대해 로직 0 을 초래할 임의의 전환 T 값들은 SDA 비트가 항상 1 인 것으로 가정하는 T[2:0]=010 으로 에일리어싱된다.

도 42 는 대역-내 IRQ 들에 이용되는 하트비트가 삼진 수 공간 내에서 수 공간 0x81BBB~0x81BD5 (즉, 27 개의 어드레스들) 를 점유하는 것을 도시한다. 도 32 및 39 에서의 하트비트와 유사하게, 도 39 내지 도 41 의 대인적인 하트비트는 또한 비트 19 영역의 27 개의 주소들을 점유한다. 그러나, 이러한 대안적인 하트비트는 2222_2222_2xxx 삼진 수 공간의 이용을 금지하지 않아, 2222_2222_2222 워드가 동기화를 위해 여전히 이용가능하다. 이러한 하트비트 패턴은 또한 보다 짧은 대역-내 IRQ 기간을 수용하기 위해 마스터 디바이스가 비동기식 대역-내 IRQ 검출 회로를 이용할 것을 요구하며, 이는 큰 희생은 아닐 것이다.

이상적으로, 대역-내 인터럽트들을 구현하기 위한 프로토콜은 1 개 또는 2 개의 CCIe 워드들처럼 가능한 한 간소하여 가능한 한 최소 프로토콜 오버헤드로 가능한 한 자주 대역-내 IRQ 들이 발행될 수 있어야 한다. 예를 들어, 주기식 대역-내 IRQ 윈도우가 정의될 수도 있다. 다른 고려사항 중에서, 슬레이브 디바이스들에 의해 "고갈" 을 방지하기 위해 버스 시스템이 로우-전력 모드로 있을지라도 대역-내 IRQ 기간은 이용가능해야 한다. 이에 대한 한 가지 해결책은 공유 제어 데이터 버스를 통해 마스터 디바이스에 의해 주기적으로 송신되는 CCIe "하트비트" 워드 내에 대역-내 IRQ 를 정의하여 슬레이브 디바이스들의 동기화를 가능하게 하는 것일 수도 있다.

도 43 은 마스터 디바이스가 활성 모드이고 전력 절감 모드인 경우에 하트비트들이 송신될 수도 있는 방법을 도시한다. 마스터 디바이스가 활성 모드 (4302) 에 있는 경우에 정상 동작들 중에, 마스터 디바이스는 슬레이브 디바이스들이 대역-내 IRQ 들을 발행하는 것을 가능하게 하기 위해 CCIe 프레임들 (4306) 사이에 하트비트 워드 (4608) 를 주기적으로 전송한다. 하트비트 워드 간격은 슬레이브 디바이스들이 인터럽트 요청을 발행할 기회들을 갈망하지 않게 될 수도 있다.

마스터 디바이스가 전력 절감 모드에 있는 경우에, 하트비트 (4316) 가 또한 송신될 수도 있어, 공유 버스 (예를 들어, SDA 라인 (4310) 및 SCL 라인 (4312)) 상의 슬레이브 디바이스들이 전력 절감 모드 중에 대역-내 IRQ 를 발행할 기회를 허용한다.

마스터 디바이스는 마스터 디바이스에 의한 전력 절감들을 위해 충분히 느리지만 슬레이브 디바이스들이 IRQ 신호를 발행할 기회들에 굶주리지 않을 만큼 빠른 레이트로 이러한 "하트비트" CCIe 워드 (4316) 를 전송할 수도 있다. 이러한 "하트비트" CCIe 워드는 IRQ 들을 발행할 수도 있는 슬레이브 디바이스들에 표지사의 역할을 할 수도 있다. 용어 "하트비트" 는 활성 (살아있음) 을 죽이도록 최소의 기능성을 위해 전력 절감 모드 중에 슬레이브 디바이스들에 느린 구동 클록을 나타내기 위해 본원에서 이용된다.

도 44 는 결합 동기화 워드 및 하트비트를 도시한다. 하트비트 워드는 또한 동기화 워드 시퀀스의 두번째 워드의 역할을 한다. 2 워드 동기화 시퀀스는 "SY-" 로 표기되는 바와 같이 모두 2 워드 2222_2222_2222 로 시작하고, 하트비트 워드는 "-NC" 로 표기되는 바와 같이 2222_2222_1101 로 시작한다.

"SY-" 워드는 버스 상태 (심볼) 가 형태 1 (SDA=0, SCL=1) 에서 3 (SDA=1, SCL=1) 으로 되는 경우에 RX 디바이스들이 START 조건에 의한 하나의 "2" 및 마지막 심볼 후에 하나의 "2" 를 포함하여 14 개의 전환 상태 2 들을 생성하게 한다.

"-NC" 워드는 RX 디바이스들이 START 조건에 의한 하나의 "2" 를 포함하여 9 개의 전환 상태 2 들을 생성하게 한다.

"SY-" 워드 및 "-NC" 워드는 조합되거나 결합되어 (예를 들어, 따라서 "SYNC"), 총 23 개의 전환 상태 2 들에 뒤이어 "1101" 시퀀스를 초래하며, 이는 고유한 시퀀스이고 임의의 다른 CCIe 전환들에서 발생할 수 없다. CCIe 디바이스들은 시퀀스를 이용하여 CCIe 워드 경계를 동기화할 수 있다.

도 45 는 CCIe 프로토콜의 비트 19 내에서의 동기화 및 하트비트 맵핑을 도시한다. 42 개의 수들에 걸치는 수치 공간 0x81BC6~0x81BEF hex는 동기화를 위해서만 절대적으로 고유한 2 워드 패턴 "SY-NC" 23 "2" 들 및 "1101" 을 만들기 위해 금지된다. 마스터 디바이스는, 슬레이브 디바이스들이 동기화 손실 시에 재동기화하거나, 핫-플러깅된 슬레이브들이 버스에 동기화하는 것을 가능하게 하기 위해, "-NC" 워드인 하트비트 직전에 "SY-" 워드를 주기적으로 전송한다.

예시적인

IRQ

그룹 질의

일 피쳐에 따르면, 각각의 슬레이브 디바이스는 "그룹" 이 할당되거나 "그룹" 과 연관될 수도 있으며, 각각의 "그룹" 은 하나 이상의 슬레이브 디바이스들을 포함한다. 특정 "그룹" 과 연관된 IRQ 신호를 검출할 시에, 마스터 디바이스는 IRQ 신호를 어써트한 슬레이브 디바이스(들)를 식별하기 위해 (여기서, IRQ 신호는 제어 데이터 버스를 통해 대역-내 IRQ 로 또는 전용 IRQ 버스를 통해 측파-대역 IRQ 로 어써트된다.) "그룹" 내의 슬레이브 디바이스들의 각각에 (예를 들어, 제어 데이터 버스를 통해) 질의를 전송할 수도 있다. IRQ 를 어써트한 슬레이브 디바이스는 그것의 할당된 그룹 내에서만 그 질의에 응답할 수도 있으며, 그렇게 함으로써 어써트하는 슬레이브 디바이스를 마스터 디바이스가 식별한다. 슬레이브 디바이스들의 각각의 "그룹" 은 하나 이상의 슬레이브 디바이스들을 가질 수도 있음에 유의한다. 전력 절감이 마스터 디바이스에 의해 구현되는 경우, 슬레이브 디바이스가 하트비트 워드 내에 대역-내 인터럽트를 발행할 수도 있음에 유의한다. 또한, 다수의 슬레이브 디바이스들은 동일한 하트비트 워드 내에 인터럽트를 발행할 수도 있다.

도 46 은 일 예시적인 CCIe 프로토콜 내에서의 인터럽트 그룹 질의 일반 호를 도시한다. 마스터 디바이스는 공유 버스 상으로 모든 슬레이브 디바이스들에 일반 호 IRQ 그룹 질의 (4600) 를 브로드캐스트할 수도 있다. IRQ 그룹 질의 커맨드 0x0007 hex (4602) 다음에, 복수의 IRQ 그룹 질의 워드들 (4604) 이 전송된다. 일 예에서, 각각의 질의 워드는 3 개의 질의 응답 슬롯들 및 그룹 0 내지 그룹 32 에 대한 총 33 개의 슬롯들을 갖는다. 일 예에서, 질의 워드들 (4604) 은 한 개 (1) 내지 11 개 (11) 의 IRQ 그룹 질의 워드들 (IQ) 및 끝에 하나의 종결 워드 (Term) (4606) 를 포함할 수도 있다. 각각의 질의 워드 (4604) 에 대해, 모든 슬레이브 디바이스들은 공유 버스의 SDA 라인을 마스킹한다.

일반 호의 페이로드 (4604) 의 각각의 IRQ 그룹 질의 (IQ) 워드 (4608) 에서, 각각의 슬레이브 수신기는 T11 RXCLK 에서 SDA 를 마스킹하기 시작하고 더미 (T-1) RXCLK 에서 마스크를 릴리스해야 한다.

도 47 은 그룹 질의 호에 대한 응답을 도시한다. 이러한 예에서, 하나 이상의 응답 기간들 (즉, 질의 워드들) 은 SCL 라인 (4710) 으로 하트비트를 전송하고 SDA 마스크 (4712) 를 이용함으로써 SDA 라인 (4708) 에 대해 정의될 수도 있다. 이러한 예에서, 3 개의 별도의 슬롯들 (4702, 4704, 및 4706) 이 각각의 질의 워드 (4608) 에 대해 정의되었다 (도 46). 각각의 IQ 워드 (4608) 에서의 3 개의 타임 슬롯들 (4702, 4704, 및 4706) 의 각각은 3 개의 상이한 IRQ 그룹들에 할당될 수도 있다. 각각의 슬롯 (4702, 4704, 및 4706) 에 할당된 슬레이브 디바이스들은 IRQ 를 발행했거나 서비스되지 않은 IRQ 를 가지고 있음을 나타내기 위해 질의 응답으로서 할당된 슬롯 (4702, 4704, 및 4706) 중에 SDA 라인 (4708) 을 구동할 수 있다. 각각의 IRQ 그룹 질의 (IQ) 워드 (4608) 가 3 개의 질의 응답 슬롯들 (4702, 4704, 및 4706) 을 가지고, 최대 11 개의 IRQ 그룹 질의 (IQ) 워드들이 일반 호 페이로드 (4604) 에 있을 수 있으므로, 하나의 호에 최대 33 개의 그룹 슬롯들이 있을 수 있다.

하나의 디바이스는 한 그룹에만 있도록 최대 32 개의 (32) 디바이스들이 그룹들에 할당되며, 그렇게 함으로써 IRQ 발행자들의 즉각적인 식별을 제공한다. 이러한 접근법은 한번에 다수의 IRQ 그룹들을 식별하며, 그렇게 함으로써 필요한 IRQ 스캔들의 수를 감소시킨다 (예를 들어, 보다 적은 IRQ 네스팅 (nesting)). 대안으로, 다수의 디바이스들이 각각의 그룹에 할당될 수도 있으나, 그룹 내의 복수의 디바이스들 중 어느 디바이스가 IRQ 를 발행했는지를 식별하기 위해 마스터 디바이스에 의한 추가적인 질의가 필요할 수도 있다.

마스터 디바이스는 버스 시스템에서의 IRQ 그룹들의 수에 기초하여 일반 호에 포함시킬 IRQ 그룹 질의 (IQ) 워드들의 수를 선택할 수도 있다. 일부 예들에서, 마스터 디바이스는 보다 적은 (예를 들어, 최대 수인 11 개 (11) 보다 적은) 수의 질의 워드들 (4608) 을 전송할 수도 있다. 이는 IRQ 그룹 질의 일반 호에 대한 시간을 짧게 하는 것을 가능하게 할 수도 있다.

IRQ 그룹 질의 (IQ) 워드들의 시퀀스는 종결 워드 (Term) (4606) 로 종료된다. 종결 워드 (4606) 의 심볼 패턴은 T11 RXCLK 에서 워드가 종결어 (Term) 이고 IRQ 그룹 질의 (IQ) 가 아니라는 것을 각각의 수신기 슬레이브 디바이스가 인식하여 SDA 라인 (4708) 을 마스킹하는 것을 중단할 때 및 IRQ 그룹 질의 일반 호의 끝을 알 수 있도록 선택될 수도 있다.

제 1 IRQ 그룹 질의 (IQ) 에 대한 3 개의 슬롯들 (4702, 4704, 및 4706) 은 그룹 0 , 1, 및 2 에 할당될 수도 있다. 보다 작은 수를 갖는 그룹에는 보다 빠른 응답 슬롯이 할당될 수도 있다.

일 예에서, 그룹 0 은 핫-플러깅된 디바이스들 또는 마스터 디바이스가 공유 버스 상에서 아직 인식하지 않은 디바이스들에 예약될 수도 있다. 적어도 하나의 IRQ 그룹 질의 (IQ) 워드가 전송되어야 하기 때문에, IRQ 를 발행한 임의의 핫-플러깅된 디바이스가 항상 인식된다.

종결 (Term) 워드 (4606) 의 이용 덕분에, 페이로드 (4604) 의 길이는 가변적으로 설정될 수 있고, IRQ 그룹 질의 (IQ) 워드 시퀀스의 길이는 필요하다면 11 워드들을 초과할 수 있다.

도 48 은 플렉시블한 IRQ 그룹 질의 일반 호의 길이 (즉, 워드 카운트) 를 가변적으로 하기 위해 IRQ 그룹 질의 일반 호의 끝을 나타내는데 이용될 수도 있는 일 예시적인 "종결 워드" 를 도시한다.

본원에서 설명된 IRQ 그룹 질의 방법은 대역-내 IRQ 들 및 측파-대역 IRQ 들 양자 모두에 적용가능할 수도 있다. 일 예에서, 설명된 IRQ 그룹 질의 방법을 이용하는 것은 슬레이브 디바이스 그룹들 사이에서 구별하기 위해서 IRQ 어써션 기간들을 이용하는 것을 막는다. 즉, 모든 슬레이브 디바이스들이 스캔되기 때문에, 상이한 폭들을 갖는 인터럽트 요청들을 이용하여 슬레이브 디바이스들을 구별할 필요가 없다. 결과적으로 측파대역 IRQ 들은 이제 어떠한 임의적 기간도 가질 수 있다. 슬레이브 디바이스 더 이상 정확하게 IRQ 기간을 맞추지 않으며, 따라서 자유 구동 클록이 더 이상 필요하지 않을 수도 있다.

또한, IRQ 그룹 질의를 이용하여 IRQ 조정이 또한 제거될 수 있다. 마스터 디바이스가 모든 그룹들 및 그 안의 슬레이브 디바이스들을 스캔하기 때문에, 마스터 디바이스는 한번에 다수의 IRQ 발행자들을 식별할 수 있으며, 이는 더 이상 조종 손실을 다룰 필요가 없기 때문에 슬레이브 디바이스 로직을 간소화한다.

슬레이브 디바이스들이 IRQ 그룹 질의를 이용하는 하나의 추가적인 혜택은 전력 절감인데, 슬레이브 디바이스가 DC 전류를 풀-업 레지스터로부터 그라운드로 야기할 수도 있는, 긴 시간의 기간 동안 IRQ 라인을 로우로 유지하는 것을 더 이상 할 필요가 없기 때문이다.

예시적인 전역 클록 판독

CCIe 는 소스 동기 심볼 전환 클록킹 시스템이다. 제어 데이터 버스를 통해 데이터를 전송하는 것은 누구든지 또한 데이터 내에 임베딩된 클록을 전송한다. I2C 와 달리, 모든 슬레이브 디바이스들은 클록 정보를 갖는 판독 데이터를 생성하기 위해 그것들의 클록 소스를 구비해야 한다. 그러나, IRQ 그룹 질의를 위해 이용되는 기법, 예를 들어, 모든 슬레이브 디바이스들이 그것들의 SDA 입력을 마스킹하고 슬레이브 디바이스들이 SDA 라인을 구동하는 것을 가능하게 하는 동안에 SCL 라인을 항상 토글하는 것은, 실제로 전역 클록 판독을 달성한다.

도 46 및 도 47 에서 이해될 수 있는 바와 같이, 주로 상이한 RXCLK 타이밍들을 갖는 다수의 슬레이브들이 동일한 타임 슬롯 내에서 SDA 라인을 구동하는 것을 가능하게 하도록, IRQ 그룹 질의 워드는 오직 3 개의 슬레이브 디바이스 응답들만을 반송할 수 있다. 그러나, 단일의 슬레이브 디바이스만이 SDA 마스크 중에 SDA 라인을 구동하는 것을 가능하게 하는 것은 더블 데이터 레이트 (double data rate; DDR) 전역 클록 판독을 구현하는 것을 가능하게 한다.

도 49 는 DDR 클록 판독 일반 호가 구현될 수도 있는 방법의 일 예를 도시한다. DDR 전역 클록 판독 시퀀스를 시작하기 전에, 마스터 디바이스는 다음을 나타내는 일부 CCIe 프로토콜 (예컨대, 일반 호) 을 발행한다:

1. 다음의 시퀀스는 DDR 전역 클록 판독물이다.

2. DDR 전역 클록 판독물의 워드들의 수.

3. 데이터를 판독할 디바이스의 SID.

4. 데이터를 판독할 디바이스의 레지스터 주소.

버스 상의 모든 디바이스들은 (특정 수의 워드들이 전송될 때까지) 호가 DDR 전역 클록 판독물인 이후의 모든 CCIe 트랜잭션들을 이해한다.

DDR 전역 클록 모드에서, 버스 상의 모든 디바이스들은 워드의 끝에서의 더미 심볼을 포함하여 심볼 기간 중에 그것들의 클록 데이터 복구 (CDR) 회로에 대해 SDA 입력을 마스킹해야 한다.

어드레싱된 슬레이브 디바이스는 (START 조건에 의해 RXCLK 를 포함하지 않는) 제 2 RXCLK 에서 SDA 라인을 로우로 구동하고, SDA 라인을 샘플링하도록 그것의 클록 (SDACLK) 을 교정하기 위해 마스터 디바이스에 의해 해당 로직 0 이 이용된다.

제 3 RXCLK 로부터, 어드레싱된 슬레이브 디바이스는 직렬로 데이터 중 9-비트들을 구동할 수 있다. 데이터 중 9-비트들은 시스템 요구사항에 따라 MSB 우선 또는 LSB 우선 또는 다른 포맷일 수도 있다. 이러한 기간 중에, 마스터 디바이스는 SCL 라인 상으로 DDR 전역 클록을 제공하거나 구동한다.

슬레이브 디바이스는 제 12 RXCLK 에서 SDA 라인을 하이로 구동하고, 제 13 RXCLK 에서 SDA 라인을 릴리스한다.

마스터 디바이스는 제 1 심볼 "3" 이 전송된 후에 SDA 라인을 릴리스하고, 마지막 심볼 "2" 후에 그것의 SDA 구동기를 인에이블하여 SDA 라인을 하이로 구동한다.

마스터는 9 개의 판독 데이터 비트들을 안쪽으로 쉬프트하도록 (shift-in) SDACLK 타이밍에 SDA 라인에서 샘플링한다.

도 50 은 전역 클록 판독 워드에 대한 일 예시적인 타이밍도를 도시한다. 제 1 클록 신호 SDACLK (5002) 및 제 2 클록 신호 RXCLK (5004) 는 마스터 디바이스 내의 내부 신호들을 나타낸다. 제 2 클록 신호 RXCLK (5004) 는 마스터 디바이스의 클록 데이터 복구 회로 (CDR) 에 의해 생성될 수도 있다. 제 1 클록 신호 SDACLK (5002) 는 클록 신호 생성 회로 (5006) 에 의해 생성될 수도 있으며, 클록 신호 생성 회로는 슬레이브 디바이스 신호에 의해 구동되는 경우 (공유 버스의 일부인) SDA 라인 (5008) 으로부터 데이터 값들을 샘플링하기 위해 마스터 디바이스에 의해 이용될 수도 있다. 제 1 클록 신호 SDACLK (5002) 는 SDAMASK 신호 (5010) 가 1 인 경우 (CDR 로의 SDA 라인 (5008) 입력은 마스킹된다) 에만 생성될 수도 있다.

전역 클록 판독 기간 중에 SDA 라인 (5008) 을 구동하는 것이 슬레이브 디바이스이기 때문에, (마스터 디바이스를 포함하여) 버스 상의 모든 디바이스들은 이러한 기간 중에 그것들의 CDR 로의 SDA 라인 (5008) 입력을 마스킹해야 하며, 이는 START 조건으로부터 제 2 클록 신호 RXCLK 상승 (5012) 에서 시작하고 더미 심볼에 의한 워드에 대한 마지막 RXCLK 상승 에지 (5014) 에서 종료한다.

이러한 예에서, 마스터 디바이스는 전역 클록 판독 워드로 0x5BE75 (2010_1010_10103) 를 전송한다. 이는 전역 클록 판독 일반 호의 페이로드 부분이기 때문에, 공유 버스 상의 각각의 디바이스는 호 메시지 "6" 후에 전역 클록 판독 워드들이 뒤따를 것을 알게 되며, 각각의 디바이스는 또한 SDAMASK (5010) 를 시작하고 끝낼 때를 알게 된다.

각각의 디바이스는 다음 워드가 제 1 심볼에서 구별되는 신호 패턴을 갖는 "종결" 워드가 아닌 한 다음 워드에 대해 전역 클록 판독 워드를 예상한다.

SDA 라인 (5008) 상의 데이터 신호가 슬레이브 디바이스의 CDR 로부터의 RXCLK (5016) 를 이용하여 슬레이브 디바이스에 의해 구동되기 때문에, 마스터 디바이스는 마스터 디바이스가 충분한 설정 및 대기 시간을 가지고 데이터를 샘플링하기 위해 마스터 디바이스의 CDR 로부터의 제 2 클록 신호 RXCLK (5004) 를 "적절히" 지연시켜야 한다. 마스터 디바이스는 마스터 디바이스가 전역 클록 판독 워드의 제 2 심볼을 전송한 후에 (즉, T10 사이클) 글로벌 전역 판독 프로토콜마다 슬레이브 디바이스에 의해 구동되는 SDA 라인 (5008) 의 제 1 하강 에지에서의 "적절한" 지연을 알게 된다. "교정 로직" (5018) 은 T10 사이클의 시작에서부터 하강하는 SDA 라인 (5008) 의 지연을 측정하고 "SDACLK 지연" 을 구성하는데 그 지연을 이용하므로, 마스터 디바이스는 다음 샘플로부터 슬레이브 디바이스로부터의 SDA 라인 (5008) 송신들을 신뢰할 수 있게 샘플링한다.

대역-내

IRQ

들을 이용하는

sI2C

및

CCIe

디바이스들의

예시적인 공존

도 51 은 디바이스 (5102) 내의 공유 버스 (5104) 에서의 I2C-호환가능한 디바이스와 CCIe-호환가능한 디바이스의 공존을 도시하며, 여기서 모든 마스터/슬레이브 디바이스들은 공유 버스 (5104) 를 통한 대역-내 인터럽트들을 이용한다. 이러한 예에서, I2C-호환가능하고 CCIe-호환가능한 마스터 디바이스 (5108) 가 공유 버스 (5104) 를 통한 통신들을 관리할 수도 있다. 마스터 디바이스 (5108) 는 I2C 모드 및 CCIe 모드 양자 모두에서 (즉, 2 개 이상의 구별되는 프로토콜들에 따라) 동작하도록 구성될 수도 있다. I2C-호환가능하고 CCIe-호환가능한 슬레이브 디바이스 (5110) 는 또한 공유 버스 (5104) 에 연결될 수도 있고 I2C 모드 및 CCIe 모드 양자 모두에서 동작하도록 구성된다. I2C-호환가능한 슬레이브 디바이스 (5112) 는 또한 공유 버스 (5104) 에 연결될 수도 있고 I2C 모드에서 동작하도록 구성된다. CCIe-호환가능한 슬레이브 디바이스 (5114) 는 또한 공유 버스 (5104) 에 연결될 수도 있고 CCIe 모드에서 동작가능하도록 구성된다.

도 52 는 공유 버스를 통한 도 51 의 마스터/슬레이브 디바이스들의 공존을 도시한다. I2C-호환가능하고 CCIe-호환가능한 마스터 디바이스 (5108) 는 초기에 제 1 프로토콜 모드 (예를 들어, I2C 모드) (5202) 로 동작할 수도 있다. 슬레이브 디바이스들 (5110, 5112, 5114) 은 마스터 디바이스 (5108) 또는 다른 슬레이브 디바이스들로부터의 커맨드들/송신들에 대해 공유 버스 (5204) 를 단순히 모니터링한다.

I2C-호환가능하고 CCIe-호환가능한 마스터 디바이스 (5108) 는 공유 버스 (5208) 를 통해 진입 호 메시지를 전송함으로써 제 2 프로토콜 모드 (예를 들어, CCIe 모드) 로의 스위치를 시작할 수도 있다. 모든 슬레이브 디바이스들 (5110, 5112, 및 5114) 은 공유 버스를 모니터링하고 공유 버스가 이용되는 방법에서의 변화 (예를 들어, 제 1 프로토콜 모드로부터 제 2 프로토콜 모드로의 변화) 로서 진입 호 메시지를 인식한다. 진입 호는 제 1 프로토콜 모드 (예를 들어, I2C 모드) 및 제 2 프로토콜 모드 (예를 들어, CCIe 모드) 로 동작하는 디바이스들이 진입 호를 검출하고/하거나 디코딩할 수 있는 것일 수도 있다. I2C & CCIe 슬레이브 (1510) 는 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두로 통신할 수 있기 때문에 여전히 버스를 이용할 수도 있고 인터럽트 요청들 (5210a) 을 발행할 수 있다. I2C-호환가능한 슬레이브 2 (5112) 는 제 2 프로토콜 모드 (CCIe 모드) 로 통신할 수 없기 때문에 버스를 이용할 수 없을 수도 있고 인터럽트 요청들 (5210b) 을 발행할 수 없다. CCIe-호환가능한 슬레이브 3 (5114) 은 제 2 프로토콜 모드 (CCIe 모드) 로 통신할 수 있기 때문에 버스를 이용할 수도 있고 인터럽트 요청들 (5210c) 을 발행할 수 있다.

I2C-호환가능하고 CCIe-호환가능한 마스터 디바이스 (5108) 는 나중에 공유 버스 (5212) 를 통해 종료 호 메시지를 전송함으로써 제 1 프로토콜 모드 (예를 들어, I2C 모드) 로 다시 스위칭할 수도 있다. 모든 슬레이브 디바이스들 (5110, 5112, 및 5114) 은 공유 버스를 모니터링하고 공유 버스가 이용되는 방법에서의 변화 (예를 들어, 제 2 프로토콜 모드로부터 제 1 프로토콜 모드로의 변화) 로서 종료 호 메시지를 인식한다. 종료 호는 제 1 프로토콜 모드 (예를 들어, I2C 모드) 및 제 2 프로토콜 모드 (예를 들어, CCIe 모드) 로 동작하는 디바이스들이 종료 호를 검출하고/하거나 디코딩할 수 있는 것일 수도 있다. I2C & CCIe 슬레이브 1 (1510) 은 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두로 통신할 수 있기 때문에 여전히 버스를 이용할 수도 있고 인터럽트 요청들 (5216a) 을 발행할 수 있다. I2C-호환가능한 슬레이브 2 (5112) 는 제 1 프로토콜 모드 (I2C 모드) 로 통신할 수 있기 때문에 버스를 이용할 수도 있고 인터럽트 요청들 (5216b) 을 발행할 수 있다. CCIe-호환가능한 슬레이브 3 (5114) 은 제 1 프로토콜 모드 (I2C 모드) 로 통신할 수 없기 때문에 버스를 이용할 수 없을 수도 있고 인터럽트 요청들 (5216b) 을 발행할 수 없다.

도 53 은 공유 버스를 통해 CCIe-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 I2C-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통해 대역-내 인터럽트들을 이용할 수도 있다. 제 1 슬레이브 디바이스 (예를 들어, I2C-호환가능한 슬레이브 디바이스) 는 공유 버스를 통한 대역-내 인터럽트 요청들을 포함하는 제 1 프로토콜 모드에 따라 동작될 수도 있으며, 공유 버스는 복수의 다른 슬레이브 디바이스들과 공유된다 (5302). 공유 버스는 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터의 진입 호에 대해 제 1 슬레이브 디바이스에 의해 모니터링될 수도 있다 (5304). 진입 호를 검출할 시에, 제 1 슬레이브 디바이스는 공유 버스를 통해 제 1 프로토콜 모드에 따라 제 1 슬레이브 디바이스가 임의의 대역-내 인터럽트 요청들을 하는 것을 디스에이블할 수도 있다 (5306). 제 1 슬레이브 디바이스는 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링할 수도 있다 (5308). 공유 버스를 통한 마스터 디바이스로부터의 종료 호의 검출 시에, 제 1 슬레이브 디바이스는 제 1 슬레이브 디바이스가 대역-내 인터럽트 요청을 하는 것을 인에이블할 수도 있다 (5310). 복수의 다른 슬레이브 디바이스들은 제 2 프로토콜 모드에 따라 동작하는 하나 이상의 슬레이브 디바이스들을 포함한다. 진입 호는 제 2 프로토콜 모드로 동작하는 하나 이상의 슬레이브 디바이스들에 대해 공유 버스가 제 2 프로토콜 모드에 따라 동작할 수 있다는 표시자의 역할을 할 수도 있다.

일 예에서, 제 1 슬레이브 디바이스는 프로세싱 회로에 연결된 버스 인터페이스를 포함할 수도 있다. 버스 인터페이스는 공유되는 공유 버스를 복수의 다른 슬레이브 디바이스들과 연결하는 역할을 할 수도 있다. 프로세싱 회로는 (a) 공유 버스를 통한 대역-내 인터럽트 요청들을 포함하는 제 1 프로토콜 모드에 따라 제 1 슬레이브 디바이스를 동작시키고 (공유 버스는 복수의 다른 슬레이브 디바이스들과 공유된다); (b) 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터의 진입 호에 대해 공유 버스를 모니터링하고; (c) 진입 호의 검출 시에 제 1 슬레이브 디바이스가 공유 버스를 통해 제 1 프로토콜 모드에 따라 임의의 대역-내 인터럽트 요청들을 하는 것을 디스에이블하고; (d) 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링하고; 및/또는 (e) 마스터 디바이스로부터의 종료 호의 검출 시에 제 1 슬레이브 디바이스가 공유 버스를 통해 대역-내 인터럽트 요청을 하는 것을 인에이블하도록 구성될 수도 있다. 복수의 다른 슬레이브 디바이스들은 제 2 프로토콜 모드에 따라 동작하는 하나 이상의 슬레이브 디바이스들을 포함할 수도 있다. 진입 호는 제 2 프로토콜 모드로 동작하는 하나 이상의 슬레이브 디바이스들에 대해 공유 버스가 제 2 프로토콜 모드에 따라 동작할 수 있다는 표시자의 역할을 할 수도 있다.

도 54 는 공유 버스를 통해 I2C-호환가능한 슬레이브 디바이스들과의 공존을 가능하게 하는 CCIe-호환가능한 슬레이브 디바이스에 의해 동작가능한 방법을 도시하며, 여기서 모든 디바이스들은 공유 버스를 통한 대역-내 인터럽트들을 이용할 수 있다. 슬레이브 디바이스는 복수의 다른 디바이스들과 공유되는 공유 버스에 연결되며, 여기서 적어도 다른 디바이스들의 제 1 서브세트는 제 1 프로토콜 모드에 따라 동작하고 슬레이브 디바이스는 제 2 프로토콜 모드에 따라 동작한다 (5402). 진입 호는 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터 공유 버스를 통해 슬레이브 디바이스에 의해 검출될 수도 있다 (5404). 인터럽트 요청 (IRQ) 은 공유 버스를 통해 대역-내로 또는 제 2 프로토콜 모드에 따라 별도의 경로를 통해 측파-대역으로 슬레이브 디바이스에 의해 전송될 수도 있다 (5406). 진입 호는 슬레이브 디바이스에 대해 공유 버스가 제 2 프로토콜 모드에 따라 동작할 수 있다는 표시자의 역할을 할 수도 있다. 슬레이브 디바이스는 제 2 프로토콜 모드에 따라 공유 버스를 통해 데이터 또는 커맨드들을 전송할 수도 있다 (5408).

슬레이브 디바이스는 또한 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링할 수도 있다 (5410). 마스터 디바이스로부터의 종료 호의 검출 시에, 슬레이브 디바이스는 공유 버스를 통해 대역-내 인터럽트 요청을 하는 것을 디스에이블하거나 중단할 수도 있다 (5412). 종료 호는 공유 버스가 제 1 프로토콜 모드에 따라 동작할 것임을 슬레이브 디바이스에 나타내는 역할을 할 수도 있다.

일 예에서, 슬레이브 디바이스는 프로세싱 회로에 연결된 버스 인터페이스를 포함할 수도 있다. 버스 인터페이스는 복수의 다른 디바이스들과 공유되는 공유 버스에 연결하는 역할을 할 수도 있으며, 여기서 적어도 다른 디바이스들의 제 1 서브세트는 제 1 프로토콜 모드에 따라 동작하고 슬레이브 디바이스는 제 2 프로토콜 모드에 따라 동작한다. 프로세싱 회로는 (a) 제 1 프로토콜 모드 및 제 2 프로토콜 모드에 따라 동작할 수 있는 마스터 디바이스로부터 공유 버스를 통해 진입 호를 검출하고; (b) 공유 버스 통해 대역-내 또는 제 2 프로토콜 모드에 따라 별도의 경로를 통해 측파-대역 인터럽트 요청 (IRQ) 을 전송하고; (c) 제 2 프로토콜 모드에 따라 공유 버스를 통해 데이터 및 커맨드들을 전송하고; (d) 마스터 디바이스로부터의 종료 호에 대해 공유 버스를 모니터링하고; 및/또는 (e) 마스터 디바이스로부터의 종료 호의 검출 시에 슬레이브 디바이스가 공유 버스를 통해 대역-내 인터럽트 요청을 하는 것을 디스에이블하도록 구성될 수도 있다.

진입 호는 슬레이브 디바이스에 대해 공유 버스가 제 2 프로토콜 모드에 따라 동작할 수 있다는 표시자의 역할을 할 수도 있다. 종료 호는 공유 버스가 제 1 프로토콜 모드에 따라 동작할 것임을 슬레이브 디바이스에 나타내는 역할을 한다.

유사하게, I2C-호환가능한 디바이스들 및 CCIe-호환가능한 디바이스들이 공존하면서 양 유형의 디바이스들이 공유 버스를 통한 인터럽트 요청들을 이용할 수도 있는 시스템이 제공된다. 디바이스들의 제 1 세트는 공유 버스에 연결된다. 디바이스들의 제 2 세트도 공유 버스에 연결된다.

디바이스들의 제 1 세트 내의 제 1 디바이스는 (a) 공유 버스를 통해 대역-내 인터럽트 요청들을 전송/수신하는 것을 포함하는 제 1 프로토콜 모드에 따라 동작하고; (b) 디바이스들의 제 2 세트에 있는 디바이스로부터의 진입 호에 대해 공유 버스를 모니터링하고; 및/또는 (c) 진입 호의 검출 시에, 제 1 슬레이브 디바이스가 공유 버스를 통해 임의의 대역-내 인터럽트 요청들을 하는 것을 디스에이블하도록 구성될 수도 있다.

디바이스들의 제 2 세트 내의 제 2 디바이스는 (a) 제 1 프로토콜 모드에 따라 공유 버스를 통해 진입 호를 검출하고; (b) 제 2 프로토콜 모드에 따라 공유 버스를 통해 인터럽트 요청 (IRQ) 을 전송하고; (c) 제 2 프로토콜 모드에 따라 공유 버스를 통해 데이터 또는 커맨드들을 전송하고; 및/또는 (d) 종료 호가 공유 버스 상에서 검출되면 제 2 프로토콜 모드에 따라 공유 버스를 통해 임의의 대역-내 인터럽트를 전송하는 것을 디스에이블하도록 구성될 수도 있다.

마스터 디바이스는 공유 버스에 연결되고, (a) 공유 버스를 통한 통신들을 관리하기 위해 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두 따라 동작하고; (b) 제 1 프로토콜 모드에 따라 공유 버스를 통해 진입 호를 전송하고; (c) 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두에 따라 슬레이브 디바이스들로부터의 인터럽트 요청들을 검출하고; 및/또는 (d) 요청하는 슬레이브 디바이스가 공유 버스에 액세스하는 것을 승인함으로써 인터럽트 요청들에 응답하도록 구성될 수도 있다.

예시적인 다중-

모드

공유 버스

아키텍쳐

공유 버스, 제 1 슬레이브 디바이스, 제 2 슬레이브 디바이스, 및/또는 마스터 디바이스를 포함하는 디바이스가 제공된다. 제 1 슬레이브 디바이스는 공유 버스에 연결될 수도 있고, (a) 공유 버스를 통해 대역-내 인터럽트 요청들을 발행하는 것을 포함하는 제 1 프로토콜 모드에 따라 동작하고; (b) 공유 버스가 제 2 프로토콜 모드로 스위칭하고 있다는 것을 나타내는 진입 호에 대해 공유 버스를 모니터링하고; 및/또는 (c) 진입 호의 검출 시에, 제 1 슬레이브 디바이스가 공유 버스를 통해 대역-내 인터럽트 요청들을 하는 것을 디스에이블하도록 구성된다.

제 2 슬레이브 디바이스는 공유 버스에 연결될 수도 있고, (a) 인터럽트 버스를 통해 측파-대역 인터럽트 요청들 또는 공유 버스를 통해 대역-내 인터럽트 요청을 발행하는 것을 포함하는 제 2 프로토콜 모드에 따라 동작하고; 및/또는 (b) 공유 버스를 통해 진입 호를 검출하도록 구성된다 (진입 호는 제 2 프로토콜 모드에 따라 송신된다).

마스터 디바이스는 공유 버스에 연결되고, (a) 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두에 따라 동작하고; (b) 공유 버스를 통한 통신들을 관리하고; (c) 공유 버스가 제 2 프로토콜 모드로 스위칭하고 있다는 것을 나타내는 진입 호를 공유 버스를 통해 전송하고 (여기서 진입 호는 제 1 프로토콜 모드에 따라 전송된다); (d) 제 1 프로토콜 모드 및 제 2 프로토콜 모드 양자 모두에 따라 슬레이브 디바이스들로부터의 인터럽트 요청들을 검출하고; 및/또는 (e) 공유 버스에 대한 요청하는 슬레이브 디바이스 액세스를 승인함으로써 인터럽트 요청들에 응답하도록 구성될 수도 있다.

마스터 디바이스는 공유 버스가 제 1 프로토콜 모드로 스위칭하는 것을 나타내는 종료 호를 공유 버스를 통해 전송하도록 더 구성될 수도 있으며, 여기서 종료 호는 제 2 프로토콜 모드 및 제 1 프로토콜 모드 양자 모두에 따라 전송된다.

대역-내 인터럽트들에 있어서, 제 2 프로토콜은 공유 버스를 통해 심볼들이 송신되는 심볼들 내의 인터럽트 기간을 정의하며, 그 동안에 공유 버스에 연결된 하나 이상의 슬레이브 디바이스들은 공유 버스의 제 1 라인 상으로 인터럽트 요청을 어써트할 수 있고, 한편 공유 버스의 제 2 라인은 하트비트 송신을 위해 마스터 디바이스에 의해 이용된다. 일 구현에서, 마스터 디바이스 및 제 2 슬레이브 디바이스는 인터럽트 기간 중에 공유 버스의 제 1 라인을 내부적으로 마스킹하도록 구성될 수도 있다.

마스터 디바이스는 공유 버스로 제 2 프로토콜 모드에 따라 동작하는 인터럽트 그룹 질의 호를 모든 슬레이브 디바이스들에 전송하도록 구성될 수도 있으며, 여기서 그러한 인터럽트 그룹 질의 호는 임의의 어써트하는 슬레이브 디바이스들이 응답할 수 있는 슬롯들을 제공한다.

제 2 슬레이브 디바이스는 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 경우 제 2 프로토콜 모드에 따라 공유 버스를 통해 데이터 또는 커맨드들을 수신하도록 더 구성될 수도 있다.

제 1 슬레이브 디바이스는 공유 버스가 제 2 프로토콜 모드에 따라 동작하는 동안에 전용 인터럽트 라인 또는 공유 버스와 별개인 버스를 통해 인터럽트 요청을 전송하도록 더 구성될 수도 있다.

디바이스는 또한 전용 라인을 통해 제 1 슬레이브 디바이스로부터 인터럽트 요청들을 수신하고 전용 인터럽트 버스 또는 제 2 프로토콜에 따른 버스를 통해 수신된 인터럽트 요청을 전송하도록 구성된 인터럽트 라우터 슬레이브 디바이스를 포함할 수도 있다.