KR20160029835A - 비트 셀 및 로직 패터닝을 갖는 모놀리식 3차원(3d) 랜덤 액세스 메모리(ram) 어레이 아키텍처 - Google Patents

비트 셀 및 로직 패터닝을 갖는 모놀리식 3차원(3d) 랜덤 액세스 메모리(ram) 어레이 아키텍처 Download PDFInfo

- Publication number

- KR20160029835A KR20160029835A KR1020167003141A KR20167003141A KR20160029835A KR 20160029835 A KR20160029835 A KR 20160029835A KR 1020167003141 A KR1020167003141 A KR 1020167003141A KR 20167003141 A KR20167003141 A KR 20167003141A KR 20160029835 A KR20160029835 A KR 20160029835A

- Authority

- KR

- South Korea

- Prior art keywords

- ram

- tier

- 3dic

- disposed

- data bank

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000000638 solvent extraction Methods 0.000 title abstract description 7

- 238000000034 method Methods 0.000 claims description 22

- 230000008878 coupling Effects 0.000 claims description 4

- 238000010168 coupling process Methods 0.000 claims description 4

- 238000005859 coupling reaction Methods 0.000 claims description 4

- 230000003068 static effect Effects 0.000 claims description 4

- 238000004891 communication Methods 0.000 claims description 3

- 230000001413 cellular effect Effects 0.000 claims description 2

- 238000003491 array Methods 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 238000012545 processing Methods 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 239000000872 buffer Substances 0.000 description 4

- 210000000038 chest Anatomy 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000010295 mobile communication Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 239000004744 fabric Substances 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

- 239000002918 waste heat Substances 0.000 description 1

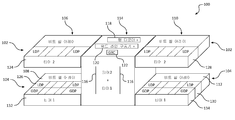

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1072—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for memories with random access ports synchronised on clock signal pulse trains, e.g. synchronous memories, self timed memories

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

- G11C5/025—Geometric lay-out considerations of storage- and peripheral-blocks in a semiconductor storage device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/12—Group selection circuits, e.g. for memory block selection, chip selection, array selection

-

- H01L27/0688—

-

- H01L27/108—

-

- H01L27/11—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Memories (AREA)

- Static Random-Access Memory (AREA)

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361845044P | 2013-07-11 | 2013-07-11 | |

| US61/845,044 | 2013-07-11 | ||

| US14/012,478 US20150019802A1 (en) | 2013-07-11 | 2013-08-28 | Monolithic three dimensional (3d) random access memory (ram) array architecture with bitcell and logic partitioning |

| US14/012,478 | 2013-08-28 | ||

| PCT/US2014/046152 WO2015006563A1 (en) | 2013-07-11 | 2014-07-10 | A monolithic three dimensional (3d) random access memory (ram) array architecture with bitcell and logic partitioning |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160029835A true KR20160029835A (ko) | 2016-03-15 |

Family

ID=52278089

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167003141A Withdrawn KR20160029835A (ko) | 2013-07-11 | 2014-07-10 | 비트 셀 및 로직 패터닝을 갖는 모놀리식 3차원(3d) 랜덤 액세스 메모리(ram) 어레이 아키텍처 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20150019802A1 (enExample) |

| EP (1) | EP3020045A1 (enExample) |

| JP (1) | JP6407992B2 (enExample) |

| KR (1) | KR20160029835A (enExample) |

| CN (1) | CN105378843A (enExample) |

| WO (1) | WO2015006563A1 (enExample) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108292514B (zh) | 2015-11-06 | 2022-04-29 | 卡弗科学有限公司 | 电熵存储器设备 |

| US9929149B2 (en) | 2016-06-21 | 2018-03-27 | Arm Limited | Using inter-tier vias in integrated circuits |

| CN115188591A (zh) | 2016-12-02 | 2022-10-14 | 卡弗科学有限公司 | 存储设备和电容储能设备 |

| GB2563473B (en) * | 2017-06-15 | 2019-10-02 | Accelercomm Ltd | Polar coder with logical three-dimensional memory, communication unit, integrated circuit and method therefor |

| CN110603640B (zh) * | 2017-07-17 | 2023-06-27 | 美光科技公司 | 存储器电路系统 |

| JP7338975B2 (ja) | 2018-02-12 | 2023-09-05 | 三星電子株式会社 | 半導体メモリ素子 |

| FR3089678B1 (fr) | 2018-12-11 | 2021-09-17 | Commissariat Energie Atomique | Memoire ram realisee sous la forme d’un circuit integre 3d |

| US11469214B2 (en) | 2018-12-22 | 2022-10-11 | Xcelsis Corporation | Stacked architecture for three-dimensional NAND |

| US11139283B2 (en) | 2018-12-22 | 2021-10-05 | Xcelsis Corporation | Abstracted NAND logic in stacks |

| EP4024222A1 (en) | 2021-01-04 | 2022-07-06 | Imec VZW | An integrated circuit with 3d partitioning |

| CN115996200A (zh) * | 2021-10-15 | 2023-04-21 | 西安紫光国芯半导体有限公司 | 3d-ic基带芯片、堆叠芯片及数据处理方法 |

| US20240008239A1 (en) * | 2022-07-01 | 2024-01-04 | Intel Corporation | Stacked sram with shared wordline connection |

| CN116741227B (zh) * | 2023-08-09 | 2023-11-17 | 浙江力积存储科技有限公司 | 一种三维存储器架构及其操作方法和存储器 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5089993B1 (en) * | 1989-09-29 | 1998-12-01 | Texas Instruments Inc | Memory module arranged for data and parity bits |

| JP3707888B2 (ja) * | 1996-02-01 | 2005-10-19 | 株式会社日立製作所 | 半導体回路 |

| US5673227A (en) * | 1996-05-14 | 1997-09-30 | Motorola, Inc. | Integrated circuit memory with multiplexed redundant column data path |

| KR100699421B1 (ko) * | 1999-02-23 | 2007-03-26 | 가부시키가이샤 히타치세이사쿠쇼 | 반도체집적회로장치 |

| JP4421957B2 (ja) * | 2004-06-29 | 2010-02-24 | 日本電気株式会社 | 3次元半導体装置 |

| EP2248130A1 (en) * | 2008-02-19 | 2010-11-10 | Rambus Inc. | Multi-bank flash memory architecture with assignable resources |

| US7894230B2 (en) * | 2009-02-24 | 2011-02-22 | Mosaid Technologies Incorporated | Stacked semiconductor devices including a master device |

| TW201207852A (en) * | 2010-04-05 | 2012-02-16 | Mosaid Technologies Inc | Semiconductor memory device having a three-dimensional structure |

| US8273610B2 (en) * | 2010-11-18 | 2012-09-25 | Monolithic 3D Inc. | Method of constructing a semiconductor device and structure |

| JP2012083243A (ja) * | 2010-10-13 | 2012-04-26 | Elpida Memory Inc | 半導体装置及びそのテスト方法 |

| US9257152B2 (en) * | 2012-11-09 | 2016-02-09 | Globalfoundries Inc. | Memory architectures having wiring structures that enable different access patterns in multiple dimensions |

-

2013

- 2013-08-28 US US14/012,478 patent/US20150019802A1/en not_active Abandoned

-

2014

- 2014-07-10 CN CN201480039131.9A patent/CN105378843A/zh active Pending

- 2014-07-10 JP JP2016525483A patent/JP6407992B2/ja not_active Expired - Fee Related

- 2014-07-10 EP EP14744412.9A patent/EP3020045A1/en not_active Withdrawn

- 2014-07-10 WO PCT/US2014/046152 patent/WO2015006563A1/en not_active Ceased

- 2014-07-10 KR KR1020167003141A patent/KR20160029835A/ko not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| EP3020045A1 (en) | 2016-05-18 |

| JP6407992B2 (ja) | 2018-10-17 |

| JP2016528727A (ja) | 2016-09-15 |

| US20150019802A1 (en) | 2015-01-15 |

| CN105378843A (zh) | 2016-03-02 |

| WO2015006563A1 (en) | 2015-01-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20160029835A (ko) | 비트 셀 및 로직 패터닝을 갖는 모놀리식 3차원(3d) 랜덤 액세스 메모리(ram) 어레이 아키텍처 | |

| US9171608B2 (en) | Three-dimensional (3D) memory cell separation among 3D integrated circuit (IC) tiers, and related 3D integrated circuits (3DICS), 3DIC processor cores, and methods | |

| US9111635B2 (en) | Static random access memories (SRAM) with read-preferred cell structures, write drivers, related systems, and methods | |

| US9876017B2 (en) | Static random access memory (SRAM) bit cells with wordline landing pads split across boundary edges of the SRAM bit cells | |

| CN105683864B (zh) | 具有垂直存储器部件的单片式三维(3d)集成电路(ic)(3dic) | |

| JP6290515B2 (ja) | 性能を向上させるために別々の金属層上にワード線を有するスタティックランダムアクセスメモリ(sram)ビットセル、および関連する方法 | |

| US20140293682A1 (en) | Memory bitcell clusters employing localized generation of complementary bitlines to reduce memory area, and related systems and methods |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20160203 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |