KR20110118150A - Mixed format media transmission systems and methods - Google Patents

Mixed format media transmission systems and methods Download PDFInfo

- Publication number

- KR20110118150A KR20110118150A KR1020117020191A KR20117020191A KR20110118150A KR 20110118150 A KR20110118150 A KR 20110118150A KR 1020117020191 A KR1020117020191 A KR 1020117020191A KR 20117020191 A KR20117020191 A KR 20117020191A KR 20110118150 A KR20110118150 A KR 20110118150A

- Authority

- KR

- South Korea

- Prior art keywords

- signal

- frame

- constellation

- baseband

- video signal

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/10—Adaptations for transmission by electrical cable

- H04N7/106—Adaptations for transmission by electrical cable for domestic distribution

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/26—Systems using multi-frequency codes

- H04L27/2601—Multicarrier modulation systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/32—Carrier systems characterised by combinations of two or more of the types covered by groups H04L27/02, H04L27/10, H04L27/18 or H04L27/26

- H04L27/34—Amplitude- and phase-modulated carrier systems, e.g. quadrature-amplitude modulated carrier systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/32—Carrier systems characterised by combinations of two or more of the types covered by groups H04L27/02, H04L27/10, H04L27/18 or H04L27/26

- H04L27/34—Amplitude- and phase-modulated carrier systems, e.g. quadrature-amplitude modulated carrier systems

- H04L27/38—Demodulator circuits; Receiver circuits

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/60—Control of cameras or camera modules

- H04N23/63—Control of cameras or camera modules by using electronic viewfinders

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/60—Control of cameras or camera modules

- H04N23/66—Remote control of cameras or camera parts, e.g. by remote control devices

- H04N23/661—Transmitting camera control signals through networks, e.g. control via the Internet

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/08—Systems for the simultaneous or sequential transmission of more than one television signal, e.g. additional information signals, the signals occupying wholly or partially the same frequency band, e.g. by time division

- H04N7/0806—Systems for the simultaneous or sequential transmission of more than one television signal, e.g. additional information signals, the signals occupying wholly or partially the same frequency band, e.g. by time division the signals being two or more video signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L2025/0335—Arrangements for removing intersymbol interference characterised by the type of transmission

- H04L2025/03375—Passband transmission

- H04L2025/0342—QAM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L2025/03592—Adaptation methods

- H04L2025/03598—Algorithms

- H04L2025/03611—Iterative algorithms

- H04L2025/03617—Time recursive algorithms

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/0014—Carrier regulation

- H04L2027/0044—Control loops for carrier regulation

- H04L2027/0053—Closed loops

- H04L2027/0057—Closed loops quadrature phase

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/0014—Carrier regulation

- H04L2027/0044—Control loops for carrier regulation

- H04L2027/0063—Elements of loops

- H04L2027/0067—Phase error detectors

Abstract

카메라를 동작시키는 시스템 및 방법이 설명된다. 이미지 센서로부터 수신된 이미지 신호가 이미지 신호를 나타내는 복수의 비디오 신호로서 처리될 수 있다. 인코더는 케이블을 통한 전송을 위해 기저대역 및 디지털 비디오 신호를 결합할 수도 있다. 비디오 신호는 실질적으로 등시성인 기저대역 및 디지털 비디오 신호를 포함할 수도 있다. 디코더는 업스트림 신호를 복조하여 카메라의 위치 및 방향 및 기저대역 및 디지털 비디오 신호의 콘텐츠를 제어하는 제어 신를 획득한다. 다양한 신호를 수신하여, 신호에 관련된 동기화 정보를 제공하고, 신호의 위상 시프트 오프셋을 보정하며, 시그널링에서 사용된 인코딩 방법을 사용하거나 검출한다. 신호의 존재를 검출하는 시스템 및 방법이 설명된다. Systems and methods of operating a camera are described. The image signal received from the image sensor may be processed as a plurality of video signals representing the image signal. The encoder may combine baseband and digital video signals for transmission over the cable. The video signal may include baseband and digital video signals that are substantially isochronous. The decoder demodulates the upstream signal to obtain a control scene that controls the position and orientation of the camera and the content of the baseband and digital video signals. It receives various signals, provides synchronization information related to the signals, corrects the phase shift offset of the signals, and uses or detects the encoding method used in the signaling. Systems and methods for detecting the presence of a signal are described.

Description

본 발명은 다중 매체 전송 시스템에 관한 것이며, 더욱 상세하게는 신호 케이블을 통한 표준 아날로그 비디오 및 고화질 디지털 비디오를 전송하는 시스템 및 방법에 관한 것이다. The present invention relates to a multimedia transmission system, and more particularly to a system and method for transmitting standard analog video and high definition digital video over a signal cable.

디지털 방송 텔레비전 및 스트리밍 비디오 기술의 도래와 함께, 다양한 비디오 카메라, 모니터, 및 비디오 리코더가 향상된 해상도 및 향상된 특성으로 이용가능하게 되었다. 현재, 폐쇄회로 텔레비전 (CCTV) 시스템은 구내 감시, 장비의 접근 제어 및 원격 모니터링과 같은 애플리케이션에서의 사용을 위해 고화질 비디오 출력 및 압축된 디지털 비디오 신호를 제공한다. 그러나 구형 컴퓨터 시스템은 아직 남아있고 표준 아날로그 비디오 신호는 광범위하게 사용되며 모든 디지털, 고화질 시스템으로의 전송 동안 계속 사용될 것이다. 특히, 동축 케이블 ("Coax")은 CCTV 카메라로부터 감시국으로 신호를 전달하기 위해 사용되어왔다. 몇몇 사용된 CCTV 카메라는 지역 네트워크, 또는 광역 네트워크를 통해 압축된 비디오 신호를 전송하며, 이들 카메라는 압축된 비디오 신호를 전송하는 통신 수단으로서 인터넷 프로토콜 ("IP")을 사용할 수도 있다. With the advent of digital broadcast television and streaming video technology, a variety of video cameras, monitors, and video recorders have become available with improved resolution and enhanced features. Currently, closed circuit television (CCTV) systems provide high quality video output and compressed digital video signals for use in applications such as on-premises surveillance, equipment access control and remote monitoring. However, older computer systems still remain and standard analog video signals are widely used and will continue to be used during transmission to all digital and high definition systems. In particular, coaxial cables ("Coax") have been used to transmit signals from CCTV cameras to surveillance stations. Some used CCTV cameras transmit compressed video signals over local or wide area networks, and these cameras may use the Internet Protocol (“IP”) as a communication means for transmitting the compressed video signals.

도 1은 표준 아날로그 비디오를 전달하기 위해 Coax를 사용하는 종래 시스템을 나타낸다. 통상적으로 기본 아날로그 카메라 (10)는 Coax (11)을 사용하여 300미터까지 전송될 수 있는 CVBS (composite video baseband signal)를 생성한다. 보통 CVBS 신호는 CVBS를 디지털 포맷으로 기록하는 디지털 비디오 리코더 ("DVR")을 종종 포함하는 비디오 기록 시스템에 제공된다. 종래의 모니터 (14)는 DVR (12)에 접속되어 일반적으로 720×480 화소의 해상도를 갖는 표준 아날로그 비디오를 동시에 디스플레이할 수도 있다. 1 illustrates a conventional system using Coax to deliver standard analog video. Typically, the base

디지털 카메라 (16)는 일부 적용에 있어서 아날로그 카메라 (10)를 대체할 수도 있다. 디지털 카메라 (16)는 대략 270 Mbps로 DVR (12)에 Coax (17)을 통해 비압축 표준 디지털 비디오를 전송하는데 사용될 수 있는 직렬 디지털 인터페이스 ("SDI")를 지원할 수도 있다.

도 2는 현재 사용된 시스템에서 고화질 비디오 (1920×1080 화소)를 전송함에 대한 종래의 접근이다. 우선, 디지털 카메라 (20)는 1.5Gbps 레이트로 DVR (22)에 Coax (21)을 통해 비압축 고화질 디지털 비디오를 전송하는 데 사용될 수 있는 고화질 직렬 디지털 인터페이스 (HD-SDI)를 지원할 수도 있다. 이러한 고 전송 레이트하에서 지원된 케이블 거리는 100 미터까지이다. 둘째, IP 기반 고화질 ("HD") 카메라 (24)는 100까지의 거리를 위해 표준 카테고리 5 ("CAT5") 트위스티드페어케이블 (25)을 사용하는 100Mbps 이더넷을 통해 압축된 디지털 HD 비디오 신호를 생성할 수도 있다. 신호는 DVR (22)에 의해 수신되어 비 실시간 재생을 위해 기록된다. 현재 Coax (26)는 CAT5-to-Coax 브리지 모뎀 (27 및 29) 또는 다른 변환 디바이스를 사용하여 카메라 (24)로부터 DVR (22)에 비디오를 전송하는데 사용될 수 있다. 카메라가 디지털 비디오를 전송하게 하는 네트워크의 사용은 이들 시스템이 몇몇 업스트림 통신, 통상적으로는 제어 및 오디오 신호 (28)를 부가하도록 한다. 2 is a conventional approach to transmitting high definition video (1920x1080 pixels) in currently used systems. First, the

본 발명의 특정 실시예는 카메라 및 시스템 및 카메라를 동작하는 방법을 제공한다. 프로세서는 이미지 센소로부터 이미지 신호를 수신하여 이미지 신호를 나타내는 복수의 비디오 신호를 생성할 수도 있다. 인코더는 케이블을 통한 출력 신호로서 기저대역 비디오 신호와 디지털 신호를 결합하는데 사용된다. 비디오 신호 실질적으로 등시성 (isochronous)인 디지털 비디오 및 기저대역 비디오를 포함할 수도 있다. 카메라는 폐쇄회로 고화질 텔레비전 카메라로서 동작할 수도 있다. Certain embodiments of the present invention provide a camera and system and a method of operating the camera. The processor may receive an image signal from an image sensor and generate a plurality of video signals representing the image signal. The encoder is used to combine the baseband video signal and the digital signal as an output signal through the cable. Video signals may include digital video and baseband video that are substantially isochronous. The camera may operate as a closed circuit high definition television camera.

본 발명의 특정 양태에 따르는 경우, 기저대역 신호는 표준 아날로그 비디오 신호를 포함할 수 있으며, 디지털 비디오 신호는 기저대역 비디오 신호와의 결합 이전에 변조될 수도 있다. 디지털 비디오 신호는 압축된 고화질 디지털 비디오 신호를 포함할 수 있다. 특히 변조된 디지털 신호가 비디오 리코더에 제공되는 경우, 디지털 비디오 신호의 프레임 레이트는 이미지 신호의 프레임 레이트 미만일 수 있다.In accordance with certain aspects of the present invention, the baseband signal may comprise a standard analog video signal, and the digital video signal may be modulated prior to combining with the baseband video signal. The digital video signal may comprise a compressed high definition digital video signal. In particular, when a modulated digital signal is provided to the video recorder, the frame rate of the digital video signal may be less than the frame rate of the image signal.

특정 실시예에서, 디코더는 다운스트림 비디오를 전달하는데 사용된 전송 케이블로부터 또는 무선 통신 네트워크로부터 수신된 업스트림 신호를 복조하도록 구성된다. 변조된 업스트림 신호는, 카메라의 위치 및 방향을 제어하는 신호, 프로세서에 의한 기저대역 비디오 신호 및 디지털 비디오 신호의 생성을 제어하는 신호, 기저대역 비디오 신호로서의 인코딩을 위한 이미지 신호의 부분을 선택하는 신호를 포함하는 제어 신호를 포함할 수 있다. 또한, 제어 신호는 디지털 비디오 신호로서의 인코딩을 위한 이미지 신호의 부분을 선택하는 신호, 및 확성기와 같은 카메라의 오디오 출력을 구동하는데 사용된 오디오 신호를 포함할 수도 있다. In a particular embodiment, the decoder is configured to demodulate an upstream signal received from a transmission cable used to carry downstream video or from a wireless communication network. The modulated upstream signal is a signal that controls the position and orientation of the camera, a signal that controls the generation of baseband video signals and digital video signals by a processor, and a signal that selects a portion of an image signal for encoding as a baseband video signal. It may include a control signal including a. The control signal may also include a signal that selects a portion of an image signal for encoding as a digital video signal, and an audio signal used to drive the audio output of the camera, such as a loudspeaker.

본 발명의 특정 실시예는 비디오 이미지를 전송하는 방법을 제공한다. 방법은 고화질 이미지 비디오로부터 수신한 비디오 신호를 주파수 분할 다중화하여 변조된 디지털 신호를 획득하는 단계, 변조된 신호와 비디오 신호를 나타내는 기저대역 아날로그 신호를 결합함으로써 출력 신호를 생성하는 단계, 및 모니터 및 디지털 비디오 저장 디바이스에 출력 신호를 동시에 전송하는 단계를 포함할 수도 있다. 이들 실시예들 중 일부에서, 모니터는 비디오 신호의 기저대역 아날로그 표현을 디스플레이하며, 및/또는 디지털 비디오 저장소는 디지털 비디오 리코더를 사용하여 변조된 디지털 신호로부터 추출된 고화질 프레임의 시퀀스를 기록한다. 디지털 비디오 신호는 압축될 수도 있다.Certain embodiments of the present invention provide a method of transmitting a video image. The method comprises frequency division multiplexing a video signal received from a high quality image video to obtain a modulated digital signal, generating an output signal by combining the modulated signal with a baseband analog signal representing the video signal, and monitor and digital Simultaneously transmitting output signals to the video storage device. In some of these embodiments, the monitor displays a baseband analog representation of the video signal, and / or the digital video store records a sequence of high quality frames extracted from the modulated digital signal using a digital video recorder. The digital video signal may be compressed.

특정 실시예에서, 출력 신호를 전송하는 것은 출력 신호를 동축 케이블 및/또는 무선 전송기에 제공하는 것을 포함한다. 동축 케이블 또는 무선 네트워크로부터 수신된 입력 신호는 복조되어 제어 신호를 획득할 수도 있다. 기저대역 아날로그 신호는 복합 비디오 신호에서 비디오 신호의 부분을 인코딩함으로써 생성될 수도 있으며, 복합 비디오 신호에서 인코딩될 비디오 신호의 부분은 제어 신호를 사용하여 제어될 수도 있다. 제어 신호는 카메라의 위치를 제어할 수도 있다. 입력 신호를 복조하는 것은 입력 신호로부터 오디오 신호를 추가적으로 산출할 수도 있다. In a particular embodiment, transmitting the output signal includes providing the output signal to a coaxial cable and / or a wireless transmitter. The input signal received from the coaxial cable or the wireless network may be demodulated to obtain a control signal. The baseband analog signal may be generated by encoding a portion of the video signal in the composite video signal, and the portion of the video signal to be encoded in the composite video signal may be controlled using a control signal. The control signal may control the position of the camera. Demodulating the input signal may further calculate an audio signal from the input signal.

본 발명의 특정 실시예는 카메라를 동작하는 시스템 및 방법을 제공한다. 프로세서는 이미지 센서로부터 이미지 신호를 수신하여 복수의 비디오 신호를 생성하고, 제어 로직은 카메라에 의해 수신된 제어 신호에 응답하도록 구성될 수도 있으며, 변조기는 디지털 비디오 신호를 변조하여 변조된 신호를 획득하도록 구성될 수 있다. 복수의 비디오 신호는 기저대역 비디오 신호 및 디지털 비디오 신호를 포함할 수 있다. 복수의 비디오 신호 각각은 카메라의 시야 중 적어도 일부를 나타내며, 제어 신호는 디지털 비디오 신호 및 기저대역의 콘텐츠를 제어할 수도 있다. 통상적으로, 변조된 신호 및 기저대역 비디오 신호는 카메라에 의해 동시에 전송된다. Certain embodiments of the present invention provide a system and method for operating a camera. The processor receives the image signal from the image sensor to generate a plurality of video signals, and the control logic may be configured to respond to the control signal received by the camera, wherein the modulator modulates the digital video signal to obtain a modulated signal. Can be configured. The plurality of video signals may include a baseband video signal and a digital video signal. Each of the plurality of video signals represents at least a portion of the field of view of the camera, and the control signal may control the digital video signal and the baseband content. Typically, the modulated signal and the baseband video signal are transmitted simultaneously by the camera.

기저대역 및 디지털 비디오 신호는 실질적으로 등시성일 수도 있다. 인코더는 케이블을 통한 전송용 출력 신호로서 기저대역 비디오 신호와 변조된 신호를 결합할 수 있다. 제어 신호는 예를 들어, 무선 네트워크로부터 무선으로 수신될 수 있다. 변조된 신호는 적어도 부분적으로 무선으로 전송될 수도 있다. 디지털 비디오 신호는 고화질 디지털 비디오 신호일 수도 있으며, 압축된 디지털 비디오 신호일 수도 있다. 제어 신호는 비디오 신호 중 하나에 의해 나타난 시야 중 일부를 이동시킨다. Baseband and digital video signals may be substantially isochronous. The encoder can combine the baseband video signal and the modulated signal as an output signal for transmission over the cable. The control signal can be received wirelessly, for example, from a wireless network. The modulated signal may be transmitted at least partially wirelessly. The digital video signal may be a high quality digital video signal or may be a compressed digital video signal. The control signal shifts some of the field of view represented by one of the video signals.

도 1은 표준 아날로그 비디오를 전달하는 Coax를 사용하는 종래 시스템을 나타낸다.

도 2는 고화질 디지털 비디오를 전송함에 대한 종래의 접근이다.

도 3은 본 발명의 특정 양태에 따른 아날로그 및 디지털 비디오의 전송을 위한 시스템을 나타낸다.

도 4는 본 발명의 특정 양태에 따른 아날로그 및 디지털 비디오의 전송을 위한 네트워크를 나타낸다.

도 5는 본 발명의 특정 양태에 따른 동축 케이블을 통한 아날로그 및 디지털 비디오의 전송을 위한 대역폭 할당을 도시한다.

도 6은 본 발명의 특정 양태에 따라 구축된 CCTV 장비의 일 예를 나타낸다.

도 7은 본 발명의 특정 양태에 따라 구축된 DVR 장비에서 사용된 모뎀의 일 예를 나타낸다.

도 8은 본 발명의 특정 양태에 따라 구축된 네트워크 스위치 장비에서 사용된 모뎀의 일 예를 나타낸다.

도 9는 ATSC 디지털 텔레비전에서 사용된 프레임 구조의 예이다.

도 10은 종래 프레임 동기화 패킷의 일 예이다.

도 11은 종래 데이터 프레임의 데이터 세그멘트의 일 예이다.

도 12는 프레임 배열의 간략도를 제공한다.

도 13은 본 발명의 특정 양태에 따른 변조기의 블록도이다.

도 14는 본 발명의 특정 실시예에서 사용된 프레임 구조의 블록도이다.

도 15는 본 발명의 특정 실시예에서의 컨벌루션 바이트 인터리버의 동작을 나타낸다.

도 16은 본 발명의 특정 실시예에서 사용된 선택적 코드 레이트 펑처 (punctured) 격자 코딩된 변조의 블록도이다.

도 17은 QAM 정합의 예를 나타낸다.

도 18은 프레임 동기화/모드 패킷을 나타낸다.

도 19는 본 발명의 특정 실시예에서 사용된 간단화된 프레임 구조이다.

도 20은 본 발명의 특정 양태에 따른 복조기의 블록도이다.

도 21은 본 발명의 특정 양태에 따른 카메라측 모뎀의 블록도이다.

도 22는 본 발명의 특정 양태에 따른 모니터측 모뎀의 블록도이다.

도 23은 본 발명의 특정 양태에 따른 카메라측의 기저대역에서 통과대역으로의 QAM 변조기를 나타낸다.

도 24a 및 도 24b는 본 발명의 특정 양태에 따른 모니터측의 기저대역에서 통과대역으로의 QAM 복조기를 나타낸다.

도 25는 본 발명의 특정 양태에 따른 모니터측 디지털 균등화기 및 반송파 위상/주파수 루프를 나타낸다.

도 26은 감쇄가 동축 케이블에서 주파수의 기능으로서 나타냄을 도시한다.

도 27a는 균등화기 입력의 전력 스펙트럼 밀도 (PSD)를 나타낸다.

도 27b는 수렴된 균등화기 탭 (tap)의 진폭 응답을 나타낸다.

도 28a, 도 28b, 도 29a, 및 도 29b는 상이한 주파수에서 통과대역 디지털 비디오 신호의 손실 대 경사를 나타낸다.

도 30은 본 발명의 특정 양태에 따라 QAM 복조기 내부에 디지털 균등화기를 갖는 모니터측 모뎀을 나타낸다.

도 31은 본 발명의 특정 양태에 따라 기저대역 CVBS 를 균등화하는데 적합한 아날로그 활성 필터를 나타낸다.

도 32는 본 발명의 특정 실시예에서의 필터 응답의 예를 나타낸다.

도 33a 및 도 33b는 복소평면에서의 회전을 나타내는 QPSK 성좌도 (constellations)이다.

도 34는 본 발명의 특정 양태에 따른 위상 보정 처리를 나타내는 블록도이다.

도 35는 본 발명의 특정 양태에 따른 적분-비례 ("IP") 필터를 나타낸다.

도 36은 전송된 심볼을 나타낸다.

도 37a, 도 37b, 도 37c, 및 도 37d는 도 36의 전송된 심볼에 기반하여 가능한 복구된 심볼을 나타낸다.

도 38은 수신된 심볼에서의 위상 이동을 나타낸다.

도 39는 프레임 동기화 심볼의 통상적인 실수부 및 허수부에 기반하여 전송된 성좌도의 예를 나타낸다.

도 40은 본 발명의 특정 양태에 따라 사용된 위상 오프셋 보정기의 블록도이다.

도 41은 프레임 동기화와 관련된 신뢰성을 결정하는 프로세스를 나타낸다.

도 42는 본 발명의 특정 실시예에서 사용된 균등화기 및 반송파 위상/주파수 루프의 특정 양태를 나타낸다.

도 43은 본 발명의 특정 실시예에서 사용된 위상 에러 검출 모듈 및 슬라이서 (slicer)를 나타낸다.

도 44는 본 발명의 특정 실시예에서 사용된 복수 지수 LUT 모듈을 나타낸다.

도 45a 및 도 45b는 QPSK 신호 (도 45a) 및 16-QAM 신호 (도 45b)의 균등화된 출력 중 실수부를 나타낸다.

도 46a, 도 46b, 및 도 46c는 성좌도가 균등화기가 R=58 에서 수렴되는 일 실시예를 사용하여 생성된 QPSK (도 46a), 16-QAM (도 46b), 및 64-QAM (도 46b)인 경우, 균등화된 출력의 전력의 히스토그램이다.

도 47은 균등화기 출력 및 반송파 위상/주파수 복구 루프 모듈 입력에서의 성좌도의 예이다.

도 48은 도시된 임계값으로의 QAM 정합의 예를 나타낸다.

도 49는 동일한 플롯상에서 중첩된 모든 세 개의 성좌도의 일사분면을 나타낸다.

도 50은 성좌도를 결정하는 일 접근의 동작을 나타낸다.

도 51a 및 도 51b는 신호의 중단 또는 탭을 가지며, 본 발명의 특정 양태에 따른 표준 및 고화질 비디오의 동시 전송에 위한 시스템을 나타낸다.

도 52a 및 도 52b는 본 발명의 특정 양태에 따라 노이즈 신호로부터 프레임 동기화 펄스를 생성하는 프로세스를 나타낸다.

도 53은 본 발명의 특정 양태에 따라 Coax 접속 지시자를 갖는 카메라측 모뎀의 블록도이다.

도 54는 자동 이득 제어 루프의 특정 양태를 나타낸다.1 illustrates a conventional system using Coax to deliver standard analog video.

2 is a conventional approach to transmitting high quality digital video.

3 illustrates a system for the transmission of analog and digital video in accordance with certain aspects of the present invention.

4 illustrates a network for the transmission of analog and digital video in accordance with certain aspects of the present invention.

5 illustrates bandwidth allocation for transmission of analog and digital video over coaxial cable in accordance with certain aspects of the present invention.

6 shows an example of CCTV equipment built in accordance with certain aspects of the present invention.

7 shows an example of a modem used in DVR equipment constructed in accordance with certain aspects of the present invention.

8 illustrates an example of a modem used in network switch equipment constructed in accordance with certain aspects of the present invention.

9 is an example of a frame structure used in an ATSC digital television.

10 is an example of a conventional frame synchronization packet.

11 is an example of a data segment of a conventional data frame.

12 provides a simplified diagram of a frame arrangement.

13 is a block diagram of a modulator in accordance with certain aspects of the present invention.

14 is a block diagram of a frame structure used in a particular embodiment of the present invention.

15 illustrates the operation of the convolutional byte interleaver in certain embodiments of the present invention.

16 is a block diagram of an optional code rate punctured lattice coded modulation used in a particular embodiment of the present invention.

17 shows an example of QAM matching.

18 shows a frame synchronization / mode packet.

19 is a simplified frame structure used in certain embodiments of the present invention.

20 is a block diagram of a demodulator in accordance with certain aspects of the present invention.

21 is a block diagram of a camera side modem in accordance with certain aspects of the present invention.

22 is a block diagram of a monitor side modem in accordance with certain aspects of the present invention.

23 illustrates a QAM modulator from baseband to passband on the camera side in accordance with certain aspects of the present invention.

24A and 24B illustrate a QAM demodulator from baseband to passband on the monitor side in accordance with certain aspects of the present invention.

25 illustrates a monitor side digital equalizer and a carrier phase / frequency loop in accordance with certain aspects of the present invention.

Figure 26 shows that attenuation is represented as a function of frequency in a coaxial cable.

27A shows the power spectral density (PSD) of the equalizer input.

27B shows the amplitude response of the converged equalizer taps.

28A, 28B, 29A, and 29B show the loss versus slope of a passband digital video signal at different frequencies.

30 illustrates a monitor side modem having a digital equalizer inside a QAM demodulator in accordance with certain aspects of the present invention.

31 illustrates an analog active filter suitable for equalizing baseband CVBS in accordance with certain aspects of the present invention.

32 shows an example of a filter response in a particular embodiment of the present invention.

33A and 33B are QPSK constellations showing rotation in the complex plane.

34 is a block diagram illustrating a phase correction process according to a particular aspect of the present invention.

35 illustrates an integral-proportional (“IP”) filter in accordance with certain embodiments of the present invention.

36 shows transmitted symbols.

37A, 37B, 37C, and 37D show possible recovered symbols based on the transmitted symbols of FIG. 36.

38 shows the phase shift in the received symbol.

39 shows an example of a constellation diagram transmitted based on the conventional real and imaginary parts of the frame synchronization symbol.

40 is a block diagram of a phase offset corrector used in accordance with certain aspects of the present invention.

41 shows a process for determining reliability associated with frame synchronization.

42 illustrates certain aspects of the equalizer and carrier phase / frequency loops used in certain embodiments of the present invention.

Figure 43 illustrates a phase error detection module and slicer used in certain embodiments of the present invention.

Figure 44 illustrates a multiple exponential LUT module used in certain embodiments of the present invention.

45A and 45B show the real part of the equalized output of QPSK signal (FIG. 45A) and 16-QAM signal (FIG. 45B).

46A, 46B, and 46C show QPSK (FIG. 46A), 16-QAM (FIG. 46B), and 64-QAM (FIG. 46B) generated using one embodiment where the constellation is equalized at R = 58. Is a histogram of the power of the equalized output.

47 is an example constellation diagram at the equalizer output and the carrier phase / frequency recovery loop module input.

48 shows an example of QAM matching to the threshold shown.

49 shows one quadrant of all three constellation diagrams superimposed on the same plot.

50 illustrates the operation of one approach to determining constellation degrees.

51A and 51B illustrate a system for simultaneous transmission of standard and high definition video, with a break or tap of a signal, in accordance with certain aspects of the present invention.

52A and 52B illustrate a process of generating frame synchronization pulses from a noise signal in accordance with certain aspects of the present invention.

53 is a block diagram of a camera side modem having a coax connection indicator in accordance with certain aspects of the present invention.

54 illustrates certain aspects of an automatic gain control loop.

본 발명의 실시예들이 당업자가 본 발명을 실시할 수 있게 하는 설명적인 예로서 제공된 도면을 참조하여 상세히 설명될 것이다. 특히, 이하의 도면 및 예들은 본 발명의 범위를 단일의 실시예로 제한하도록 의도되지 않으며, 다른 실시예들이 설명되거나 도시된 구성요소 중 일부 또는 전부를 교환함에 의해 가능하다. 어디서든 편리하게, 동일한 참조 번호는 동면을 통해 동일하거나 유사한 부분을 지칭하도록 사용될 것이다. 이들 실시예의 특정 구성요소가 공지된 구성요소를 사용하여 부분적으로 또는 전체적으로 구현되는 경우, 이러한 공지된 구성요소 중 본 발명의 이해를 위해 필요한 부분만이 설명될 것이며, 이러한 공지된 구성요소의 다른 부분의 상세한 설명은 본 발명을 모호하게 하지 않도록 생략될 것이다. 상세한 설명에서, 단일의 구성요소를 나타내는 실시예는 제한하도록 의도되지 않으며, 본 발명은 여기서 명백히 다르게 언급되지 않는 이상 복수의 동일한 구성요소를 포함하거나 그 역인 다른 실시예를 포함하도록 의도된다. 또한, 출원인은 상세한 설명 또는 특허청구범위에서의 임의의 단어가, 일반적이지 않거나 특정한 의미로 명백히 명시되지 않는 그와 같은 의미가 되는 것을 의도하지 않는다. 또한, 본 발명은 설명에 의해 여기서 지칭된 구성요소에 대한 현재 및 미래의 균등물을 포함하지 않는다. Embodiments of the present invention will be described in detail with reference to the drawings provided as illustrative examples to enable those skilled in the art to practice the present invention. In particular, the following figures and examples are not intended to limit the scope of the invention to a single embodiment, but other embodiments are possible by exchanging some or all of the described or illustrated components. Wherever convenient, the same reference numerals will be used to refer to the same or similar parts throughout the hibernation. Where specific components of these embodiments are implemented, in part or in whole, using known components, only those portions necessary for the understanding of the present invention will be described, and other portions of such known components. The detailed description will be omitted so as not to obscure the present invention. In the detailed description, embodiments that represent a single component are not intended to be limiting, and the invention is intended to include other embodiments that include a plurality of identical components or vice versa, unless expressly stated otherwise herein. Furthermore, Applicants do not intend any word in the description or claims to be such meaning that is not generic or expressly stated in a particular sense. In addition, the present invention does not include present and future equivalents to the components referred to herein by description.

본 발명의 특정 실시예는 카메라가 Coax를 통해 표준 아날로그 비디오 및 고화질 디지털 비디오를 동시에 전송하게 하는 시스템 및 방법을 제공한다. 고화질 카메라는 디지털 비디오 신호 및 아날로그 기저대역 신호를 생성하는데 적용된다. 디지털 신호는 변조되어 기저대역 비디오 신호의 상위 주파수와 분리된 주파수 대역으로 전송된다. 아날로그 신호는 PAL, SECAM, 및 NTSC 표준 및 이들의 변경물을 포함하는 임의의 표준에 따라 인코딩될 수도 있다.Certain embodiments of the present invention provide a system and method for allowing a camera to simultaneously transmit standard analog video and high definition digital video over coax. High definition cameras are applied to generate digital video signals and analog baseband signals. The digital signal is modulated and transmitted in a frequency band separate from the higher frequencies of the baseband video signal. Analog signals may be encoded according to any standard, including the PAL, SECAM, and NTSC standards and variations thereof.

상세한 설명의 목적을 위해, coax를 통한 보안 링크 ("SLOC")를 사용하는 시스템의 예가 설명될 것이다. SLOC는 일반적으로 카메라에 대해 업스트림 및 다운스트림 신호를 갖는 것으로 설명되며, 카메라는 업스트림에 배치된다. 상세한 설명에서, SLOC 시스템의 예는, 제 1 통과대역의 다운스트림 고화질 ("HD"), 제 2 통과대역의 업스트림 및 제어 신호, 및 다운스트림 CVBS를 제공한다. 다른 대역통과 신호 및 대역폭의 할당이 사용될 수도 있다. 예를 들어, 시스템은 표준 또는 고화질 해상도의 2개의 디지털 비디오 신호를 사용할 수도 있다.For purposes of detailed description, an example of a system using a secure link ("SLOC") over coax will be described. SLOC is generally described as having upstream and downstream signals to the camera, with the camera being placed upstream. In the detailed description, examples of SLOC systems provide downstream high definition (“HD”) of the first passband, upstream and control signals of the second passband, and downstream CVBS. Other bandpass signals and bandwidth allocations may be used. For example, the system may use two digital video signals of standard or high definition resolution.

도 3은 본 발명의 특정 동작 이론을 설명하는 본 발명의 실시예를 나타낸다. 이 예는 DVR (32)에서 고화질의 비디오 복사를 기록하면서 카메라 (30)에 의해 생성된 라이브 비디오를 보는 것이 바람직한 시스템의 HD 카메라 (30)의 사용을 나타낸다. 이러한 시스템의 예는 보안 또는 감시 시스템이다. HD 카메라 (30)의 기능은 이하 설명될 바와 같이 원격으로 제어될 수도 있다. HD 카메라 (30)는 고화질 신호 (332) 및 아날로그 CVBS 신호 (330)를 동시에 생성하도록 적용될 수 있다. 특정 실시예에서, 고화질 신호 (332) 및 아날로그 CVBS 신호 (330)는 등시성이지만, 상이한 신호를 처리하는데 있어서 지연이 동일하지 않는 경우 실질적으로 등시성일 수도 있다. 일 예에서, CVBS 신호 (330)는 디지털-아날로그 변환 오버헤드로 인해 지연될 수도 있다. 또 다른 예에서, 고화질 신호 (332)는 압출될 수도 있으며, 압축 비율에 기반한 가능한 지연의 대상이 된다. 특정 실시예에서, CVBS (330) 및 고화질 신호 (332)는 카메라 (30)에 의해 생성된 보통 오디오 신호와의 일정 시간 관계에 있어서 유지되거나 동기화될 수도 있다.3 illustrates an embodiment of the present invention illustrating a particular theory of operation of the present invention. This example illustrates the use of

카메라 (30)는 이부 컴포넌트를 부가하거나 하드웨어 및 소프트웨어를 카메라 (30)에 집적함으로써 적용될 수도 있다. 예를 들어, coax을 통한 보안 링크 모뎀 ("SLOC-T") (31)이 카메라 내부에 제공된다. SLOC-T (31)은 카메라 (30)에 부가물로서 집적된 모뎀으로서 구축되거나 카메라 (30)에 이미 집적된 컴포넌트를 사용하여 구현될 수 있다. SLOC-T (31)는 멀티미디어 공급이 도시된 바와 같이 통신을 통해 전송 다운스트림이 되게 하며, SLOC-T (31)은 카메라 (30)에 의해 생성된 비디오를 나타내는 상이한 해상도 신호를 전달하는 복수의 신호가 동축 케이블 (330을 통해 전송되게 하는 디바이스이다. 설명의 명백함을 위해, 카메라 (30)와 같은 전송 디바이스에서 사용된 SLOC는 여기서 "SLOC-T"로서 지칭될 것이며, DVR, 네트워크와 같은 수신 디바이스에서 제공된 SLOC는 "SLOC-R"로서 지칭될 것이다. SLOC-T 및 SLOC-R의 설명은 이하 더욱 상세히 설명된다.

SLOC-T (31)은 카메라 (30)의 컴포넌트들과 협력할 수도 있으며, 및/또는 카메라 (30)가 다양한 모드에서 동작하게하는 향상된 기능을 부가할 수도 있다. 일 실시예에서, 카메라 (30)는 비압축 HD 디지털 비디오 출력을 생성할 수도 있으며, SLOC-T (31)는 HD 디지털 비디오 신호를 압축하는 능력을 제공할 수도 있다. 그 결과, SLOC-T (31)는 필요에 따라 호스트 카메라 (30)의 기능성을 향상시키기 위해 변조 및 복조 이상의 성능을 제공할 수도 있다. 따라서, 몇몇 SLOC-T 디바이스는 다양한 모드에서 동작할 수 있으며, 그 중 일부가 예시적인 방법으로 제공된다. 일 모드에서, SLOC-T (31)은 카메라로부터 표준 아날로그 신호 버전 및 HD 압축된 비디오 신호를 수신하여, 이 둘의 신호를 coax (33)을 통해 전송한다. 또 다른 예에서, SLOC-T (31)는 카메라 (30)로부터 표준 아날로그 신호 버전 및 비압축 HD 비디오 신호를 수신하여, coax (33)을 통해 표준 아날로그 신호와 함께 압축된 HD 디지털 신호 버전을 전송한다. SLOC-T (31)는 카메라 (30)로부터 수신된 HD 신호로부터 추출된 표준 아날로그 신호 및 HD 디지털 신호를 전송한다.The SLOC-

특정 실시예에서, SLOC-T (31)는 주파수 분할 다중화를 사용하여, Coax (33)상의 전송을 위한 출력 신호를 생성한다. 도 5에서 도시된 예에서, 다운스트림 디지털 신호는 주파수 f Cd 의 반송파 (53)에 중앙이 위치한 주파수 (52)의 신호 대역에 제공된다. 주파수 (52)의 대역은 기저대역 아날로그 신호 (50)의 최고 주파수 f0보다 위에서 시작한다. 이 구분된 주파수 (52)의 대역은 채널로서 지칭될 수 있다. 채널 (52)은 SLOC-T (31)의 용량, 사용가능한 대역폭, 신호 대역폭 및 다른 이유에 기반하여 선택될 수도 있다. 일부 실시예에서, 채널 (52)는 수신 장비와의 호환성을 위해 선택될 수도 있다. 일 예에서, 신호는 표준 텔레비전에 직접 제공될 수도 있으며, 채널 (52)은 기저대역 신호로부터의 적당한 이격을 보장하기 위해 선택될 수도 있다. 채널 (52)의 주파수 대역은, 신호의 표준 규정 인코딩이 사용되는 경우, 디지털 비디오 전송에 대한 표준에 기반하여 선택될 수도 있다. 디지털 신호의 일부를 전달하기 위해, 단일의 디지털 신호가 2개 이상의 상이한 채널을 사용하여 전송될 수도 있음이 고려된다.In a particular embodiment, SLOC-

임의의 적당한 변조 방식이 전송가능한 디지털 신호의 버전을 생성하는데 사용될 수도 있다. 예를 들어, 상이한 유형의 유선 및 무선 접속이, 위상 편이 방식 (PSK; phase shift keying), 주파수 편이 방식 (FSK: frequency shift keying), 직교 진폭 변조 (QAM; quadrature amplitude modulation), 직교 주파수 분할 다중 (OFDM; orthogonal frequency division multiplexing) 등과 같은 변조 방식과 함께 사용될 수도 있다. 통상적으로 변조 방식은 전송에 사용된 매체, 원하는 비디오 신호의 프레임 레이트의 특성을 포함하는 요소, 및 채널 (52)의 사용가능한 대역폭에 영향을 주는 다른 요소에 기반하여 선택된다. Any suitable modulation scheme may be used to generate a version of the transmittable digital signal. For example, different types of wired and wireless connections may include phase shift keying (PSK), frequency shift keying (FSK), quadrature amplitude modulation (QAM), orthogonal frequency division multiplexing. It may be used with a modulation scheme such as orthogonal frequency division multiplexing (OFDM). The modulation scheme is typically selected based on the medium used for transmission, the factors including the characteristics of the frame rate of the desired video signal, and other factors affecting the available bandwidth of the

SLOC-R 모뎀 (35)은 DVR (32)와 같은 비디오 캡처 디바이스에 제공될 수도 있다. SLOC-R 모뎀 (35)은 디지털 비디오 및 CVBS 신호를 수신할 수도 있다. 통상적으로, CVBS 신호는 추출되어 카메라 (30)에 의해 캡처된 비디오 이미지의 라이브 시야를 위해 디스플레이 시스템 (33)에 직접 전달된다. 디스플레이 시스템 (33)은 수신된 아날로그 신호의 디지털화된 버전을 수신할 수도 있을지라도, 표준 모니터가 될 수도 있다. 일 실시예에서, SLOC-R 모뎀 (35)은 디지털 모니터 및 적당히 장착된 컴퓨터와의 사용을 위해 아날로그 신호의 디지털화된 버전을 생성할 수도 있다. 기저대역 신호는 아날로그 컴포넌트를 사용하거나 디지털 신호 처리 기술을 통해 구현될 수 있는 로우 패스 필터를 사용하여 영향받을 수 있다. 디지털 HD 신호는 개별적으로 추출되어 DVR (32)의 기록 부분에 제공될 수도 있다. 특정 실시예에서, 디지털 HD 비디오 신호는 기록 이전에 DVR에 압축될 수도 있다. 다수의 실시예에서, 디지털 HD 비디오 신호는 압축된 디지털 신호로서 수신된다.SLOC-

특정 실시예에서, SLOC-T (31) 및 SLOC-R (35)는 신호의 양방향 통신을 지원하도록 구성된다. 보안 설치의 예에서, 그리고 도 6을 참조하여 이하 상세히 설명될 바와 같이, 카메라 (30)는 마이크로폰 (614), 확성기 (612), 센서 (616), 전기기계적 작동기를 제어하는 제어 인터페이스 (618), 및 다른 특징들을 포함할 수도 있다 (도 6참조). 이 예에서, 통상적으로 SLOC-T (31) 및 SLOC-R (35)는 카메라 (30)에 제어, 오디오 및 다른 데이터 (36)를 통신하도록 구성된다.In a particular embodiment, the SLOC-

다시 도 5를 참조하면, 일 실시예에서, 업스트림 데이터는 이용가능한 대역폭의 상부 종단에 설치된 하나 이상의 채널 (54)에서 카메라에 통신될 수 있다. 디지털 멀티미디어 신호 (52)의 통신을 위한 채널 서택, 제어 및 오디오 신호 (54) 및 다른 데이터는 이용가능한 대역폭, 채널 (52 및 54)에서 검출된 신호 대 잡음비, 신호 표준 및/또는 애플리케이션 특정 조건에 기반하여 선택될 수 있다. 몇몇 실시예에서, 채널 구성, 대역폭 및 신호 대 잡음비는 연습 시퀀스 (training sequence)를 사용하여 SLOC-T (31) 및 SLOC-R (35)의 접속시 결정된다. 통상적으로, 연습 시퀀스는 미리 결정되거나 협상된 채널의 신호 용량을 확인하고, 디지털 비디오의 전송을 위한 채널 (52)을 선택하며, 선택된 채널 (52)에서 이용가능한 대역폭을 결정하는데 사용된다. 선택된 채널 (52)의 특성은 디지털 비디오 신호에 대한 압축 레벨을 설정하는데 사용될 수도 있다. Referring again to FIG. 5, in one embodiment, upstream data may be communicated to the camera in one or

특정 실시예에서, 업스트림 신호 (54)는 다운스트림 (52) 및 기저대역 (50) 신호의 중앙을 제어할 수 있는 신호를 포함한다. 예를 들어, 카메라 광학 (600)은 카메라 (60)에 의해 모니터링된 어안 (fish-eye) 시야를 제공할 수도 있으며, 카메라 프로세서는 기저대역 신호 (50)로서 전송을 위한 이미지의 부분을 선택하도록 제어될 수도 있다. 통상적으로, 다운스트림 디지털 신호 (52)는 DVR상에 기록하거나 부가 처리를 위한 완전한 이미지를 제공할 수 있다. 기저대역 신호 (50)는 감시하의 영역의 라이브 모니터링을 위한 기저대역 신호 (50)를 수신한다. 기저대역 신호 (50)는 어안 렌즈에 의해 생성된 시각 효과를 보정하는 조정된 이미지를 포함할 수도 있다. 기저대역 신호 (50)의 보는 사람은, 시야를 위해 캡처된 이미지의 새로운 부분을 선택함으로써 어안 렌즈의 시야 내에서 시야를 이동시킬 수도 있다. 예를 들어, 보는 사람은 "팬-우측 (pan-right)"을 요청하여, 시야를 우측으로 이동시킬 수도 있다. 업스트림 신호 (54)에서 전송된 데이터는 카메라가 프로세서가 시야 중 원하는 부분을 추출하여 처리하게 한다. 특정 실시예에서, 기저대역 신호 (50)에 포함된 시야 이동 요청은 카메라 (60)의 물리적 이동을 유발할 수도 있다. 그 결과, 업스트림 신호 (54)의 제어 데이터는 기저대역 (50) 및 다운스트림 디지털 (52) 신호 모두의 콘텐츠에 영향을 줄 수도 있다.In a particular embodiment, the

특정 실시예에서, 다운스트림 오디오는 HD 디지털 비디오 신호의 일부 및/또는 CVBS 신호의 일부로서 전송될 수 있다. 몇몇 다운스트림 신호는 개별 전용 채널 (미도시)에서 전달될 수도 있다. 특정 실시예에서, 카메라 (30)에 대한 업스트림 통신은 예를 들어, 유선 또는 무선 네트워크를 포함하는 통신 방법을 벗어나 취급될 수도 있다. 특정 실시예가 대안 또는 부가적인 옵션으로서 다운스트림 디지털 신호 (52)를 무선으로 전송할 수도 있다. 그 결과, 기저대역 신호 (50)는 Coax를 통해 전송될 수 있으며, 업스트림 (54)과 다운스트림 (52)의 몇몇 결합은 무선으로 전송된다. 통상적으로, 업스트림 데이터 (54)는 전송방법에 무관하게 다운스트림 (52) 및 기저대역 (50) 신호에 대한 제어 신호를 포함한다. In certain embodiments, the downstream audio may be transmitted as part of the HD digital video signal and / or as part of the CVBS signal. Some downstream signals may be carried in separate dedicated channels (not shown). In certain embodiments, upstream communication to

특정 실시예에서, 케이블 (33)은 아날로그 표준 비디오의 디스플레이를 위해 디스플레이 시스템 (33)에 직접 제공될 수도 있다. 통상적으로, 표준 모니터 또는 디스플레이 (33)는 기저대역 신호와 표준 변조된 TV 채널 사이에서 선택을 가능하게 하는 필터 회로를 포함한다. 결국, 모니터 (330는 고주파수 디지털 인코딩된 반송파 신호를 폐기할 수도 있다. 또한, DVR (32)는, 디지털 비디오 신호가 표준 채널에서 전송되며 표준 디지털 인코딩을 사용하는 경우, 부가 처리없이 디지털 비디오 신호를 수신할 수 있다. SLOC-R (35)는 SLOC-T (31)에 의해 생성된 신호를 디코딩하여 DVR (32)에 디코딩된 HD 디지털 비디오 및 다른 신호를 제공한다. 또한, SLOC-R (35)은 카메라 (30)으로의 전송을 위한 제어, 오디오 및 다른 데이터를 인코딩할 수도 있다.In a particular embodiment, the

도 4를 참조하면, 본 발명의 특정 동작 원리를 나타내는 본 발명의 실시예가 제공된다. 도 4는 네트워크 스위치 (44)를 통해 네트워크상에서 비디오의 고화질 복사본을 동시에 제공하면서, 카메라 (40)에 의해 생성된 라이브 비디오를 보는 것이 바람직한 시스템에 기반한 예를 도시한다. 일 예에서, HD 비디오 공급은 내부 또는 외부 IP 비디오 서버를 사용하여 캡처되거나 스트리밍된다. 통상적으로 카메라 (40)는 고화질 신호 및 아날로그 기저대역 비디오 신호를 동시에 생성하도록 적용된다. 카메라 (40)는 외부 컴포넌트를 부가하거나 SLOC-T (400)와 같은 하드웨어 소프트웨어를 카메라 (40)에 집적함으로써 적용될 수도 있다. SLOC-T (400)은 도 3에서 특징된 SLOC-R (31)과 같은 방법으로 동작할 수도 있다. 그러나, SLOC-T (400)은 네트워크를 통한 디지털 비디오 신호의 포워딩을 용이하게 하는 방법으로 디지털 비디오 신호를 인코딩하도록 구성될 수도 있다. 예를 들어, SLOC-T (400)은 프로그래밍되거나, 그렇지 않은 경우 IP 비디오 서버에 의해 지원된 스트리밍 포맷에 따라 디지털 비디오 신호를 제공하도록 구성될 수도 있다.With reference to FIG. 4, an embodiment of the present invention is provided that illustrates a particular operating principle of the present invention. 4 shows an example based on a system where it is desirable to view live video generated by

카메라 (40)에 의해 전송된 다중화된 비디오 신호는 SLOC-R (440)이 옵션적으로 장착된 네트워크 스위치 (44)에 의해 수신될 수도 있다. 기저대역 표준 아날로그 신호가 추출되어 디스플레이 (43)에 제공될 수 있다. 특정 실시예에서, SLOC-R (440)은 디지털 고화질 비디오 신호를 추출하여 비디오 서버 또는 디지털 비디오 신호를 전달하는데 충분한 대역폭을 갖는 적당한 네트워크를 사용하는 다른 네트워크 디바이스에 포워딩할 수도 있다. 디지털 HD 비디오 신호는 압축된 HD 비디오 신호를 포함할 수도 있다. 특정 실시예에서, SLOC-R (440)에 의해 추출된 디지털 고화질 신호는 압축되거나 비디오 서버 또는 다른 네트워크 디바이스에 포워딩하기 위해 더 압축된다. SLOC-R (440)은 네트워크상의 전송을 위해 디지털 고화질 신호를 기록 및/또는 재변조하는 하드웨어 및 소프트웨어를 포함하며, 예를 들어, SLOC-R (440)은 이더넷을 통한 통신을 위해 인코딩된 H-264 신호를 생성할 수도 있다.The multiplexed video signal transmitted by

다시 도 6을 참조하면, 본 발명의 특정 실시예는 보안 시스템에 적용가능한 향상된 성능을 제공한다. 도시된 예에서, 카메라 (60)는 본 발명의 특정 양태에 따라 디지털 인코딩된 멀티미디어 신호를 제공하도록 구성되고 적용된 프로세서 및 모뎀 SLOC-T (606)를 포함한다. 순차 이미지는 당업자에게 공지된 CCD 센서 및 렌즈 시스템의 조합을 포함하는 이미지 센서 (602) 및 광학 (600)의 조합을 사용하여 캡처될 수 있다. 통상적으로 프로세서 (604)는 원하는 또는 미리 결정된 프레임 레이트에 따라 캡처된 순차 이미지를 제공하는 이미지 센서 (602)로부터 스캔 신호 (603)를 수신한다. Referring again to FIG. 6, certain embodiments of the present invention provide improved performance applicable to security systems. In the example shown,

몇몇 실시예에서, 이미지 센서 (602)는 하나 이상의 센서에 의해 캡쳐된 이미지를 나타내는 스캔된 아날로그 신호를 변환하여 디지털 비디오 신호를 생성할 수 있다. 예를 들어, 이미지 센서 (602)는 RGB (레드, 그린, 블루) 센서를 포함할 수도 있으며, 이미지 센서 (602)는 RGB 센서 출력을 내부적으로 처리하여 이미지 센서 (602)의 출력 (603)으로서 인코딩된 컬러 비디오 신호를 생성할 수도 있다. 다른 실시예에서, 프로세서 (604)는 이미지 센서 (602)로부터 신호 (603)를 미리 처리하여 미처리 (raw) 디지털 비디오 신호를 획득할 수도 있다. 미처리 디지털 비디오는, 내부적으로 획득되거나 이미지 센서 (602)로부터 수신되든, 프로세서 (604)에 의해 더 처리되어 초기 HD 디지털 비디오 신호를 획득할 수도 있다. 아날로그 표준 신호는 미처리 디지털 비디오 신호, 센서 (602)의 출력 (603), 또는 초기 HD 디지털 비디오 신호를 처리함으로써 획득될 수도 있다. 그 후, 프로세서 (604)는 초기 HD 디지털 비디오 신호를 포맷하여 방송 및 다른 표준에 부합하는 하나 이상의 HD 디지털 비디오 신호를 획득할 수도 있다. 예를 들어, 프로세서 (604)는 ATSC 및 DVB 표준과 같은 방송 비디오 표준에 부합하는 신호를 생성할 수도 있다. 프로세서 (604)는 디지털 비디오 신호를 추가로 압축할 수도 있다. In some embodiments,

카메라 프로세서 (604)는 상업적으로 이용가능한 컴포넌트 및 맞춤형 하드웨어 및 소프트웨어의 조합을 포함할 수도 있다. 일 예에서, 프로세서는 순차적인 단계, 명령 및/또는 프로그램을 수행하는 지원 로직 및 메모리와 결합하여, 하나 이상의 마이크로프로세서, 디지털 신호 프로세서, 마이크로제어기, 시퀀서 (sequencer) 및 다른 프로그램가능한 디바이스를 포함할 수도 있다. 저장부 (610)는 실생시 이 애플리케이션에서 설명한 기능 중 일부 또는 전부를 수행하는 컴퓨터 판독가능한 명령을 저장하는데 사용될 수도 있다. 카메라 프로세서 (604)는 본 발명의 특정 실시예의 구축을 위해 사용될 수 있는 몇몇 내장 또는 "하드 코딩된" 프로세스를 포함할 수도 있다. 또한, 저장부 (610)는 프로그램 스크래치 메모리에 대해, 및/또는 구성 정보를 유지하기 위해 사용될 수도 있다. 특정 실시예에서, 저장부 (610)는 카메라 (60)에 의해 캡처된 비디오의 기록을 저장하는데 사용될 수도 있다. 따라서, 저장부 (610)는 휘발성 및 비휘발성 메모리, 광학 및 자기 디스크, 착탈가능 전기적으로 삭제가능한 메모리, USB 메모리 드라이브 및 다른 반도체, 전자기 및 광학 저장 디바이스를 사용하여 구현될 수도 있다.The

신호 (605)는 프로세서 (604)에 의해 SLOC-T (606)로 제공된 비디오 신호, 및 SLOC-T (606)에 의해 프로세서 (604)로 포워딩된, 업스트림 제어, 오디오 및 라인 (62)으로부터 수신된 다른 업스트림 정보를 포함한다. 업스트림 오디오 정보는, 오디오 정보가 확성기, 변환기, 또는 다른 오디오 출력 시스템 (612)레 릴레이되기 이전에 프로세서 (604)에 의해 디코딩, 처리, 및/또는 포맷될 수도 있다. 프로세서는 오디오 신호를 증폭하거나 오디오 출력 컴포넌트 (612)에 별개의 증폭기를 사용할 수도 있다. 업스트림 제어는 통상적으로 제어 인터페이스 (618)를 통해 제공되는 외부 디바이스에 대한 제어 신호 및 광학 제어 (601)를 포함할 수도 있다. 외부 디바이스는 카메라 (60)를 해석, 회전 또는 지향하는데 사용되는 모터 또는 작동기를 포함할 수도 있다. 광학 제어 신호 (601) 및 외부 제어 신호 (618)는 원격 제어 시스템에 의해 미리 규정된 명령에 응답하여 생성될 수도 있다. 예를 들어, 원격 사용자는 조이스틱을 조정하여 카메라 (604)에 의해 "수평면에서 시계방향으로 90도 카메라를 회전하라" 는 의미로 해석되는 코딩된 일련의 명령을 생성하며, 프로세서 (604)는 카메라 (60)에 대해 수직으로 설치된 스탭핑 모터에 일련의 펄스를 전송함으로써 반응하며, 일련의 펄스는 카메라는 카메라의 수직축에 대해 원하는 회전을 유발할 수도 있다. 유사한 명령이 광학 (600)의 초점, 줌, 및 홍채를 조절할 수도 있다.The

또 다른 예에서, 명령 및 데이터가 프로세서 (604) 및/또는 센서 (602)의 기능을 제어하는데 사용될 수 있는 업스트림 제어 정보에 제공될 수도 있다. 명령 및 데이터는 업스트림 비디오 신호들 중 하나 이상에서의 인코딩을 위해 카메라 (60)의 시야 내의 영역을 선택하는데 사용될 수 있다. 특정 실시예에서, 명령 및 데이터는 인코딩될 시야의 부분을 지정하기 위해 원격으로 조정될 수 있는 하나 이상의 가상 카메라를 제공하여, 이에 의해 이 부분은 카메라 (60)의 광학에 의해 결정된 실제 시야 내에서 동작하는 가상 팬, 줌 및 기울기에 의해 선택된다. 특정 실시예에서, 프로세서 (604)는 카메라의 물리적 이동을 부가적으로 유발하여, 이에 의해 팬, 기울기, 및 줌 기능의 범위를 연장한다. In another example, instructions and data may be provided to upstream control information that may be used to control the functionality of

적어도 몇몇 실시예에서, CVBS 및 디지털 신호는 각각 이미지 센서 (602)에 의해 캡처된 이미지의 부분을 전달할 수도 있다. 이미지의 부분은 중첩되거나 렌즈 (600)에 의해 제공된 시야 내의 상이한 영역으로부터일 수도 있다. 또한, 특정 실시예에서, 추가적인 카메라 (60) 및/또는 추가적인 이미지 센서 (602)는 이용가능한 시야를 확장하는데 사용될 수도 있다. 예를 들어, 복수의 카메라를 구성하여 영역의 파노라마 (360°) 시야를 획득하는 것이 바람직할 수도 있다. 하나 이상의 프로세서 (604)는 시야 또는 시야의 부분을 나타내는 아날로그 및 디지털 신호를 제공할 수도 있다. 일 예에서, 완전한 파노라마 시야는 DVR 에 기록될 수도 있는 디지털 신호에 제공될 수도 있으며, CVBS 신호는 파노라마 내에 선택가능한 시야를 제공할 수도 있다. 선택가능한 시야는 줌, 팬, 및 다른 제어를 사용하여 제어될 수도 있다. 또 다른 예에서, CVBS 및 디지털 신호는 파노라마 시야의 공통되거나 상이한 부분을 제공할 수도 있으며, 이 부분은 원격 시청자에 의해 독립적으로 제어될 수도 있다. In at least some embodiments, the CVBS and digital signals may each carry a portion of an image captured by

도 7은 도 3에서 설명된 SLOC-R (35)와 유사하게, 보안 디지털 비디오 기록 시스템 (70)의 SLOC-R (700)의 사용의 예를 도시한다. 시스템 (70)은 SLOC-R (700), 주변 기기 (710, 712, 및 714)에 접속된 DVR 프로세서 (702), 아날로그 비디오 디코더 (704), 디지털 비디오 디코더 (708), 및 HD 디지털 디스플레이 프로세서 (706)을 포함한다. 전술한 바와 같이, SLOC-R (700)은 통상적으로 아날로그 표준 비디오 신호 및 HD 디지털 비디오 신호를 포함하는 Coax (72)로부터의 신호를 수신하여 디코딩한다. 또한, SLOC-R (700)은 Coax (72)를 통해 업스트림 오디오 및 제어 신호를 전송한다. 통상적으로 SLOC-R은 입력신호 (72)의 HD 디지털 비디오 신호로부터 아날로그 CVBS 신호를 분할하여, 프로세서 (702)에 디지털 비디오 신호를 제공하며, 도 6에 도시된 카메라 (60)로부터의 라이브 공급으로서 표준 모니터 (74)에 CVBS를 제공한다. SLOC-R (700)은 아날로그 비디오 디코더 (704)에 아날로그 기저대역 비디오 신호 (701)를 제공하며, 아날로그 비디오 디코더 (704)는 아날로그 기저대역 비디오 신호 (701)를 처리하여 디지털 표준 비디오 신호 (705)를 생성한다. 디스플레이 프로세서 (706)는 디지털 표준 신호 (705)와 저장된 HD 디지털 비디오의 재생으로부터 유도된 신호 (707) 사이에서 다중화 및/또는 선택한다. 디스플레이 프로세서는 선택된 신호를 HD 텔레비전 또는 모니터 (76)에 의해 디스플레이 가능한 포맷으로 제공한다. 7 shows an example of the use of the SLOC-

DVR 프로세서 (702)는 디지털 HD 비디오 신호 (703)를 수신하고 옵션적으로 카메라 (60)에 의해 캡처된 비디오의 기록으로서 신호의 적어도 일부를 저장한다. 기록은 하드 디스크 드라이브 (714), 네트워크 저장부 (미도시), 또는 네트워크 인터페이스 (710) 및/또는 USB/파이어와이어 또는 다른 로컬 버스 (712)를 통해 접속된 다른 광학 전자기적 또는 반도체 저장부에 저장될 수도 있다. 기록된 비디오는 더 압축되어 저장 공간을 세이브한다. DVR 프로세서는 기록된 비디오를 회수하며 디지털 비디오 디코더 (708)를 사용하여 재신 신호 (707)를 제공한다. The

도 8은 도 4에서 설명된 SLOC-R (440)와 유사하게, 네트워크된 보안 디바이스 (80)의 SLOC-R (800)의 사용의 예를 도시한다. 디바이스 (80)는 SLOC-R (800) 및 통상적으로 네트워크에 의해 IP 비디오 서버 (86)에 접속되는 네트워크 스위치 프로세서 (802)를 포함한다. 전술한 바와 같이, SLOC-R (800)은 통상적으로 아날로그 표준 비디오 신호 및 HD 디지털 비디오 신호를 포함하는 Coax (82)로부터의 신호를 수신하여 디코딩한다. SLOC-R (800)은 옵션적으로 Coax (82)를 통해 업스트림 오디오 및 제어 신호를 전송한다. 통상적으로 SLOC-R은 입력신호 (82)의 HD 디지털 비디오 신호로부터 아날로그 CVBS 신호를 분할하여, 프로세서 (802)에 디지털 비디오 신호를 제공하며, 도 6에 도시된 카메라 (60)로부터의 라이브 공급으로서 표준 모니터 (84)에 CVBS를 제공한다. 특정 실시예에서, SLOC-R (80)은 고화질 디스플레이 (85), 또한 도 6에 도시된 카메라 (60)로부터의 라이브 공급과 같은 디지털 디스플레이로의 사용을 위해 CVBS 신호 (801)를 디지털화하는 컴포넌트 (804, 806 등)를 포함한다. 그러나, 적당히 장착된 디스플레이 디바이스 또는 연산 디바이스가 CVBS 신호 (801)를 수신하여 신호의 디지털화를 수행할 수도 있다. 스위치 프로세서 (802)는 디지털 HD 비디오 신호 (803)를 수신하여 수신한 신호를 카메라 (60)에 의해 캡처된 비디오의 기록을 유지할 수 있는 네트워크 비디오 서버 (86)에 옵션적으로 전송한다. 디지털 HD 비디오 신호 (803)는 비디오 서버 (86)에 전송되지 이전에 더 압축될 수도 있다.FIG. 8 shows an example of the use of SLOC-

도 5 및 도 6을 참조하면, 본 발명의 특정 실시예는 원하는 바에 따라 선택되는 다운스트림 신호 (52) 및 기저대역 아날로그 신호 (50)의 콘텐츠를 허용한다. 일 예에서, 기저대역 신호 (50) 및 다운스트림 신호 (52)는 동일한 이미지를 포함하며, 전자는 아날로그 형태이며, 후자는 디지털적으로 인코딩된다. 디지털 이미지는 압축 및 비압축, 표준 및 고화질, 및 전체 프레임 또는 감소된 프레임 레이트로 옵션적이며 선택적으로 전송될 수 있다. 또 다른 예에서, 기저대역 신호 (50)는 이미지 센서 (602)에 의해 캡처된 전체 이미지 중 일부를 제공하며, 다운스트림 신호 (52)는 전체 이미지를 전달한다. 또 다른 예에서, 기저대역 신호 (50)는 이미지 센서에 의해 제공된 전체 이미지를 제공하며, 다운스트림은 전체 이미지 중 일부를 포함한다. 결과적으로, 고도로 구성될 수 있는 시스템은 디지털 카메라의 사용자가 비디오 이미지를 디스플레이, 기록, 및 전송에 대한 옵션의 넒은 범위로부터 선택하도록 허용한다.5 and 6, certain embodiments of the present invention allow the content of the

기저대역 신호에 대한 아날로그 균등화기Analog Equalizer for Baseband Signals

본 발명의 특정 실시예는 케이블 길이가 증가함에 따라 더욱 많이 주파수가 감소됨을 유발하는 케이블에서의 상당한 주파수 하강의 영향을 개선하는 시스템 및 방법을 포함한다. 케이블에 의해 유발된 이 기울기는 기저대역 아날로그 신호 및 통과대역 디지털 비디오 신호를 열화시키고, 열화는 케이블 길이가 증가함에 따라 악화된다. 본 발명의 특정 실시예는 통상적으로 디지털 수신기에 디지털 통과대역 신호상의 기울기를 제거하는 균등화기를 제공하여 전송된 심볼의 신뢰할 수 있는 디코딩을 인에이블한다.Certain embodiments of the present invention include systems and methods that improve the effect of significant frequency drop in a cable causing more frequency to decrease as the cable length increases. This slope caused by the cable degrades the baseband analog signal and the passband digital video signal, and the degradation worsens as the cable length increases. Certain embodiments of the present invention typically provide a digital receiver with an equalizer to remove the slope on the digital passband signal to enable reliable decoding of the transmitted symbols.

본 발명의 특정 실시예는, 전술한 시스템을 포함하여, 기저대역 비디오 신호가 기저대역 비디오 신호의 디지털 표현 및 제어 신호와 결합되는 시스템 및 장치의 성능을 개선하여, 이에 의해 동축 케이블 ("coax")과 같은 신호를 통한 전송을 인에이블한다. 도 3 및 도 4는 SLOC 시스템을 제공하는 실시예의 예를 도시하며, 도 5는 SLOC 시스템에 대한 하나의 가능한 변조 방식을 도시한다. 도 3의 예를 참조하면, HD 카메라 (30)는 압축된 디지털 HD 비디오 (332)를 포함하는 출력을 제공하며, 보조 카메라 출력 (330)은 아날로그 표준 ("SD") CVBS을 포함한다. 압축 비디오 신호 (332)는 기저대역 아날로그 CVBS 신호 (330)과 결합될 수 있는 변조된 신호를 제공하는 QAM 변조기를 포함하는 SLOC 카메라측 모뎀 (31)을 사용하여 통과대역 (52)으로 변조된다. 결합된 신호는 통상적으로 300m 이상 연장될 수 있는 거리에 대해 동축 케이블 (33)을 통해 전송된 다운스트림이다. 모니터 측에서, SLOC 모니터측 모뎀 (35)은 통과대역 다운스트림 비디오 신호 (332)의 신호 표현으로부터 기저대역 CVBS 신호를 나타내는 신호를 분리한다. CVBS의 신호 표현은 지연없는 라이브 보기를 위해 SD 디스플레이 (34)에 공급된다. 고 통과대역 다운스트림 신호는 모니터 (34)상의 라이브 (아마 약간 지연됨) HD 보기 및 나중의 보기를 위한 비실시간 HD 재생을 지원하는 호스트 프로세서 및 DVR (32)에 출력이 공급되는 QAM 복조기로 복조된다. Certain embodiments of the present invention, including the systems described above, improve the performance of systems and apparatus in which baseband video signals are combined with digital representations and control signals of baseband video signals, thereby improving coaxial cable ("coax"). Enable transmission over a signal such as 3 and 4 show examples of embodiments for providing a SLOC system, and FIG. 5 shows one possible modulation scheme for a SLOC system. Referring to the example of FIG. 3,

예를 들어, 업스트림 통신은, 예를 들어, IP 프로토콜에 따라 제공된다. 업스트림 통신은 모니터측으로부터 카메라 (30)로 오디오 및 카메라 제어 신호 (334)를 전송하는데 부가적으로 사용될 수도 있다. 통상적으로 업스트림 신호에 대한 비트 레이트 및 그 결과 요구된 대역폭은 다운스트림 통과대역 신호에 대해 요구되는 비트 레이트 및 그 결과 요구된 대역폭보다 상당히 낮다. 모니터측 SLOC 모뎀 (35)은 IP 신호를 업스트림 통과대역 (54)으로 변조하는 QAM 변조기를 포함한다. 도 5에 도시된 바와 같이, 업스트림 통과대역 (54) 및 다운스트림 통과대역 (52)은 상이한 스펙트럼 위치에 위치한다. 카메라측에서, SLOC 모뎀 (31)은 업스트림 신호를 수신하는 QAM 복조기를 포함한다. 이 접근은 종래의 시스템 및 방법보다 아래와 같은 몇몇 이점을 제공한다. For example, upstream communication is provided, for example, in accordance with the IP protocol. Upstream communication may additionally be used to send audio and camera control signals 334 from the monitor side to the

(1) 증가된 동작 범위 - 증가된 거리.(1) Increased operating range-increased distance.

(2) 현존하는 인프라구조를 사용하며 동축케이블을 재사용하여 사용될 수 있는 시스템.(2) A system that uses existing infrastructure and can be used by reusing coaxial cables.

(3) 저-지연, 실시간 (라이브) 비디오의 사용가능성(3) Availability of low-delay, real-time (live) video

(4) 라이브 CVBS 및 HD 비디오가 개별적인 위치에서 보일 수 있음.(4) Live CVBS and HD video can be viewed in separate locations.

도 21은 도 4의 SLOC 카메라측 모뎀 (49)의 부가적인 세부사항을 도시하는 간략도이다. HD 카메라 (2100)로의 IP 접속은 미디어 독립적인 인터페이스 ("MII") 모듈 (210)을 통해 QAM 변조기 (212) 및 QAM 복조기 (214)에 인터페이스된다. 일 예에서, MII (210)은 IEEE 802.3 표준에 부합한다. QAM 변조기 (212)는 기저대역 IP 데이터 스트림 (2100)을 통과대역 QAM 심볼 (2120)로 변환하는 공지된 이론을 사용하여 동작한다. 이들 심볼은 기저대역 CVBS 신호 (2160)와 합산되어 다이플렉서 (218)로 공급된다. 다이플렉서 (218)는 coax 에 결합된 기저대역 및 저 통과대역 다운스트림 신호 (2162)를 전달하며 coax로부터 고 통과대역 업스트림 신호 (2140)를 수신하여 이를 QAM 복조기 (214)에 공급하는 이원 (2-way) 아날로그 디바일 수 있다. 통상적으로 QAM 복조기 (214)는 모니터측으로부터 수신된 고 통과대역 업스트림 신호 (2140)를 복조하여 MII 인터페이스 (210)에 기저대역 데이터를 출력하는 공지된 이론을 사용하여 동작한다. 21 is a simplified diagram showing additional details of the SLOC camera side modem 49 of FIG. The IP connection to the

도 22는 도 4의 SLOC 모니터측 모뎀 (45)의 부가적인 세부사항을 나타내는 간략도이다. 다이플렉서 (220)는 동축 케이블로부터 다운스트림 결합된 기저대역 CVBS 및 저 통과대역 IP 신호 (2200)를 수신하여, 신호 (2200)를 로우 패스 (LP) 및 하이 패스 (HP) 필터링에 의해 컴포넌트 요소 (2201-2203)로 나눈다. CVBS 신호 (2201)는 표준 모니터 또는 디스플레이 디바이스로 직접 전송될 수도 있다. 저 통과대역 신호 (2202)는 MII 인터페이스 모듈 (226)에 공급하는 QAM 복조기 (222)에 공급될 수 있다. 또한 다이플렉서는 QAM 변조기 (224)로부터 고 통과대역 신호 (2203)를 수신할 수 있으며, 이 업스트림 신호를 동축 케이블에 전달할 수도 있다. 통상적으로 QAM 변조기 (222)는 IP 프로토콜을 지원하는 호스트/DVR 에 연결될 수 있는 MII 인터페이스 (226)로부터 입력을 얻는다. FIG. 22 is a simplified diagram showing additional details of the SLOC

통상적으로 동축 케이블은 케이블 길이가 증가함에 따라 더욱 많은 고 주파수 감쇄를 유발하는 상당한 고 주파수 롤 오프 (roll off) 특성을 나타낸다. 이러한 "기울기 (tilt)"는 통과 대역 신호의 대역 내에서 중요할 수 있으며, 기울기는 상당한 내부 심볼 간섭 ("ISI")을 유발할 수 있다. 디지털 균등화가 QAM 복조기 (222)가 전송된 데이터를 정확히 복구하게 하는데 필요할 수도 있다.Coaxial cables typically exhibit significant high frequency roll off characteristics that cause more high frequency attenuation as the cable length increases. This "tilt" may be important within the band of the passband signal, and the slope may cause significant internal symbol interference ("ISI"). Digital equalization may be necessary for

기저대역에서 At baseband 통과대역으로의To the passband 모듈 module

도 23은 카메라측 기저대역에서 통과대역으로의 QAM 변조기 (212) (도 21)를 더욱 상세히 도시한다. 예를 들어, 연관된 리스-솔로몬 코딩 (concatenated Reed-Solomon coding), 바이트 인터리빙, 및/또는 격자 코딩을 사용하여, MII (210)으로부터 수신된 데이터 스트림에 에어 방지 데이터를 부가하는 FEC 인코더/정합기에 의해 MII (210)으로부터 데이터가 수신된다. 정합기/인코더 (2300)는 데이터를 스트림 (2300 및 2302)으로 역다중화하며, 각각의 스트림에 대한 주어진 비트 그룹 사이즈는 실수 및 허수 방향에서 각각 QAM 심볼 진폭 레벨을 나타낸다. 고립 전송된 QAM 펄스는, FIG. 23 shows QAM modulator 212 (FIG. 21) from camera side baseband to passband in more detail. For example, an FEC encoder / matcher that adds air protection data to a data stream received from

에 의해 주어지며,Given by

여기서 dR ,m 및 dI ,m 은 2개의 독립적인 메시지 스트림에 의해 결정되며, 각각 복소 QAM 심볼의 실수부 및 허수부를 나타내고, m=1...M 은 기수 (cardinality) 2차원 QAM 성좌도를 인덱스하며, 여기서 M은 변조 반송파 주파수이며, q(t)는 루트 레이즈드 코사인 펄스 함수 (root raised cosine pulse function)이다.Where d R , m and d I , m are determined by two independent message streams, each representing a real part and an imaginary part of a complex QAM symbol, and m = 1 ... M is a cardinality two-dimensional QAM constellation plot. Where M is the modulation carrier frequency and q (t) is the root raised cosine pulse function.

연속적인 일련의 전송된 QAM 펄스 s(t)는 Fs=1/TS 의 레이트로 잡음 다중경로 채널을 통해 전달된다. 그 결과, QAM 수신기로의 입력에서의 수신 신호는 에 의해 주어지며, 여기서 *는 컨벌루션 (convolution)을 나타내며, c(t)는 채널 임펄스 응답이고, υ(t)는 부가적인 화이트 가우시안 잡음이다. 그 결과, A successive series of transmitted QAM pulses s (t) are propagated through the noise multipath channel at a rate of F s = 1 / T S. As a result, the received signal at the input to the QAM receiver Is denoted by convolution, c (t) is the channel impulse response, and υ (t) is the additional white Gaussian noise. As a result,

이며, 여기서, d[n]은 복소 전송된 심볼이고, f0 및 θ0 은 각각 fL0=fc-f0 가 되도록, 전송기에 관하여 수신기 통과대역에서 기저대역으로의 복조기 로컬 발진기 의 주파수 및 위상 오프셋이다. Where d [n] is a complex transmitted symbol, and f 0 and θ 0 are the frequency of the demodulator local oscillator from the receiver passband to the baseband with respect to the transmitter such that f L0 = f c -f 0 , respectively. Phase offset.

통과대역에서In the passband 기저대역으로의 복조기 Demodulator to baseband

도 24a는 모니터측 통고대역에서 기저대역으로의 QAM 복조기 (222) (도 22)를 더욱 상세히 도시한다. 신호 r(t)는 동축 케이블로부터 수신될 수도 있으며, 예를 들어, 심볼 레이트보다 높은 레이트로 샘플링되어 (240 참조) 샘플링된 신호 r(nTsamp)를 유발한다. 아래의 샐플링 이후:FIG. 24A shows QAM demodulator 222 (FIG. 22) in more detail from monitor side notification band to baseband. Signal r (t) may be received from a coaxial cable, for example, sampled at a rate higher than the symbol rate (see 240) resulting in a sampled signal r (nT samp ). After sampling below:

그 후, 다운변환, 심볼 레이트 1/Ts 에서의 리샘플링, 및 정합된 필터링 이후, After downconversion, resampling at

를 획득한다. 여기서 는 샘플링된 복소 필터링된 잡음이며, 완전한 심볼 레이트 샘플 타이밍과 결합된, 펄스 형상화 및 정합된 필터링 q 로 인해, 는 채널 임펄스 응답 c 만으로 인한 것임을 가정한다. Acquire it. here Is sampled complex filtered noise and, due to pulse shaping and matched filtering q, combined with full symbol rate sample timing, It is assumed that is due to the channel impulse response c only.

균등화기 및 반송파 위상/주파수 루프Equalizer and Carrier Phase / Frequency Loop

도 24a의 디지털 균등화기 및 반송파 위상/주파수 루프가 도 25를 참조하여 더욱 상세히 설명된다. 신호 x[k]는 채널 임펄스 응답 c에 의해 유발된 기울기를 보상하는데 사용되는 선형 디지털 필터를 포함할 수 있는 어댑티브 디지털 균등화기 (250)에 인가된다. 탭 가중 조정치가 LMS 알고리즘을 포함하는 하나 이상의 공지된 방법을 사용하여 획득될 수 있다. 균등화기는 자신의 출력 y[k]를 2차원 ("2-D") 슬라이서 결정 의 위상 회전 버전과 비교하여, 필터 탭 가중치의 업데이트된 세트를 계산하는데 사용되는 에러 신호를 생성한다. LMS 알고리즘은 아래아 같이 동작할 수도 있다.The digital equalizer and carrier phase / frequency loop of FIG. 24A are described in more detail with reference to FIG. 25. Signal x [k] is applied to adaptive

x[k]는 N 개의 긴 균등화기 입력 벡터를 나타내며,x [k] represents N long equalizer input vectors,

y[k]는 균등화기 출력 벡터 gH[k]x[k]를 나타낸다.y [k] denotes the equalizer output vector g H [k] x [k].

여기서, gH[k]는 N개의 긴 균등화기 탭 가중 벡터이며, 위첨자 H는 켤레 전치 (conjugate transposition) (헤르미이트)Where g H [k] is N long equalizer tap weighting vectors, and superscript H is conjugate transposition (hermitite)

여기서, μ은 작은 단계 사이즈의 파라미터이며, 위첨자 *는 켤레 복소수를 나타낸다.Where μ is a small step size parameter and superscript * denotes a conjugate complex number.

통과대역 케이블 기울기의 영향을 제거하기 위해, 변환 이후, LMS 균등화기 탭은 채널 임펄스 응답 c의 역에 근접한다.To eliminate the effects of passband cable slope, after conversion, the LMS equalizer tap is close to the inverse of the channel impulse response c.

2-D 슬라이서 (252)는 원래 전송된 d[k]의 추정치인 출력 및 z[k]의 실수부 및 허수부를 독립적으로 나눈다. 위상 에러 검출 모듈 (258)은 z[k] 및 을 수시ㄴ하여 위상 에러 신호 를 형성한다. 로우 패스 ("LP")필터 (256)은 루프가 위상 및 주파수 오프셋 모두를 정정하게 하는 적분 비례 필터일 수 있다. 로우 패스 필터 (256)의 출력은 θ0 및 f0 모두를 정정하는 복소 위상/주파수 정정 요소 를 출력하는 복소 이산 전압 제어된 발진기 ("VCO") (254)에 공급된다. 또한, VCO (254)은 슬라이스 출력 을 "비보정"하는 출력 을 제공하여, 균등화기 탭 업데이트를 위한 에러 신호를 도출하는데 사용될 수 있다. 이는 통상적으로 균등화기가 x[k] 상에서 동작하기 때문에 요구된다. 또한, 도 24a를 참조하면, 균등화기 출력 z[k]은 검출된 실수 및 허수 레벨을 비트 그룹으로 변환하는 심볼 역정합기에 공급된다. 그 후, 디코더는 비터비 (Viterbi) 디코딩, 바이트 역인터리빙, 및/또는 리드-솔로몬 디코딩을 실행하여, 수신된 비트 에러를 정정하며 결과적인 데이터를 MII 인터페이스에 전달한다. 2-

케이블 길이의 영향Influence of Cable Length

수신된 비디오 신호는 주파수의 함수가 케이블의 특정 특성에 기여함에 따라 감쇄를 경험할 수 있다. 이 논의 목적을 위해, 동축 케이블의 예가 설명된다. 기울기로 지칭되는 감쇄의 엄정함은 통상적으로 케이블 유형 및 길이에 의존한다. 도 26a 및 도 26b는 다양한 길이의 케이블 유형 RG6 및 RG59에대한 주파수 함수로서의 감쇄를 도시한다. 기울기는 다중경로 왜곡과 균등하며, 부가 경로 및 주요 경로는 극히 작은 지연 스프레드 (spread)를 가진다. 기울기가 증가함에 따라, 적지않은 다중경로 컴포넌트의 수, 및 이들 각각의 이득 또한 증가한다. 다중경로 왜곡은 수신된 신호에서의 를 유발하며, 그 결과, 전송 신뢰도를 상당히 악화시킬 수 있다. 디지털 신호에서, 균등화기는 이러한 장애를 제거하기 위해 수신기에서 사용될 수 있다. 도 27a 및 도 27b는 균등화기 입력의 전력 스펙트럼 밀도 (PSD) 및 수렴된 균등화기 탭의 응답을 각각 도시한다. 특히, 도 27a는 15.98MHz (통과대역 및 상대적인 기적대역 주파수 모두 도시)의 반송파 주파수로, RG-6 케이블의 2000ft를 통한 전송 이후 균등화기 입력의 PSD 를 도시하며, 도 27b는 수렴된 디지털 균등화기 탭의 진폭 응답을 도시한다. The received video signal may experience attenuation as a function of frequency contributes to certain characteristics of the cable. For the purposes of this discussion, examples of coaxial cables are described. The stringency of the attenuation, referred to as the slope, typically depends on the cable type and length. 26A and 26B show the attenuation as a function of frequency for cable types RG6 and RG59 of various lengths. The slope is equivalent to multipath distortion, with the additional path and the main path having an extremely small delay spread. As the slope increases, the number of many multipath components, and their respective gains, also increases. Multipath distortion can occur in the received signal And, as a result, can significantly degrade transmission reliability. In digital signals, the equalizer can be used at the receiver to eliminate this obstacle. 27A and 27B show the power spectral density (PSD) of the equalizer input and the response of the converged equalizer taps, respectively. In particular, FIG. 27A shows the PSD of the equalizer input after transmission over 2000 ft of the RG-6 cable, with a carrier frequency of 15.98 MHz (both the passband and relative miraculous band frequencies), and FIG. 27B shows the converged digital equalizer. The amplitude response of the tap is shown.

본 발명의 특정 실시예는 케이블에 의해 소개된 기울기를 언두 (undo) 할 수 있는 디지털 균등화기를 포함할 수 있어 통과대역 신호에서의 를 제거할 수 있으며, 전송된 데이터의 신뢰할 수 있는 디코딩을 가능케 한다. 케이블의 길이가 증가함에 따라, 모니터측에서 디지털 통과대역 신호는 디지털 균등화기, 또는 연관된 리스-솔로몬 코딩 및 격자 코딩과 같은 디지털 데이터에 대한 공지된 포워드 에러 방지 방법을 사용하여 신뢰성 있게 수신될 수 있다. 그러나, 케이블 기울기는 기저대역 아날로그 CVBS 신호의 고 주파수에 불리한 영향을 미쳐, 모니터측에서 보이는 컬러의 선명함 및 휘도를 감소시킨다. 따라서, 특정 실시예는 기저대역에서의 케이블 기울기를 보상하기 위해 모니터측에서의 CVBS 신호에 인가될 수 있는, 아날로그 균등화기와 같은 적용가능한 필터를 제공한다. 특정 실시예는 기저대역에서의 기울기 총량을 측정하기 위해 통과대역 디지털 균등화기를 사용하여, 수신된 CVBS 신호에 적용될 기저대역 아날로그 필터들 중 적당한 하나의 세트를 선택한다. Certain embodiments of the present invention may include a digital equalizer capable of undoing the slope introduced by the cable to provide a Can be eliminated, enabling reliable decoding of transmitted data. As the length of the cable increases, the digital passband signal at the monitor side can be reliably received using a digital equalizer or known forward error prevention methods for digital data such as associated Lis-Solomon coding and lattice coding. . However, the cable slope adversely affects the high frequency of the baseband analog CVBS signal, reducing the sharpness and brightness of the color seen on the monitor side. Thus, certain embodiments provide an applicable filter, such as an analog equalizer, that can be applied to the CVBS signal at the monitor side to compensate for cable slope at baseband. A particular embodiment uses a passband digital equalizer to measure the total amount of slope in the baseband to select a suitable set of baseband analog filters to be applied to the received CVBS signal.

통과대역Passband 기울기의 효율적인 측정 Efficient Measurement of Tilt

신호 대역에서 기울기를 측정함에 있어서, 입력 신호의 PSD 에서의 기울기가 dB 로 수량화되는 경우 대략 선형이 될 부분에서 주파수 대역이 선택될 수 있다. 따라서, 그 결과, 통과대역 입력 신호의 13.31MHz 및 18.65MHz에 대응하는 기저대역 디지털 균등화기 입력의 -2.67MHz 내지 2.67MHz의 주파수는 적당한 범위를 제공한다. 도 26a에 도시된 바와 같이, 13.31MHz 및 18.65MHz의 기울기는 RG-6의 2000피트 (feet)에 대해 대략 3.7dB 이다. 수렴된 디지털 균등화기 필터 탭으로부터 dB 의 기울기를 측정하기 위해, 다음의 계산이 수행될 수 있다. In measuring the slope in the signal band, a frequency band may be selected at a portion that will be approximately linear when the slope of the input signal in PSD is quantified in dB. As a result, the frequencies of -2.67 MHz to 2.67 MHz of the baseband digital equalizer inputs corresponding to 13.31 MHz and 18.65 MHz of the passband input signal provide a suitable range. As shown in FIG. 26A, the slopes of 13.31 MHz and 18.65 MHz are approximately 3.7 dB for 2000 feet of RG-6. To measure the slope of dB from the converged digital equalizer filter tap, the following calculation can be performed.

G[k]는 시간 도메인 수렴된 균등화기 필터 탭의 DFT이며, k1 및 k2 는 DFT의 특정 주파수 빈 (bin)에 대응한다. 도 25의 디지털 균등화기는 시간 도메인 컨벌루션으로 수행될 수도 있기 때문에, 통상적으로 FFT (또는 양 포인트에 N 개의 복소수를 곱하거나 더하는 것도 가능함)는 주어진 k1 및 k2에 대한 기울기를 측정할 목적으로 요구된다. 즉,G [k] is the DFT of the time domain converged equalizer filter tap, and k 1 and k 2 correspond to specific frequency bins of the DFT. Since the digital equalizer of FIG. 25 may be performed with time domain convolution, an FFT (or it is also possible to multiply or add N complex numbers to both points) is typically required for the purpose of measuring the slope for a given k1 and k2. In other words,

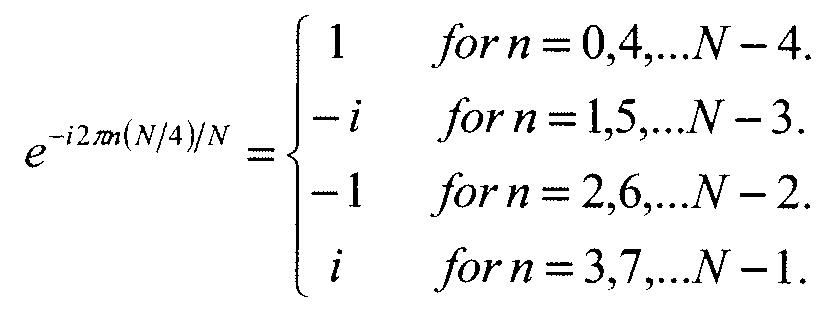

여기서, 이며, n=0, 1...N-1은 N 개의 시간 도메인 군등화기 탭이다 (시간 인덱스에 대한 의존성은 생략됨). 1/N 스칼라는 이 계산에서 불필요하다. 유사한 계산이 G(k2)에 대해 수행될 수도 있다. 그러나, 계산은 주파수 빈을 주의깊게 선택함으로써 상당히 감소될 수 있다. 2.67MHz의 주파수에 대응하여 K1=N/4 로 함으로써, 수학식 (2)의 복소 지수는 상당히 간단화된다.here, N = 0, 1 ... N-1 are N time domain equalizer taps (dependence on time index is omitted). 1 / N scalar is unnecessary in this calculation. Similar calculations may be performed for G (k 2 ). However, the calculation can be significantly reduced by carefully choosing the frequency bins. By making K 1 = N / 4 corresponding to the frequency of 2.67 MHz, the complex exponent of Equation (2) is considerably simplified.

필터 주파수 응답의 실수 및 허수부는 합산을 이용하여 계산될 수 있다. The real and imaginary parts of the filter frequency response can be calculated using summation.

최종적으로, 이 주파수 빈에서의 전력은:Finally, the power at this frequency bin is:

k1=N/4 로 허용함으로써, 전력 계산은 상당히 간단화된다. 유사하게, -2.67MHz의 주파수에 대응하여, K1=3N/4로 함으로서, 복소 지수는 다시 상당히 간단화될 것이다.By allowing k 1 = N / 4, the power calculation is greatly simplified. Similarly, by corresponding to the frequency of -2.67 MHz, by setting K 1 = 3N / 4, the complex index will again be considerably simplified.

실수부 및 허수부는:Real and imaginary parts:

와 같으며, 전력 는 상기와 같이 계산된다. 도 2b에서, 수렴된 필터 탭의 (dB 의) 진폭 응답의 상승 기울기는 탭 잡음 및 64-QAM 신호 대한 보통의 SNR까지 선형이다. 또한, 이러한 방법에서 계산시, 이며, 이는 이 3.7dB의 대역에 걸처 실제 기울기에 상당히 근접한다.Equals power Is calculated as above. In FIG. 2B, the rising slope of the amplitude response (of dB) of the converged filter tap is linear up to the tap noise and the normal SNR for the 64-QAM signal. In addition, when calculating in this way, This is quite close to the actual slope over this 3.7dB band.

기저대역 Baseband CVBSCVBS 기울기 보정을 위한 For tilt correction 통과대역Passband 기울기 추정치의 이용 Use of slope estimates

디지털 비디오 신호에 대한 통과대역 기울기를 추정한 이후, 적당한 기저대역 아날로그 필터가 M 개의 상이한 필터들 중 하나로부터 선택될 수도 있다. 디지털 비디오 신호 대역의 추정된 통과대역 기울기는 기저대역 CVBS 신호의 기울기의 강도 (severity)를 나타낼 것이며, 강도는 아날로그 필터로 대략 보정될 수 있다. 도 28a에서, 13.31MHz 및 18.65MHz의 디지털 비디오 신호 대역의 기울기는 RG-6, RG-11, RG-59, 및 RG-174 및 이들 케이블과 유사한 길이에 대해 도시된다. 도 28a는 RG-6, RG-11, RG-59, 및 RG-174 케이블 유형에 대한 통과대역 디지털 비디오 신호에서의 기울기 대 3.58MHz에서의 손실을 도시한다. 도 28b는 6MHz에서의 손실을 도시한다. 3.58MHz 및 6MHz에서의 손실은 주어진 기울기에 대해 4개의 케이블 유형에 대해 대략 동일하다. 도 29a는 RG-6, RG-11, RG-59, 및 RG-174 케이블 유형에 대한 통과대역 디지털 비디오 신호에서의 기울기 대 3.58MHz에서의 손실을 도시한다. 도 29b는 6MHz에서의 손실을 도시한다. 3.58MHz 및 6MHz에서의 손실은 주어진 기울기에 대해 4개의 케이블 유형에 대해 대략 동일함이 관측될 것이다.After estimating the passband slope for the digital video signal, a suitable baseband analog filter may be selected from one of M different filters. The estimated passband slope of the digital video signal band will represent the severity of the slope of the baseband CVBS signal, which can be approximately corrected with an analog filter. In FIG. 28A, the slopes of the digital video signal bands of 13.31 MHz and 18.65 MHz are shown for RG-6, RG-11, RG-59, and RG-174 and similar lengths with these cables. FIG. 28A shows the slope versus loss at 3.58 MHz in a passband digital video signal for RG-6, RG-11, RG-59, and RG-174 cable types. 28B shows the loss at 6 MHz. The losses at 3.58 MHz and 6 MHz are approximately the same for the four cable types for a given slope. 29A shows the slope versus loss at 3.58 MHz in a passband digital video signal for RG-6, RG-11, RG-59, and RG-174 cable types. 29B shows the loss at 6 MHz. It will be observed that the losses at 3.58 MHz and 6 MHz are approximately the same for the four cable types for a given slope.

추정된 통과대역 기울기가 케이블의 주파수 응답에 관한 유일한 이용가능한 정보이기 때문에, 이상적인 시나리오는, 기저대역 (CVBS 신호 대역)에서의 케이블의 주파수 응답이 케이블 유형 또는 길이에 관계없이 공지된 방법으로 통과대역 디지털 신호의 기울기에 관련된다는 것이다. 도 28b, 29a, 및 29b는 DC, 3.58MHz, 및 6MHz에서의 주파수 응답의 이러한 상황을 확인한다. 예를 들어, 통과대역 디지털 비디오 신호의 1.5dB 의 기울기에서, DC에서의 손실, 컬러 반송파 (3.58MHz)에서의 손실, 및 6MHz에서의 손실은 모든 4 개의 케이블에 대해 각각 대략 0.68dB, 4.1dB, 및 5.3dB이다. 그 결과, 통과대역 기울기의 1.5dB가 RG-174의 275ft., RG-59의 750ft., RG-9의 825ft., 또는 RG-11의 1825ft.로부터 유발되는지 여부에 관계없이, 동일한 아날로그 필터가 CVBS 신호의 기저대역 기울기를 언두할 수도 있다.Since the estimated passband slope is the only available information about the frequency response of the cable, the ideal scenario is that the frequency response of the cable in the baseband (CVBS signal band) is passband in a known manner regardless of cable type or length. Is related to the slope of the digital signal. 28B, 29A, and 29B confirm this situation of frequency response at DC, 3.58 MHz, and 6 MHz. For example, at a 1.5 dB slope of the passband digital video signal, the loss at DC, the loss at color carrier (3.58 MHz), and the loss at 6 MHz are approximately 0.68 dB and 4.1 dB for all four cables, respectively. , And 5.3 dB. As a result, regardless of whether 1.5 dB of passband slope is derived from 275 ft. Of RG-174, 750 ft. Of RG-59, 825 ft. Of RG-9, or 1825 ft. Of RG-11, the same analog filter The baseband slope of the CVBS signal may be undone.

M 개의 필터 세트로부터 적당한 아날로그 필터를 선택하는데 사용된 알고리즘의 일 예는 아래와 같다.An example of the algorithm used to select the appropriate analog filter from the M filter sets is shown below.

α0=1이고, αn의 다른 값은 1보다 작으며, 비트-이동된 부가 (bit-shifted addition)는 Rn을 계산하는데 충분하도록 선택된다. 따라서, 도 24a의 모니터측 QAM 복조기는 통상적으로 수정되어, 통과대역 QAM 복조기의 디지털 균등화기는 M개의 아날로그 CVBS 필터 응답 중 하나를 선택하는 신호를 제공한다. 도 24b는 전술한 알고리즘에 따라 동작하는 디지털 균등화기로부터의 아날로그 필터 선택 출력을 갖는 모니터측 QAM 복조기의 수정된 부분을 도시한다. 도 30은 CVBS 아날로그 균등화기 (302)에 필터 선택 신호 (305)를 제공하는 QAM 복조기 (304) 내의 디지털 균등화기를 갖는 전체 모니터측 모뎀을 도시한다. α 0 = 1, the other value of α n is less than 1, and the bit-shifted addition is chosen to be sufficient to calculate R n . Thus, the monitor-side QAM demodulator of FIG. 24A is typically modified such that the digital equalizer of the passband QAM demodulator provides a signal that selects one of the M analog CVBS filter responses. FIG. 24B shows a modified portion of the monitor side QAM demodulator with analog filter selection output from a digital equalizer operating according to the algorithm described above. 30 shows a full monitor side modem with a digital equalizer in

기저대역 CVBS 신호를 균등화하는데 적합한 아날로그 활성 필터의 예가 도 31에 도시된다. 이 예에서, M=3이여서, 4개의 가능한 필터링 선택이 존재한다. 바람직한 필터 응답은 스위치 모듈 (310)에 접속된 각각의 RC 쌍에 차례로 접지하는 스위치 모듈 (310)의 M+1 개의 스위치 중 하나를 닫음으로써 선택된다. 가능한 필터 응답은 도 32에 도시된다.An example of an analog active filter suitable for equalizing the baseband CVBS signal is shown in FIG. 31. In this example, M = 3, so there are four possible filtering choices. The preferred filter response is selected by closing one of the M + 1 switches of the

당업자는 본 발명이 다른 통과대역 변조를 사용하는 디지털 통신 시스템 및 포워드 에러 정정 방법에 적용됨을 이해할 것이다. 또한, 당업자는 통과대역 디지털 균등화기 탭 가중 벡터 g[n]의 FFT의 2개 이상의 포인트가 CVBS 신호에 대한 아날로그 필터를 선택하는데 사용될 수도 있으며, G1[k] 및 G2[k]의 값이 균등화 처리의 일부로서 이미 계산된 주파수 도메인 균등화기를 포함하여 통과대역 신호에 대한 다른 유형의 디지털 균등화기 설계가 사용될 수 있음을 인식할 것이다. 또한, RLS 와 같이, LMS 이외의 공지된 균등화기 탭 가중 계상 방법이 사용될 수도 있다.Those skilled in the art will appreciate that the present invention applies to digital communication systems and forward error correction methods that use other passband modulation. One skilled in the art can also use two or more points of the FFT of the passband digital equalizer tap weighting vector g [n] to select an analog filter for the CVBS signal, with values of G 1 [k] and G 2 [k]. It will be appreciated that as part of this equalization process, other types of digital equalizer designs for passband signals can be used, including frequency domain equalizers that have already been calculated. Also, such as RLS, known equalizer tap weighted phase imaging methods other than LMS may be used.

특정 실시예에서, 선택가능한 응답을 갖는 CVBS 아날로그 필터는 전술한 형태 이외의 형태를 취할 수도 있다. 또한, CVBS 신호에 대한 균등화기는 CVBS가 균등화 이전에 샘플링 및 디지털화되는 디지털 필터의 형태를 취할 수도 있다. 이 경우, 디지털 필터의 탭 가중치는 M 개의 아날로그 필터 응답 중 하나를 선택하기 위해 설명된 동일한 알고리즘에 따라 소정의 M개의 가중 벡터 세트로부터 선택된다.In certain embodiments, the CVBS analog filter with the selectable response may take a form other than the form described above. The equalizer for the CVBS signal may also take the form of a digital filter where the CVBS is sampled and digitized prior to equalization. In this case, the tap weight of the digital filter is selected from a predetermined set of M weighted vectors according to the same algorithm described for selecting one of the M analog filter responses.

디지털 통신 시스템에서의 In digital communication systems 프레임화Framing

통상적으로 디지털 데이터는 몇몇 종류의 프레임 구조를 가져서, 데이터는 균일한 크기의 비트 또는 바이트 그룹으로 조직화된다. 블록 기반 포워드 에러 정정 (FEC)을 사용하는 시스템은 에러 정정 코드 워드 사이즈 주변에서 조직화된 프레임을 가진다. 또한, 시스템이 임펄스 잡음과 싸우는 인터리빙을 사용하는 경우, 프레임 구조는 마음속의 인터리버 파라미터로 배열될 것이다. 시스템이 플랫 (flat) 스펙트럼을 획득하기 위해 데이터 랜덤화를 사용하는 경우, 사용된 의사-랜덤 시퀀스 (pseudo-random sequence)가 각각의 프레임의 시작에서 재시작하는 프레임 구조에 동기화될 수도 있다. Typically, digital data has some kind of frame structure, so that the data is organized into groups of bits or bytes of uniform size. Systems using block based forward error correction (FEC) have frames organized around the error correction code word size. Also, if the system uses interleaving to combat impulse noise, the frame structure will be arranged with interleaver parameters in mind. If the system uses data randomization to obtain a flat spectrum, the pseudo-random sequence used may be synchronized to the frame structure restarting at the beginning of each frame.

RF 디지털 통신 시스템에 대해, 통상적으로 수신기는 우선 반송파 및 심볼 플럭 동기화 및 균등화를 획득해야 한다. 그 후, 수신기는 전성된 데이터를 복구할 수 있다. 그러나 인가되는 데이터 스트림을 이해하기 위해서는, 수신기는 프레임 구조에 동기화하여야 한다. 즉, 수신기는 에러 정정 코드 워드가 어디서 시작하고 종료하는지 알아야 한다. 또한, 전송기의 인터리버 동작에 정합하기 위해 역인터리버와 같은 수신기 모듈을 동기화하여, 결과적인 역인터리빙된 비트 또는 바이트가 정확히 순서화되어야 하며, 역랜덤화기는 스펙트럼을 평탄화하기 위해 송신기에서 사용된 의사-랜덤 시퀀스의 시작 포인트에 정합한다. For RF digital communication systems, a receiver typically must first obtain carrier and symbol block synchronization and equalization. The receiver can then recover the matured data. However, in order to understand the applied data stream, the receiver must synchronize to the frame structure. That is, the receiver must know where the error correction code word starts and ends. In addition, the receiver module, such as a deinterleaver, is synchronized to match the interleaver operation of the transmitter so that the resulting deinterleaved bits or bytes must be correctly ordered, and the derandomizer is a pseudo-random used at the transmitter to smooth the spectrum. Matches the starting point of the sequence.

종래의 시스템은 종종 프레임의 시작과 종료에 고정된 길이의 공지된 패턴의 심볼을 첨부함으로써 수신기 프레임 동기화를 제공한다. 이 동일한 패턴은 매 프레임마다 반복되며, 선호할만한 자동-상관 특성을 갖는 2-레벨 (즉, 이진) 의사-랜덤 시퀀스로 구성된다. 이는 시퀀스의 자동-상관이 0 오프셋에서 큰 값을 산출하는 동안, 오프셋이 0이 아닌 경우, 상관값 (사이드 로브 (side-lobe))는 상당히 작음을 의미한다. 또한, 랜덤 심볼을 갖는 이 프레임 동기 시퀀스에 대한 상관은 작은 값을 산출할 것이다. 따라서, 수신기가 저장된 프레임 동기 패턴 버전으로, 인가되는 심볼들의 상관을 실행하는 경우, 각각의 프레임의 정확한 시작에서만 큰 값으르 산출할 것이다. 그 후, 수신기는 각각의 프레임의 시작 포인트를 용이하게 결정할 수 있다. Conventional systems often provide receiver frame synchronization by appending symbols of a known pattern of fixed length to the beginning and end of the frame. This same pattern repeats every frame and consists of a two-level (ie binary) pseudo-random sequence with preferred auto-correlation characteristics. This means that while the auto-correlation of the sequence yields a large value at zero offset, the correlation value (side-lobe) is quite small if the offset is not zero. Also, the correlation for this frame sync sequence with random symbols will yield a small value. Thus, if the receiver performs correlation of the applied symbols with the stored frame sync pattern version, it will yield a large value only at the exact beginning of each frame. The receiver can then easily determine the starting point of each frame.

프레임 구조의 예Example of frame structure

도 9를 참조시, 1996년에 채택된 ATSC 디지털 텔레비전 (DTV) 지상 전송 표준은 데이터가 프레임으로 전송되는 시스템을 제공한다. 프레임 (90)은 313 개의 세그멘트를 포함하고, 각각의 세그멘트는 832개의 심볼을 포함하여, 프레임당 총 260,416개의 심볼이 포함된다. 각 세그멘트의 최초 4개의 심볼은 시퀀스 [+5, -5, -5, +5]를 포함하는 세그멘트 동기 심볼 (92)이다. 각각의 프레임의 최초 세그멘트는 312개의 데이터 세그멘트 (96, 98)를 갖는 프레임 동기 세그멘트 (94)이다. 도 10을 참조하면, 프레임 동기 세그멘트 (94)는 세그멘트 동기 (100), 511개의 심볼 의사-랜덤 잡음 (PN511) 시퀀스 (101), 63개의 심볼 의사-랜덤 잡음 (PN63) 시퀀스 (102), 제 2 PN63 시퀀스 (203), 및 제 3 PN63 시퀀스 (104)를 가진다. 이는 모드가 8개의 VSB 임을 나타내는 24개의 모드 심볼 (105)에 의해 후속된다. 프리-코드 (Pre-code) 심볼 (107) 및 예약 심볼 (106)은 프레임 동기 세그멘트 (94)를 완성한다. 세그멘트 동기 (100) 및 PN511 (101) 심볼은 수신기에 공지되어 있으며, 상관 방법을 통해 프레임 동기화를 획득하는데 사용될 수도 있다. 전술한 모든 심볼은 세트 {+5, -5}로부터 온다. 이 세그멘트의 최종 12개의 심볼 세트 {-7 -5 -3 -1 +1 +3 +5 +7}로부터이며, 선행하는 데이터 필드의 최종 12개의 심볼의 복사본이다. 이들은 프리코드 (precode) 심볼 (본 명세서에서는 논의하지 않음)로 지칭된다.Referring to FIG. 9, the ATSC Digital Television (DTV) Terrestrial Transmission Standard, adopted in 1996, provides a system in which data is transmitted in frames.

또한, 도 11을 참조하면, 데이터 세그멘트로 지칭되는, 필드의 후속하는 312개의 세그멘트 각각에 대해, 4개의 세그멘트 동기 심볼 (30)에 후속하는 828개의 심볼 (32)은 한번에 2개의 비트를 취하여 이들을 3개의 비트로 격자 인코딩 (trellis encoding)한 후, 3개의 비트의 각각의 유닛을 세트 {-7 -5 -3 -1 +1 +3 +5 +7}로부터의 8 개의 레벨 심볼에 정합함으로써, 단일의 207 바이트 (1656 비트) 리드-솔로몬 (RS) 코드-워드로부터 생성된다. Referring also to FIG. 11, for each of the subsequent 312 segments of the field, referred to as data segments, the 828

디지털 통신 시스템에서 프레임화의 또 다른 예는 ISDB-T 시스템에서 나타난다. 단일-반송파 ATSC 시스템과는 달리, ISDB-T 는 직교 부호화 주파수 분할 다중 방식 {COFDM; coded orthogonal frequency division multiplexing}을 사용하는 다중-반송파 시스템이다. 예를 들어, ISDB-T에 대한 모드 1은 1,404개의 반송파를 사용한다. 프레임은 204개의 COFDM 심볼로 구성되며, 각각의 COFDM 심볼은 각각의 반송파에 대해 하나인, 1,404개의 독립적인 QAM 심볼의 조합으로 생각될 수 있다. 그 결과, 프레임은 204×1040=286,416 개의 QAM 심볼로 구성된다. 이 중에서, 254,592개는 데이터이며, 31,824개는 파일롯 정보 (프레임 동기화에 사용될 수 있음) 및 공지된 패턴으로 프레임을 통해 분산되는 모드 정보를 포함한다.Another example of framing in a digital communication system is shown in an ISDB-T system. Unlike single-carrier ATSC systems, ISDB-T is orthogonal coded frequency division multiplex {COFDM; coded orthogonal frequency division multiplexing}. For example,

이러한 프레임 구성의 간략화된 보기가 도 12에 도시된다. 파일롯 및 모드 정보가 공지된 패턴으로 프레임에 대해 분산됨을 알 수 있다. 이 시스템은 3개의 상이한 QAM 성좌도 -QPSK, 16 QAM, 및 64 QAM 을 사용하는 모드를 가진다. 또한, 이 시스템은 단일의 천공 모 코드 {punctured mother code} 에 기반하여 5개의 상이한 격자 코딩 레이트 {1/2, 2/3, 3/4, 5/6, 7/8}를 지원한다. 이 공지된 기술은 용이하게 조정되어 특정 코드 중 5개 모두를 디코딩할 수 있는 수신기에서 단일의 비터비 (Viterbi) 디코더를 구축하는데 상당히 경제적이다. A simplified view of this frame configuration is shown in FIG. 12. It can be seen that the pilot and mode information are distributed over the frame in a known pattern. This system has a mode that uses three different QAM constellations -QPSK, 16 QAM, and 64 QAM. The system also supports five different lattice coding rates {1/2, 2/3, 3/4, 5/6, 7/8} based on a single punctured mother code. This known technique is quite economical to build a single Viterbi decoder in a receiver that can be easily adjusted to decode all five of certain codes.

전송기에서의 격자 코딩 이전에, 데이터는 204 바이트 (1,632 개의 비트) 긴 RS 블록으로 형성된다. 프레임 당 COFDM 심볼의 수는 언제나 일정하며, 프레임 당 RS 블록의 수는 선택된 모드에 따라 변경되지만, 가장 중요한 것은 그 수는 언제나 정수라는 것이다. 이는 프레임 동기가 확립되었으며 격자 코드 레이트가 공지된 경우, 수신기에서 RS 블록 동기화를 용이하게 한다. 이것이 사실이 되도록, 격자 코딩 이전의 프레임당 데이터 비트의 수는 모든 모드에 대해 1.632개로 고르게 분배되어야 한다.Prior to grating coding at the transmitter, data is formed of 204 byte (1,632 bits) long RS blocks. The number of COFDM symbols per frame is always constant and the number of RS blocks per frame changes depending on the mode selected, but most importantly, the number is always an integer. This facilitates RS block synchronization at the receiver when frame synchronization is established and the lattice code rate is known. For this to be true, the number of data bits per frame before lattice coding should be evenly distributed to 1.632 for all modes.

표 1은 모든 모드 (QAM 성좌도 및 격자 코드 레이트의 조합) 에 대해 프레임 당 데이터 비트의 수를 나타낸다. 모든 경우에, 프레임 당 데이터 비트의 수는 1632개로 고르게 분배된다 (데이터 비트는 격자 코딩 이전의 비트를 의미함). Table 1 shows the number of data bits per frame for all modes (combination of QAM constellation and lattice code rate). In all cases, the number of data bits per frame is evenly divided into 1632 (data bits mean bits before lattice coding).

본 발명의 특정 실시예는 디지털 통신 시스템에서 사용된 변조 시스템에 대한 프레임 구조를 제공한다. 특히, 전술한 것들을 포함하여, 보안 시스템에서 사요될 수 있는 신호 시스템 및 방법이 제공된다. 컨벌루션 바이트 인터리버는 데이터의 프레임을 인터리빙하고, 인터리버는 프레임 구조로 동기화되며, 랜덤화기는 인터리빙된 데이터 프레임으로부터 랜덤화된 데이터 프레임을 생성하도록 구성된다. 일 예에서, 천공된 격자 코드 변조기는 랜덤화된 데이터 프레임으로부터 격자 코딩된 데이터 프레임을 생성하는 선택가능한 코드 레이트에서 동작된다. QAM 정합기는 격자 코딩된 데이터 프레임의 비트 그룹을 변조 심볼에 정합시켜 이에 의해 정합된 프레임을 제공하며, 동기화기는 정합된 프레임에 동기화 패킷을 부가한다. 천공된 격자 코드 변조기는 다양한 백색 잡음 조건 하에서 최적화된 네트 비트 레이트를 획득하기 위해 원하는 데로 바이패스 (bypass)될 수 있어, 이에 의해 시스템의 성능 최적화를 허가한다. Certain embodiments of the present invention provide a frame structure for a modulation system used in a digital communication system. In particular, signal systems and methods are provided that can be used in security systems, including those described above. The convolution byte interleaver interleaves a frame of data, the interleaver is synchronized to a frame structure, and the randomizer is configured to generate a randomized data frame from the interleaved data frame. In one example, the perforated lattice code modulator is operated at a selectable code rate that generates a lattice coded data frame from a randomized data frame. The QAM matcher matches a group of bits of the lattice coded data frame to a modulation symbol to provide a matched frame, and the synchronizer adds a synchronization packet to the matched frame. The perforated grating code modulator can be bypassed as desired to obtain an optimized net bit rate under various white noise conditions, thereby allowing for performance optimization of the system.

특정 실시예에서, 신규 프레임 구조가 단일의 반송파 통신 시스템에 제공된다. 0의 오프셋에서 프레임의 시작과 종단에서의 고정된 길이의 심볼의 공지된 패턴의 자동-상관은 큰 값을 산출하며, 오프셋이 0이 아닌 경우, 상관값 (사이드-로브 (side-lobe))는 상당히 작다. 그러나, 랜덤 심볼을 갖는 이 프레임 동기 시퀀스에 대한 상관은 작은 값을 산출한다. 따라서, 수신기가 각각의 프레임의 시작 포인트를 결정하게 하는 각각의 프레임의 정확한 시작에서 큰 값을 획득하기 위해, 수신기는 프레임 동기 패턴의 저장된 버전으로 인가되는 심볼의 상관을 수행할 수도 있다. 통신 시스템은 복수의 모드 중 임의의 모드에서 동작할 수 있으며, 심볼 성좌도, 격자 코드, 및 인터리브 패턴의 다양한 조합을 사용할 수도 있다. 수신기는 전송된 데이터를 성공적으로 복구하기 위해 모드를 인식하고 이해해야 한다. 이 목적을 위해, 부가적인 모드 심볼이 프레임 동기 패턴에 부가될 수 있다. 이들 모드 심볼은, 모드 심볼이 매 프레임마다 반복적으로 전송되기 때문에 상관 방법을 사용하여 신뢰성있게 수신될 수 있다. 블록 코드를 사용하여 모드 심볼을 인코딩함으로써 신뢰성 있는 수신이 더욱 견성해질 수 있다. In certain embodiments, a new frame structure is provided in a single carrier communication system. Auto-correlation of a known pattern of fixed length symbols at the beginning and end of a frame at an offset of zero yields a large value, and if the offset is not zero, the correlation value (side-lobe) Is quite small. However, the correlation for this frame sync sequence with random symbols yields a small value. Thus, to obtain a large value at the exact beginning of each frame that allows the receiver to determine the start point of each frame, the receiver may perform correlation of the symbols applied to the stored version of the frame sync pattern. The communication system may operate in any of a plurality of modes, and may use various combinations of symbol constellations, lattice codes, and interleaved patterns. The receiver must recognize and understand the mode in order to successfully recover the transmitted data. For this purpose, additional mode symbols may be added to the frame sync pattern. These mode symbols can be reliably received using the correlation method because the mode symbols are transmitted repeatedly every frame. Reliable reception can be made more robust by encoding the mode symbols using block codes.