KR101271432B1 - 주파수 혼합기 - Google Patents

주파수 혼합기 Download PDFInfo

- Publication number

- KR101271432B1 KR101271432B1 KR1020090128512A KR20090128512A KR101271432B1 KR 101271432 B1 KR101271432 B1 KR 101271432B1 KR 1020090128512 A KR1020090128512 A KR 1020090128512A KR 20090128512 A KR20090128512 A KR 20090128512A KR 101271432 B1 KR101271432 B1 KR 101271432B1

- Authority

- KR

- South Korea

- Prior art keywords

- line

- input

- unit

- input unit

- output

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1441—Balanced arrangements with transistors using field-effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1408—Balanced arrangements with diodes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1433—Balanced arrangements with transistors using bipolar transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D7/00—Transference of modulation from one carrier to another, e.g. frequency-changing

- H03D7/14—Balanced arrangements

- H03D7/1425—Balanced arrangements with transistors

- H03D7/1458—Double balanced arrangements, i.e. where both input signals are differential

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0001—Circuit elements of demodulators

- H03D2200/0025—Gain control circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0001—Circuit elements of demodulators

- H03D2200/0033—Current mirrors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0041—Functional aspects of demodulators

- H03D2200/0043—Bias and operating point

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0041—Functional aspects of demodulators

- H03D2200/0084—Lowering the supply voltage and saving power

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D2200/00—Indexing scheme relating to details of demodulation or transference of modulation from one carrier to another covered by H03D

- H03D2200/0041—Functional aspects of demodulators

- H03D2200/0094—Measures to address temperature induced variations of demodulation

- H03D2200/0096—Measures to address temperature induced variations of demodulation by stabilising the temperature

Abstract

본 발명은 무선 통신 시스템에서 주파수를 변환해주는 주파수 혼합기에 관한 것으로, 더욱 상세하게는 전원라인(VDD 또는 GND) 노이즈에 영향을 받지 않으면서 낮은 전원전압에서도 안정적인 동작이 가능한 주파수 혼합기에 관한 것이다.

본 발명에 따른 주파수 혼합기는, VDD 라인과 GND 라인 사이에 배치되고, RF(Radio Frequency) 신호를 입력받는 RF 입력부와; 내부 주파수 합성기(Frequency Synthesizer)로부터 방송파(Carrier Frequency, 이하 'LO'라 함) 신호를 입력받는 LO 입력부와; 상기 VDD 라인과 상기 GND 라인 사이에서 상기 RF 입력부와 병렬로 배치되고, 상기 입력된 RF 신호를 상기 LO 신호와 혼합하여 IF(Intermediate Frequency) 신호를 출력하는 IF 출력부와; 상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈에 영향을 받지 않고 안정된 전류를 생성하는, 전류 생성부와; 상기 VDD 라인과 상기 RF 입력부 사이, 상기 VDD 라인과 상기 IF 출력부 사이, 상기 GND 라인과 상기 RF 입력부 사이 및 상기 GND 라인과 상기 LO 입력부 사이에 배치되고, 상기 전류 생성부에서 생성된 전류를 복사하여 안정적인 전류원을 생성하는, 노이즈 차단부를 포함한다.

주파수 혼합기(MIXER), 길버트 주파수 혼합기(Gilbert MIXER), PTAT.

Description

본 발명은 무선 통신 시스템에서 주파수를 변환해주는 주파수 혼합기에 관한 것으로, 더욱 상세하게는 VDD 또는 GND 등의 전원라인 노이즈에 영향을 받지 않으면서 낮은 전원전압에서도 안정적인 동작이 가능한 주파수 혼합기에 관한 것이다.

본 발명은 지식경제부의 IT 원천기술개발사업의 일환으로 수행한 연구로부터 도출된 것이다[과제고유번호: 2008-F-014-02, 과제명: U-사회 전파환경 보호를 위한 전자파양립성 연구].

일반적으로 주파수 혼합기(MIXER)는 통신 시스템에서 중요하게 사용되는 하나의 장치이다. 이러한 주파수 혼합기는 고주파 신호를 저주파 신호로 변환하거나 반대로 저주파 신호를 고주파 신호로 변환하는 장치이다.

초기 통신 시스템에서, 주파수 혼합기는 음성, 영상 또는 데이터를 멀리 안전하게 보내기 위해 사용되었지만, 현재는 덧붙여 신호품질이나 전송거리 확장뿐만 아니라 안테나 크기문제, 다중 사용자를 수용키 위한 채널 관리 등의 여러 목적 때 문에 유선과 무선의 통신시스템에서 필수적으로 사용되고 있다.

좀 더 구체적으로 일반적인 주파수 혼합기는 두 개의 주파수를 섞어서 제 3 의 주파수를 생성하는데, 크게 송신용과 수신용 주파수 혼합기로 나뉜다.

송신용 주파수 혼합기는 저주파(IF) 신호와 LO(Local Oscillator) 신호를 혼합하여 고주파(RF) 신호를 생성하고, 수신용 주파수 혼합기는 고주파(RF) 신호와 LO 신호를 혼합하여 저주파(IF) 신호를 생성한다.

그러면, 이하 첨부된 도면을 참조하여, 일반적인 주파수 혼합기의 회로구조를 살펴보도록 한다.

도 1은 일반적인 싱글 밸런스드 길버트 주파수 혼합기(Single Balanced Gilbert MIXER)의 회로도이고, 도 2는 일반적인 더블 밸런스드 길버트 주파수 혼합기(Double Balanced Gillbert MIXER)의 회로도이다.

도 1의 주파수 혼합기는 RF 신호가 싱글일 때 사용되며, 도 2의 주파수 혼합기는 RF 신호가 차동일 때 사용된다.

도 1에 도시된 주파수 혼합기에 비해 도 2에 도시된 주파수 혼합기의 구조가 복잡하지만, 도 2에 도시된 주파수 혼합기가 각 포트(RF to LO, LO to RF, RF to IF, LO to IF)간 격리(Isolation)특성이 월등히 우수하다. 또한, 도 2에 도시된 주파수 혼합기는 180도 위상차로 인한 신호상쇄로 각종 스퓨리어스나 하모닉 발생을 억제할 수 있어 외부필터의 요구규격을 완화할 수 있다. 따라서 도 1에 도시된 주파수 혼합기보다는 도 2에 도시된 주파수 혼합기가 많이 사용되고 있다.

한편, 주파수 혼합기의 성능을 판단함에 있어서, 격리 특성을 얼마나 가지고 있는지가 하나의 판단요소가 된다. 그 이유는 어느 포트의 신호가 다른 포트에 누설될 경우 자기신호끼리 재결합하는 셀프-믹싱(self-mixing)을 일으켜 출력 DC 값이 요동치는 DC 오프셋(offset)이 발생할 수 있기 때문이다. DC 오프셋(offset)이 발생하면 전체 시스템 동작을 비정상상태로 만들 수 있다. 따라서 포트간 격리(Isolation)특성을 크게 할수록 전체 시스템은 성능이 좋아진다. 특히, 옆 라인으로 커플링이 잘 일어나는 RF 신호나 신호레벨이 제일 큰 LO의 격리특성이 무엇보다 중요하다.

도 1 내지 도 2에 도시된 주파수 혼합기는 외부에서 유입되는 전도성 EMI(전자파방사)나 방사성 EMI의 영향으로 인해, PCB에 유기되어 들어오는 전원라인(VDD, GND) 노이즈에 취약하다는 문제점이 있다. 이를 좀 더 구체적으로 설명하면, VDD 라인을 통해 유입된 노이즈(110, 210)는 부하저항(RL)에 흐르는 전류를 타고 출력 IF 포트에 직접적 전달되며, GND 라인을 통해 유입된 노이즈(130, 230)는 RF 입력단 트랜지스터(MN1, MN2)로 입력되고 증폭되어 출력 IF 포트에 전달되므로, 도 1 내지 도 2에 도시된 주파수 혼합기들은 전원라인 노이즈에 취약하다.

이러한 전원라인 노이즈 문제는 테일 커런트 소스(tail current source)를 추가하면, 전원라인을 통해 유입되는 노이즈의 영향을 감쇄시킬 수 있다. 예를 들면, 도 2에 도시된 주파수 혼합기에서 RF 포트의 격리특성을 더 좋게 하기 위해 RF 입력 트랜지스터 MN1, MN2의 소스가 바로 접지(GND)와 연결되지 않고 중간에 테일 커런트 소스를 삽입시켜 GND 라인을 통해 유입되는 노이즈의 영향을 감쇄시킬 수 있고, 완벽한 위상차 특성을 얻을 수 있다.

그러나 1V 근처의 저 전원전압이 사용되는 현재의 저전력화 추세에서, 테일 커런트 소스를 추가한 주파수 혼합기는 신호의 헤드룸(headroom)을 낮추게 하여, 조금만 신호가 커져도 셋츄레이션(saturation)이 되어 신호가 쉽게 왜곡되는 문제가 있다. 따라서 주파수 혼합기의 다이나믹 레인지(Dynamic Range)나 선형성(IP3)을 고려할 때, 테일 커런트 소스는 부담을 주게 된다.

따라서 테일 커런트 소스를 주파수 혼합기에 추가하고 싶어도 추가하지 못하는 상황이 발생하므로, 결국, 도 1 내지 도 2에 도시된 종래의 주파수 혼합기는 외부에서 유입되는 전원라인 노이즈에 직접적인 영향을 받을 수밖에 없다. 그 결과, 전원라인 노이즈는 주파수 혼합기 뒷단에 이어지는 가변이득증폭기(VGA)에 의해 증폭되어 전체 시스템의 NF(Noise Figure)를 증가시키고, 내성을 떨어뜨린다. 결국, 전원라인 노이즈에 영향을 받지 않는 다른 대책이 필요하다.

또 하나, 도 1 내지 도 2에 도시된 주파수 혼합기는 추가 전압 바이어스회로에서 RFBIAS, LOBIAS 등의 DC 전압을 제공받아 동작점을 유지하였다. 그러나 이러한 개별적인 DC 전압 바이어스는 전압의 변동성도 크고, RF 와 LO DC 바이어스의 연관성을 고려하지 않기 때문에 주파수 혼합기들의 구동오차가 커지는 문제점이 있다.

또한, 추가 전압 바이어스회로는 대부분 전원단에 저항을 직렬로 배열한 구조이거나 저항과 트랜지스터 또는 트랜지스터들만으로 구성되는 구조로서, 전원라인 노이즈가 그대로 DC 바이어스에 누설되기 쉬운 회로 구조를 가진다.

따라서 설계된 주파수 혼합기들 간의 구동오차를 줄이기 위해, 또 전원라인 노이즈에 영향을 받지 않는 바이어스 전압을 제공하기 위해 회로에 대한 대책이 필요하다.

따라서 본 발명은 전원라인 노이즈에 영향을 받지 않는 주파수 혼합기를 제공한다.

또한, 종래의 테일 커런트(tail current)를 가진 더블 밸런스드 길버트 믹서의 우수한 포트간 격리(Isolation)특성을 저전압 전원동작에서도 그대로 유지할 수 있는 주파수 혼합기를 제공한다.

또한, 이득조절이 용이하고, 선형성을 개선시킬 수 있는 주파수 혼합기를 제공한다.

또한, 구동오차를 줄일 수 있는 주파수 혼합기를 제공한다.

또한, 전원라인 노이즈에 영향을 받지 않는 바이어스 회로를 포함한 주파수 혼합기를 제공한다.

본 발명에 따른 주파수 혼합기는, VDD 라인과 GND 라인 사이에 배치되고, RF(Radio Frequency) 신호를 입력받는 RF 입력부와; 내부 주파수 합성기(Frequency Synthesizer)로부터 방송파(Carrier Frequency, 이하 'LO'라 함) 신호를 입력받는 LO 입력부와; 상기 VDD 라인과 상기 GND 라인 사이에서 상기 RF 입력부와 병렬로 배치되고, 상기 입력된 RF 신호를 상기 LO 신호와 혼합하여 IF(Intermediate Frequency) 신호를 출력하는 IF 출력부와; 상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈에 영향을 받지 않고 안정된 전류를 생성하는, 전류 생성부와; 상기 VDD 라인과 상기 RF 입력부 사이, 상기 VDD 라인과 상기 IF 출력부 사이, 상기 GND 라인과 상기 RF 입력부 사이 및 상기 GND 라인과 상기 LO 입력부 사이에 배치되고, 상기 전류 생성부에서 생성된 전류를 복사하여 안정적인 전류원을 생성하는, 노이즈 차단부를 포함한다.

본 발명에 따른 주파수 혼합기를 사용하면, 전원라인 노이즈에 대한 영향을 감쇄시킬 수 있는 이점이 있다.

또한, 종래의 테일 커런트(tail current)를 가진 더블 밸런스드 길버트 믹서의 우수한 포트간 격리(Isolation)특성을 저전압 전원동작 시스템에서도 그대로 유지할 수 있는 이점이 있다.

또한, RF 입력부의 트랜스컨덕터를 별도로 구성하므로, IF 출력부에 흐르는 전류와 독립적으로 RF 입력부에 흐르는 전류를 조절할 수 있어, 이득조절과 선형성의 개선에 탁월한 이점이 있다.

또한, 구동오차를 줄일 수 있는 이점이 있다.

또한, 전원라인 노이즈에 영향을 받지 않는 바이어스 회로를 포함한 주파수 혼합기를 제공하는 이점이 있다.

이하 첨부된 도면을 참조하여 본 발명을 설명한다. 본 발명을 설명함에 있어 당업자에게 자명한 부분에 대하여는 본 발명의 요지를 흩뜨리지 않도록 생략하기로 한다. 또한 이하에서 설명되는 각 용어들은 본 발명의 이해를 돕기 위해 사용된 것일 뿐이며, 각 제조 회사 또는 연구 그룹에서는 동일한 용도임에도 불구하고 서로 다른 용어로 사용될 수 있음에 유의해야 한다.

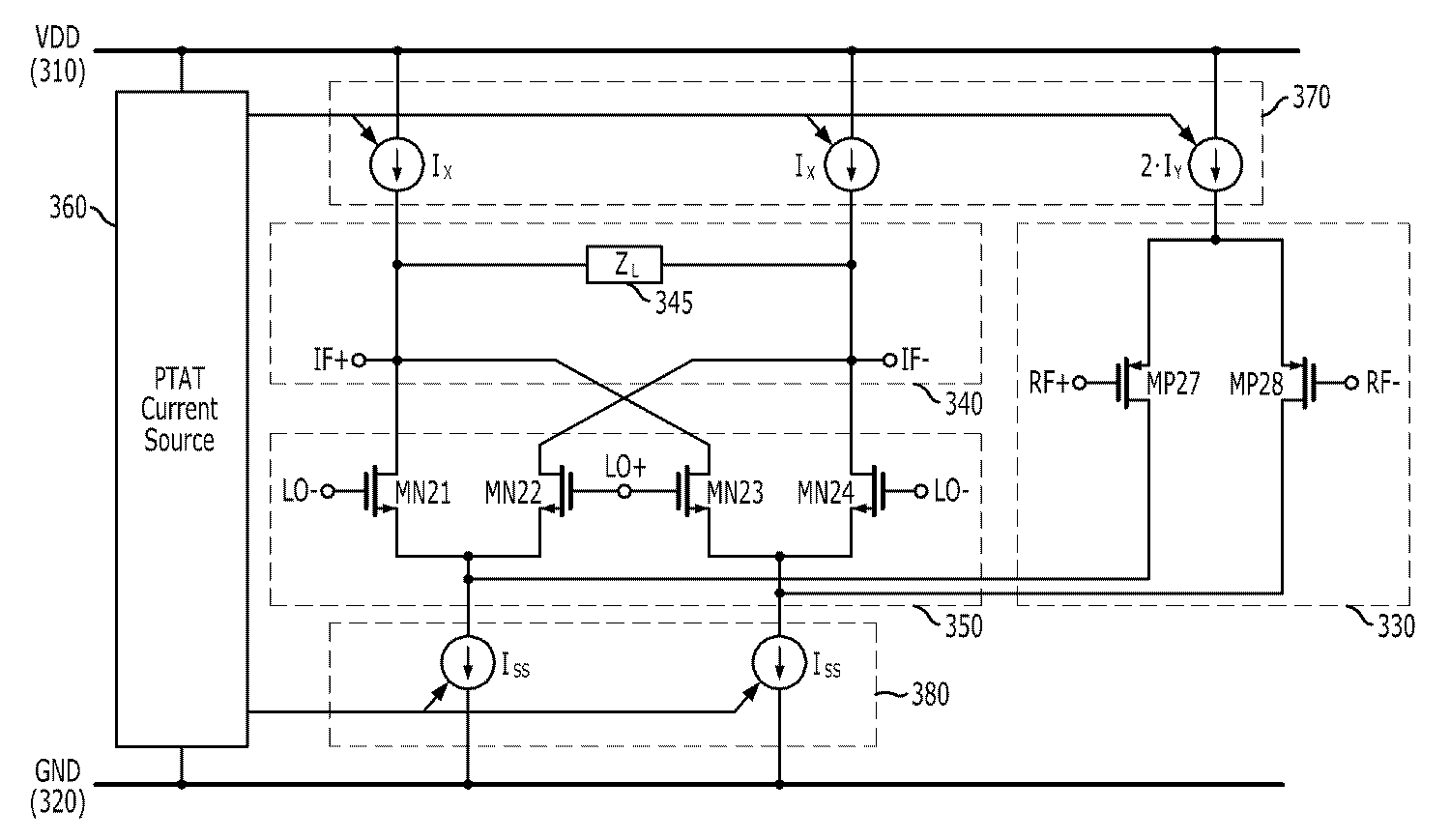

도 3은 본 발명의 일 실시 예에 따른 주파수 혼합기의 회로도이다.

도 3에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기는, RF 입력부(330), IF 출력부(340), LO 입력부(350), 전류 생성부(360), VDD 노이즈 차단부(370), GND 노이즈 차단부(380)를 포함한다.

이러한 본 발명의 일 실시 예에 따른 주파수 혼합기의 IF 출력부(340)는 도 2에 도시된 더블 밸런스드 길버트 주파수 혼합기의 IF 출력부와 동일한 회로 구성을 갖는다. 다만, 본 발명의 일 실시 예에 따른 주파수 혼합기의 IF 출력부(340)의 부하 임피던스(345)는 도 2에 도시된 종래의 더블 밸런스드 길버트 주파수 혼합기와 다른데, 이에 대해서는 후술하기로 한다.

VDD 라인(310)과 IF 출력부(340) 사이에는 VDD 노이즈 차단부(370)가 배치되며, GND 라인(320)과 LO 입력부(350) 사이에는 GND 노이즈 차단부(380)가 배치된 다. 또한, VDD 노이즈 차단부(370)와 GND 노이즈 차단부(380)사이에 LO 입력부(350)와 병렬로 RF 입력부(330)가 연결된다.

그리고 VDD 노이즈 차단부(370)는 VDD 라인(310)을 통해 유입되는 VDD 노이즈를 차단하고, GND 노이즈 차단부(380)는 GND 라인(320)을 통해 유입되는 GND 노이즈를 차단한다. VDD 노이즈 차단부(370)와 GND 노이즈 차단부(380)는 전류 생성부(360)에서 생성된 PTAT 전류에 의해 제어되는 복사 전류원이다.

그리고 본 발명의 일 실시 예에 따른 주파수 혼합기의 모든 트랜지스터들(MN21, MN22, MN23, MN24, MP27, MP28)은 전류 생성부(360)에서 생성된 PTAT 전류를 통해 복사된 미러전류를 공급받는다.

여기서, 전류 생성부(360)는 온도보상회로로 일반적으로 사용되는 밴드갭 회로로 구성되는데, P-N 접합(junction)소자에 흐르는 안정화된 전류를 출력한다. P-N 접합(junction)소자는 다이오드나 바이폴라 트랜지스터(BJT)가 대표적으로 사용되며 P-N 접합(junction)소자의 면적과 전류의 크기에 따라 다른 온도특성을 밴드갭 회로구성을 통해 온도변화에 비례적인 특성을 갖는 전류를 생성한다. 이 전류를 PTAT 전류라 하는데, 절대온도에만 비례하는 전류를 다른 회로단(stage)에 복사해 준다.

전류 생성부(360)에서 생성된 PTAT 전류는 절대온도에 비례하는 전류특성을 가지기 때문에, 일정 온도에서 모든 트랜지스터들(MN21, MN22, MN23, MN24, MP27, MP28)의 p-n 접합(junction)에 흐르는 전류는 전원전압변동에 무관하게 일정하다. 이것은 VDD 전원(310)과 GND 전원(320)의 노이즈 영향을 받지 않는 일정한 전류가 모든 트랜지스터들(MN21, MN22, MN23, MN24, MP27, MP28)의 p-n 접합(junction)에 캐스코드된 모든 소자에 동일하게 적용된다. 따라서 전류미러 쌍 회로구조를 통해 전류 생성부(360)에 의하여 복사된 전류원들(IX, ISS, IY)은 전원노드(VDD, GND)에 영향을 받지 않는 일정한 전류를 발생한다. 따라서 본 발명의 일 실시 예에 다른 주파수 혼합기는 전원라인(310, 320)에 유입되는 노이즈에 무관하게 안전하게 동작할 수 있는 상태를 유지한다.

또한, 도 3을 참조하면, RF 입력부(330)는 도 2에서는 LO 입력부와 적층(Cascode)된 NMOS 소자(MN1, MN2)로 되었지만, 본 발명의 일 실시 예에 따른 주파수 혼합기에서는 LO 입력부(350)와 병렬 연결된 PMOS 소자(MP27, MP28)가 사용되고, 여기에 GND 노이즈 차단부(380), 즉 PTAT 미러 전류원(ISS)을 추가함으로써, GND 라인(320)을 통해 유입되는 노이즈를 예방할 수 있으며, 전압 헤드룸(voltage headroom)을 차지하지 않아 저전압 설계의 목적을 충족시킬 수 있다.

또한, PMOS 소자로 구성된 RF 입력부(330)의 트랜지스터들(MP27, MP28)과 VDD 전원(310) 사이에 PTAT 미러 전류 소스(2IY)를 삽입하여 RF 입력부(330)의 트랜지스터들(MP27, MP28)로 VDD 라인(310) 노이즈가 유입되는 것을 예방할 수 있다.

이와 더불어, 도 2에 도시된 더블 밸런스드 길버트 주파수 혼합기의 최대장점을 저전압에서도 이끌어 낼 수 있다. 다시 말해, 본 발명의 일 실시 예에 따른 주파수 혼합기에서 RF 입력부(330)의 배치는 최대 포트간 격리특성과 전압 헤드룸(voltage headroom)이 덜 차지하기 때문에, 선형성과 동적영역(Dynamic range)등 이 우수하다.

또한, 종래의 더블 밸런스드 길버트 주파수 혼합기의 이득을 결정하는 부하저항(RL)을 도 3에 도시된 바와 같이 병렬 임피던스, ZL(345)로 대체함으로써, 출력매칭과 종래의 더블 밸런스드 길버트 주파수 혼합기의 이득을 유지할 수 있다.

한편, 도 3에 도시된 PTAT 복사 전류원들(IX, ISS, IY)은 아래의 <수학식 1>과 같은 관계를 갖는다.

위 <수학식 1>을 참조하면, PTAT 복사 전류원들(IX, ISS, IY)의 대부분 전류는 RF 입력부(330)로 흐르고, LO 스위칭(switching)을 하는 IF 출력부(340)의 트랜지스터들(MN21, MN22, MN23, MN24)에는 상대적으로 작은 전류가 흐른다. 그 이유는 본 발명의 일 실시 예에 따른 주파수 혼합기의 컨버젼 이득이 주로 RF 입력부(330)의 트랜스컨덕턴스, gm 크기와 LO 입력부(350)의 스위칭특성에 좌우되기 때문이다. LO 입력부(350)에 전류가 적게 흐를수록 스위칭 트랜지스터들(MN21, MN22, MN23, MN24)의 동작 게이트-소스 전압이 낮아져서 LO 입력부(350) LO 스위칭 특성이 좋아지기 때문이다. 즉 작은 전압차이에도 트랜지스터의 ON & OFF가 확실하다. 이렇게 효과적인 스위칭 특성은 주파수변환 효율을 높이고, 동시에 LO 입력부(350)의 트랜지스터들(MN21, MN22, MN23, MN24)이 과도상태의 온(On)인 시간이 아주 작기 때문 에 LO 신호의 누설을 막을 수 있다. LO 입력부(350)의 트랜지스터들(MN21, MN22, MN23, MN24)이 완벽한 스위칭 동작을 할 때, 본 발명의 일 실시 예에 따른 주파수 혼합기의 출력은 아래의 <수학식 2>로 표현될 수 있다.

<수학식 2>에서, gm은 RF 입력부(330) 내의 트랜지스터(MP27)의 트랜스컨덕턴스, Vrf는 RF 입력부(330)로 입력되는 RF 신호의 전압크기를 의미한다. 따라서 본 발명의 일 실시 예에 따른 주파수 혼합기의 이득(Av)은 아래의 <수학식 3>으로 표현될 수 있다.

<수학식 3>에서, 는 RF 입력부(330) PMOS 소자의 홀 이동도(mobility)이고, 는 게이트-옥사이드의 면적당 커패시턴스이고, 는 트랜지스터(MP27, MP28)의 사이즈(size)이고, 는 이다.

따라서, 본 발명의 일 실시 예에 따른 주파수 혼합기의 이득을 증가시키기 위해서는, <수학식 3>과 같이, ZL(345)을 크게 하거나 RF 입력부(330)의 트랜스컨덕턴스, gm를 크게 하기 위해 트랜지스터(MP27, MP28)의 사이즈(W/L)나 RF입력단 전류 IY를 증가시켜야 한다. 특히, 주파수 혼합기의 이득, LO 스위칭(switching)특성 및 IP3를 고려할 때에는 IX를 줄이고 IY는 증가시키는 방향으로 설계되는 것이 바람직하다.

도 4는 도 3에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기의 동작을 개략적으로 설명하기 위한 동작모델링이다.

RF 입력부(330)로 입력된 입력 RF 신호는 트랜스컨덕터(W/LMP27, MP28, 2IY)에 의해 gm만큼 증폭된 소신호 전류로 변환되어, 더블 밸런스드(double balanced) 구조의 LO 스위칭부(353)를 통해 주파수 변환된 전류가 IF 출력단(IF+, IF-)(340)으로 전달된다. IF 출력단(340)으로 전달되는 차동 믹싱(mixing) 전류는 부하 임피던스(ZL/2)와 결합하여 전압으로 출력된다.

여기서, RF 입력부(330) 내의 RF 입력 트랜지스터는 PMOS 소자이기 때문에, 동일 사이즈의 NMOS 소자일 때 보다 트랜스컨덕턴스가 작으므로, 이를 고려하여 2~3배의 사이즈만큼 큰 소자를 사용하는 것이 바람직하다.

또한, 상대적으로 작은 전류가 흐르는 LO 스위칭부(353)의 트랜지스터들도 스위칭 모드의 민감도를 증가시키기 위하여 소자의 사이즈를 키우는 것이 바람직하 며, 아울러 PTAT 복사 전류원(IX)와 PTAT 복사 전류원(IY)의 비율을 적절히 조절하여 이득과 스위칭 효율이 가장 좋은 게이트-소스 전압점을 찾아야 할 것이다. 완벽한 스위칭 동작을 한다는 가정하에, 차동 LO 입력파형의 비교 전위차에 따라 양의 값일 때는 H(High)로, 음의 값일 때는 L(Low)로 붙어 디지털동작을 수행한다. 이때 이득효율을 증가시키기 위해 LO 스위칭부(353)의 디지털준위 H와 L의 듀티 레이트(Duty Rate)가 0.5가 되도록 설계되어야 한다.

한편, 노이즈 차단부(370, 380)는 PTAT 복사 전류원들로 이루어짐으로서, VDD/GND 라인(310, 320)의 유입 노이즈(311, 321)에 독립적으로 동작하는 것을 특징적으로 보여 준다.

도 5는 도 3에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기의 회로도이다.

도 5를 참조하면, 도 5에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기는 전류 생성부(560), 전원노이즈에 독립적인 바이어스부(590), 주파수 혼합기 코어부(500)를 포함한다.

전류 생성부(560)는 온도보상회로로 일반적으로 사용되는 밴드갭 회로로 구성되는데, P-N 접합(junction)소자에 흐르는 안정화된 전류를 출력한다. 이때 비례적인 미러 전류를 출력할 수 있도록 미러링 쌍 구조를 갖는다. 여기서, P-N 접합(junction)소자는 다이오드나 바이폴라 트랜지스터(BJT)가 대표적으로 사용되며 P-N 접합(junction)소자의 면적과 전류의 크기에 따라 다른 온도특성을 밴드갭회로 구성을 통해 온도변화에 비례적인 특성을 갖는 전류를 생성한다. 이 전류를 PTAT 전류라 하는데 트랜지스터(MP11 및 MP12)와 증폭기로 구성된 능동 미러 구조를 통해 절대온도에만 비례하는 전류를 다른 회로단(stage)에 복사해 준다.

바이어스부(590)는 주파수 혼합기 코어부(500)의 전류와 RF 입력부(530) 및 LO 입력부(550) 각각에 바이어스 전압을 제공한다.

여기서, 상기 바이어스부(590)는 대칭 형태를 갖는 주파수 혼합기 코어부(500)의 반쪽 구조로서 리플리카(replica) 바이어스 구조를 갖는다. 즉, 도 5에서 상기 바이어스부의 MN18, MN15, MN16, MP17, MP13, MP14는 MN31, MN21, MN22, MP27, MP19 및 MP25을 포함하는 구조 또는 MN32, MN23, MN24, MP28, MN26 및 MP20를 포함하는 구조와 대칭된다.

상기 바이어스부(590)에서 RF 입력부(530)에 바이어스 전압을 제공하는 트랜지스터(MP17), LO 입력부(550)에 바이어스 전압을 제공하는 트랜지스터들(MN15, MN16) 및 GND 노이즈 차단부(580)에 PTAT 테일(tail) 전류를 제공하는 트랜지스터(MN18)는 게이트와 드레인이 전기적으로 연결된 다이오드 연결구조로서 각 노드의 바이어스 전압을 안정화 한다.

이러한 리플리카 바이어스 구조는 주파수 혼합기 코어부(500)에서 사용된 트랜지스터들과 동일한 트랜지스터 사이즈와 전류값을 갖는다.

좀 더 구체적으로, 상기 바이어스부(590)를 이하에서 설명하도록 한다.

MP13과 MP14는 전류 생성부(560)에서 생성된 PTAT 전류를 제공받아 바이어스부내에 동작 전류를 공급한다.

MN15와 MN16은 다이오드 연결구조로서, 주파수 혼합기 코어부(500)의 LO 입력부(550) 내에 차동 쌍 트랜지스터들(MN21과 MN22, MN23과 MN24) 각각에 게이트 바이어스를 제공한다.

MP17은 다이오드 연결구조로서, 주파수 혼합기 코어부(500)의 RF 입력부(530) 내에 배치된 트랜지스터들(MP27, MP28) 각각에 게이트 바이어스를 생성하여 공급한다.

MN18은 다이오드 연결구조로서, 주파수 혼합기 코어부(500)의 GND 노이즈 차단부(580) 내에 배치된 트랜지스터들(MN31, MN32) 각각에 복사된 PTAT 테일(tail) 전류를 생성한다. 또한, MN18은 MN31, MN32와 동일한 사이즈를 갖는 미러링 쌍으로서, MN18의 소스-드레인 단자를 흐르는 전류는 MP13과 MP14의 소스-드레인 단자를 흐르는 전류의 합과 같다. 따라서 MP13, MP14에 흐르는 전류의 합은 MP19, MP25과 MP26, MP20에 흐르는 전류의 합과 동일하다.

주파수 혼합기 코어부(500)에서 RF 입력부(530)로 입력되는 RF 신호와 LO 입력부(550)로 입력되는 LO 신호는 커패시터를 통해 커플링되어 전달되고, 바이어스는 큰 값의 바이어스 저항을 통해 바이어스부(590)로부터 제공된다. 여기서, 바이어스 저항은 인덕터로 대체하여도 무방하다.

바이어스 저항(또는 인덕터)은 바이어스부(590)와 주파수 혼합기 코어부(500) 사이의 커패시터들(CLO, CRF)과 결합하여 저역통과필터(LPF)를 구성하는데, 이는 LO 신호나 RF 신호가 바이어스부(590)를 경유함으로써 포트간 격리 특성을 열 화시키는 것을 예방하기 위함이다.

부하 임피던스(545)는 이득과 매칭을 위해 LC 공진기로 구성될 수도 있고 수동저항 R이나 능동저항(예, MOSFET 소자)으로 구성될 수도 있다. 그리고 출력단의 DC 전압을 안전하게 유지하기 위해, N2 노드의 전압은 추가적인 기준전압회로를 통해 안정된 바이어스를 공급받거나 그렇지 않을 경우는 단순하게 바이어스부(590)의 N1노드와 연결해도 무방하나 이 경우 IF 신호가 LO 입력부(550)로 입력되는 것을 막기 위하여, CLO값을 적절한 값으로 설정하는데 신경을 써야 한다.

본 발명의 일 실시 예에 따른 주파수 혼합기가 적절한 노이즈 차단(noise blocking)과 미러 전류의 오차를 감소시키기 위해, 전류 미러 쌍 구조의 트랜지스터들은 가능하면 긴 채널길이(L: channel length of MOSFET)를 갖는 것이 바람직하다.

이제까지 본 발명에 대하여 그 바람직한 실시 예를 중심으로 살펴보았다. 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자는 본 발명이 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 변형된 형태로 구현될 수 있음을 이해할 수 있을 것이다. 그러므로 개시된 실시 예는 한정적인 관점이 아니라 설명적인 관점에서 고려되어야 한다. 본 발명의 범위는 전술한 설명이 아니라 특허청구범위에 나타나 있으며, 그와 동등한 범위 내에 있는 모든 차이점은 본 발명에 포함된 것으로 해석되어야 할 것이다.

도 1은 일반적인 싱글 밸런스드 길버트 주파수 혼합기(Single Balanced Gilbert MIXER)의 회로도,

도 2는 일반적인 더블 밸런스드 길버트 주파수 혼합기(Double Balanced Gillbert MIXER)의 회로도,

도 3은 본 발명의 일 실시 예에 따른 주파수 혼합기의 회로도, 도 4는 도 3에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기의 동작을 개략적으로 설명하기 위한 동작모델링,

도 5는 도 3에 도시된 본 발명의 일 실시 예에 따른 주파수 혼합기 회로도.

Claims (10)

- 하향변환 주파수 혼합기에 있어서,VDD 라인과 GND 라인 사이에 배치되고, RF(Radio Frequency) 신호를 입력받는 RF 입력부;상기 VDD 라인과 상기 GND 라인 사이에 배치되고, 내부 주파수 합성기(Frequency Synthesizer)로부터 LO(Local Oscillator) 신호를 입력받는 LO 입력부;상기 VDD 라인과 상기 GND 라인 사이에서 상기 RF 입력부와 병렬로 배치되고, 상기 입력된 RF 신호를 상기 LO 신호와 혼합하여 IF(Intermediate Frequency) 신호를 출력하는 IF 출력부;상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈에 영향을 받지 않고 일정한 전류를 생성하는, 전류 생성부; 및상기 VDD 라인과 상기 GND 라인을 통해, 상기 RF 입력부, 상기 LO 입력부, 및 상기 IF 출력부로 각각 유입되는 노이즈를 차단하는 노이즈 차단부를 포함하며,상기 노이즈 차단부는,상기 VDD 라인과 상기 RF 입력부 사이, 상기 VDD 라인과 상기 IF 출력부 사이, 상기 VDD 라인과 상기 LO 입력부 사이, 상기 GND 라인과 상기 RF 입력부 사이, 상기 GND 라인과 상기 IF 출력부 사이, 및 상기 GND 라인과 상기 LO 입력부 사이에 배치되고;상기 전류 생성부에서 생성된 전류를 상기 RF 입력부, 상기 LO 입력부, 및 상기 IF 출력부로 공급하여, 상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈를 차단하는 것을 특징으로 하는, 주파수 혼합기.

- 제 1 항에 있어서,상기 RF 입력부는,상기 VDD 라인 노이즈 차단부의 2개의 전류원들 각각에 연결된 두 개의 PMOS 트랜지스터들이 차동쌍 구조를 형성하고, 상기 PMOS 트랜지스터들 각각의 드레인은 상기 GND 라인 노이즈 차단부의 두 전류원에 연결되고, 상기 LO 입력부의 트랜지스터의 소스와 병렬로 연결되고,상기 LO 입력부와 상기 IF 출력부는,상기 RF 입력부와 병렬로 연결된 상기 LO 입력부는 2개의 NMOS트랜지스터가 차동쌍 구조를 형성하고, 상기 NMOS 트랜지스터들 각각의 드레인은 더블 밸런스드 길버트 주파수 혼합기 구조와 같이 차동출력(IF+, IF-)인 상기 IF 출력단에 각각 연결되며, 상기 VDD 라인 노이즈 차단부의 2개의 전류원들 각각에 상기 IF 출력단이 연결되며, 병렬로 상기 IF 출력단의 IF+ 출력단과 IF- 출력단 사이에 부하 임피던스가 형성되어 코어 구조를 형성하는 것을 특징으로 하는, 주파수 혼합기.

- 제 1 항에 있어서, 상기 전류 생성부는,밴드갭 회로로 구성된 것을 특징으로 하는, 주파수 혼합기.

- 제 1 항에 있어서,상기 VDD 라인과 상기 RF 입력부 사이에 배치된 노이즈 차단부의 복사 전류 원 크기는, 상기 VDD 라인과 상기 IF 출력부 사이에 배치된 노이즈 차단부의 복사 전류원의 크기보다 큰 것을 특징으로 하는, 주파수 혼합기.

- 제 2 항에 있어서,상기 LO 입력부와 상기 RF 입력부의 입력단에 바이어스 전압을 제공하는, 바이어스부를 더 포함하며,상기 바이어스부는 상기 코어 구조의 반쪽구조로서, 리플리카(Replica) 바이어스 구조를 가지며, 상기 리플리카 바이어스 구조는 상기 코어 구조에서 사용된 트랜지스터들과 동일한 트랜지스터 사이즈를 가지며, 상기 코어 구조에서 사용된 트랜지스터들에 흐르는 전류와 동일한 전류가 흐르는 것을 특징으로 하는, 주파수 혼합기.

- 상향 변환 주파수 혼합기에 있어서,VDD 라인과 GND 라인 사이에 배치되고, IF(Intermediate Frequency) 신호를 입력받는 IF 입력부;상기 VDD 라인과 상기 GND 라인 사이에 배치되고, 내부 주파수 합성기(Frequency Synthesizer)로부터 LO(Local Oscillator) 신호를 입력받는 LO 입력부;상기 VDD 라인과 상기 GND 라인 사이에서 상기 IF 입력부와 병렬로 배치되고, 상기 입력된 IF 신호를 상기 LO 신호와 혼합하여 RF(Radio Frequency) 신호를 출력하는 RF 출력부;상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈에 영향을 받지 않고 일정한 전류를 생성하는, 전류 생성부; 및상기 VDD 라인과 상기 GND 라인을 통해, 상기 IF 입력부, 상기 LO 입력부, 및 상기 RF 출력부로 각각 유입되는 노이즈를 차단하는 노이즈 차단부를 포함하며;상기 노이즈 차단부는,상기 VDD 라인과 상기 IF 입력부 사이, 상기 VDD 라인과 상기 RF 출력부 사이, 상기 VDD 라인과 상기 LO 입력부 사이, 상기 GND 라인과 상기 IF 입력부 사이, 상기 GND 라인과 상기 RF 출력부 사이, 및 상기 GND 라인과 상기 LO 입력부 사이에 배치되고;상기 전류 생성부로부터 생성된 전류를 상기 IF 입력부, 상기 LO 입력부, 및 상기 RF 출력부에 공급하여, 상기 VDD 라인과 상기 GND 라인을 통해 유입되는 노이즈를 차단하는 것을 특징으로 하는 주파수 혼합기.

- 제 6 항에 있어서,상기 IF 입력부는,상기 VDD 라인 노이즈 차단부의 2개의 전류원들 각각에 연결된 두 개의 PMOS 트랜지스터들이 차동쌍 구조를 형성하고, 상기 PMOS 트랜지스터들 각각의 드레인은 상기 GND 라인 노이즈 차단부의 두 전류원에 연결되고 상기 LO 입력부의 트랜지스터의 소스와 병렬로 연결되고,상기 LO 입력부와 상기 RF 출력부는,상기 IF 입력부와 병렬로 연결된 LO 입력부는 2개의 NMOS트랜지스터 차동쌍 구조를 형성하고, 상기 NMOS 트랜지스터들 각각의 드레인은 더블 밸런스드 길버트 주파수 혼합기 구조와 같이 차동출력(RF+, RF-)인 상기 RF 출력단에 각각 연결되며, 상기 VDD 전원 노이즈 차단부의 2개의 전류원들 각각에 상기 RF 출력단이 연결되며, 병렬로 상기 RF 출력단의 RF+ 출력단과 RF- 출력단 사이에 부하 임피던스가 형성되어 코어 구조를 형성하는 것을 특징으로 하는 주파수 혼합기.

- 제 6 항에 있어서, 상기 전류 생성부는,밴드갭 회로로 구성된 것을 특징으로 하는, 주파수 혼합기.

- 제 6 항에 있어서,상기 VDD 라인과 상기 IF 입력부 사이에 배치된 노이즈 차단부의 복사 전류원 크기는, 상기 VDD 라인과 상기 IF 출력부 사이에 배치된 노이즈 차단부의 복사 전류원의 크기보다 큰 것을 특징으로 하는, 주파수 혼합기.

- 제 7 항에 있어서,상기 LO 입력부와 상기 IF 입력부의 입력단에 바이어스 전압을 제공하는, 바이어스부를 더 포함하며,상기 바이어스부는 상기 코어 구조의 반쪽구조로서, 리플리카(Replica) 바이 어스 구조를 가지며, 상기 리플리카 바이어스 구조는 상기 코어 구조에서 사용된 트랜지스터들과 동일한 트랜지스터 사이즈를 가지며, 상기 코어 구조에서 사용된 트랜지스터들에 흐르는 전류와 동일한 전류가 흐르는 것을 특징으로 하는, 주파수 혼합기.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090128512A KR101271432B1 (ko) | 2009-12-21 | 2009-12-21 | 주파수 혼합기 |

| US12/837,807 US8358998B2 (en) | 2009-12-21 | 2010-07-16 | Frequency mixer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090128512A KR101271432B1 (ko) | 2009-12-21 | 2009-12-21 | 주파수 혼합기 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110071843A KR20110071843A (ko) | 2011-06-29 |

| KR101271432B1 true KR101271432B1 (ko) | 2013-06-05 |

Family

ID=44151779

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090128512A KR101271432B1 (ko) | 2009-12-21 | 2009-12-21 | 주파수 혼합기 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8358998B2 (ko) |

| KR (1) | KR101271432B1 (ko) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102196071B (zh) * | 2010-07-30 | 2013-02-20 | 惠州Tcl移动通信有限公司 | 一种移动终端 |

| KR101756484B1 (ko) | 2011-07-20 | 2017-07-10 | 엘지이노텍 주식회사 | 전기 자전거용 모터 |

| TWI549422B (zh) * | 2014-09-12 | 2016-09-11 | Univ Nat Chi Nan | Mixed circuit |

| KR102419350B1 (ko) | 2017-11-08 | 2022-07-12 | 한국전자통신연구원 | 무선 전력 전송 장치, 그리고 무선 전력 수신 장치. |

| WO2023277351A1 (ko) * | 2021-06-28 | 2023-01-05 | 삼성전자주식회사 | 상·하향 주파수 변환 전자 장치 및 밀리미터파 저 위상 잡음 국부 발진기 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20070106009A (ko) * | 2005-01-21 | 2007-10-31 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 저잡음 혼합기 회로, 잡음 감소 회로, 수신기 회로,고주파수 수신기 및 잡음 감소 방법 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5649312A (en) * | 1994-11-14 | 1997-07-15 | Fujitsu Limited | MMIC downconverter for a direct broadcast satellite low noise block downconverter |

| US6975838B1 (en) * | 1999-10-21 | 2005-12-13 | Broadcom Corporation | Adaptive radio transceiver with noise suppression |

| KR100456238B1 (ko) | 2001-11-16 | 2004-11-09 | 한국전자통신연구원 | 시모스 소자의 주파수 상향 변환 믹서 |

| US7181168B2 (en) * | 2002-04-02 | 2007-02-20 | Northrop Grumman Corporation | Radio frequency integrated circuit for loopback self-test |

| US7509111B2 (en) * | 2002-04-30 | 2009-03-24 | Infineon Technologies Ag | Integrated circuit having a mixer circuit |

| GB2389253B (en) * | 2002-05-31 | 2005-09-21 | Hitachi Ltd | Transmitter and semiconductor integrated circuit for communication |

| JP2005072031A (ja) * | 2003-08-22 | 2005-03-17 | Renesas Technology Corp | 高周波用半導体装置および通信用電子部品並びに無線通信システム |

| KR100783492B1 (ko) | 2004-07-31 | 2007-12-11 | 인티그런트 테크놀로지즈(주) | 차동증폭회로 및 이를 포함한 믹서회로 |

| KR100825813B1 (ko) | 2007-05-08 | 2008-04-29 | 삼성전자주식회사 | 직접 변환 수신기에 사용되는 믹서 |

-

2009

- 2009-12-21 KR KR1020090128512A patent/KR101271432B1/ko active IP Right Grant

-

2010

- 2010-07-16 US US12/837,807 patent/US8358998B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20070106009A (ko) * | 2005-01-21 | 2007-10-31 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 저잡음 혼합기 회로, 잡음 감소 회로, 수신기 회로,고주파수 수신기 및 잡음 감소 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110151820A1 (en) | 2011-06-23 |

| KR20110071843A (ko) | 2011-06-29 |

| US8358998B2 (en) | 2013-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6947720B2 (en) | Low noise mixer circuit with improved gain | |

| Gupta et al. | Analysis and design of monolithic, high PSR, linear regulators for SoC applications | |

| US6748204B1 (en) | Mixer noise reduction technique | |

| JP2651920B2 (ja) | 正確なデューティサイクルを有するデータクロック発振器 | |

| US10998862B2 (en) | Temperature compensated oscillator | |

| CN107645300B (zh) | 一种电流复用低功耗射频接收机 | |

| US7898332B2 (en) | Semiconductor integrated circuit device | |

| Ng et al. | A 1-V 17-GHz 5-mW CMOS quadrature VCO based on transformer coupling | |

| KR101271432B1 (ko) | 주파수 혼합기 | |

| US20120249250A1 (en) | Quadrature Voltage Controlled Oscillator | |

| KR100487813B1 (ko) | 상보 소자를 이용한 싱글엔드형 차동 회로 | |

| US6150885A (en) | Transconductance amplifier with wideband noise filtering | |

| Nguyen et al. | Ultralow-power Ku-band dual-feedback Armstrong VCO with a wide tuning range | |

| CN206948297U (zh) | 用于接收输入信号的电路 | |

| CN107070405B (zh) | 一种振荡器装置 | |

| Debono et al. | A 900 MHz, 0.9 V low-power CMOS downconversion mixer | |

| Alaybeyoglu et al. | Frequency agile filter structure improved by MOS-only technique | |

| Floyd | A CMOS wireless interconnect system for multigigahertz clock distribution | |

| KR20100079080A (ko) | 길버트 셀 타입 믹서 | |

| KR100492280B1 (ko) | 표준 3중 웰 씨모스 공정에서 구현된 수직형 바이폴라정션 트랜지스터를 전류 소오스로 사용하는 회로 | |

| US20040160246A1 (en) | Frequency converter having low supply voltage | |

| KR100618354B1 (ko) | 교차 연결된 트랜지스터를 이용하는 초광대역 필터 | |

| US6603964B1 (en) | Mixer with reduced carrier feedthrough | |

| Wang et al. | The 1-V 24-GHz low-voltage low-power current-mode transmitter in 130-nm CMOS technology | |

| Raja et al. | A low power fully differential RF receiver front-end for 2.4 GHz wireless sensor networks |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20160427 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20170427 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20180426 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20190425 Year of fee payment: 7 |