JP7403972B2 - イメージセンサ - Google Patents

イメージセンサ Download PDFInfo

- Publication number

- JP7403972B2 JP7403972B2 JP2019090581A JP2019090581A JP7403972B2 JP 7403972 B2 JP7403972 B2 JP 7403972B2 JP 2019090581 A JP2019090581 A JP 2019090581A JP 2019090581 A JP2019090581 A JP 2019090581A JP 7403972 B2 JP7403972 B2 JP 7403972B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- photodiode group

- pixels

- photodiodes

- photodiode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012546 transfer Methods 0.000 claims description 107

- 238000009792 diffusion process Methods 0.000 claims description 25

- 239000012535 impurity Substances 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 80

- 238000010586 diagram Methods 0.000 description 24

- 230000000875 corresponding effect Effects 0.000 description 22

- 238000002955 isolation Methods 0.000 description 22

- 238000005070 sampling Methods 0.000 description 10

- 230000006870 function Effects 0.000 description 9

- 238000012545 processing Methods 0.000 description 9

- 239000004065 semiconductor Substances 0.000 description 6

- 230000002596 correlated effect Effects 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 238000000034 method Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 101100328883 Arabidopsis thaliana COL1 gene Proteins 0.000 description 1

- 101100328886 Caenorhabditis elegans col-2 gene Proteins 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14645—Colour imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14641—Electronic components shared by two or more pixel-elements, e.g. one amplifier shared by two pixel elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

- H01L27/14607—Geometry of the photosensitive area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/59—Control of the dynamic range by controlling the amount of charge storable in the pixel, e.g. modification of the charge conversion ratio of the floating node capacitance

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/79—Arrangements of circuitry being divided between different or multiple substrates, chips or circuit boards, e.g. stacked image sensors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/1461—Pixel-elements with integrated switching, control, storage or amplification elements characterised by the photosensitive area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14621—Colour filter arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14627—Microlenses

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

Description

2、3、10、100、1010 イメージセンサ

11、110、200、300、400、500、600 ピクセルアレイ

12、120 ロードライバ

13 カラムドライバ

14 タイミングコントローラ

15、130 リードアウト回路

20 イメージプロセッサ

30 客体

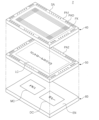

40、70 第1層

50、80 第2層

60 第3層

131 サンプリング回路

132 アナログ-デジタルコンバータ

210、310、410、510、610 第1ピクセル

220、320、420、520、620 第2ピクセル

230、330、430、530、630 第3ピクセル

240、340、440、540、640 第4ピクセル

301 第1素子分離膜

302 第2素子分離膜

311、321、331、341、431、441、531、541 マイクロレンズ

313、323、333、343、433、443、533、543 カラーフィルター

315、325、335、345、435、445、535、545 ピクセル回路

401、501 素子分離膜

611、621、631、641 第1連結ライン

612、622、632、642 第2連結ライン

613、614、623、624、633、634、643、644 中間ライン

1000 コンピュータ装置

1020 入出力装置

1030 メモリ

1040 プロセッサ

1050 ポート

1060 バス

CL1 第1素子連結層

CL2 第2素子連結層

CL 素子連結層

CM 電荷移動層

PD1 第1フォトダイオード

PD2 第2フォトダイオード

PD3 第3フォトダイオード

PD4 第4フォトダイオード

PG1 第1フォトダイオードグループ

PG2 第2フォトダイオードグループ

Claims (17)

- 第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分され、1つのカラーフィルタを共有する複数のフォトダイオードを含み、第1フォトダイオードグループ及び第2フォトダイオードグループのうちの少なくとも1つが、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに隣接して配置される2つ以上の前記フォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、1つの前記ピクセルにおいて前記第1フォトダイオードグループと前記第2フォトダイオードグループのうちの少なくとも1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードの下部に配置された素子連結層と、前記素子連結層の下部に配置されたピクセル回路とを含み、

前記素子連結層は、前記複数のフォトダイオードのうちの少なくとも一部を互いに連結して前記第1フォトダイオードグループ及び前記第2フォトダイオードグループを提供し、

前記コントロールロジックは、前記複数のピクセルのそれぞれにおいて前記第1フォトダイオードグループに連結された第1転送トラジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記複数のピクセルのそれぞれにおいて前記第2フォトダイオードグループに連結された第2転送トラジスタをターンオンさせて、前記第1フォトダイオードグループと前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出し、

前記コントロールロジックは、前記第1ピクセル電圧を検出した後、前記和のピクセル電圧を検出する前に前記第1転送トラジスタ及び前記第2転送トラジスタに連結され、電荷が蓄積されるフローティングディフュージョンをリセットしないことを特徴とするイメージセンサ。 - 前記ピクセル回路は、前記フローティングディフュージョンに蓄積された電荷に対応する電圧を生成する駆動トランジスタ、前記駆動トランジスタが生成した電圧を前記コントロールロジックに出力する選択トランジスタ、及び前記フローティングディフュージョンをリセットするリセットトランジスタを含むことを特徴とする請求項1に記載のイメージセンサ。

- 前記コントロールロジックは、前記第1ピクセル電圧及び前記第2ピクセル電圧を用いて自動焦点機能を提供することを特徴とする請求項1に記載のイメージセンサ。

- 前記コントロールロジックは、前記ピクセル電圧を用いてイメージデータを生成することを特徴とする請求項1に記載のイメージセンサ。

- 前記素子連結層は、N型不純物でドープされた領域であることを特徴とする請求項1に記載のイメージセンサ。

- 前記複数のピクセルのうちの互いに隣接する一部のピクセルに含まれる前記素子連結層は、互いに異なる面積または形状を有することを特徴とする請求項1に記載のイメージセンサ。

- 前記複数のピクセルのうちの少なくとも1つにおいて、前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに異なる大きさの受光面積を有することを特徴とする請求項1に記載のイメージセンサ。

- 前記複数のピクセルのうちの少なくとも1つにおいて、前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに同一の大きさの受光面積を有することを特徴とする請求項1に記載のイメージセンサ。

- 第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分され、1つのカラーフィルタを共有する複数のフォトダイオードを含み、第1フォトダイオードグループ及び第2フォトダイオードグループのうちの少なくとも1つが、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに隣接して配置される2つ以上の前記フォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、1つの前記ピクセルにおいて前記第1フォトダイオードグループと前記第2フォトダイオードグループのうちの少なくとも1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記コントロールロジックは、前記複数のピクセルのそれぞれにおいて前記第1フォトダイオードグループに連結された第1転送トラジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記複数のピクセルのそれぞれにおいて前記第2フォトダイオードグループに連結された第2転送トラジスタをターンオンさせて、前記第1フォトダイオードグループと前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出し、

前記コントロールロジックは、前記第1ピクセル電圧を検出した後、前記和のピクセル電圧を検出する前に前記第1転送トラジスタ及び前記第2転送トラジスタに連結され、電荷が蓄積されるフローティングディフュージョンをリセットせず、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードにそれぞれ連結された複数の転送トランジスタ、及び前記複数の転送トランジスタのうちの少なくとも一部のゲート電極層を互いに連結して、前記複数のフォトダイオードを前記第1フォトダイオードグループと前記第2フォトダイオードグループとに分離する連結ラインを有することを特徴とするイメージセンサ。 - 前記複数のピクセルのうちの互いに隣接する一部のピクセルにおいて、前記第1フォトダイオードグループは、互いに異なる位置に設けられることを特徴とする請求項9に記載のイメージセンサ。

- 前記連結ラインは、前記第1フォトダイオードグループを提供する第1連結ライン、及び前記第2フォトダイオードグループを提供する第2連結ラインを含むことを特徴とする請求項9に記載のイメージセンサ。

- 前記コントロールロジックは、

前記第1連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、

前記第2連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループ及び前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、

前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出することを特徴とする請求項11に記載のイメージセンサ。 - 前記コントロールロジックは、前記ピクセル電圧を用いてイメージデータを生成し、前記第1ピクセル電圧及び前記第2ピクセル電圧を用いて自動焦点機能を提供することを特徴とする請求項12に記載のイメージセンサ。

- 前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに同一の大きさの受光面積を有することを特徴とする請求項9に記載のイメージセンサ。

- 前記コントロールロジックは、前記複数のピクセルのうちの少なくとも一部から互いに異なる方向への自動焦点機能を提供するための情報を獲得することを特徴とする請求項1に記載のイメージセンサ。

- 第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分された複数のフォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、前記複数のピクセルのうちの1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記第1フォトダイオードグループ及び前記第2フォトダイオードグループのうちの少なくとも1つは、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに隣接する2つ以上のフォトダイオードを含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードの下部に配置され、前記複数のフォトダイオードのうちの少なくとも一部を互いに連結して前記複数のフォトダイオードを前記第1フォトダイオードグループと前記第2フォトダイオードグループとに区分する素子連結層、及び前記素子連結層の下に配置されるピクセル回路を含み、

前記ピクセル回路は、前記第1フォトダイオードグループに連結された第1転送トランジスタ、前記第2フォトダイオードグループに連結された第2転送トランジスタ、及び前記第1転送トランジスタと前記第2転送トランジスタとに連結されたフローティングディフュージョンを含み、

前記コントロールロジックは、前記第1転送トランジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記第2転送トランジスタをターンオンさせて、前記第1フォトダイオードグループ及び前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出することを特徴とするイメージセンサ。 - 第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分された複数のフォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、前記複数のピクセルのうちの1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記第1フォトダイオードグループ及び前記第2フォトダイオードグループのうちの少なくとも1つは、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに隣接する2つ以上のフォトダイオードを含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードにそれぞれ連結された複数の転送トランジスタ、及び前記複数の転送トランジスタのゲート電極層のうちの少なくとも一部を互いに連結して、前記複数のフォトダイオードを前記第1フォトダイオードグループと前記第2フォトダイオードグループとに区分する複数の連結ラインを含み、

前記連結ラインは、前記第1フォトダイオードグループに含まれる前記フォトダイオードを互いに連結する第1連結ライン、及び前記第2フォトダイオードグループに含まれる前記フォトダイオードを互いに連結する第2連結ラインを含み、

前記コントロールロジックは、前記第1連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記第2連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループ及び前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出することを特徴とするイメージセンサ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2018-0085245 | 2018-07-23 | ||

| KR1020180085245A KR102614851B1 (ko) | 2018-07-23 | 2018-07-23 | 이미지 센서 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020017941A JP2020017941A (ja) | 2020-01-30 |

| JP2020017941A5 JP2020017941A5 (ja) | 2022-05-19 |

| JP7403972B2 true JP7403972B2 (ja) | 2023-12-25 |

Family

ID=69161340

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019090581A Active JP7403972B2 (ja) | 2018-07-23 | 2019-05-13 | イメージセンサ |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US11094735B2 (ja) |

| JP (1) | JP7403972B2 (ja) |

| KR (1) | KR102614851B1 (ja) |

| CN (1) | CN110753193B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019140528A (ja) * | 2018-02-09 | 2019-08-22 | ソニーセミコンダクタソリューションズ株式会社 | 撮像装置、及び電子機器 |

| KR102614851B1 (ko) | 2018-07-23 | 2023-12-19 | 삼성전자주식회사 | 이미지 센서 |

| KR20210054629A (ko) * | 2019-11-05 | 2021-05-14 | 삼성전자주식회사 | 이미지 센서 |

| WO2021102366A1 (en) * | 2019-11-20 | 2021-05-27 | Gigajot Technology, Inc. | Scalable-pixel-size image sensor |

| KR20220007261A (ko) * | 2020-07-10 | 2022-01-18 | 삼성전자주식회사 | 이미지 센서 |

| US12101554B2 (en) | 2021-11-26 | 2024-09-24 | Samsung Electronics Co., Ltd. | Method and apparatus for performing autofocusing using summed signals |

| US11979675B2 (en) * | 2022-04-25 | 2024-05-07 | Sony Semiconductor Solutions Corporation | Image sensing device with event based vision sensor pixels and imaging pixels |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017184181A (ja) | 2016-03-31 | 2017-10-05 | キヤノン株式会社 | 撮像素子 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8059174B2 (en) | 2006-05-31 | 2011-11-15 | Ess Technology, Inc. | CMOS imager system with interleaved readout for providing an image with increased dynamic range |

| JP5300414B2 (ja) | 2008-10-30 | 2013-09-25 | キヤノン株式会社 | カメラ及びカメラシステム |

| JP5744545B2 (ja) * | 2011-01-31 | 2015-07-08 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| JP6039165B2 (ja) * | 2011-08-11 | 2016-12-07 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| JP2013084785A (ja) * | 2011-10-11 | 2013-05-09 | Sony Corp | 固体撮像装置、撮像装置 |

| JP2015012127A (ja) * | 2013-06-28 | 2015-01-19 | ソニー株式会社 | 固体撮像素子および電子機器 |

| JP2015216625A (ja) * | 2014-04-22 | 2015-12-03 | キヤノン株式会社 | 撮像素子及び撮像装置 |

| KR102268712B1 (ko) * | 2014-06-23 | 2021-06-28 | 삼성전자주식회사 | 자동 초점 이미지 센서 및 이를 포함하는 디지털 영상 처리 장치 |

| KR102286109B1 (ko) * | 2014-08-05 | 2021-08-04 | 삼성전자주식회사 | 이미지 픽셀, 이를 포함하는 이미지 센서, 및 이를 포함하는 이미지 처리 시스템 |

| JP2016058559A (ja) * | 2014-09-10 | 2016-04-21 | ソニー株式会社 | 固体撮像装置およびその駆動方法、並びに電子機器 |

| US10070088B2 (en) * | 2015-01-05 | 2018-09-04 | Canon Kabushiki Kaisha | Image sensor and image capturing apparatus for simultaneously performing focus detection and image generation |

| US9749556B2 (en) * | 2015-03-24 | 2017-08-29 | Semiconductor Components Industries, Llc | Imaging systems having image sensor pixel arrays with phase detection capabilities |

| GB2537421A (en) | 2015-04-17 | 2016-10-19 | Stmicroelectronics (Research & Development) Ltd | A pixel having a plurality of photodiodes |

| JP6470404B2 (ja) | 2015-05-22 | 2019-02-13 | オリンパス株式会社 | 撮像装置 |

| KR102374112B1 (ko) * | 2015-07-15 | 2022-03-14 | 삼성전자주식회사 | 오토 포커싱 픽셀을 포함하는 이미지 센서, 및 이를 포함하는 이미지 처리 시스템 |

| KR20170019542A (ko) * | 2015-08-11 | 2017-02-22 | 삼성전자주식회사 | 자동 초점 이미지 센서 |

| KR102437162B1 (ko) | 2015-10-12 | 2022-08-29 | 삼성전자주식회사 | 이미지 센서 |

| KR20170056909A (ko) * | 2015-11-16 | 2017-05-24 | 삼성전자주식회사 | 이미지 센서 및 이를 포함하는 전자 장치 |

| JP2017194558A (ja) | 2016-04-20 | 2017-10-26 | オリンパス株式会社 | 撮像装置および撮像方法 |

| KR102591008B1 (ko) | 2016-05-23 | 2023-10-19 | 에스케이하이닉스 주식회사 | 이미지 센서 |

| US9936123B2 (en) | 2016-08-04 | 2018-04-03 | Omnivision Technologies, Inc. | Camera and method with widescreen image on nearly-square aspect ratio photosensor array |

| JP6778595B2 (ja) * | 2016-08-17 | 2020-11-04 | ルネサスエレクトロニクス株式会社 | 撮像素子 |

| US10038863B2 (en) * | 2016-08-17 | 2018-07-31 | Renesas Electronics Corporation | Image sensing device |

| US11082649B2 (en) * | 2017-06-02 | 2021-08-03 | Sony Semiconductor Solutions Corporation | Solid-state imaging device with pixels having an in-pixel capacitance |

| KR102614851B1 (ko) | 2018-07-23 | 2023-12-19 | 삼성전자주식회사 | 이미지 센서 |

-

2018

- 2018-07-23 KR KR1020180085245A patent/KR102614851B1/ko active IP Right Grant

-

2019

- 2019-03-04 US US16/291,345 patent/US11094735B2/en active Active

- 2019-05-13 JP JP2019090581A patent/JP7403972B2/ja active Active

- 2019-06-18 CN CN201910526394.7A patent/CN110753193B/zh active Active

-

2021

- 2021-07-08 US US17/370,724 patent/US11791365B2/en active Active

-

2023

- 2023-09-13 US US18/466,475 patent/US20230420481A1/en active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017184181A (ja) | 2016-03-31 | 2017-10-05 | キヤノン株式会社 | 撮像素子 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20200027914A1 (en) | 2020-01-23 |

| US11791365B2 (en) | 2023-10-17 |

| CN110753193B (zh) | 2024-04-12 |

| CN110753193A (zh) | 2020-02-04 |

| JP2020017941A (ja) | 2020-01-30 |

| US20210335879A1 (en) | 2021-10-28 |

| US20230420481A1 (en) | 2023-12-28 |

| US11094735B2 (en) | 2021-08-17 |

| KR20200010769A (ko) | 2020-01-31 |

| KR102614851B1 (ko) | 2023-12-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7403972B2 (ja) | イメージセンサ | |

| US11189651B2 (en) | Image sensor | |

| US10950640B2 (en) | Image sensor | |

| KR102543350B1 (ko) | 이미지 센서 | |

| US11637979B2 (en) | Image sensor using a boosting capacitor and a negative bias voltage | |

| US11658193B2 (en) | Image sensor | |

| CN112929585A (zh) | 图像传感器 | |

| US12087791B2 (en) | Image sensor | |

| US11552122B2 (en) | Image sensor and operating method | |

| US11652130B2 (en) | Image sensor and manufacturing method of the same | |

| US11575846B2 (en) | Image sensor configured to dynamically adjust conversion gain of a pixel in accordance with exposure time | |

| KR102656526B1 (ko) | 이미지 센서 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220511 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230623 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230627 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20231114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20231213 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7403972 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |