JP7316130B2 - 画像処理装置、画像処理装置の制御方法、プログラム - Google Patents

画像処理装置、画像処理装置の制御方法、プログラム Download PDFInfo

- Publication number

- JP7316130B2 JP7316130B2 JP2019131395A JP2019131395A JP7316130B2 JP 7316130 B2 JP7316130 B2 JP 7316130B2 JP 2019131395 A JP2019131395 A JP 2019131395A JP 2019131395 A JP2019131395 A JP 2019131395A JP 7316130 B2 JP7316130 B2 JP 7316130B2

- Authority

- JP

- Japan

- Prior art keywords

- image

- processing

- memory

- size

- stored

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T9/00—Image coding

- G06T9/002—Image coding using neural networks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T1/00—General purpose image data processing

- G06T1/60—Memory management

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T7/00—Image analysis

- G06T7/10—Segmentation; Edge detection

- G06T7/174—Segmentation; Edge detection involving the use of two or more images

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T7/00—Image analysis

- G06T7/97—Determining parameters from multiple pictures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06V—IMAGE OR VIDEO RECOGNITION OR UNDERSTANDING

- G06V10/00—Arrangements for image or video recognition or understanding

- G06V10/70—Arrangements for image or video recognition or understanding using pattern recognition or machine learning

- G06V10/764—Arrangements for image or video recognition or understanding using pattern recognition or machine learning using classification, e.g. of video objects

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06V—IMAGE OR VIDEO RECOGNITION OR UNDERSTANDING

- G06V10/00—Arrangements for image or video recognition or understanding

- G06V10/70—Arrangements for image or video recognition or understanding using pattern recognition or machine learning

- G06V10/77—Processing image or video features in feature spaces; using data integration or data reduction, e.g. principal component analysis [PCA] or independent component analysis [ICA] or self-organising maps [SOM]; Blind source separation

- G06V10/7715—Feature extraction, e.g. by transforming the feature space, e.g. multi-dimensional scaling [MDS]; Mappings, e.g. subspace methods

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06V—IMAGE OR VIDEO RECOGNITION OR UNDERSTANDING

- G06V10/00—Arrangements for image or video recognition or understanding

- G06V10/70—Arrangements for image or video recognition or understanding using pattern recognition or machine learning

- G06V10/82—Arrangements for image or video recognition or understanding using pattern recognition or machine learning using neural networks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/045—Combinations of networks

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Vision & Pattern Recognition (AREA)

- Evolutionary Computation (AREA)

- Artificial Intelligence (AREA)

- Multimedia (AREA)

- Computing Systems (AREA)

- Databases & Information Systems (AREA)

- General Health & Medical Sciences (AREA)

- Medical Informatics (AREA)

- Software Systems (AREA)

- Health & Medical Sciences (AREA)

- Image Processing (AREA)

- Complex Calculations (AREA)

- Image Analysis (AREA)

Description

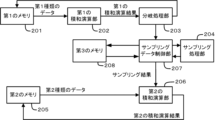

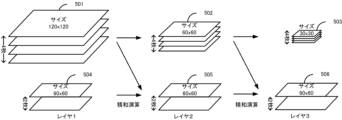

入力された画像の画像サイズを判定し、前記判定した画像サイズが第1のサイズより大きい場合には、当該入力された画像を第1のサイズに縮小処理をしてから第1のメモリに記憶するよう制御し、前記判定した画像サイズが前記第1のサイズ以下の場合には、当該入力された画像を前記縮小処理をせずに第1のメモリに記憶するよう制御する制御手段と、

前記第1のメモリに記憶された画像が前記第1のサイズより小さい場合には、拡大処理をしてから画像処理をし、前記第1のメモリに記憶された画像が前記第1のサイズの場合には、前記拡大処理をせずに前記画像処理をする第1の処理手段を有することを特徴とする。

以下では図面を参照しながら本発明の実施形態について詳細に説明する。

図1は、実施形態に対応するデータ処理装置100の一構成例を示すブロック図である。以下では、データ処理装置100として入力画像を処理する画像処理装置について説明するが、処理対象は画像に限らず、音声であってもよいし、その他の任意のセンサにより取得されたデータであってもよい。

Ai,j =B[i/r],[j/r] ・・・(式2)

Ai,j =Br'i+k,r'j+l ・・・(式3)

ここで、k、lはサンプリング位置の水平・垂直方向のオフセットを示す。r'はサンプリング倍率の逆数を示す整数であり、r'=(1/r)で計算される。式3によれば、サンプリング後の特徴画像は、サンプリング前の特徴画像の位置(k,l)を始点として間隔r'で水平・垂直方向にサンプリングした特徴画像となる。

上記の実施形態1ではダウンサンプリング時に補間処理を行うことなく単純にサンプリングする例を示したが、サンプリング時に補間処理を行っても良い。そこで本実施形態ではダウンサンプリング時に水平方向に平均値補間を施す例を示す。本実施形態では下記の式4に基づいてダウンサンプリングを行う。ダウンサンプリング以外の処理、および構成は実施例1と同様である。

実施形態2ではダウンサンプリング処理において水平方向に平均値補間する例を示したが、本実施形態では水平・垂直方向に平均値補間を施すダウンサンプリング処理を用いた例を示す。データ処理装置100の構成は実施形態1と同一であるので記載を省略する。

Ai,j =B[i/r+0.5],[j/r+0.5] ・・・(式7)

また、上述の実施形態において、サンプリング方法は限定されるものではない。ダウンサンプリング・アップサンプリング処理時にバイリニア補間、バイキュービック補間、Lanczos補間など、種々の補間処理を施しても良い。

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサがプログラムを読出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

Claims (13)

- 画像処理装置であって、

入力された画像の画像サイズを判定し、前記判定した画像サイズが第1のサイズより大きい場合には、当該入力された画像を第1のサイズに縮小処理をしてから第1のメモリに記憶するよう制御し、前記判定した画像サイズが前記第1のサイズ以下の場合には、当該入力された画像を前記縮小処理をせずに第1のメモリに記憶するよう制御する制御手段と、

前記第1のメモリに記憶された画像が前記第1のサイズより小さい場合には、拡大処理をしてから画像処理をし、前記第1のメモリに記憶された画像が前記第1のサイズの場合には、前記拡大処理をせずに前記画像処理をする第1の処理手段を有することを特徴とする画像処理装置。 - 前記第1の処理手段は、前記第1のメモリに記憶された画像と、第2のメモリに記憶された画像とを処理して、処理結果を前記第2のメモリに記憶し、

前記第2のメモリに記憶された画像は、前記第1のサイズを有することを特徴とする請求項1に記載の画像処理装置。 - 前記第1の処理手段は、前記第1のメモリに記憶された画像に対する処理を、前記第1のメモリから該画像を繰り返し読み出して行うことを特徴とする請求項2に記載の画像処理装置。

- 第3のメモリに記憶された画像を処理する第2の処理手段を更に備え、

前記入力された画像は、第2の処理手段により処理された画像であることを特徴とする請求項2または3に記載の画像処理装置。 - 前記第2の処理手段は処理結果を前記第3のメモリに記憶し、

前記画像処理装置は、

前記第2のメモリに記憶された前記第1の処理手段の処理結果と、前記第3のメモリに記憶された前記第2の処理手段の処理結果とに対し、活性化処理及びプーリング処理を行う後処理手段を更に備え、

前記後処理手段によるそれぞれの後処理結果が、前記第2のメモリ及び前記第3のメモリのうちの対応するメモリに記憶され、

前記第2の処理手段は、前記第3のメモリに記憶された後処理結果を処理し、

前記制御手段は、前記第2の処理手段により処理された前記後処理結果を前記入力された画像とする、ことを特徴とする請求項4に記載の画像処理装置。 - 前記第1の処理手段、及び、前記第2の処理手段は、積和演算を実行することを特徴とする請求項5に記載の画像処理装置。

- 前記積和演算は、畳み込みニューラルネットワークの畳み込み演算であることを特徴とする請求項6に記載の画像処理装置。

- 画像サイズを変換する変換手段を更に備え、

前記制御手段は、

前記入力された画像の前記画像サイズが前記第1のサイズより大きい場合に、前記変換手段に前記入力された画像を前記第1のサイズに縮小させ、

前記第1のメモリに記憶された画像が前記第1のサイズより小さい場合、前記第1のメモリに記憶された画像を前記第1のサイズに拡大させて、前記第1の処理手段に提供する

ことを特徴とする、請求項1から7のいずれか1項に記載の画像処理装置。 - 前記変換手段は、ダウンサンプリングにより前記画像サイズを縮小することを特徴とする請求項8に記載の画像処理装置。

- 前記変換手段は、水平方向の補間処理を伴うダウンサンプリングにより前記画像サイズを縮小することを特徴とする請求項9に記載の画像処理装置。

- 前記変換手段は、水平方向及び垂直方向の平均値補間処理を伴うダウンサンプリングにより画像サイズを縮小することを特徴とする請求項9に記載の画像処理装置。

- 画像処理装置の制御方法であって、

制御手段が、入力された画像の画像サイズを判定し、前記判定した画像サイズが第1のサイズより大きい場合は、当該入力された画像を第1のサイズに縮小処理をしてから第1のメモリに記憶するよう制御し、前記判定した画像サイズが前記第1のサイズ以下の場合には、当該入力された画像を前記縮小処理をせずに第1のメモリに記憶するよう制御する制御工程と、

第1の処理手段が、前記第1のメモリに記憶された画像が前記第1のサイズより小さい場合には、拡大処理をしてから画像処理をし、前記第1のメモリに記憶された画像が前記第1のサイズの場合には、前記拡大処理をせずに前記画像処理をする第1の処理工程と、

を含むことを特徴とする画像処理装置の制御方法。 - コンピュータを請求項1から11のいずれか1項に記載の画像処理装置の各手段として機能させるためのプログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019131395A JP7316130B2 (ja) | 2019-07-16 | 2019-07-16 | 画像処理装置、画像処理装置の制御方法、プログラム |

| US16/925,801 US11514614B2 (en) | 2019-07-16 | 2020-07-10 | Image processing apparatus, method of controlling image processing apparatus, and non-transitory computer-readable storage medium |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019131395A JP7316130B2 (ja) | 2019-07-16 | 2019-07-16 | 画像処理装置、画像処理装置の制御方法、プログラム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2021015569A JP2021015569A (ja) | 2021-02-12 |

| JP2021015569A5 JP2021015569A5 (ja) | 2022-07-27 |

| JP7316130B2 true JP7316130B2 (ja) | 2023-07-27 |

Family

ID=74341002

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019131395A Active JP7316130B2 (ja) | 2019-07-16 | 2019-07-16 | 画像処理装置、画像処理装置の制御方法、プログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US11514614B2 (ja) |

| JP (1) | JP7316130B2 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005242675A (ja) | 2004-02-26 | 2005-09-08 | Seiko Epson Corp | 画像サイズ縮小処理方法及び画像サイズ拡大処理方法 |

| JP2007109204A (ja) | 2005-09-15 | 2007-04-26 | Fujitsu Ltd | 画像処理装置及び画像処理方法 |

| WO2016039167A1 (ja) | 2014-09-12 | 2016-03-17 | ソニー株式会社 | 画像処理装置、画像処理方法、及び、プログラム |

| JP7302331B2 (ja) | 2019-06-26 | 2023-07-04 | 味の素株式会社 | 樹脂組成物 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3397670B2 (ja) * | 1998-01-09 | 2003-04-21 | キヤノン株式会社 | 記録装置および方法 |

| JP2001146010A (ja) * | 1999-11-18 | 2001-05-29 | Nec Corp | インクジェット記録ヘッド |

| US7400779B2 (en) * | 2004-01-08 | 2008-07-15 | Sharp Laboratories Of America, Inc. | Enhancing the quality of decoded quantized images |

| JP4605715B2 (ja) * | 2006-06-14 | 2011-01-05 | Kddi株式会社 | 多視点画像圧縮符号化方法、装置及びプログラム |

| US8509565B2 (en) * | 2008-12-15 | 2013-08-13 | National Tsing Hua University | Optimal multi-resolution blending of confocal microscope images |

| JP6365258B2 (ja) | 2014-11-19 | 2018-08-01 | 株式会社デンソー | 演算処理装置 |

| US10102664B1 (en) * | 2014-12-03 | 2018-10-16 | Charles Schwab & Co., Inc. | System and method for causing graphical information to be rendered |

| JP6777993B2 (ja) * | 2016-01-29 | 2020-10-28 | キヤノン株式会社 | 画像処理装置、画像処理方法及びプログラム |

| JP6856999B2 (ja) * | 2016-09-23 | 2021-04-14 | キヤノン株式会社 | 画像処理装置、画像処理方法及びプログラム |

| JP7016712B2 (ja) * | 2018-02-02 | 2022-02-07 | キヤノン株式会社 | 撮像装置、撮像装置の制御方法、およびプログラム |

| JP7249766B2 (ja) * | 2018-12-14 | 2023-03-31 | キヤノン株式会社 | 情報処理装置、システム、情報処理装置の制御方法、及び、プログラム |

-

2019

- 2019-07-16 JP JP2019131395A patent/JP7316130B2/ja active Active

-

2020

- 2020-07-10 US US16/925,801 patent/US11514614B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005242675A (ja) | 2004-02-26 | 2005-09-08 | Seiko Epson Corp | 画像サイズ縮小処理方法及び画像サイズ拡大処理方法 |

| JP2007109204A (ja) | 2005-09-15 | 2007-04-26 | Fujitsu Ltd | 画像処理装置及び画像処理方法 |

| WO2016039167A1 (ja) | 2014-09-12 | 2016-03-17 | ソニー株式会社 | 画像処理装置、画像処理方法、及び、プログラム |

| JP7302331B2 (ja) | 2019-06-26 | 2023-07-04 | 味の素株式会社 | 樹脂組成物 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2021015569A (ja) | 2021-02-12 |

| US20210019917A1 (en) | 2021-01-21 |

| US11514614B2 (en) | 2022-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Dai et al. | Softcuts: a soft edge smoothness prior for color image super-resolution | |

| US9652830B2 (en) | Method and apparatus for performing hierarchical super-resolution of an input image | |

| JP4162610B2 (ja) | 複数の低解像度の画像を使用して解像度が向上された画像を生成するための方法 | |

| US20180253641A1 (en) | Arithmetic processing apparatus and control method therefor | |

| JP5517954B2 (ja) | 変換の高速でメモリ効率の良い実施のための方法 | |

| Chen | VLSI implementation of an adaptive edge-enhanced image scalar for real-time multimedia applications | |

| JP2013518336A (ja) | 入力画像から増加される画素解像度の出力画像を生成する方法及びシステム | |

| Singh et al. | Survey on single image based super-resolution—implementation challenges and solutions | |

| WO2014114635A1 (en) | Method and apparatus for performing super-resolution of single images | |

| JP7165018B2 (ja) | 情報処理装置、情報処理方法 | |

| CN108876716A (zh) | 超分辨率重建方法及装置 | |

| JP7402623B2 (ja) | フィルタ処理装置及びその制御方法 | |

| JP7316130B2 (ja) | 画像処理装置、画像処理装置の制御方法、プログラム | |

| WO2019090876A1 (zh) | 一种基于直线扩展收缩模式的图像缩放方法 | |

| JP2005326977A (ja) | 画像拡大装置、及びプログラム | |

| CN116341630A (zh) | 神经网络处理 | |

| Siva et al. | A low cost high performance VLSI architecture for image scaling in multimedia applications | |

| CN110619668B (zh) | 一种图像抽象方法、装置及终端设备 | |

| KR20200143274A (ko) | 데이터 처리장치 및 그 제어 방법 | |

| JP7114321B2 (ja) | データ処理装置及びその方法 | |

| CN112241740A (zh) | 一种特征提取方法及装置 | |

| JP2019197324A (ja) | 画像処理装置、画像処理方法 | |

| CN113780300B (zh) | 图像反池化方法、装置、计算机设备和存储介质 | |

| CN111626935B (zh) | 像素图缩放方法、游戏内容生成方法及装置 | |

| CN112017113B (zh) | 图像处理方法及装置、模型训练方法及装置、设备及介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20210103 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220719 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230616 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230714 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7316130 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |