JP6996497B2 - 情報処理装置、及び情報処理方法 - Google Patents

情報処理装置、及び情報処理方法 Download PDFInfo

- Publication number

- JP6996497B2 JP6996497B2 JP2018514172A JP2018514172A JP6996497B2 JP 6996497 B2 JP6996497 B2 JP 6996497B2 JP 2018514172 A JP2018514172 A JP 2018514172A JP 2018514172 A JP2018514172 A JP 2018514172A JP 6996497 B2 JP6996497 B2 JP 6996497B2

- Authority

- JP

- Japan

- Prior art keywords

- neural network

- constraint

- unit

- hardware

- information processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/086—Learning methods using evolutionary algorithms, e.g. genetic algorithms or genetic programming

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/049—Temporal neural networks, e.g. delay elements, oscillating neurons or pulsed inputs

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/10—Interfaces, programming languages or software development kits, e.g. for simulating neural networks

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/10—Interfaces, programming languages or software development kits, e.g. for simulating neural networks

- G06N3/105—Shells for specifying net layout

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/08—Learning methods

- G06N3/082—Learning methods modifying the architecture, e.g. adding, deleting or silencing nodes or connections

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Life Sciences & Earth Sciences (AREA)

- Health & Medical Sciences (AREA)

- Software Systems (AREA)

- Computing Systems (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Computational Linguistics (AREA)

- Data Mining & Analysis (AREA)

- Evolutionary Computation (AREA)

- General Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Artificial Intelligence (AREA)

- General Engineering & Computer Science (AREA)

- Evolutionary Biology (AREA)

- Physiology (AREA)

- Bioinformatics & Computational Biology (AREA)

- Bioinformatics & Cheminformatics (AREA)

- Neurology (AREA)

- User Interface Of Digital Computer (AREA)

Description

<1-1.背景>

<1-2.構成例>

<1-3.動作例>

<1-4.効果>

<<2.第二の実施形態>>

<2-1.構成例>

<2-2.動作例>

<2-3.効果>

<<3.変形例>>

<3-1.変形例1>

<3-2.変形例2>

<<4.ハードウェア構成例>>

<<5.むすび>>

<1-1.背景>

本開示の第一の実施形態に係る情報処理装置について説明する前に、まず、本実施形態の創作に至った背景を説明する。

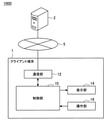

図2を参照しながら、本開示の第一の実施形態の構成例を説明する。図2は、本開示の第一の実施形態に係る情報処理システムの構成例を説明するための説明図である。本実施形態に係る情報処理システム1000は、ユーザによるニューラルネットワークの設計のための情報処理システムであり、例えばビジュアルプログラミングにより、ニューラルネットワークを設計することが可能なツールを提供してもよい。

続いて、本実施形態に係るクライアント端末1について詳細に説明する。図2に示すように、本実施形態に係るクライアント端末1は、制御部10、通信部12、表示部14、及び操作部16を備える情報処理装置である。なお、クライアント端末1は、例えばPC(Personal Computer)、タブレットPC等であってもよい。

以上、本実施形態に係るクライアント端末1の構成例を説明した。続いて、図5を参照して、本実施形態に係るサーバ2の構成例を説明する。図5は、本実施形態に係るサーバ2の構成例を説明するための説明図である。図5に示すように、サーバ2は、制御部20、通信部22、及び記憶部24を備える情報処理装置である。

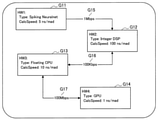

・ニューロチップが処理可能なノード数は10以下である

・ニューロチップが処理可能なレイヤーはコンボリューションレイヤーのみである

・ニューロチップとCPUとの間の通信速度は所定の速度である

・CPUが利用可能なRAMは所定値以下である

・CPUとGPUとの間の通信速度は所定の速度である

・GPUはニューロチップと直接接続できない

・CPUは整数演算のみ可能(浮動小数点演算不可能)である

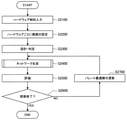

以上、本実施形態による情報処理システム1000の構成例について説明した。続いて、本実施形態による情報処理システム1000の動作例について、図6~10を参照して説明する。以下では、まず情報処理システム1000の処理フローについて図6、図7を参照して説明した後、本実施形態においてクライアント端末1に表示される画面遷移例について図8~10を参照して説明する。

図6は、本実施形態による情報処理システム1000の処理フロー例を示すフローチャート図である。図6に示すフローチャートは、本実施形態に係る動作のうち、特にニューラルネットワークの設計に係る処理フローを示す。

図7は、本実施形態による情報処理システム1000の処理フロー例を示すフローチャート図である。図7に示すフローチャートは、本実施形態に係る動作のうち、特にニューラルネットワークの設計の変更に係る処理フローを示す。例えば以下に説明する処理フローは、図6に示したフローチャートの処理により設計されたニューラルネットワークの設計を変更する際の処理フローであってもよい。

以上、本実施形態による情報処理システム1000の処理フローを説明した。続いて、図7を参照して説明した処理フローにおいて、クライアント端末1に表示される画面の遷移例を図3、4及び図8~10を参照して説明する。図8~10は、本実施形態に係るクライアント端末1に表示される画面例を示す説明図である。なお、図8~10は図4を参照して説明した設計画面に含まれるニューラルネットワークの設計変更に係る画面遷移の一例である。また、以下では、図7に示した処理ステップを適宜参照しながら説明を行う。

以上説明したように、本開示の第一の実施形態によれば、複数のハードウェアに係る制約に基づき、ニューラルネットワークが当該制約を満たすか否かを判定し、例えばユーザに判定結果に基づく警告画面を提供する。係る構成により、複数のハードウェアによる処理に適合したニューラルネットワークをより効率的に設計することが可能である。また、本実施形態によれば、変更されたニューラルネットワークが当該制約を満たさない場合には、制約を満たすように自動的に再配置が行われることで、制約を満たしたニューラルネットワークの設計を支援することが可能である。

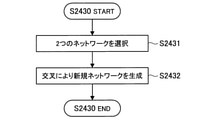

以上、本開示の第一の実施形態を説明した。続いて、本開示の第二の実施形態を説明する。本開示の第二の実施形態は、設計されたニューラルネットワークの評価結果に基づいて、ネットワーク構造の異なる別のニューラルネットワークを生成する。また、本開示の第二の実施形態は、生成されたニューラルネットワークの評価結果に基づいて、評価済のニューラルネットワークに係るパレート最適解を更新する。さらに、本開示の第二の実施形態は、ネットワークの生成とパレート最適解の更新を繰り返すことで、効率の良いネットワーク構造を探索することが可能である。

図11は、本開示の第二の実施形態に係るサーバ2-2の構成例を説明するための説明図である。図11に示すように、サーバ2-2は、制御部21、通信部22、及び記憶部24を備える情報処理装置である。図11に示すように、本実施形態に係るサーバ2―2は、制御部21の機能構成が図5の制御部20の機能構成と一部異なる点で、図5のサーバ2と異なる。なお、図11に示す各構成のうち、図5に示した各構成と実質的に同様の構成については同一の符号を付してあるため、説明を省略する。以下では、本実施形態に係る制御部21が有する判定部213、生成部217、及び評価部218、としての機能について説明する。

以上、本実施形態に係るサーバ2-2の構成例について説明した。続いて、本実施形態の動作例について、図12~15を参照して説明する。

以上説明したように、本開示の第二の実施形態によれば、設計されたニューラルネットワークの評価結果に基づいて、ネットワーク構造の異なる別のニューラルネットワークを生成することができる。また、本実施形態は、ネットワークの生成と、パレート最適解の更新を繰り返すことで、効率の良いネットワーク構造を探索することが可能である。また、本実施形態において、生成されるニューラルネットワークは、判定部213により、複数のハードウェアに係る制約を満たすと判定されたニューラルネットワークである。したがって、本実施形態によれば、複数のハードウェアによる処理に適合し、かつ効率の良いネットワーク構造を探索することが可能である。

以上、本開示の実施形態を説明した。以下では、本開示に係る幾つかの変形例を説明する。なお、以下に説明する各変形例は、単独で各実施形態に適用されてもよいし、組み合わせで各実施形態に適用されてもよい。また、各変形例は、上記実施形態で説明した構成に代えて適用されてもよいし、上記実施形態で説明した構成に対して追加的に適用されてもよい。

上記実施形態ではビジュアルプログラミングによりニューラルネットワークの設計が行われる例を説明したが、本技術は係る例に限定されない。例えば、本技術に係るニューラルネットワークの設計は、テキストによるプログラミングや、CUI(Command User Interface)上の操作により行われてもよい。また、ハードウェアに係る制約や、ハードウェアとレイヤーの対応付けも、上記で説明された例に限定されず、テキスト、またはCUIにより入力されてもよい。

また、上記実施形態では、図2、図5、及び図11を参照してクライアント端末1、サーバ2、及びサーバ2-2が有する機能を説明したが、本技術は係る例に限定されない。上記実施形態で説明したクライアント端末1の機能をサーバ2、またはサーバ2-2が有してもよいし、上記実施形態で説明したサーバ2、またはサーバ2-2の機能をクライアント端末1が有してもよい。

以上、本開示の各実施形態を説明した。上述した表示制御処理、通信制御処理、取得処理、判定処理、設計制御処理、学習処理、認識処理、ネットワーク生成処理、評価結果取得処理等の情報処理は、ソフトウェアと、クライアント端末1、サーバ2、2-2との協働により実現される。以下では、本実施形態に係るサーバ2のハードウェア構成例について説明する。

以上、説明したように、本開示の実施形態によれば、複数のハードウェアによる処理に適合したニューラルネットワークをより効率的に設計することが可能である。

(1)

複数のハードウェアに係る制約を取得する取得部と、

ニューラルネットワークが、前記制約を満たすか否か判定を行う判定部と、

を備える情報処理装置。

(2)

ユーザの入力に基づく前記ニューラルネットワークの設計を制御する設計制御部をさらに備える、前記(1)に記載の情報処理装置。

(3)

前記判定部は、前記設計制御部により前記ニューラルネットワークが変更された場合に、前記判定を行う、前記(2)に記載の情報処理装置。

(4)

前記設計制御部は、前記判定部により、前記制約を満たさないと判定された場合に、前記制約を満たすように、前記変更に係るレイヤーの再配置を行う、前記(3)に記載の情報処理装置。

(5)

前記設計制御部は、前記判定部により、前記制約を満たすと判定された場合に、前記ニューラルネットワークを構築するプログラムを作成する、前記(2)~(4)のいずれか一項に記載の情報処理装置。

(6)

前記判定部により、前記制約を満たさないと判定された場合に、前記制約が満たされないことを示す警告画面を表示させる、表示制御部をさらに備える、前記(1)~(5)のいずれか一項に記載の情報処理装置。

(7)

前記警告画面は、前記ニューラルネットワークにおいて、前記制約を満たない部分を提示する、前記(6)に記載の情報処理装置。

(8)

前記制約に基づいて、前記ニューラルネットワークにおけるレイヤーごとに、前記レイヤーに対応付けられたハードウェアに応じた学習を行う学習部をさらに備える、前記(1)~(7)のいずれか一項に記載の情報処理装置。

(9)

前記判定部により前記制約を満たすと判定されたニューラルネットワークから、ネットワーク構造の異なる別のニューラルネットワークを生成する生成部と、

生成されたニューラルネットワークの評価結果を取得する評価部と、をさらに備え、

前記評価部は、生成されたニューラルネットワークの評価結果に基づいて、評価済のニューラルネットワークに係るパレート最適解を更新し、

前記生成部は、前記パレート最適解に係るニューラルネットワークから、ネットワーク構造の異なる別のニューラルネットワークを生成する、

前記(1)~(8)のいずれか一項に記載の情報処理装置。

(10)

前記判定部は、前記生成部により生成されるニューラルネットワークが、前記制約を満たすか否か判定を行い、

前記生成部は、前記判定部により前記制約を満たすと判定されたニューラルネットワークが生成されるまで、前記別のニューラルネットワークの生成を繰り返す、前記(9)に記載の情報処理装置。

(11)

前記生成部は、遺伝的操作により、前記別のニューラルネットワークを生成する、前記(9)または(10)に記載の情報処理装置。

(12)

前記遺伝的操作は、突然変異または交叉のうち少なくとも一方を含む、前記(11)に記載の情報処理装置。

(13)

前記突然変異は、レイヤーの挿入、レイヤーの削除、レイヤー種類の変更、パラメータの変更、グラフ分岐、またはグラフ分岐の削除のうち少なくともいずれか一つを含む、前記(12)に記載の情報処理装置。

(14)

前記情報処理装置は、前記判定部による判定結果を送信させる通信制御部をさらに備える、前記(1)~(13)のいずれか一項に記載の情報処理装置。

(15)

ニューラルネットワークが複数のハードウェアに係る制約を満たすか否かの判定結果を受信する受信部と、

前記判定結果に基づいて処理を行う処理部と、

を備える情報処理装置。

(16)

複数のハードウェアに係る制約を取得することと、

ニューラルネットワークが、前記制約を満たすか否か判定を行うことと、

を含む情報処理方法。

2、2-2 サーバ

5 通信網

10 制御部

12 通信部

14 表示部

16 操作部

20、21 制御部

22 通信部

24 記憶部

201 通信制御部

202 取得部

203、213 判定部

204 設計制御部

205 学習部

206 認識部

217 生成部

218 評価部

1000 情報処理システム

Claims (8)

- ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行う判定部と、

前記ニューラルネットワークの設計を制御し、前記判定部により前記制約を満たさないと判定された場合に、前記制約を満たすように、前記ニューラルネットワークにおけるレイヤーの再配置を行う設計制御部と、

を備える情報処理装置。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行う判定部と、

前記判定部により前記制約を満たさないと判定された場合に、前記ニューラルネットワークにおいて前記制約が満たされない部分を提示する警告画面を表示させる表示制御部と、

を備える情報処理装置。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行う判定部と、

前記制約に基づいて、前記ニューラルネットワークにおけるレイヤーごとに、前記レイヤーに対応付けられたハードウェアに応じた学習を行う学習部と、

を備える情報処理装置。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行う判定部と、

前記判定部により前記制約を満たすと判定されたニューラルネットワークから、ネットワーク構造の異なる別のニューラルネットワークを生成する生成部と、

を備え、

前記判定部は、前記生成部により生成されるニューラルネットワークが前記制約を満たすか否か判定を行い、

前記生成部は、前記判定部により前記制約を満たすと判定されるニューラルネットワークが生成されるまで、前記別のニューラルネットワークの生成を繰り返す、

情報処理装置。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行うことと、

前記ニューラルネットワークの設計を制御することと、

前記制約を満たさないと判定した場合に、前記制約を満たすように、前記ニューラルネットワークにおけるレイヤーの再配置を行うことと、

を含む情報処理方法。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行うことと、

前記制約を満たさないと判定した場合に、前記ニューラルネットワークにおいて前記制約が満たされない部分を提示する警告画面を表示させることと、

を含む情報処理方法。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行うことと、

前記制約に基づいて、前記ニューラルネットワークにおけるレイヤーごとに、前記レイヤーに対応付けられたハードウェアに応じた学習を行うことと、

を含む情報処理方法。 - ニューラルネットワークが、複数のハードウェアに係る制約を満たすか否か判定を行うことと、

前記制約を満たすと判定したニューラルネットワークから、ネットワーク構造の異なる別のニューラルネットワークを生成することと、

生成したニューラルネットワークが前記制約を満たすか否か判定することと、

前記制約を満たすと判定されるニューラルネットワークが生成されるまで、前記別のニューラルネットワークの生成を繰り返すことと、

を含む情報処理方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016091418 | 2016-04-28 | ||

| JP2016091418 | 2016-04-28 | ||

| PCT/JP2017/008988 WO2017187798A1 (ja) | 2016-04-28 | 2017-03-07 | 情報処理装置、及び情報処理方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2017187798A1 JPWO2017187798A1 (ja) | 2019-03-07 |

| JP6996497B2 true JP6996497B2 (ja) | 2022-01-17 |

Family

ID=60161587

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018514172A Active JP6996497B2 (ja) | 2016-04-28 | 2017-03-07 | 情報処理装置、及び情報処理方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US20190057309A1 (ja) |

| EP (1) | EP3451237A4 (ja) |

| JP (1) | JP6996497B2 (ja) |

| WO (1) | WO2017187798A1 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018173121A1 (ja) * | 2017-03-21 | 2018-09-27 | 株式会社Preferred Networks | サーバ装置、学習済モデル提供プログラム、学習済モデル提供方法及び学習済モデル提供システム |

| JP7065368B2 (ja) * | 2017-11-17 | 2022-05-12 | パナソニックIpマネジメント株式会社 | 情報処理方法および情報処理システム |

| US11270228B2 (en) * | 2017-11-17 | 2022-03-08 | Panasonic Intellectual Property Management Co., Ltd. | Information processing method and information processing system |

| WO2019181137A1 (ja) * | 2018-03-23 | 2019-09-26 | ソニー株式会社 | 情報処理装置および情報処理方法 |

| WO2019187542A1 (ja) * | 2018-03-28 | 2019-10-03 | ソニー株式会社 | 情報処理方法、情報処理装置、およびプログラム |

| CN112088383B (zh) * | 2018-05-10 | 2025-03-14 | 衛來科技公司 | 神经网络构筑装置及方法、信息处理装置及记录介质 |

| US12050991B1 (en) * | 2018-05-21 | 2024-07-30 | Google Llc | Connectomics-based neural architecture search |

| WO2019230254A1 (ja) * | 2018-05-31 | 2019-12-05 | ソニー株式会社 | 情報処理装置、情報処理方法およびプログラム |

| JP6890741B2 (ja) * | 2019-03-15 | 2021-06-18 | 三菱電機株式会社 | アーキテクチャ推定装置、アーキテクチャ推定方法、およびアーキテクチャ推定プログラム |

| JP7111671B2 (ja) * | 2019-09-05 | 2022-08-02 | 株式会社東芝 | 学習装置、学習システム、および学習方法 |

| WO2021079763A1 (ja) * | 2019-10-21 | 2021-04-29 | ソニー株式会社 | 情報処理方法、情報処理装置、及びプログラム |

| CN112884118A (zh) * | 2019-11-30 | 2021-06-01 | 华为技术有限公司 | 神经网络的搜索方法、装置及设备 |

| JP7475164B2 (ja) * | 2020-03-05 | 2024-04-26 | キヤノン株式会社 | 情報処理装置、情報処理方法およびプログラム |

| TWI900601B (zh) * | 2021-01-15 | 2025-10-11 | 美商谷歌有限責任公司 | 用於硬體加速器之神經架構縮放之電腦實施方法、系統及非暫時性電腦可讀儲存媒體 |

| CN114969636B (zh) * | 2021-03-23 | 2023-10-03 | 华为技术有限公司 | 一种模型推荐的方法、装置和计算机设备 |

| CN113033784A (zh) * | 2021-04-18 | 2021-06-25 | 沈阳雅译网络技术有限公司 | 一种针对cpu和gpu设备搜索神经网络结构的方法 |

| CN115438767B (zh) * | 2021-06-02 | 2025-12-12 | 杭州海康威视数字技术股份有限公司 | 神经网络模型的配置确定方法、装置、设备及存储介质 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080319933A1 (en) | 2006-12-08 | 2008-12-25 | Medhat Moussa | Architecture, system and method for artificial neural network implementation |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03237557A (ja) * | 1990-02-14 | 1991-10-23 | Oki Electric Ind Co Ltd | ニューラルネットワークシミュレータ及び計算機システム |

| US5812993A (en) * | 1996-03-07 | 1998-09-22 | Technion Research And Development Foundation Ltd. | Digital hardware architecture for realizing neural network |

| JPH1091676A (ja) * | 1996-07-25 | 1998-04-10 | Toyota Motor Corp | 安定化設計方法及び安定化設計プログラムを記録した記録媒体 |

| US8225074B2 (en) * | 2008-10-02 | 2012-07-17 | Nec Laboratories America, Inc. | Methods and systems for managing computations on a hybrid computing platform including a parallel accelerator |

| CN103678002A (zh) * | 2013-12-09 | 2014-03-26 | 华为技术有限公司 | 资源复用的控制方法和装置 |

| US10769517B2 (en) * | 2016-03-05 | 2020-09-08 | Fujitsu Limited | Neural network analysis |

-

2017

- 2017-03-07 EP EP17789087.8A patent/EP3451237A4/en not_active Ceased

- 2017-03-07 WO PCT/JP2017/008988 patent/WO2017187798A1/ja not_active Ceased

- 2017-03-07 US US16/080,475 patent/US20190057309A1/en active Pending

- 2017-03-07 JP JP2018514172A patent/JP6996497B2/ja active Active

-

2025

- 2025-09-19 US US19/333,985 patent/US20260017521A1/en active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080319933A1 (en) | 2006-12-08 | 2008-12-25 | Medhat Moussa | Architecture, system and method for artificial neural network implementation |

Non-Patent Citations (2)

| Title |

|---|

| JIN, Yaochu ほか,"Neural network regularization and ensembling using multi-objective evolutionary algorithms",Proceedings of the 2004 Congress on Evolutionary Computation,米国,IEEE,2004年06月23日,pp.1-8 |

| 片山 立 ほか,「複数評価基準にもとづくファジィモデルとニューロモデルの総合評価」,日本ファジィ学会誌,日本ファジィ学会,1992年10月31日,第4巻, 第5号,pp.942-957 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20190057309A1 (en) | 2019-02-21 |

| EP3451237A1 (en) | 2019-03-06 |

| EP3451237A4 (en) | 2019-04-17 |

| US20260017521A1 (en) | 2026-01-15 |

| JPWO2017187798A1 (ja) | 2019-03-07 |

| WO2017187798A1 (ja) | 2017-11-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6996497B2 (ja) | 情報処理装置、及び情報処理方法 | |

| JP6852748B2 (ja) | 情報処理方法および情報処理装置 | |

| US10496436B2 (en) | Method and apparatus for automatically scheduling jobs in computer numerical control machines using machine learning approaches | |

| TW201329788A (zh) | 適應性調整虛擬按鍵尺寸的方法及其顯示裝置 | |

| US20150220311A1 (en) | Computer implemented modeling system and method | |

| CN110968943A (zh) | 一种终端界面的显示方法及装置 | |

| KR102549980B1 (ko) | 강화 학습 기반 인테리어 서비스의 사물 배치 모델 제공 장치 및 방법 | |

| JP2022164534A5 (ja) | ||

| KR102592108B1 (ko) | 동적 발광 패턴을 이용한 공연 연출 시뮬레이션 제공 시스템, 장치, 방법 및 프로그램 | |

| Engert et al. | STRAIDE: a research platform for shape-changing spatial displays based on actuated strings | |

| KR101416916B1 (ko) | 에이전트 기반의 군사 시뮬레이션 환경에서 물자의 최적 분배 시스템 및 그것의 제어방법 | |

| CN110297432A (zh) | 机器人动作序列生成方法、装置和系统 | |

| KR102601286B1 (ko) | 조명 제어 장치, 방법 및 프로그램 | |

| JP2015170009A (ja) | 表示情報生成装置、プログラム実行状況表示システム、方法およびプログラム | |

| CN108108430A (zh) | 一种基于Unity3D知识森林虚拟现实系统实现的方法 | |

| JP7279705B2 (ja) | 情報処理方法、情報処理装置、およびプログラム | |

| JP6314717B2 (ja) | ラダープログラム作成装置、モニタリング装置、コンピュータプログラム及び機器制御装置 | |

| JP2007310860A (ja) | 学習装置及び方法 | |

| WO2021079763A1 (ja) | 情報処理方法、情報処理装置、及びプログラム | |

| CN111880402A (zh) | 荧光粉层产品参数控制方法、装置和存储介质 | |

| EP4002020B1 (en) | Method and system for determining optimal outcome in a dynamic environment | |

| EP3822769B1 (en) | Method for editing continual vertical line of visual programming language | |

| JPWO2019064461A1 (ja) | 学習ネットワーク生成装置、及び学習ネットワーク生成プログラム | |

| MIRRA et al. | A Reinforcement Learning Agent for Enhancing the Reuse of Structural Components in New Buildings | |

| CN101599092B (zh) | 用于计算机辅助设计与制造的人机交互方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20190208 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20190214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20190222 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20190515 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20190522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210618 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211116 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211129 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6996497 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |