JP6974446B2 - 誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ(FET)(FinFET) - Google Patents

誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ(FET)(FinFET) Download PDFInfo

- Publication number

- JP6974446B2 JP6974446B2 JP2019513978A JP2019513978A JP6974446B2 JP 6974446 B2 JP6974446 B2 JP 6974446B2 JP 2019513978 A JP2019513978 A JP 2019513978A JP 2019513978 A JP2019513978 A JP 2019513978A JP 6974446 B2 JP6974446 B2 JP 6974446B2

- Authority

- JP

- Japan

- Prior art keywords

- dielectric material

- material layer

- fin

- finfet

- channel region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003989 dielectric material Substances 0.000 title claims description 134

- 230000005669 field effect Effects 0.000 title claims description 8

- 239000000758 substrate Substances 0.000 claims description 63

- 238000000034 method Methods 0.000 claims description 37

- 239000000463 material Substances 0.000 claims description 18

- 238000000137 annealing Methods 0.000 claims description 6

- 238000005229 chemical vapour deposition Methods 0.000 claims description 6

- 238000005530 etching Methods 0.000 claims description 4

- 238000004519 manufacturing process Methods 0.000 description 22

- 230000008569 process Effects 0.000 description 19

- 230000006870 function Effects 0.000 description 9

- 238000003860 storage Methods 0.000 description 6

- 238000012545 processing Methods 0.000 description 4

- 238000007796 conventional method Methods 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000036541 health Effects 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000006249 magnetic particle Substances 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7846—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being located in the lateral device isolation region, e.g. STI

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823418—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823431—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823437—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823481—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type isolation region manufacturing related aspects, e.g. to avoid interaction of isolation region with adjacent structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823821—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

- H01L21/845—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body including field-effect transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/0886—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate including transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

- H01L27/0924—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors including transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

- H01L27/1211—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI combined with field-effect transistors with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41791—Source or drain electrodes for field effect devices for transistors with a horizontal current flow in a vertical sidewall, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66787—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel

- H01L29/66795—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a gate at the side of the channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7843—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being an applied insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/785—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET

- H01L29/7851—Field effect transistors with field effect produced by an insulated gate having a channel with a horizontal current flow in a vertical sidewall of a semiconductor body, e.g. FinFET, MuGFET with the body tied to the substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

- H10B12/056—Making the transistor the transistor being a FinFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/36—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the transistor being a FinFET

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- General Engineering & Computer Science (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

本出願は、2016年9月15日に出願された「FIN FIELD EFFECT TRANSISTORS(FETs)(FINFETs) EMPLOYING DIELECTRIC MATERIAL LAYERS TO APPLY STRESS TO CHANNEL REGIONS」という名称の米国特許出願第15/266,840号の優先権を主張する。米国特許出願第15/266,840号は、その全体が参照により本明細書に組み込まれる。

102 基板

104 フィン

106 酸化物層

108 ソース

110 ドレイン

112 伝導チャネル

114 ゲート

116 応力

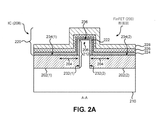

200 FinFET

202(1)、202(2) 誘電体材料層

204 応力

206 チャネル領域

208 集積回路

210 基板

212 フィン

214 第1の方向

216 ソース

218 ドレイン

220 ゲート

222 ゲート酸化物層

224 ゲート誘電体材料層

226 仕事関数層

228 導電層

230(1)〜230(4) ゲート構造

232(1) 第1の側

232(2) 第2の側

234(1)、234(2) 上面

236 上面

238 活性領域境界

240 活性層

242(1)、242(2) STI構造

404(1) 第1の側

404(2) 第2の側

406 ゲート領域

408 ドレイン領域

410 ソース材料

412 ドレイン材料

414 第2の方向

500 FinFET

502(1) 第1の側

502(2) 第2の側

504 活性領域境界

506 活性層

600 プロセッサベースシステム

602 中央処理装置(CPU)

604 プロセッサ

606 キャッシュメモリ

608 システムバス

610 メモリコントローラ

612 メモリシステム

614 入力デバイス

616 出力デバイス

618 ネットワークインターフェースデバイス

620 ディスプレイコントローラ

622 ネットワーク

624(0)〜624(M) メモリユニット

626 ディスプレイ

628 ビデオプロセッサ

Claims (13)

- フィン電界効果トランジスタFinFETであって、

基板と、

前記基板の上に配設された第1のフィンであって、

第1のソースと、

第1のドレインと、

前記第1のソースと前記第1のドレインとの間に配設された第1のチャネル領域とを備える第1のフィンと、

前記第1のチャネル領域の周りに配設されたゲートと、

前記基板の上にかつ前記第1のフィンの第1の側の前記第1のチャネル領域に隣接するように配設された第1の誘電体材料層であって、前記第1のチャネル領域に応力を加える第1の誘電体材料層と、

前記基板の上にかつ前記第1の側とは異なる前記第1のフィンの第2の側の前記第1のチャネル領域に隣接するように配設された第2の誘電体材料層であって、前記第1のチャネル領域に応力を加える第2の誘電体材料層と、

前記基板の上にかつ前記第1のフィンに平行に配設された第2のフィンであって、

第2のソースと、

第2のドレインと、

前記第2のフィンの前記第2のソースと前記第2のドレインとの間に配設された第2のチャネル領域とを備える第2のフィンと、

前記第2のフィンの前記第2のチャネル領域の周りに配設された前記ゲートと、

前記基板の上にかつ前記第2のフィンの第2の側の前記第2のチャネル領域に隣接するように配設された第3の誘電体材料層であって、前記第2のフィンの前記第2のチャネル領域に応力を加える第3の誘電体材料層と

を備え、

前記第2の誘電体材料層は、前記第2の誘電体材料層が前記第2のフィンの前記第2のチャネル領域に応力を加えるように、前記基板の上にかつ前記第2の側とは異なる前記第2のフィンの第1の側の前記第2のチャネル領域に隣接するように配設され、

前記第1のフィンと前記第2のフィンとの間の距離が、32ナノメートル以下であり、

前記FinFETの活性層を囲む活性領域境界をさらに備え、前記活性層は、その上に前記ソースおよびドレインが形成された前記基板のドープ領域に対応し、前記第1の誘電体材料層、前記第2の誘電体材料層、および前記第3の誘電体材料層の各々は、前記活性領域境界内のみに配設される、FinFET。 - 前記第1の誘電体材料層の上面は、前記第1のフィンの上面よりも低く、

前記第2の誘電体材料層の上面は、前記第1のフィンの上面よりも低い、請求項1に記載のFinFET。 - 前記FinFETはN型FinFETを備え、

前記第1および第2の誘電体材料層は、前記第1および第2の誘電体材料層が前記第1のチャネル領域に引張応力を加えるように1つまたは複数の酸化物材料を含む、請求項1に記載のFinFET。 - 前記FinFETはP型FinFETを備え、

前記第1および第2の誘電体材料層は、前記第1および第2の誘電体材料層が前記第1のチャネル領域に圧縮応力を加えるように1つまたは複数の酸化物材料を含む、請求項1に記載のFinFET。 - 集積回路ICに組み込まれる、請求項1に記載のFinFET。

- 誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタFinFETを製作するための方法であって、

第1のフィンおよび第2のフィンを備える基板を設けるステップであって、前記第1のフィンは、第1のソースと、第1のドレインと、前記第1のソースと前記第1のドレインとの間に配設された第1のチャネル領域とを備え、前記第2のフィンは、第2のソースと、第2のドレインと、前記第2のソースと前記第2のドレインとの間に配設された第2のチャネル領域とを備える、ステップと、

前記基板の上にかつ前記第1のフィンの第1の側の前記チャネル領域に隣接するように第1の誘電体材料層を配設するステップと、

前記基板の上にかつ前記第1のフィンの第2の側の前記チャネル領域に隣接するように第2の誘電体材料層を配設するステップであって、前記第2の側が前記第1の側とは異なる、ステップと、

前記第1のフィン、前記第2のフィン、前記第1の誘電体材料層、および前記第2の誘電体材料層の上のゲート領域内に、前記FinFETのゲート長に等しい幅を有するゲートを配設するステップとを含み、

前記第1のフィンと前記第2のフィンとの間の距離が、32ナノメートル以下であり、

前記第1の誘電体材料層を配設する前記ステップは、前記基板の上に、かつ前記FinFETの活性層を囲む活性領域境界内のみに、前記第1のフィンの第1の側の前記チャネル領域に隣接するように前記第1の誘電体材料層を配設するステップであって、前記活性層は、その上に前記ソースおよびドレインが形成された前記基板のドープ領域に対応する、ステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、前記基板の上に、かつ前記活性領域境界内のみに、前記第1のフィンの前記第2の側の前記チャネル領域に隣接するように前記第2の誘電体材料層を配設するステップを含む、方法。 - 前記第1の誘電体材料層および前記第2の誘電体材料層をウェットアニールして前記FinFETの前記チャネル領域に加えられる応力を調整するステップをさらに含む、請求項6に記載の方法。

- 前記第1の誘電体材料層および前記第2の誘電体材料層をドライアニールして前記FinFETのチャネル領域に加えられる応力を調整するステップをさらに含む、請求項7に記載の方法。

- 前記ゲートを配設する前記ステップは、

前記FinFETのゲート長に等しい幅を有するゲート酸化物層を前記第1のフィンおよび前記第2のフィンの上の前記ゲート領域内に配設するステップと、

前記ゲート酸化物層、前記第1の誘電体材料層、および前記第2の誘電体材料層の上のゲート領域内に、前記FinFETの前記ゲート長に等しい幅を有するゲート誘電体材料層を配設するステップと、

前記ゲート誘電体材料層の上の前記ゲート領域内に、前記FinFETの前記ゲート長に等しい幅を有する仕事関数層を配設するステップと、

前記仕事関数層の上の前記ゲート領域内に、前記FinFETの前記ゲート長に等しい幅を有する導電層を配設するステップとを含む、請求項6に記載の方法。 - 前記ゲート領域の第1の側の前記FinFETのソース領域に対応する前記第1のフィンをエッチングするステップと、

前記ゲート領域の第1の側とは異なる前記ゲート領域の第2の側の前記FinFETのドレイン領域に対応する前記第1のフィンをエッチングするステップと、

前記ソース領域においてソース材料を成長させるステップと、

前記ドレイン領域内でドレイン材料を成長させるステップとをさらに含む、請求項6に記載の方法。 - 前記第1の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第1の側の前記チャネル領域に隣接するように前記第1の誘電体材料層を配設するステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第2の側の前記チャネル領域に隣接するように前記第2の誘電体材料層を配設するステップを含む、請求項6に記載の方法。 - 前記第1の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第1の側に隣接するように1つまたは複数の酸化物材料を配設するステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第2の側に隣接するように1つまたは複数の酸化物材料を配設するステップを含む、請求項6に記載の方法。 - 前記第1の誘電体材料層を配設する前記ステップは、高アスペクト比処理を使用して前記基板の上にかつ前記第1のフィンの前記第1の側の前記チャネル領域に隣接するように1つまたは複数の酸化物材料を配設するステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、高アスペクト比処理を使用して前記基板の上にかつ前記第1のフィンの前記第2の側の前記チャネル領域に隣接するように1つまたは複数の酸化物材料を配設するステップを含む、請求項6に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/266,840 US9882051B1 (en) | 2016-09-15 | 2016-09-15 | Fin field effect transistors (FETs) (FinFETs) employing dielectric material layers to apply stress to channel regions |

| US15/266,840 | 2016-09-15 | ||

| PCT/US2017/046525 WO2018052591A1 (en) | 2016-09-15 | 2017-08-11 | Fin field effect transistors (fets) (finfets) employing dielectric material layers to apply stress to channel regions |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019530227A JP2019530227A (ja) | 2019-10-17 |

| JP2019530227A5 JP2019530227A5 (ja) | 2020-08-27 |

| JP6974446B2 true JP6974446B2 (ja) | 2021-12-01 |

Family

ID=59684098

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019513978A Active JP6974446B2 (ja) | 2016-09-15 | 2017-08-11 | 誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ(FET)(FinFET) |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9882051B1 (ja) |

| JP (1) | JP6974446B2 (ja) |

| KR (1) | KR102550579B1 (ja) |

| CN (1) | CN109844957A (ja) |

| BR (1) | BR112019004507B1 (ja) |

| CA (1) | CA3032965A1 (ja) |

| WO (1) | WO2018052591A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10109507B2 (en) * | 2016-06-01 | 2018-10-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Fluorine contamination control in semiconductor manufacturing process |

| US11211243B2 (en) * | 2018-11-21 | 2021-12-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of filling gaps with carbon and nitrogen doped film |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7081395B2 (en) | 2003-05-23 | 2006-07-25 | Taiwan Semiconductor Manufacturing Co., Ltd. | Silicon strain engineering accomplished via use of specific shallow trench isolation fill materials |

| JP2007207837A (ja) | 2006-01-31 | 2007-08-16 | Toshiba Corp | 半導体装置および半導体装置の製造方法 |

| US7939862B2 (en) | 2007-05-30 | 2011-05-10 | Synopsys, Inc. | Stress-enhanced performance of a FinFet using surface/channel orientations and strained capping layers |

| US7943531B2 (en) * | 2007-10-22 | 2011-05-17 | Applied Materials, Inc. | Methods for forming a silicon oxide layer over a substrate |

| US7915112B2 (en) | 2008-09-23 | 2011-03-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal gate stress film for mobility enhancement in FinFET device |

| US9953885B2 (en) * | 2009-10-27 | 2018-04-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | STI shape near fin bottom of Si fin in bulk FinFET |

| US8426923B2 (en) * | 2009-12-02 | 2013-04-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Multiple-gate semiconductor device and method |

| DE102010002410B4 (de) | 2010-02-26 | 2017-03-02 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Verformungsgedächtnistechnologie in verformten SOI-Substraten von Halbleiterbauelementen |

| US8937353B2 (en) * | 2010-03-01 | 2015-01-20 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dual epitaxial process for a finFET device |

| JP2013093438A (ja) * | 2011-10-26 | 2013-05-16 | Renesas Electronics Corp | 半導体装置の製造方法 |

| US8698199B2 (en) | 2012-01-11 | 2014-04-15 | United Microelectronics Corp. | FinFET structure |

| US8941187B2 (en) | 2012-01-13 | 2015-01-27 | Globalfoundries Inc. | Strain engineering in three-dimensional transistors based on strained isolation material |

| CN103681846B (zh) | 2012-09-20 | 2017-02-08 | 中芯国际集成电路制造(上海)有限公司 | 半导体装置及其制造方法 |

| US9263585B2 (en) * | 2012-10-30 | 2016-02-16 | Globalfoundries Inc. | Methods of forming enhanced mobility channel regions on 3D semiconductor devices, and devices comprising same |

| US8759874B1 (en) * | 2012-11-30 | 2014-06-24 | Stmicroelectronics, Inc. | FinFET device with isolated channel |

| US8877588B2 (en) | 2013-02-11 | 2014-11-04 | Globalfoundries Inc. | Methods of forming a three-dimensional semiconductor device with a dual stress channel and the resulting device |

| US9721955B2 (en) | 2014-04-25 | 2017-08-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and method for SRAM FinFET device having an oxide feature |

| US9306067B2 (en) | 2014-08-05 | 2016-04-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Nonplanar device and strain-generating channel dielectric |

| TWI655774B (zh) * | 2015-08-12 | 2019-04-01 | 聯華電子股份有限公司 | 半導體元件及其製作方法 |

| US9614086B1 (en) * | 2015-12-30 | 2017-04-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Conformal source and drain contacts for multi-gate field effect transistors |

-

2016

- 2016-09-15 US US15/266,840 patent/US9882051B1/en active Active

-

2017

- 2017-08-11 KR KR1020197007266A patent/KR102550579B1/ko active IP Right Grant

- 2017-08-11 CA CA3032965A patent/CA3032965A1/en active Pending

- 2017-08-11 CN CN201780056420.3A patent/CN109844957A/zh active Pending

- 2017-08-11 BR BR112019004507-4A patent/BR112019004507B1/pt active IP Right Grant

- 2017-08-11 JP JP2019513978A patent/JP6974446B2/ja active Active

- 2017-08-11 WO PCT/US2017/046525 patent/WO2018052591A1/en active Search and Examination

Also Published As

| Publication number | Publication date |

|---|---|

| CA3032965A1 (en) | 2018-03-22 |

| EP3513437A1 (en) | 2019-07-24 |

| CN109844957A (zh) | 2019-06-04 |

| BR112019004507A2 (pt) | 2019-06-04 |

| KR102550579B1 (ko) | 2023-07-03 |

| US9882051B1 (en) | 2018-01-30 |

| JP2019530227A (ja) | 2019-10-17 |

| KR20190047696A (ko) | 2019-05-08 |

| WO2018052591A1 (en) | 2018-03-22 |

| BR112019004507B1 (pt) | 2023-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10134734B2 (en) | Fin field effect transistor (FET) (FinFET) complementary metal oxide semiconductor (CMOS) circuits employing single and double diffusion breaks for increased performance | |

| US9570442B1 (en) | Applying channel stress to Fin field-effect transistors (FETs) (FinFETs) using a self-aligned single diffusion break (SDB) isolation structure | |

| US10032678B2 (en) | Nanowire channel structures of continuously stacked nanowires for complementary metal oxide semiconductor (CMOS) devices | |

| JP2018113485A (ja) | ダミーゲートで分割された連続活性領域を有する金属酸化物半導体(mos)分離方式および関連する方法 | |

| CN108369948B (zh) | 用于改进的静电学的非平面igzo器件的制造 | |

| TWI836013B (zh) | 用於finfet電晶體的閘極堆疊 | |

| JP6974446B2 (ja) | 誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ(FET)(FinFET) | |

| US20200273998A1 (en) | Source electrode and drain electrode protection for nanowire transistors | |

| EP3378095B1 (en) | Semiconductor devices with wider field gates for reduced gate resistance | |

| EP3712937A1 (en) | Capacitance reduction for semiconductor devices based on wafer bonding | |

| US20170084628A1 (en) | Substrate-transferred, deep trench isolation silicon-on-insulator (soi) semiconductor devices formed from bulk semiconductor wafers | |

| US9171952B2 (en) | Low gate-to-drain capacitance fully merged finFET | |

| TWI721110B (zh) | 用於電晶體整合的奈米線 | |

| EP3513437B1 (en) | Fin field effect transistors (fets) (finfets) employing dielectric material layers to apply stress to channel regions | |

| US20190296126A1 (en) | Systems and methods for dummy gate tie-offs in a self-aligned gate contact (sagc) cell | |

| EP3513429B1 (en) | Semiconductor devices employing field effect transistors (fets) with multiple channel structures without shallow trench isolation (sti) void-induced electrical shorts | |

| US10600774B2 (en) | Systems and methods for fabrication of gated diodes with selective epitaxial growth | |

| US11532719B2 (en) | Transistors on heterogeneous bonding layers |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190318 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200717 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200717 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210531 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210831 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211004 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211104 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6974446 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |