JP6542985B2 - アナログ−デジタル変換を実行する方法 - Google Patents

アナログ−デジタル変換を実行する方法 Download PDFInfo

- Publication number

- JP6542985B2 JP6542985B2 JP2018513445A JP2018513445A JP6542985B2 JP 6542985 B2 JP6542985 B2 JP 6542985B2 JP 2018513445 A JP2018513445 A JP 2018513445A JP 2018513445 A JP2018513445 A JP 2018513445A JP 6542985 B2 JP6542985 B2 JP 6542985B2

- Authority

- JP

- Japan

- Prior art keywords

- range

- digital

- analog

- sigma

- delta modulator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

- H03M3/478—Means for controlling the correspondence between the range of the input signal and the range of signals the converter can handle; Means for out-of-range indication

- H03M3/488—Means for controlling the correspondence between the range of the input signal and the range of signals the converter can handle; Means for out-of-range indication using automatic control

- H03M3/49—Means for controlling the correspondence between the range of the input signal and the range of signals the converter can handle; Means for out-of-range indication using automatic control in feedback mode, i.e. by determining the range to be selected from one or more previous digital output values

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/32—Delta-sigma modulation with special provisions or arrangements for power saving, e.g. by allowing a sleep mode, using lower supply voltage for downstream stages, using multiple clock domains, by selectively turning on stages when needed

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/39—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators

- H03M3/412—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution

- H03M3/422—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

- H03M3/464—Details of the digital/analogue conversion in the feedback path

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

- H03M3/494—Sampling or signal conditioning arrangements specially adapted for delta-sigma type analogue/digital conversion systems

- H03M3/496—Details of sampling arrangements or methods

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/39—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators

- H03M3/412—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution

- H03M3/422—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only

- H03M3/43—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only the quantiser being a single bit one

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/39—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators

- H03M3/436—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the order of the loop filter, e.g. error feedback type

- H03M3/438—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the order of the loop filter, e.g. error feedback type the modulator having a higher order loop filter in the feedforward path

Description

Claims (13)

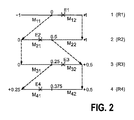

- フィードバックデジタル−アナログ変換器を含むシグマ−デルタ変調器を使用して、1つのレンジの中で入力信号についてアナログ−デジタル変換を実行する方法であって、前記方法は、N回の反復を伴う反復方法を含み、Nは少なくとも3であり、かつ、少なくとも2回目から(N−1)回目までの前記反復は、

前記反復について定められたレンジにおける前記入力信号の振幅推定値を獲得するステップと、

前記反復について定められたレンジをM個のサブレンジへと分割するステップであり、Mは少なくとも2である、ステップと、

前記M個のサブレンジのうち前記振幅推定値を含むサブレンジを、次の反復のためのレンジとして定める、ステップと、

前記次の反復のために定められた前記レンジを設定するために、前記フィードバックデジタル−アナログ変換器の動作パラメータを調整するステップと、

を含む、

方法。 - 1回目の反復について前記振幅推定値は、最大で5のオーバーサンプリング比において獲得される、

請求項1に記載の方法。 - N回目の反復について前記振幅推定値は、少なくとも50のオーバーサンプリング比において獲得される、

請求項1に記載の方法。 - 前記フィードバックデジタル−アナログ変換器は、非対称に動作されるデジタル−アナログ変換器を含み、かつ、

前記フィードバックデジタル−アナログ変換器の動作パラメータを調整する前記ステップは、前記デジタル−アナログ変換器のゲイン及び/又はオフセットを調整することを含む、

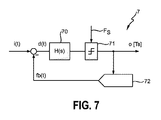

請求項1に記載の方法。 - アナログ−デジタル変換器のシグマ−デルタ変調器であって、

アクティブループフィルタおよび1つの入力レンジの中で入力信号の振幅推定値を獲得するための量子化器、を含むフォワードパスと、

デジタル−アナログ変換器およびレンジ調整手段を含むフィードバック装置であり、前記レンジ調整手段は、

前記入力レンジのサブレンジについて前記シグマ−デルタ変調器のダイナミックレンジを調整するように構成されており、前記サブレンジは、中間点によって定められ、かつ、前記振幅推定値を含み、前記調整されたダイナミックレンジの前記中間点は、前記サブレンジを定めている前記中間点とは独立しており、かつ、

前記調整されたダイナミックレンジに応じて、フィードバックデジタル−アナログ変換器の動作パラメータを調整するように構成されており、

前記レンジ調整手段による調整が複数回にわたり反復される、フィードバック装置と、

を含む、シグマ−デルタ変調器。 - 前記デジタル−アナログ変換器は、切替えキャパシタバンクとして具現化されている、

請求項5に記載のシグマ−デルタ変調器。 - 少なくとも15の有効ビット数を有する、

請求項5に記載のシグマ−デルタ変調器。 - 前記フォワードパスは、少なくとも2次フィルタを含み、

前記変調器は、最大で20のオーバーサンプリング比において最終でない推定値を獲得し、かつ、少なくとも150のオーバーサンプリング比において最終推定値を獲得する、ように構成されている、

請求項5に記載のシグマ−デルタ変調器。 - インクリメンタルシグマ−デルタ変調器として具現化されている、

請求項5に記載のシグマ−デルタ変調器。 - 入力信号についてアナログ−デジタル変換を実行するためのアナログ−デジタル変換器であって、

請求項5に記載のシグマ−デルタ変調器、を含む、

アナログ−デジタル変換器。 - 請求項5に記載のシグマ−デルタ変調器を含むアナログ−デジタル変換器を用いて、入力信号についてアナログ−デジタル変換を実行するための装置。

- 最終でない推定値は、最大で5のオーバーサンプリング比において獲得される、

請求項5に記載のシグマ−デルタ変調器。 - 前記振幅推定値は、最終でない推定値および最終推定値を含み、かつ、

前記最終推定値は、最大で200のオーバーサンプリング比において獲得される、

請求項5に記載のシグマ−デルタ変調器。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP15185239 | 2015-09-15 | ||

| EP15185239.9 | 2015-09-15 | ||

| PCT/EP2016/070912 WO2017045962A1 (en) | 2015-09-15 | 2016-09-06 | Method of performing analog-to-digital conversion |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018527839A JP2018527839A (ja) | 2018-09-20 |

| JP2018527839A5 JP2018527839A5 (ja) | 2019-03-22 |

| JP6542985B2 true JP6542985B2 (ja) | 2019-07-10 |

Family

ID=54145675

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018513445A Active JP6542985B2 (ja) | 2015-09-15 | 2016-09-06 | アナログ−デジタル変換を実行する方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10284223B2 (ja) |

| EP (1) | EP3350929A1 (ja) |

| JP (1) | JP6542985B2 (ja) |

| CN (1) | CN108028662B (ja) |

| WO (1) | WO2017045962A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11036294B2 (en) | 2015-10-07 | 2021-06-15 | The Governing Council Of The University Of Toronto | Wireless power and data transmission system for wearable and implantable devices |

| EP3487578B1 (en) * | 2016-07-20 | 2022-12-07 | The Governing Council of the University of Toronto | Neurostimulator for delivering a stimulation in response to a predicted or detected neurophysiological condition |

| US9780798B1 (en) * | 2016-11-01 | 2017-10-03 | Texas Instruments Incorporated | Digital modulator entropy source |

| US10574257B2 (en) * | 2018-02-09 | 2020-02-25 | The Regents Of The University Of California | Predictive digital autoranging analog-to-digital converter |

| US11265010B2 (en) * | 2019-04-29 | 2022-03-01 | Mediatek Inc. | Incremental analog-to-digital converter |

| US11949426B2 (en) * | 2020-12-16 | 2024-04-02 | Qualcomm Incorporated | Configurable analog-to-digital conversion parameters |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5187482A (en) | 1992-03-02 | 1993-02-16 | General Electric Company | Delta sigma analog-to-digital converter with increased dynamic range |

| US7295645B1 (en) | 2002-01-29 | 2007-11-13 | Ellipsis Digital Systems, Inc. | System, method and apparatus to implement low power high performance transceivers with scalable analog to digital conversion resolution and dynamic range |

| JP2006140600A (ja) * | 2004-11-10 | 2006-06-01 | Fujitsu Ltd | シグマデルタa/d変換器 |

| US7456766B2 (en) * | 2006-07-19 | 2008-11-25 | Qualcomm Incorporated | Sigma-delta modulation with offset |

| WO2007107188A1 (en) * | 2006-03-23 | 2007-09-27 | Freescale Semiconductor, Inc. | Electronic device and integrated circuit comprising a delta-sigma converter and method therefor |

| GB0617848D0 (en) * | 2006-09-11 | 2006-10-18 | Global Silicon Ltd | A random number generator |

| US7446686B2 (en) | 2006-09-22 | 2008-11-04 | Cirrus Logic, Inc. | Incremental delta-sigma data converters with improved stability over wide input voltage ranges |

| US7656330B2 (en) * | 2007-05-23 | 2010-02-02 | Analog Devices, Inc. | Automatic range shift system and method for an analog to digital converter |

| JP5154659B2 (ja) * | 2007-12-19 | 2013-02-27 | エスティー‐エリクソン、ソシエテ、アノニム | フィードバックパスにおいてビット数の減少したマルチビットシグマ・デルタ変調器 |

| US7825838B1 (en) | 2008-09-05 | 2010-11-02 | National Semiconductor Corporation | Capacitor rotation method for removing gain error in sigma-delta analog-to-digital converters |

| CN101764616B (zh) * | 2009-11-27 | 2012-05-02 | 四川和芯微电子股份有限公司 | 一种具有宽输入范围的σ-δ调变器 |

| JP5094916B2 (ja) * | 2010-06-09 | 2012-12-12 | 株式会社半導体理工学研究センター | パイプライン・ad変換回路 |

| US8665126B2 (en) * | 2010-12-08 | 2014-03-04 | National Semiconductor Corporation | ΣΔ difference-of-squares LOG-RMS to DC converter with forward and feedback paths signal squaring |

| US8723706B1 (en) | 2012-08-28 | 2014-05-13 | Maxim Integrated Products, Inc. | Multi-step ADC with sub-ADC calibration |

| US9344104B1 (en) * | 2013-05-18 | 2016-05-17 | S9Estre, Llc | Digital to analog converter and analog to digital converter calibration techniques |

| US20150031971A1 (en) | 2013-07-26 | 2015-01-29 | Covidien Lp | Methods and systems for using an estimate signal to improve signal resolution in a physiological monitor |

| JP2015103820A (ja) * | 2013-11-20 | 2015-06-04 | 株式会社東芝 | アナログ/ディジタル変換器及びアナログ/ディジタル変換方法 |

-

2016

- 2016-09-06 CN CN201680053483.9A patent/CN108028662B/zh active Active

- 2016-09-06 JP JP2018513445A patent/JP6542985B2/ja active Active

- 2016-09-06 EP EP16765946.5A patent/EP3350929A1/en not_active Withdrawn

- 2016-09-06 US US15/757,001 patent/US10284223B2/en active Active

- 2016-09-06 WO PCT/EP2016/070912 patent/WO2017045962A1/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| US10284223B2 (en) | 2019-05-07 |

| WO2017045962A1 (en) | 2017-03-23 |

| CN108028662A (zh) | 2018-05-11 |

| JP2018527839A (ja) | 2018-09-20 |

| US20180269896A1 (en) | 2018-09-20 |

| EP3350929A1 (en) | 2018-07-25 |

| CN108028662B (zh) | 2022-01-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6542985B2 (ja) | アナログ−デジタル変換を実行する方法 | |

| Li et al. | A sub-microwatt asynchronous level-crossing ADC for biomedical applications | |

| US10158369B2 (en) | A/D converter | |

| JP6070654B2 (ja) | A/d変換器 | |

| US7450046B2 (en) | Delta-sigma modulator and A/D converter | |

| CN111327323B (zh) | 无源噪声整形过采样逐次逼近模数转换器及控制方法 | |

| US7379002B1 (en) | Methods and apparatus for a multi-mode analog-to-digital converter | |

| Liew et al. | A 0.5-V 1.13-μW/channel neural recording interface with digital multiplexing scheme | |

| JP6206738B2 (ja) | Ad変換器 | |

| Santos et al. | A survey on nonlinear analog-to-digital converters | |

| Markus et al. | Incremental delta-sigma structures for DC measurement: An overview | |

| Leene et al. | A 0.016 mm2 12 b $\Delta\Sigma $ SAR With 14 fJ/conv. for Ultra Low Power Biosensor Arrays | |

| Wang et al. | Near-optimal decoding of incremental delta-sigma ADC output | |

| US9077374B2 (en) | Resolution-boosted sigma delta analog-to-digital converter | |

| He et al. | Self-dithering technique for high-resolution SAR ADC design | |

| Chen et al. | History, present state-of-art and future of incremental ADCs | |

| Temes | Micropower data converters: A tutorial | |

| Ravanshad et al. | A fully-synchronous offset-insensitive level-crossing analog-to-digital converter | |

| Somappa et al. | A 400 mV 160 nW/Ch Compact Energy Efficient $\Delta\Sigma $ Modulator for Multichannel Biopotential Signal Acquisition System | |

| TW200814541A (en) | Range compression in oversampling analog-to-digital converters using differential input signals | |

| Mahdavi et al. | Analysis simulation and comparison different types of the Sigma Delta ADC modulators based on ideal model system level and behavioral model using MATLAB | |

| CN113169745A (zh) | 至少包括delta-sigma调制器和采样保持元件的电路装置 | |

| CN107294537B (zh) | 一种基于Sigma Delta Modulator的模数转换器 | |

| US10305507B1 (en) | First-order sigma-delta analog-to-digital converter | |

| Das et al. | ADC and DAC for biomedical application |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180316 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190207 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20190207 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20190214 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190508 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190521 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190613 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6542985 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |