JP6485016B2 - 無線通信装置、無線通信装置におけるクロックの位相調整方法 - Google Patents

無線通信装置、無線通信装置におけるクロックの位相調整方法 Download PDFInfo

- Publication number

- JP6485016B2 JP6485016B2 JP2014243187A JP2014243187A JP6485016B2 JP 6485016 B2 JP6485016 B2 JP 6485016B2 JP 2014243187 A JP2014243187 A JP 2014243187A JP 2014243187 A JP2014243187 A JP 2014243187A JP 6485016 B2 JP6485016 B2 JP 6485016B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- clock

- carrier wave

- wireless communication

- communication apparatus

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Transceivers (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

Description

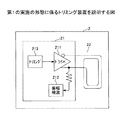

図1は、第1の実施の形態に係る無線通信装置を説明する図である。図1に示すように、第1の実施の形態に係る無線通信装置1は、主要な構成要素として、アンテナ11と、共振容量12と、増幅回路13と、タグLSI16とを有する。無線通信装置1は、例えば、受信した搬送波と同一周波数のクロックを加算して送信(応答)する、ISO18092に準拠したアンテナ付のタグモジュール(RFIDタグ)である。

第1の実施の形態の変形例1では、1相のクロックを生成し、生成した1相のクロックに対して遅延制御素子を用いて位相を遅らせる例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第1の実施の形態の変形例2では、1相のクロックを生成し、生成した1相のクロックからDLL(Digital Locked Loop)を用いて遅延の異なる多相のクロックを生成する例を示す。なお、第1の実施の形態の変形例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

2 トリミング装置

11、22 アンテナ

12 共振容量

13 増幅回路

16 タグLSI

21 リーダライタ

131 クロック抽出回路

132、151 PLL

133、136、211 ドライバ

134 搬送波除去回路

135、142 2値化回路

137 選択回路

141 復調回路

143 コマンド認識回路

144 制御回路

145 不揮発性メモリ

146 レジスタ

147 パワーオン回路

148 初期化制御回路

152 遅延制御素子

153 DLL

212 振幅検波回路

213 トリミング部

301 デジタル/アナログコンバータ

302、303 遅延素子

Claims (5)

- 受信した搬送波を復調した2値波形からコマンドの検出を行い、位相設定コマンドを認識するコマンド認識回路を備え、

前記コマンド認識回路が前記位相設定コマンドを認識したときにレジスタ回路へ位相設定値を設定する制御回路を備え、

前記搬送波に同期して前記搬送波と同一周波数である多相クロックを生成してトリミング装置に送信すると共に、前記トリミング装置で検知された前記多相クロックのうちの振幅が最大となるクロックの位相を示す設定値を受信するアンテナを備え、

前記設定値に基づいて前記多相クロックの1つのクロックを選択する選択回路を備えた無線通信装置。 - 前記搬送波の受信開始前に、前記制御回路がメモリから読み出した前記振幅が最大となるクロックの位相を示す設定値に基づいて前記レジスタ回路の初期設定を行う請求項1記載の無線通信装置。

- 負荷変調を併用して振幅変化を最大とする請求項1又は2記載の無線通信装置。

- 前記コマンド認識回路が認識したコマンドに基づいて、振幅が最大となる位相を示す設定値を前記制御回路がメモリに書き込みを行う請求項1乃至3のいずれか一項記載の無線通信装置。

- 請求項1乃至4のいずれか一項記載の無線通信装置において、受信した前記搬送波と同一周波数のクロックを加算してトリミング装置へ送信してクロックの位相を調整するクロックの位相調整方法であって、

前記無線通信装置が、前記搬送波と同一周波数のクロックを前記搬送波に加算して変調信号を生成するステップと、

前記トリミング装置が、前記変調信号を受信して前記変調信号の振幅を計測するステップと、

前記無線通信装置が前記搬送波に加算するクロックの位相を順次切り替え、前記トリミング装置が前記振幅の最大値となるクロックの位相を示す設定値を記録するステップと、

前記トリミング装置が、前記設定値を前記無線通信装置に記憶させるステップと、を有することを特徴とする無線通信装置におけるクロックの位相調整方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014243187A JP6485016B2 (ja) | 2014-12-01 | 2014-12-01 | 無線通信装置、無線通信装置におけるクロックの位相調整方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014243187A JP6485016B2 (ja) | 2014-12-01 | 2014-12-01 | 無線通信装置、無線通信装置におけるクロックの位相調整方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016105560A JP2016105560A (ja) | 2016-06-09 |

| JP2016105560A5 JP2016105560A5 (ja) | 2017-12-21 |

| JP6485016B2 true JP6485016B2 (ja) | 2019-03-20 |

Family

ID=56102466

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014243187A Expired - Fee Related JP6485016B2 (ja) | 2014-12-01 | 2014-12-01 | 無線通信装置、無線通信装置におけるクロックの位相調整方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6485016B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9887832B1 (en) * | 2016-08-01 | 2018-02-06 | Nxp B.V. | Method and system to calibrate phase supported by factory trim data |

| JP7101152B2 (ja) * | 2019-09-06 | 2022-07-14 | 株式会社東芝 | 電子回路、電流計測装置、および方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009130389A (ja) * | 2007-11-19 | 2009-06-11 | Felica Networks Inc | 通信装置、同調周波数調整方法、およびプログラム |

| JP5990436B2 (ja) * | 2012-09-07 | 2016-09-14 | ルネサスエレクトロニクス株式会社 | 無線通信システムおよび無線通信装置 |

| US9450646B2 (en) * | 2013-03-15 | 2016-09-20 | Qualcomm Incorporated | Direct power transmission load modulation in near field communication devices |

-

2014

- 2014-12-01 JP JP2014243187A patent/JP6485016B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016105560A (ja) | 2016-06-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7120550B2 (en) | Radio-frequency identification circuit oscillator calibration | |

| US7388468B2 (en) | Method and system to backscatter modulate a radio-frequency signal from an RFID tag in accordance with both an oscillation frequency signal and a command signal | |

| US7394324B2 (en) | Method and system to calibrate an oscillator within an RFID circuit utilizing a test signal supplied to the RFID circuit | |

| EP2128804B1 (en) | Transponder and interrogator | |

| CN109428630B (zh) | 用于驱动nfc设备的天线的电路和方法 | |

| US20050225434A1 (en) | Method and system to generate modulator and demodulator clock signals within an RFID circuit utilizing a multi-oscillator architecture | |

| KR101147250B1 (ko) | 적응적으로 펄스 폭 변조 신호를 복조하는 복조기 및 복조방법 | |

| JP2009130389A (ja) | 通信装置、同調周波数調整方法、およびプログラム | |

| US20060022803A1 (en) | Semiconductor device and IC tag for transmitting/receiving data in radio communication | |

| JP6485016B2 (ja) | 無線通信装置、無線通信装置におけるクロックの位相調整方法 | |

| JP4680256B2 (ja) | Icタグ | |

| JP2006040184A (ja) | リーダ・ライタ、それを用いた通信方法及び通信システム | |

| Tang et al. | A novel method to improve the subcarrier frequency accuracy for UHF RFID sensing system | |

| US20050225436A1 (en) | Method and system to calibrate an oscillator within an RFID circuit responsive to a received update value | |

| JP2006229433A (ja) | Rfidタグシステム,rfidタグ及びタグリーダ | |

| US20130094562A1 (en) | Transmitter and transmitting method using delay locked loop | |

| JP4407675B2 (ja) | Icカードリーダ | |

| JP4321490B2 (ja) | 非接触式通信システム | |

| JP2007060416A (ja) | 非接触icタグ、リーダ装置、情報書込システム及びそれらの制御方法 | |

| JP4682478B2 (ja) | 非接触型icカードの通信システム,icカード及びicカードリーダ | |

| JP4407674B2 (ja) | Icカードリーダ | |

| JP6102275B2 (ja) | 増幅回路、アンテナモジュール及び無線通信装置 | |

| JP2018206150A (ja) | 電子回路 | |

| JP2008011198A (ja) | 無線通信装置 | |

| JP4913465B2 (ja) | Icタグ、icタグシステムおよびそのデータの通信方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171109 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180918 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190204 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6485016 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |