JP6445899B2 - 画像形成装置及びその制御方法 - Google Patents

画像形成装置及びその制御方法 Download PDFInfo

- Publication number

- JP6445899B2 JP6445899B2 JP2015037295A JP2015037295A JP6445899B2 JP 6445899 B2 JP6445899 B2 JP 6445899B2 JP 2015037295 A JP2015037295 A JP 2015037295A JP 2015037295 A JP2015037295 A JP 2015037295A JP 6445899 B2 JP6445899 B2 JP 6445899B2

- Authority

- JP

- Japan

- Prior art keywords

- image data

- unit

- processing

- forming apparatus

- partial area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K15/00—Arrangements for producing a permanent visual presentation of the output data, e.g. computer output printers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K15/00—Arrangements for producing a permanent visual presentation of the output data, e.g. computer output printers

- G06K15/02—Arrangements for producing a permanent visual presentation of the output data, e.g. computer output printers using printers

- G06K15/18—Conditioning data for presenting it to the physical printing elements

- G06K15/1848—Generation of the printable image

- G06K15/1856—Generation of the printable image characterized by its workflow

- G06K15/1857—Generation of the printable image characterized by its workflow involving parallel processing in the same printing apparatus

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K15/00—Arrangements for producing a permanent visual presentation of the output data, e.g. computer output printers

- G06K15/02—Arrangements for producing a permanent visual presentation of the output data, e.g. computer output printers using printers

- G06K15/18—Conditioning data for presenting it to the physical printing elements

- G06K15/1848—Generation of the printable image

- G06K15/1849—Generation of the printable image using an intermediate representation, e.g. a list of graphical primitives

- G06K15/1851—Generation of the printable image using an intermediate representation, e.g. a list of graphical primitives parted in a plurality of segments per page

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Record Information Processing For Printing (AREA)

- Image Generation (AREA)

- Facsimiles In General (AREA)

Description

前記部分領域のうち、前記部分領域を分割した前記描画対象領域のいずれかについて画像データの生成が最初に完了した時点で生成されていない画像データの量を、前記複数の描画手段に割り振り、前記時点で各描画手段により生成が完了しているそれぞれの画像データの量に、前記割り振られた量を加えた画像データの量を、次の部分領域についての前記描画対象領域として設定することを特徴とする。

<画像形成装置の構成>

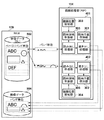

以下、本発明を実施するための形態について図面を用いて説明する。図1は、本発明の第1の実施例における画像形成装置の構成例を示す図である。図1に示すように、画像形成装置100は、コントローラ101、ネットワーク102、操作部103、読取部104、印刷部105を有する。ネットワーク102は、LANやWAN(公衆回線)等で実現され、ホストコンピュータやサーバ等の外部装置と画像形成装置100との間で画像データやデバイス情報を送受信する通信部である。操作部103は、ユーザによる操作を画像処理の制御情報として取得したり、ユーザに対して画像処理の制御情報を表示したりする処理部である。読取部(スキャナエンジン)104は、画像入力デバイスであって、光学センサ等を用いて画像形成装置100の内部に画像データを取り込む処理部である。印刷部(プリンタエンジン)105は、画像出力デバイスであって、画像形成装置100の内部の画像データを記録媒体に印字して出力する処理部である。

次に、図2及び図12を用いて、画像形成装置100におけるPDL印刷処理のデータフロー及び画像データ単位の関係を説明する。図2は、画像形成装置100におけるPDL印刷処理のデータフローを示す図である。図12は、画像形成装置100で扱うページ内での矩形領域の座標系の例を示す図である。なお、図2のデータフローは、画像形成装置100の起動時にRAM109に展開されたプログラムを、CPU108により実行することで実現されるものとする。図2に示すように、画像形成装置100は、ホストコンピュータから送信されたPDLデータを通信部I/F107で受信し、ページ単位のPDLデータ201としてRAM109あるいはHDD111に記憶する。次に、CPU108は、受信したPDLデータ201を解釈し、ページ単位あるいはバンド単位の中間データ(DL)202を作成し、再びRAM109に記憶する。

次に、図3を用いて、本発明におけるPDL印刷時の描画処理の動作を説明する。図3は、RAM109に保持した中間データ(DL)202に対してバンド単位で並列に描画処理を実行した後に、ブロック単位の圧縮画像データ205を再びRAM109に記憶するまでの内部動作を示している。

ここディスプレイリストと第1描画部401および第2描画部402それぞれによる描画処理についてもう少し詳しく説明する。中間データであるディスプレイリストには、たとえばページ単位のベクトルオブジェクトが、それぞれの位置やレベルを示す情報とともに含まれて(記述されて)いる。各描画部は、入力された描画オブジェクトを、その位置やレベルに応じた描画処理(スキャンラインレンダリング)を行って画像データ(ラスタデータ)を生成する。描画処理は大きく分けて、エッジ処理、レベル処理、フィル処理、コンポジット処理の4つに分かれている。

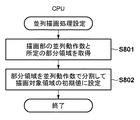

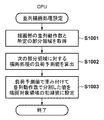

図7は、PDL印刷処理を説明するためのコントローラ101により実行されるフローチャートである。まず、CPU108は、ホストコンピュータから送信されたPDLデータを通信部I/F107を介して受信し、ページ単位のPDLデータとしてRAM109あるいはHDD111に記憶する(S701)。次に、CPU108は、受信したPDLデータを解釈し(S702)、解釈した情報を元に中間データ(DL)を生成する(S703)。次に、CPU108は、描画処理部114による並列描画処理設定を実行する(S704)。S704については、図8のフローチャートを用いて別途説明する。次に、CPU108は、描画処理部114を制御して描画処理部114を構成する複数の描画部を用いた描画処理を実行する(S705)。S705については、図9のフローチャートを用いて別途説明する。次に、CPU108は、圧縮処理部116を制御して圧縮処理を実行した後に、RAM109に圧縮画像データを記憶する(S706)。次に、CPU108は、伸張処理部117を制御して、RAM109に記憶された圧縮画像データに対して伸張処理を実行した後に、再びRAM109に画像データを記憶する(S707)。次に、CPU108は、印刷部I/F118を制御してRAM109から印刷部105に対して画像データを転送し、印刷部105のデバイス特性に合わせた補正の画像処理を行った後に、印刷部105に対して画像処理後の画像データを転送する(S708)。その後、印刷部105は、印刷部I/F118から転送された画像データを記録媒体に印字して出力する(S709)。

図8は、並列描画処理の初期設定を説明するためのフローチャートである。まず、CPU108は、描画処理部114において並列処理を行う並列動作数、及び、画像処理部114の後処理で扱う画像データ単位として所定の部分領域を取得する(S801)。ここで、並列動作数は、例えば、描画処理部114が図3に示す構成の場合、第1描画部401と第2描画部402とが並列動作するので、並列動作数は2となる。また、描画処理部114による処理対象の部分領域は、画像処理部114の後処理としての圧縮処理部116で扱う画像データに対応して定まる画像データサイズを有する領域であって、例えば、32画素×32画素の正方形タイル形状をもつブロック単位の複数個分に対応するものとする。ここで、部分領域に対応する画像データサイズ分の記憶領域の容量は、ブロックRAM115のダブルバッファのように描画処理部114と圧縮処理部116の双方の処理を停止させることなく読み書きできるものとする。上記の例の場合、所定の部分領域は、ブロックの高さとページ単位の主走査幅とを持つ領域、たとえば32ラインで構成された領域となる。このため、部分領域のサイズは、ブロックサイズが後段の処理部たとえば圧縮処理部116の仕様により決まっているなら、処理対象のページのサイズによって決定できる。

図9は、並列描画処理を説明するためのフローチャートである。以下、CPU108の制御に基づいて描画処理部114が動作するものとして説明する。まず、描画処理部114で並列に動作する各描画部の読み出し処理部は、CPU108から描画処理部114の内部レジスタに設定された中間データ(DL)の先頭アドレスを取得する(S901)。次に、描画処理部114は、S801でCPU108から設定された並列動作数と所定の部分領域を取得する(S902)。すなわち、上記の例の場合、並列動作数を2、部分領域のバンドの高さを32ラインとする。次に、描画処理部114における各描画部は、S802でCPU108から設定された描画対象領域の初期値を取得する(S903)。すなわち、上記の例の場合、第1描画部401が担当する描画対象領域の初期値は、1ライン目から16ライン目までの16ライン分となり、第2描画部402が担当する描画対象領域の初期値は、17ライン目から32ライン目までの16ライン分となる。次に、描画処理部114における各描画部は、S901で取得した中間データ(DL)の先頭アドレスから描画する部分領域内に含まれる描画オブジェクトを参照して、該当する描画オブジェクトをすべて取得する(S904)。次に、描画処理部114における各描画部は、取得した描画オブジェクトが、自身が担当する描画対象領域内であるか否かを判断し(S905)、描画対象領域内であれば(YES)、S906に遷移し、描画対象領域外でなければ(NO)、S907に遷移する。

第1の実施例では、描画処理部114で生成した画像データがRAM109とは異なるローカルメモリとしてのブロックRAM115に一時保持したが、本変形例では、描画処理部114で生成した画像データを直接RAM109に格納する構成例を示す。

第1の実施例では、描画処理部114の内部で実測の描画位置に基づく描画対象領域の割合の変更を行ったが、本変形例では、スキャンライン毎に予測した負荷予測値が与えられた場合の組み合わせによる構成例を示す。

第1の実施例では、ページ単位の主走査幅を持つバンド単位の部分領域、更には部分領域を構成する描画対象領域を複数の描画処理部に割り当てたが、図12(c)に示すように、ページ単位を主走査方向で分割したバンド単位で順次描画出力しても良い。この場合、ブロックRAM115を構成するバッファ容量を小さく抑えることができる。

第1の実施例では、並列動作数が2の例を示したが、3以上の場合でも同様の考え方で割り当てを変更できる。例えば、並列動作数が3の場合、1番目に描画処理が完了した描画部が、他の2つの描画部の描画位置をそれぞれ参照し、1番目と3番目の間で割り当てを変更し、2番目は均等分割に相当する割り当てを維持する方法が考えられる。同様に、例えば、並列動作数が4の場合、1番目と4番目の間で割り当てを変更し、2番目と3番目の間で割り当てを変更する方法が考えられる。

変形例2において、負荷予測処理そのものの処理負荷が重く、本来の描画処理の開始が遅延する可能性がある場合は、負荷予測値を用いずに第1の実施例に記載の実測した描画位置に基づく割り当ての変更のみを実施するように制御しても良い。

第1の実施例では、一方の描画部による対象バンドの描画処理が完了した時点における他方の描画部による処理の進捗を、対象バンドの処理済みライン数を参照することで決定していた。これに対して、進捗を例えば時間で決定することもできる。たとえば各描画部は、それぞれの対象バンドの処理を開始時にタイマをスタートさせ、終了時にタイマの値を読み取ることで、描画処理に要した時間を測定する。そして、全描画部によるバンドの描画処理が完了したなら、測定した時間差をライン数の差に換算し、第1の実施例またはその変形例と同様の手順で、次の対象バンドの高さを決定する。たとえば、先に対象バンドの処理を完了させた描画部による対象バンド高さをHf、処理時間をTf、後に対象バンドの処理を完了させた描画部による対象バンド高さをHs、処理時間をTs、測定した前記時間差をΔTとする。先に対象バンドの処理を完了させた描画部による次の対象バンド高さHfnはたとえば、Hfn=Hf(1+(ΔT/2)*(1/Tf))とする。後に対象バンドの処理を完了させた描画部による次の対象バンド高さHsnはたとえば、Hsn=Hs−(Hfn−Hf)とする。ここでHf+Hs=Hfn+Hsn=ブロック高さである。

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

Claims (13)

- 並列に動作可能な複数の描画手段を有し、前記複数の描画手段それぞれにより、所定高さの部分領域の画像データを、該部分領域を分割した描画対象領域ごとに分担して生成する画像形成装置であって、

前記部分領域のうち、前記部分領域を分割した前記描画対象領域のいずれかについて画像データの生成が最初に完了した時点で生成されていない画像データの量を、前記複数の描画手段に割り振り、前記時点で各描画手段により生成が完了しているそれぞれの画像データの量に、前記割り振られた量を加えた画像データの量を、次の部分領域についての前記描画対象領域として設定することを特徴とする画像形成装置。 - 前記複数の描画手段はそれぞれ、

前記部分領域において前記複数の描画手段が生成中の位置を保持する保持手段と、

前記部分領域において前記複数の描画手段のそれぞれが、他の描画手段が生成中の位置を検知する検知手段と

を有し、

前記描画対象領域の画像データの生成を最初に完了した描画手段が、他の描画手段の前記保持手段により保持された生成中の位置を前記検知手段により検知することで、前記部分領域を分割した前記描画対象領域のいずれかについて画像データの生成が最初に完了した時点で生成されていない前記画像データの量を決定することを特徴とする請求項1に記載の画像形成装置。 - 前記複数の描画手段により生成された前記部分領域の画像データを記憶する記憶手段と、

前記記憶手段に記憶された画像データを読み出す読み出し手段とを更に有し、

前記読み出し手段は、前記複数の描画手段により前記部分領域の画像データが生成されたときに前記記憶手段により記憶された画像データを読み出すことを特徴とする請求項1又は2に記載の画像形成装置。 - 前記記憶手段には、前記部分領域を記憶する少なくとも二つの領域が含まれ、

前記複数の描画手段により生成された部分領域の画像データは、前記少なくとも二つの領域に、交互に記憶されることを特徴とする請求項3に記載の画像形成装置。 - 前記複数の描画手段は、オブジェクトにより記述された中間データから前記画像データを生成することを特徴とする請求項1乃至4のいずれか一項に記載の画像形成装置。

- 前記画像データはラスタ形式の画像データであり、前記複数の描画手段は、ライン単位で画像データを生成することを特徴とする請求項1乃至5のいずれか一項に記載の画像形成装置。

- 前記複数の描画手段による描画データを生成する処理の負荷予測値を前記ライン単位で求める手段を更に有し、

前記複数の描画手段は、前記描画対象領域の画像データの各ラインに前記負荷予測値により重み付けして重み付けした画像データの量を決定し、前記画像データの量として、前記負荷予測値により重み付けした画像データの量を用いることを特徴とする請求項6に記載の画像形成装置。 - 前記部分領域は、ページを均等な高さに分割した領域であることを特徴とする請求項1乃至7のいずれか一項に記載の画像形成装置。

- 前記部分領域は、ページを均等な高さ及び幅に分割した領域であることを特徴とする請求項1乃至8のいずれか一項に記載の画像形成装置。

- 前記複数の描画手段として、2つの描画手段を有し、

前記2つの描画手段のそれぞれにより、前記部分領域を高さ方向に更に分割した描画対象領域の画像データを生成することを特徴とする請求項8又は9に記載の画像形成装置。 - 前記部分領域の画像データを圧縮する圧縮手段を更に有することを特徴とする請求項1乃至10のいずれか一項に記載の画像形成装置。

- 並列に動作可能な複数の描画手段を有し、前記複数の描画手段それぞれにより、所定高さの部分領域の画像データを、該部分領域を分割した描画対象領域ごとに分担して生成する画像形成装置の制御方法であって、

前記部分領域のうち、前記部分領域を分割した前記描画対象領域のいずれかについて画像データの生成が最初に完了した時点で生成されていない画像データの量を、前記複数の描画手段に割り振り、前記時点で各描画手段により生成が完了しているそれぞれの画像データの量に、前記割り振られた量を加えた画像データの量を、次の部分領域についての前記描画対象領域として設定することを特徴とする画像形成装置の制御方法。 - コンピュータにより請求項12に記載の画像形成装置の制御方法を実行させるためのプログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015037295A JP6445899B2 (ja) | 2015-02-26 | 2015-02-26 | 画像形成装置及びその制御方法 |

| US15/045,568 US9600747B2 (en) | 2015-02-26 | 2016-02-17 | Image forming apparatus and control method that execute a plurality of rendering processing units in parallel |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015037295A JP6445899B2 (ja) | 2015-02-26 | 2015-02-26 | 画像形成装置及びその制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016159437A JP2016159437A (ja) | 2016-09-05 |

| JP2016159437A5 JP2016159437A5 (ja) | 2018-04-12 |

| JP6445899B2 true JP6445899B2 (ja) | 2018-12-26 |

Family

ID=56799128

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015037295A Expired - Fee Related JP6445899B2 (ja) | 2015-02-26 | 2015-02-26 | 画像形成装置及びその制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9600747B2 (ja) |

| JP (1) | JP6445899B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6544905B2 (ja) * | 2014-09-29 | 2019-07-17 | キヤノン株式会社 | 画像処理装置、画像処理方法、プログラム |

| JP6772020B2 (ja) | 2016-10-06 | 2020-10-21 | キヤノン株式会社 | 画像処理装置、画像処理装置の制御方法、及びプログラム |

| JP6876247B2 (ja) * | 2017-03-09 | 2021-05-26 | コニカミノルタ株式会社 | 画像形成装置 |

| KR102663537B1 (ko) | 2019-01-31 | 2024-05-08 | 삼성전자 주식회사 | 전자 장치 및 이미지 처리 방법 |

| CN113986409B (zh) * | 2021-09-14 | 2024-08-06 | 阿里巴巴(中国)有限公司 | 信息交互方法、装置、设备及存储介质 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000132350A (ja) * | 1998-10-21 | 2000-05-12 | Fuji Xerox Co Ltd | 描画処理装置 |

| US7266254B2 (en) * | 2002-02-13 | 2007-09-04 | Canon Kabushiki Kaisha | Data processing apparatus, image processing apparatus, and method therefor |

| US20040246502A1 (en) * | 2003-06-09 | 2004-12-09 | Jacobsen Dana A. | Rendering sub-sections |

| US7277095B2 (en) * | 2004-03-16 | 2007-10-02 | Canon Kabushiki Kaisha | Method of rendering graphical objects |

| JP3892016B2 (ja) * | 2005-02-23 | 2007-03-14 | 株式会社ソニー・コンピュータエンタテインメント | 画像処理装置および画像処理方法 |

| JP4408836B2 (ja) * | 2005-05-30 | 2010-02-03 | キヤノン株式会社 | 画像処理装置及びその制御方法、プログラム |

| JP5300317B2 (ja) | 2008-05-09 | 2013-09-25 | キヤノン株式会社 | 画像処理装置及びその制御方法 |

| JP2011158951A (ja) * | 2010-01-29 | 2011-08-18 | Konica Minolta Business Technologies Inc | 画像処理装置、プログラム及び画像処理方法 |

| JP2012081626A (ja) * | 2010-10-08 | 2012-04-26 | Ricoh Co Ltd | 画像形成装置、画像処理方法、プログラム |

| JP2012254583A (ja) * | 2011-06-09 | 2012-12-27 | Canon Inc | 画像形成装置、画像形成方法、及びコンピュータプログラム |

| JP6128782B2 (ja) * | 2012-09-07 | 2017-05-17 | キヤノン株式会社 | 画像処理装置、画像処理装置の制御方法、プログラム、及び記憶媒体 |

-

2015

- 2015-02-26 JP JP2015037295A patent/JP6445899B2/ja not_active Expired - Fee Related

-

2016

- 2016-02-17 US US15/045,568 patent/US9600747B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20160253129A1 (en) | 2016-09-01 |

| US9600747B2 (en) | 2017-03-21 |

| JP2016159437A (ja) | 2016-09-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6445899B2 (ja) | 画像形成装置及びその制御方法 | |

| JP6029344B2 (ja) | 画像処理装置、画像処理方法、プログラム | |

| US8212815B2 (en) | Drawing apparatus, drawing program, and drawing method | |

| JP5051327B1 (ja) | 画像処理装置及びプログラム | |

| US20180082160A1 (en) | Image processing apparatus and image processing method | |

| JP5675445B2 (ja) | 情報処理装置、情報処理装置の制御方法、及びコンピュータプログラム | |

| JP6544905B2 (ja) | 画像処理装置、画像処理方法、プログラム | |

| JP6772020B2 (ja) | 画像処理装置、画像処理装置の制御方法、及びプログラム | |

| JP2017024321A (ja) | 画像処理装置、画像形成装置及び画像処理時間予測方法及びプログラム | |

| KR101945581B1 (ko) | 화상 처리 장치, 화상 처리 방법, 및 저장 매체 | |

| JP6460627B2 (ja) | 原稿を読み取ることで得られた画像データに基づく印刷を行うことが可能な画像処理装置、画像処理装置の制御方法、およびプログラム | |

| CN107203354B (zh) | 图像处理设备及其控制方法 | |

| JP6904717B2 (ja) | 画像処理装置、その制御方法、およびプログラム | |

| JP6902861B2 (ja) | 符号化装置、符号化方法、復号装置、復号方法および生成方法 | |

| JP2013123118A (ja) | 画像処理装置、画像処理方法、およびプログラム | |

| JP6434775B2 (ja) | 画像形成装置およびその制御方法、並びにプログラム | |

| JP2017189968A (ja) | 画像処理装置及び画像処理方法 | |

| JP2016206934A (ja) | 画像処理装置、画像処理方法及びプログラム | |

| JP2021022024A (ja) | 画像処理装置、画像処理方法およびプログラム | |

| JP2016052724A (ja) | 画像処理装置、画像処理方法、およびプログラム | |

| JP2017087514A (ja) | 画像処理装置、画像処理方法、およびプログラム | |

| JP2002158852A (ja) | 画像処理装置 | |

| JP4840033B2 (ja) | 画像処理プログラムおよび画像処理装置 | |

| JP2000255116A (ja) | 印刷処理装置および印刷処理方法 | |

| JP3514895B2 (ja) | 画像展開処理方法及び装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180226 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20181102 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181031 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20181130 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6445899 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |