JP6367939B2 - 基板内のソレノイドインダクタ - Google Patents

基板内のソレノイドインダクタ Download PDFInfo

- Publication number

- JP6367939B2 JP6367939B2 JP2016529451A JP2016529451A JP6367939B2 JP 6367939 B2 JP6367939 B2 JP 6367939B2 JP 2016529451 A JP2016529451 A JP 2016529451A JP 2016529451 A JP2016529451 A JP 2016529451A JP 6367939 B2 JP6367939 B2 JP 6367939B2

- Authority

- JP

- Japan

- Prior art keywords

- pad

- wiring

- implementations

- substrate

- inductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000000758 substrate Substances 0.000 claims description 205

- 238000004804 winding Methods 0.000 claims description 202

- 238000000034 method Methods 0.000 claims description 132

- 239000011521 glass Substances 0.000 claims description 15

- 229910052710 silicon Inorganic materials 0.000 claims description 15

- 239000010703 silicon Substances 0.000 claims description 15

- 239000000919 ceramic Substances 0.000 claims description 14

- 230000001939 inductive effect Effects 0.000 claims description 9

- 238000004891 communication Methods 0.000 claims description 8

- 230000008878 coupling Effects 0.000 claims description 3

- 238000010168 coupling process Methods 0.000 claims description 3

- 238000005859 coupling reaction Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 291

- 239000002184 metal Substances 0.000 description 151

- 229910052751 metal Inorganic materials 0.000 description 151

- 230000008569 process Effects 0.000 description 101

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 90

- 229910052802 copper Inorganic materials 0.000 description 74

- 239000010949 copper Substances 0.000 description 74

- 239000002131 composite material Substances 0.000 description 41

- 238000007747 plating Methods 0.000 description 27

- 239000012792 core layer Substances 0.000 description 22

- 238000000059 patterning Methods 0.000 description 18

- 238000004806 packaging method and process Methods 0.000 description 17

- 239000011889 copper foil Substances 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 15

- 239000007769 metal material Substances 0.000 description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 12

- 238000005530 etching Methods 0.000 description 12

- 239000011888 foil Substances 0.000 description 12

- 238000005553 drilling Methods 0.000 description 11

- 238000010586 diagram Methods 0.000 description 9

- 239000000463 material Substances 0.000 description 8

- 239000004065 semiconductor Substances 0.000 description 8

- 239000000654 additive Substances 0.000 description 6

- 229910000990 Ni alloy Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 150000001879 copper Chemical class 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/10—Inductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F17/00—Fixed inductances of the signal type

- H01F17/0006—Printed inductances

- H01F17/0013—Printed inductances with stacked layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/02—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets

- H01F41/04—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets for manufacturing coils

- H01F41/041—Printed circuit coils

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F17/00—Fixed inductances of the signal type

- H01F17/0006—Printed inductances

- H01F2017/0053—Printed inductances with means to reduce eddy currents

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Coils Or Transformers For Communication (AREA)

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Micromachines (AREA)

Description

本出願は、その内容全体が参照によって本明細書に組み込まれる、2013年11月13日に米国特許商標庁に出願された、米国非仮特許出願第14/079,488号の優先権および利益を主張する。

いくつかの新規の特徴は、基板と基板内のインダクタとを含む集積デバイス(たとえば、半導体デバイス)に関する。いくつかの実装形態では、インダクタは、ソレノイドインダクタである。インダクタは、巻線のセットを含む。巻線のセットは、内周囲(たとえば、内周)を有する。巻線のセットは、配線のセットとビアのセットとを含む。配線のセットおよびビアのセットは、巻線のセットの内周囲の外側に配置される。いくつかの実装形態では、巻線のセットは、キャプチャパッドのセットをさらに含む。配線のセットは、キャプチャパッドのセットを介してビアのセットに結合される。いくつかの実装形態では、巻線のセットは、外周囲(たとえば、外周)を有する。パッドのセットは、巻線のセットの外周囲の外側に少なくとも一部があるように配線のセットに結合される。いくつかの実装形態では、巻線のセットは、外周囲を含み、キャプチャパッドのセットは、インダクタの内側部分および巻線のセットから突出するように配線のセットに結合される。いくつかの実装形態では、配線のセットは、第1の配線および第2の配線を含み、ビアのセットは、第1のビアおよび第2のビアを含み、パッドのセットは、第1のキャプチャパッドおよび第2のキャプチャパッドを含む。いくつかの実装形態では、第1の配線は、第1のパッドを介して第1のビアに結合され、第1のビアは、第2のパッドを介して第2の配線に結合される。いくつかの実装形態では、基板は、少なくとも誘電体、ガラス、セラミック、および/またはシリコンのうちの1つを含む。いくつかの実装形態では、基板は、パッケージング用基板である。

図2〜図3は、デバイス(たとえば、集積デバイス、半導体デバイス)用の新規のインダクタを概念的に示す。詳細には、図2は、巻線のセット202、第1のキャプチャパッド204、第2のキャプチャパッド206、第1のポート207、および第2のポート209を含むインダクタ200の上面図を示す。いくつかの実装形態では、インダクタ200は、ソレノイドインダクタである。いくつかの実装形態では、インダクタ200は、基板(たとえば、ラミネート基板、ガラス基板、セラミック基板、シリコン基板)内に配置される。巻線のセット202は、らせん状配線(たとえば、金属層)を含む。図2に示すように、インダクタ200は、内周囲220(たとえば、内周)および外周囲222(たとえば、外周)を有する。いくつかの実装形態では、巻線のセット202(たとえば、配線)は、内周囲220および外周囲222を有する。内周囲220は、内半径を有する。図2にさらに示すように、インダクタ200の構成要素のいずれも、内周囲220内に配置されていない。すなわち、インダクタ200の構成要素のすべてが、内周囲220上、または内周囲220の外側にある。いくつかの実装形態では、第1のパッド204および第2のパッド206は、渦電流損を低減/最小化するために内周囲220の外側にある。いくつかの実装形態では、渦電流損を低減/最小化することは、巻線のセット202および/またはインダクタ200のQ値(Q)の増加をもたらし得る。

図7〜図8は、デバイス(たとえば、集積デバイス、半導体デバイス)用の新規のインダクタを概念的に示す。詳細には、図7は、巻線のセット702、第1のキャプチャパッド704、第2のキャプチャパッド706、第1のポート707、および第2のポート709を含むインダクタ700の上面図を示す。巻線のセット702は、非円形である。特に、巻線のセット702は、八角形のらせんを形成する。いくつかの実装形態では、インダクタ700は、ソレノイドインダクタである。いくつかの実装形態では、インダクタ700は、基板(たとえば、ラミネート基板、ガラス基板、セラミック基板、シリコン基板)内に配置される。巻線のセット702は、らせん状配線(たとえば、金属層)を含む。いくつかの実装形態では、インダクタ700は、インダクタ200が円形のらせんを有する一方でインダクタ700が八角形のらせんを有することを除けば、図2のインダクタ200と同様である。

図9〜図10は、デバイス(たとえば、半導体デバイス)用の別の新規のインダクタを概念的に示す。詳細には、図9は、巻線のセット902、第1のパッド904、第2のパッド906、第3のパッド908、第1のポート907、および第2のポート909を含むインダクタ900の上面図を示す。いくつかの実装形態では、インダクタ900は、基板(たとえば、ラミネート基板、ガラス基板、セラミック基板、シリコン基板)内に配置される。巻線のセット902は、らせん状配線(たとえば、金属層)を含む。図9に示すように、インダクタ900は、内周囲920(たとえば、内周)および外周囲922(たとえば、外周)を有する。いくつかの実装形態では、巻線のセット902は、内周囲920および外周囲922を有する。内周囲920は、内半径を有する。図9にさらに示すように、インダクタ900の構成要素のいずれも、内周囲920内に配置されていない。すなわち、インダクタ900の構成要素のすべてが、内周囲920上、または内周囲920の外側にある。

図14〜図15は、デバイス(たとえば、半導体デバイス)用の別の新規のインダクタを概念的に示す。詳細には、図14は、巻線のセット1402、第1のパッド1404、第2のパッド1406、第3のパッド1408、第1のポート1407、および第2のポート1409を含むインダクタ1400の上面図を示す。いくつかの実装形態では、インダクタ1400は、基板および/またはダイ内に配置される。巻線のセット1402は、八角形のらせん状配線(たとえば、金属層)を含む。いくつかの実装形態では、インダクタ1400は、インダクタ900が円形のらせんを有する一方でインダクタ1400が八角形のらせんを有することを除けば、図9のインダクタ900と同様である。

図16A〜図16Dは、インダクタ(たとえば、ソレノイドインダクタ)を含む基板を提供/製造するための例示的なシーケンスを示す。明瞭性および単純化の目的のために、図16A〜図16Dのプロセスは、基板を製造するすべてのステップおよび/または段階を必ずしも含まないことに留意されたい。さらに、いくつかの事例では、いくつかのステップおよび/または段階は、プロセスの説明を簡単にするために、単一のステップおよび/または段階に結合されている場合がある。図16A〜図16Dのパターンの形状、パターン特徴部、構成要素(たとえば、複合材料導電性トレース、ビア)は、概念的な例にすぎず、パターンの実際の形状および形態、パターン特徴部、ならびに構成要素を必ずしも表さないものとすることにも留意されたい。

図17は、ソレノイドインダクタを含む基板を製造するためのモディファイドセミアディティブ工法(mSAP)パターニングプロセスの流れ図を示す。図17について、いくつかの実装形態のmSAPプロセス中の基板の層(たとえば、コア層、プリプレグ層)のシーケンスを示す図18を参照しながら説明する。

図22は、新規のソレノイドインダクタを含む基板を設けるための方法の例示的な流れ図を示す。いくつかの実装形態では、図22の方法は、図2、3、4、5、6、7、8、9、10、11、12、13、14、および/または15のインダクタを提供するために使用され得る。

図23は、上述の集積デバイス(たとえば、半導体デバイス)、集積回路、ダイ、インターポーザ、および/またはパッケージのうちのいずれかと統合され得る様々な電子デバイスを示す。たとえば、モバイル電話2302、ラップトップコンピュータ2304、および固定位置端末2306が、本明細書で説明した集積回路(IC)2300を含み得る。IC2300は、たとえば、本明細書で説明した集積デバイス、集積回路、ダイ、またはパッケージのうちのいずれかであり得る。図23に示すデバイス2302、2304、2306は、単なる例示である。限定はしないが、モバイルデバイス、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、GPS対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンタテイメントユニット、メータ読取り機器などの固定位置データユニット、通信デバイス、スマートフォン、タブレットコンピュータ、またはデータもしくはコンピュータ命令の記憶もしくは取り出しを行う任意の他のデバイス、またはそれらの任意の組合せを含む他の電子デバイスが、IC2300を採用することもできる。

102 巻線のセット

104 第1のポート

106 ビア

108 第2のポート

200 インダクタ

202 巻線のセット

204 第1のキャプチャパッド

206 第2のキャプチャパッド

207 第1のポート

209 第2のポート

212 第1の金属層

214 第2の金属層

216 第3の金属層

220 内周囲

222 外周囲

224 第3のキャプチャパッド

226 第4のキャプチャパッド

234 第1のビア

236 第2のビア

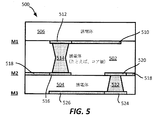

500 集積デバイス

502 第1の誘電体層

504 第2の誘電体層

506 第3の誘電体層

510 第1の配線

512 第1のパッド

514 第1のビア

516 第2のパッド

518 第2の配線

520 第3のパッド

522 第2のビア

524 第4のパッド

526 第3の配線

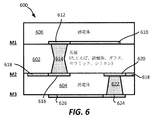

600 集積デバイス

602 基板層

604 第1の誘電体層

606 第2の誘電体層

610 第1の配線

612 第1のパッド

614 第1のビア

616 第2のパッド

618 第2の配線

620 第3のパッド

622 第2のビア

624 第4のパッド

626 第3の配線

700 インダクタ

702 巻線のセット

704 第1のキャプチャパッド

706 第2のキャプチャパッド

707 第1のポート

709 第2のポート

720 内周囲

722 外周囲

800 内周

802 外周

900 インダクタ

902 巻線のセット

904 第1のパッド

906 第2のパッド

907 第1のポート

908 第3のパッド

909 第2のポート

912 第1の金属層

914 第2の金属層

916 第3の金属層

918 第4の金属層

920 内周囲

922 外周囲

924 第4のパッド

926 第5のパッド

928 第6のパッド

934 第1のビア

936 第2のビア

938 第3のビア

1200 集積デバイス

1202 第1の誘電体層

1204 第2の誘電体層

1206 第3の誘電体層

1207 第1の配線

1208 第1のパッド

1209 第1のビア

1210 第2のパッド

1211 第2の配線

1212 第3のパッド

1214 第2のビア

1216 第4のパッド

1218 第3の配線

1220 第5のパッド

1222 第3のビア

1224 第6のパッド

1226 第4の配線

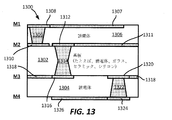

1300 集積デバイス

1302 基板層

1304 第1の誘電体層

1306 第2の誘電体層

1307 第1の配線

1308 第1のパッド

1309 第1のビア

1310 第2のパッド

1311 第2の配線

1312 第3のパッド

1314 第2のビア

1316 第4のパッド

1318 第3の配線

1320 第5のパッド

1322 第3のビア

1324 第6のパッド

1326 第4の配線

1400 インダクタ

1402 巻線のセット

1404 第1のパッド

1406 第2のパッド

1407 第1のポート

1408 第3のパッド

1409 第2のポート

1420 内周囲

1422 外周囲

1500 内周

1502 外周

1602 コア層

1604 第1の金属層

1606 第2の金属層

1608 ビアパターン特徴部

1609 ビア特徴部

1610 第1のプリプレグ層

1611 複合材料導電性トレース

1612 第2のプリプレグ層

1614 第3の金属層

1616 第4の金属層

1617 ビアパターン特徴部

1618 ビア特徴部

1620 複合材料導電性トレース

1802 誘電体層

1804 銅層

1806 ドライフィルムレジスト、DFR

1808 開口部

1810 銅複合材料

2002 誘電体

2004 プライマ

2006 銅箔

2008 銅シード層

2010 ドライフィルムレジスト、DFR

2012 開口部

2300 集積回路、IC

2302 モバイル電話

2304 ラップトップコンピュータ

2306 固定位置端末

Claims (24)

- 複数の層を有する基板と、

前記基板の前記複数の層内に形成されたインダクタであって、巻線のセットを形成するためにビアのセットおよびパッドのセットと直列に結合された配線のセットを含み、前記巻線のセットにおける各巻線の内周囲が、前記巻線のセットにおける各巻線に共通している内半径を有する、インダクタと

を含み、

前記配線のセット、前記パッドのセット、および前記ビアのセットが、各巻線の前記内周囲の外側のみに配置され、前記パッドのセットにおける各パッドの少なくとも一部が、各巻線の外周囲の外側に配置され、各配線の長さが、巻線の周未満であり、前記配線のセットにおける各配線の幅が、前記ビアのセットにおける各ビアの幅未満である、集積デバイス。 - 前記配線のセットが前記パッドのセットを介して前記ビアのセットに結合される、請求項1に記載の集積デバイス。

- 前記配線のセットが第1の配線および第2の配線を含み、前記ビアのセットが第1のビアおよび第2のビアを含み、前記パッドのセットが第1のパッドおよび第2のパッドを含む、請求項2に記載の集積デバイス。

- 前記第1の配線が前記第1のパッドを介して前記第1のビアに結合され、前記第1のビアが前記第2のパッドを介して前記第2の配線に結合される、請求項3に記載の集積デバイス。

- 前記インダクタが、ソレノイドインダクタである、請求項1に記載の集積デバイス。

- 前記基板が、誘電体、ガラス、セラミック、およびシリコンのうちの少なくとも1つを含む、請求項1に記載の集積デバイス。

- 前記巻線のセットが非円形巻線を有する、請求項1に記載の集積デバイス。

- 前記集積デバイスが、音楽プレーヤ、ビデオプレーヤ、エンタテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、およびラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項1に記載の集積デバイス。

- 前記配線のセットにおける各配線の幅が、前記パッドのセットにおける各パッドの幅未満である、請求項1に記載の集積デバイス。

- 複数の層を有する基板と、

前記基板の前記複数の層に形成された誘導性手段であって、前記基板内の横方向に沿った電気的横方向経路を提供するための巻線手段のセット、および、複数の前記巻線手段を直列に結合するための且つ前記基板内の垂直方向に沿った電気的垂直方向経路を提供するためのビアおよびパッド手段のセットを含み、前記巻線手段のセットならびに前記ビアおよびパッド手段のセットが巻線のセットを形成し、前記巻線のセットにおける各巻線の内周囲が、前記巻線のセットにおける各巻線の内周囲に共通している内半径を有する、誘導性手段と、

を含み、

前記巻線手段のセットならびにビアおよびパッド手段のセットが、各巻線の内周囲の外側のみに配置され、前記ビアおよびパッド手段のセットにおける各パッドの少なくとも一部が、各巻線の外周囲の外側に配置され、前記巻線手段のセットにおける各巻線手段の幅が、前記ビアおよびパッド手段における各ビアの幅未満である、装置。 - 前記ビアおよびパッド手段が、前記巻線手段および前記誘導性手段の内側部分から突出する、請求項10に記載の装置。

- 前記巻線手段が第1の配線および第2の配線を含み、前記ビアおよびパッド手段が、第1のビア、第2のビア、第1のパッド、および第2のパッドを含む、請求項10に記載の装置。

- 前記基板が、誘電体、ガラス、セラミック、およびシリコンのうちの少なくとも1つを含む、請求項10に記載の装置。

- 前記巻線のセットが非円形巻線を有する、請求項10に記載の装置。

- 前記装置が、音楽プレーヤ、ビデオプレーヤ、エンタテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、およびラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項10に記載の装置。

- 前記巻線手段のセットにおける各巻線手段の幅が、前記ビアおよびパッド手段における各パッドの幅未満である、請求項10に記載の装置。

- 集積デバイスを設けるための方法であって、

複数の層を有する基板を設けるステップと、

前記基板の前記複数の層内に形成される配線のセットを設けるステップと、

前記配線のセットを結合するのに前記基板内にビアのセットを設けるステップと、

前記基板においてパッドのセットを設けて、インダクタとして動作するように構成された巻線のセットを形成するために前記パッドのセットを介して直列で前記ビアのセットへ前記配線のセットを結合するステップであって、前記巻線のセットにおける各巻線の内周囲が、前記巻線のセットにおける各巻線に共通している内半径を有する、ステップと、

各巻線の前記内周囲の外側のみに前記配線のセット、前記パッドのセットおよび前記ビアのセットを配置して、各巻線の外周囲の外側に前記パッドのセットにおける各パッドの少なくとも一部を配置するステップと、

を含み、前記配線のセットにおいて提供される各配線の幅が、前記ビアのセットにおいて提供される各ビアの幅未満である、方法。 - 前記パッドのセットは、前記インダクタの内側部分および前記巻線のセットから突出するように前記配線のセットに結合される、請求項17に記載の方法。

- 前記配線のセットが第1の配線および第2の配線を含み、前記ビアのセットが第1のビアおよび第2のビアを含み、前記パッドのセットが第1のパッドおよび第2のパッドを含む、請求項17に記載の方法。

- 前記第1の配線が前記第1のパッドを介して前記第1のビアに結合され、前記第1のビアが前記第2のパッドを介して前記第2の配線に結合される、請求項19に記載の方法。

- 前記基板が、誘電体、ガラス、セラミック、およびシリコンのうちの少なくとも1つを含む、請求項17に記載の方法。

- 前記巻線のセットが、非円形巻線を有する請求項17に記載の方法。

- 前記集積デバイスが、音楽プレーヤ、ビデオプレーヤ、エンタテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、およびラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項17に記載の方法。

- 前記配線のセットにおいて提供される各配線の幅が、前記パッドのセットにおいて提供される各パッドの幅未満である、請求項17に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/079,488 US9806144B2 (en) | 2013-11-13 | 2013-11-13 | Solenoid inductor in a substrate |

| US14/079,488 | 2013-11-13 | ||

| PCT/US2014/064299 WO2015073295A1 (en) | 2013-11-13 | 2014-11-06 | Solonoid inductor in a substrate |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016538721A JP2016538721A (ja) | 2016-12-08 |

| JP2016538721A5 JP2016538721A5 (ja) | 2018-02-08 |

| JP6367939B2 true JP6367939B2 (ja) | 2018-08-01 |

Family

ID=51947506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016529451A Expired - Fee Related JP6367939B2 (ja) | 2013-11-13 | 2014-11-06 | 基板内のソレノイドインダクタ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9806144B2 (ja) |

| EP (1) | EP3069356B1 (ja) |

| JP (1) | JP6367939B2 (ja) |

| CN (1) | CN105723477B (ja) |

| WO (1) | WO2015073295A1 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6432531B2 (ja) * | 2015-03-27 | 2018-12-05 | 株式会社村田製作所 | 積層コイル部品 |

| US10249580B2 (en) | 2016-06-22 | 2019-04-02 | Qualcomm Incorporated | Stacked substrate inductor |

| US10490348B2 (en) | 2016-06-24 | 2019-11-26 | Qualcomm Incorporated | Two-dimensional structure to form an embedded three-dimensional structure |

| US10163771B2 (en) * | 2016-08-08 | 2018-12-25 | Qualcomm Incorporated | Interposer device including at least one transistor and at least one through-substrate via |

| KR20180085219A (ko) * | 2017-01-18 | 2018-07-26 | 삼성전기주식회사 | 인덕터 및 그 제조 방법 |

| US10978240B2 (en) | 2017-05-01 | 2021-04-13 | Qualcomm Incorporated | Inductor with embraced corner capture pad |

| US20180323369A1 (en) | 2017-05-02 | 2018-11-08 | Micron Technology, Inc. | Inductors with through-substrate via cores |

| US10134671B1 (en) * | 2017-05-02 | 2018-11-20 | Micron Technology, Inc. | 3D interconnect multi-die inductors with through-substrate via cores |

| US10872843B2 (en) | 2017-05-02 | 2020-12-22 | Micron Technology, Inc. | Semiconductor devices with back-side coils for wireless signal and power coupling |

| US11817239B2 (en) | 2017-12-15 | 2023-11-14 | Qualcomm Incorporated | Embedded vertical inductor in laminate stacked substrates |

| KR102064044B1 (ko) * | 2017-12-26 | 2020-01-08 | 삼성전기주식회사 | 코일 부품 |

| US11011461B2 (en) * | 2018-02-12 | 2021-05-18 | Qualcomm Incorporated | Perpendicular inductors integrated in a substrate |

| CN108347229A (zh) * | 2018-03-19 | 2018-07-31 | 南京邮电大学 | 一种具有高性能电容、电感的ltcc正交型耦合器 |

| KR102163060B1 (ko) * | 2019-01-16 | 2020-10-08 | 삼성전기주식회사 | 인덕터 및 인덕터를 포함하는 저잡음 증폭기 |

| US11881449B2 (en) * | 2019-07-19 | 2024-01-23 | Texas Instruments Incorporated | High performance high voltage isolators |

| US11296022B2 (en) * | 2020-08-25 | 2022-04-05 | Qualcomm Incorporated | Package and substrate comprising interconnects with semi-circular planar shape and/or trapezoid planar shape |

| JP2022057272A (ja) * | 2020-09-30 | 2022-04-11 | オムロン株式会社 | 基板コイル及びトランス |

| JP2023013849A (ja) * | 2021-07-16 | 2023-01-26 | 株式会社村田製作所 | 送受信モジュール |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005191191A (ja) * | 2003-12-25 | 2005-07-14 | Tdk Corp | 積層型チップインダクタ |

| TWI296845B (en) * | 2006-05-17 | 2008-05-11 | Via Tech Inc | Multilayer winding inductor |

| JP2007317838A (ja) * | 2006-05-25 | 2007-12-06 | Sanyo Electric Co Ltd | 回路装置および表面実装コイル |

| US8093983B2 (en) * | 2006-08-28 | 2012-01-10 | Avago Technologies Ecbu Ip (Singapore) Pte. Ltd. | Narrowbody coil isolator |

| JP2008098552A (ja) * | 2006-10-16 | 2008-04-24 | Seiko Epson Corp | パターン形成方法 |

| US7750435B2 (en) | 2008-02-27 | 2010-07-06 | Broadcom Corporation | Inductively coupled integrated circuit and methods for use therewith |

| US20100019300A1 (en) | 2008-06-25 | 2010-01-28 | The Trustees Of Columbia University In The City Of New York | Multilayer integrated circuit having an inductor in stacked arrangement with a distributed capacitor |

| US7811919B2 (en) | 2008-06-26 | 2010-10-12 | International Business Machines Corporation | Methods of fabricating a BEOL wiring structure containing an on-chip inductor and an on-chip capacitor |

| US8079134B2 (en) | 2008-08-01 | 2011-12-20 | International Business Machines Corporation | Method of enhancing on-chip inductance structure utilizing silicon through via technology |

| US8855786B2 (en) | 2009-03-09 | 2014-10-07 | Nucurrent, Inc. | System and method for wireless power transfer in implantable medical devices |

| US8471358B2 (en) * | 2010-06-01 | 2013-06-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | 3D inductor and transformer |

| JP2012064683A (ja) * | 2010-09-15 | 2012-03-29 | Murata Mfg Co Ltd | 積層型コイル |

| US8809956B2 (en) * | 2011-10-13 | 2014-08-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Vertically oriented semiconductor device and shielding structure thereof |

| WO2013101131A1 (en) * | 2011-12-29 | 2013-07-04 | Intel Corporation | Integrated inductor for integrated circuit devices |

| US9009951B2 (en) * | 2012-04-24 | 2015-04-21 | Cyntec Co., Ltd. | Method of fabricating an electromagnetic component |

| CN103377795B (zh) | 2012-04-24 | 2016-01-27 | 乾坤科技股份有限公司 | 电磁器件及其制作方法 |

-

2013

- 2013-11-13 US US14/079,488 patent/US9806144B2/en active Active

-

2014

- 2014-11-06 JP JP2016529451A patent/JP6367939B2/ja not_active Expired - Fee Related

- 2014-11-06 CN CN201480061884.XA patent/CN105723477B/zh not_active Expired - Fee Related

- 2014-11-06 WO PCT/US2014/064299 patent/WO2015073295A1/en active Application Filing

- 2014-11-06 EP EP14802565.3A patent/EP3069356B1/en not_active Not-in-force

Also Published As

| Publication number | Publication date |

|---|---|

| EP3069356B1 (en) | 2019-10-30 |

| JP2016538721A (ja) | 2016-12-08 |

| WO2015073295A1 (en) | 2015-05-21 |

| CN105723477B (zh) | 2019-09-10 |

| US20150130021A1 (en) | 2015-05-14 |

| US9806144B2 (en) | 2017-10-31 |

| EP3069356A1 (en) | 2016-09-21 |

| CN105723477A (zh) | 2016-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6367939B2 (ja) | 基板内のソレノイドインダクタ | |

| US11862552B2 (en) | Methods of embedding magnetic structures in substrates | |

| JP5113025B2 (ja) | コイル構造体及びその製造方法 | |

| US20160055976A1 (en) | Package substrates including embedded capacitors | |

| JP2013251520A (ja) | 一体的ファラデーシールドを備えた多層電子構造体 | |

| JP6240342B2 (ja) | 表面相互配線と無電解フィルを含むキャビティとを備えるパッケージ基板 | |

| US9449762B2 (en) | Embedded package substrate capacitor with configurable/controllable equivalent series resistance | |

| JP6459107B2 (ja) | 多層電子支持構造体の製作方法 | |

| US9466578B2 (en) | Substrate comprising improved via pad placement in bump area | |

| US9807884B2 (en) | Substrate comprising embedded elongated capacitor | |

| TWI836197B (zh) | 建構螺線管電感器的方法及以其建構的螺線管電感器 | |

| JP4504774B2 (ja) | 配線基板の製造方法 | |

| JP2006013117A (ja) | インダクタ構造体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160516 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171020 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171222 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20171222 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20180111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180402 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180611 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180705 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6367939 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |