JP6249403B2 - 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 - Google Patents

光遅延線及び電子バッファ融合型光パケットバッファ制御装置 Download PDFInfo

- Publication number

- JP6249403B2 JP6249403B2 JP2014036222A JP2014036222A JP6249403B2 JP 6249403 B2 JP6249403 B2 JP 6249403B2 JP 2014036222 A JP2014036222 A JP 2014036222A JP 2014036222 A JP2014036222 A JP 2014036222A JP 6249403 B2 JP6249403 B2 JP 6249403B2

- Authority

- JP

- Japan

- Prior art keywords

- buffer

- optical

- electronic

- packet

- delay line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000872 buffer Substances 0.000 title claims description 300

- 230000003287 optical effect Effects 0.000 title claims description 184

- 230000004927 fusion Effects 0.000 title claims description 33

- 230000015654 memory Effects 0.000 claims description 49

- 238000006243 chemical reaction Methods 0.000 claims description 31

- 238000010586 diagram Methods 0.000 description 20

- 238000011156 evaluation Methods 0.000 description 9

- 238000012546 transfer Methods 0.000 description 8

- 238000004891 communication Methods 0.000 description 7

- 238000004088 simulation Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 6

- 238000000034 method Methods 0.000 description 6

- 230000007704 transition Effects 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000006872 improvement Effects 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000006855 networking Effects 0.000 description 2

- 239000013307 optical fiber Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0005—Switch and router aspects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0003—Details

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L47/00—Traffic control in data switching networks

- H04L47/10—Flow control; Congestion control

- H04L47/11—Identifying congestion

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9005—Buffering arrangements using dynamic buffer space allocation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0062—Network aspects

- H04Q11/0066—Provisions for optical burst or packet networks

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L43/00—Arrangements for monitoring or testing data switching networks

- H04L43/16—Threshold monitoring

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0005—Switch and router aspects

- H04Q2011/0007—Construction

- H04Q2011/0011—Construction using wavelength conversion

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0005—Switch and router aspects

- H04Q2011/0007—Construction

- H04Q2011/002—Construction using optical delay lines or optical buffers or optical recirculation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0005—Switch and router aspects

- H04Q2011/0037—Operation

- H04Q2011/0039—Electrical control

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0005—Switch and router aspects

- H04Q2011/0037—Operation

- H04Q2011/0041—Optical control

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/0001—Selecting arrangements for multiplex systems using optical switching

- H04Q11/0062—Network aspects

- H04Q2011/0073—Provisions for forwarding or routing, e.g. lookup tables

Description

バッファ制御部23は,遅延線の利用状況に関する情報を得て,光バッファの起動や停止,及び光バッファに含まれるメモリの状態(利用状態(アクティブ状態),利用準備状態(ホット状態)及び停止状態(コールド状態)を制御してもよい。この場合,バッファ制御部23は,あらかじめ所定の閾値を記憶しておき,遅延線の利用状態に関する情報を受け取って,所定の閾値と比較し,その上で電子バッファに対して各種の制御信号を出力すればよい。

1.光遅延線バッファ

1.1.光統合ネットワークでのパケット通信

下記文献に開示されている光パケット・光パス統合ネットワークノードを例に光遅延線バッファを用いた光パケットスイッチ機能を説明する。

(文献:H. Furukawa, T. Miyazawa, N. Wada, and H. Harai, "Moving the

Boundary between Wavelength Resources in Optical Packet and Circuit Integrated

Ring Network," Optics Express, vol. 22, no. 1, pp. 47-54, Jan. 2014.)

エッジノードにおいて外部ネットワークから受信したイーサネット(登録商標)フレームを10分割し,それぞれを光パケットにカプセル化して転送する。図3は,イーサネット(登録商標)フレームと光パケット変換を示す概念図である。この例のイーサネット(登録商標)フレームは,MACヘッダ,IPヘッダ,ペイロード及びFCS(フレームチェックシークエンス)を含む。この例は,1波長あたり10Gbpsの通信を行い,10波長の多重転送により100Gbpsの通信を実現する。この例では,一つの波長のパケット先頭に送受信ノードの情報などが記載された8バイトのルートヘッダを付加する。統合ネットワーク内のノードはルートヘッダに記載された情報を読み取り,次にパケットを渡す隣接ノードを選択する。

N×N光パケットスイッチは,N個の1×Nスイッチと,N入力1出力・遅延線数B本の光遅延線バッファが,フルメッシュに接続され構成される。

(文献:H. Harai and M. Murata, "High-Speed Buffer Management for 40

Gb/s-Based Photonic Packet Switches," IEEE/ACM Transactions on Networking, vol. 14, pp. 191-204, Feb. 2006.)

それらの結果を用いて,パケットをどのポートに出力し,どの遅延線を経由させるかを決定した。B本の遅延線は,長さD[ns]を単位長として,0, D, 2D, …, (B-1)D の離散的な遅延を与える。ある出力ポートに到着した複数のパケットが遅延線バッファを経由して衝突を回避するときの動作例を図5に示す。図5は,光遅延線バッファの振る舞いを示す概念図である。図5(a)は,パケット到着時の様子を示す図である。図5(b)は,パケットの相対位置を示す図である。図5(c)は,光遅延バッファからの出力の論理的な位置関係の例を示す図である。4入力4遅延線バッファ (N = 4, B = 4) において,ある時刻に図5(a) のように4つのパケットが到着したとする。ここで時間Tは,コントローラがパケットの到着状況を観測する周期を表し(内部クロック周波数は1/T),T は最小パケット長より短い。コントローラはパケット到着時刻とパケット長を取得し,ポート1, 2, …, N の順に到着パケットが通過する遅延線を決め,光パケットの出力先を切り替える。図5(a) のように到着したパケットのそれぞれに遅延を与えた結果,パケットAが遅延線d0 に到着した直後のパケットの相対位置は図5(b) のようになり,AからCの3 パケットが衝突なく出力され,パケットD は棄却される。図5(c) はこのときの光遅延線バッファからの出力の論理的な位置を示しており,図のように光遅延線バッファの離散特性上,出力には空き(Void)が発生する。

光遅延線バッファにおける遅延線数Bがネットワークの性能に与える影響を評価するため,ネットワークシミュレータns−3に光遅延線バッファ等の光パケットスイッチの機能を実装し,シミュレーション評価を行った。

まずシミュレーションで用いたトポロジと各パラメータの設定,およびトラヒックモデルについて述べる。ネットワークトポロジは,図6に示すダンベル型トポロジを用いた。図6は,ダンベル型トポロジの構成概念を示すブロック図である。100Gbpsの光パケット回線で接続されたスイッチの両端にそれぞれ10のイーサネット(登録商標)スイッチが接続する。各イーサネット(登録商標)スイッチには10の端末が接続する。トポロジの両端にそれぞれ100の端末が接続する。端末とイーサネット(登録商標)スイッチの間は伝播遅延1ms,回線速度10Gbps,イーサネット(登録商標)スイッチと光パケットスイッチの間は伝播遅延0.5ms,回線速度40Gbpsの回線で接続され,いずれもMTUは1500Byteである。最小パケット長は64Byteであり,光パケットに変換すると19.2nsとなるので,光パケットスイッチの観測周期Tは19nsとしている。遅延線の単位長Dは100nsとする。なおトラヒック発生モデルはUDPおよびTCPを用いて評価した。

時刻[0,0.5]の間に1Gbpsのフローを到着率λ(フロー/秒)のポアソン過程に従い発生させる。送受信端末の組み合わせは端末の中からランダムに選び,図左端の端末から右端の端末へトラヒックが流れる。

フロー制御プロトコルとしてTCP NewRenoを使用した。到着率λのポアソン過程に従いフローを発生させる点はUDPの場合と同様である。ただし左端から右端,もしくは右端から左端の端末へ向かいトラヒックを流すフローを同時に発生させ,様々な大きさのパケットがボトルネックを行き交う状況を与える。また,ファイル転送を想定し個々のフローに転送量の上限を定義する。フロー発生時の平均が780KByte前後となるようにα=0.5,Xm=90としたパレート分布を用いた。シミュレーション時間は5秒間とした。また,時刻[0,0.01]に発生したフローの転送量を無制限とし,それらのフローは終始バックグラウンドトラヒックを流し続けた。

上記のシミュレーション環境において,遅延線数Bを4,8,16,32,64とし性能評価を行った。また,比較のためにダンベル型トポロジのOPS部分を100Gbpsのイーサネット(登録商標)スイッチに置換した場合の性能評価(Ether)も同時に行った。ここで100Gbpsスイッチのバッファ容量は長さ63Dの遅延線と同等の20.48KByteとし,FIFO,DropTail方式でパケットを格納した。また,光遅延線バッファと同程度の高速処理ができると仮定し,パケット処理遅延は2T=38nsとした。総受信バイト数(UDP)トラヒック下でのフロー到着率λと端末が受信したデータ量の関係を図7に示す。図7は,端末の総受信バイト数(UDP)を示すグラフである。図7において,X軸はフロー到着率を表し,Y軸は右端端末が受信したパケットの総バイト数を表す。時刻[0,0.5]でフローを発生させることで,λ/2×1Gbpsのフローがボトルネックリンクに流入する。λ=200の時点で流入フローが100Gbpsになる。一方,λ=150を超えた段階で,多量のパケットが棄却されるようになり光パケットスイッチの転送量は上がらない。遅延線数を4本から8本に増やすことで転送量は約10%向上するものの,16本以上に増やしても転送量はほとんど増えず,イーサネット(登録商標)スイッチの転送量とは大きな差が開いている。

1.光・電子融合型バッファ

参考例1にて,光遅延線バッファの遅延線数Bを増やすことで光パケットスイッチの通信性能が向上することが示された。一方,数十本程度の遅延線数で高速なイーサネット(登録商標)スイッチと同等の性能を得ることは難しいことも示された。先述の通り,光遅延線バッファの拡張は経済的・技術的観点から難しいと考えられるため,光遅延線バッファと安価な電子バッファを組み合わせることで光パケットバッファの性能向上を目指す。

(文献:H. Uzawa, K. Terada, N. Ikeda, A. Miyazaki, M. Urano, and T. Shibata,

"Energy-efficient Frame-buffer Architecture and It’s Control Schemes for

ONU Power Reduction," in Proceedings of IEEE GLOBECOM, Dec. 2011.)

二種のバッファを組み合わせ,各々を適切に用いることで,光遅延線バッファの低遅延・低消費電力という特色を活かしつつ,電子バッファによりパケット収容能力を拡張することが可能となる。

電子メモリの稼働領域を必要に応じて増減させることが,電子バッファの低消費電力化に繋がる。融合型バッファの低消費電力化には電子バッファの非稼働時の待機電力を最小限に抑えることが求められる。

そのためには,電子メモリの稼働領域を制御でき,かつ,稼働・停止の遷移時間が短いことが望ましい。以下の文献で提案されているスライス化メモリは,メモリを複数のスライスに分割し,スライス毎に個別に電源を制御することで,メモリの効率的な運用を実現する。スライス化メモリにおいて,各スライスは以下の3状態に遷移する。

(文献:K. Okuda, S. Ata, Y. Kuroda, Y. Yano, I. Iwamoto, K. Inoue, and I.

Oka, "2D Sliced Packet Buffer with Traffic Volume and Buffer Occupancy

Adaptation for Power Saving," in Proceedings of Consumer Communications

and Networking Conference, pp. 97-105, Jan. 2013.)

ホット(ホットスタンバイ)(Hot)状態…CLK入力を遮断し待機電力はAct.状態の43%に抑える。Act.状態へ1μsで遷移可能な状態。

コールド(コールドスタンバイ)(Cold)状態…電力供給を遮断した状態で消費電力を0にできるがHot状態への遷移に100μsを要する状態。

Act.およびHot状態のいずれからも即時にCold状態に遷移可能。

例えばAct.状態の領域が不足するとHot状態の領域をAct.に切り替え,メモリの占有率が下がるとAct.の領域の一部をHotに切り替えるなど,スライス単位で状態を制御することで,メモリの容量制御が可能となる。スライス化メモリの柔軟かつ高速な電源制御機能に着目し,光・電子融合型バッファの電子メモリへ組み込む。

光・電子融合型バッファを,図4の光遅延線バッファへ新たに電子バッファを併設した形で構成した(図10)。図10は,融合型バッファの構成例を示すブロック図である。融合型バッファでは,光遅延線バッファからの出力と電子バッファからの出力を光カプラで束ね隣接ノードに伝送する。カプラは束ねられる入力信号の数に限りがある。このため,電子バッファ起動時には遅延線のうちの1本,今回は最大長の遅延線は利用しないように制御することが好ましい。このようにすることで,比較的安価なカプラを用いても効果的にバッファ機能を達成できる。カプラの性能が非常に高い場合は,電子バッファを起動した場合でも,全ての遅延線を利用し続けてもよい。

前節で述べた融合型バッファが全てのパケットを電子バッファに格納する場合と比較してどの程度省電力化が見込めるかについて試算する。

2.1.融合型バッファの動作モデル

前述の光遅延線と電子メモリを組み合わせた融合型バッファの性能を示すため,シミュレーションによる評価を行う。融合型バッファの大まかな性能特性を示すため,融合型バッファにおける電子バッファ部の電源制御やスライス化メモリ内部のAct.状態やHot状態の切り替え制御に関しては,非常に単純な動作モデルを定義し評価する。融合型バッファにおける電子バッファ部の電源制御モデルについては以下の通りである。

利用された遅延線の数が遅延線総数の50%を超えると電子バッファ部を起動する。なお,利用された遅延線の数が,遅延線総数の30%以上80%以下のある値を越えた場合に,電子バッファを起動するようにしてもよく,40%以上60%以下のある値でもよい。このように利用された遅延線の数に応じて,電子バッファ部を起動するか又は起動しないかを制御してもよい。

Act.領域の利用率が75%を超えた際に,Hot領域(Hot状態にある領域)をAct.領域に遷移させ,拡張後のAct.領域と同じ大きさのCold領域をHot状態に遷移させる。また,Act.領域の利用率が25%を下回ると,Hot領域をColdの状態に,Act.領域の半分をHotに遷移させる。すなわち,スライス数の上限に達するまでは,利用率75%を超える度にAct.領域を2倍に拡張し,利用率25%を下回る度にAct.領域を半分に縮小するように振る舞う。本発明は,上記の具体的な数値を特定の値又は特定の範囲と読み替えた制御を行うことができる。

ネットワークトポロジは先の参考例1と同じダンベル型トポロジを用いた。トラヒックモデルとしてTCPモデルを用いた評価,および融合型バッファの電源制御がトラヒック需要の変動に十分に対応可能であるかを確認するため,フロー到着率が2秒ごとに増減する場合の評価を行った。電子メモリは1ポート当たり約1MByte,16スライスに分割し1スライスあたりの容量は約64Kbyteであった。また,メモリの読み書きには10.66GByte/sの遅延がかかる。REDのパラメータは,maxp=20%,minth=12.5%,maxth=80%, wq=0.002としている。

図11は,TCPモデルを用いたときの,融合型バッファの平均グッドプットを示す。図11は,時刻[3,4]に発生したフローの平均グッドプットを計測した図である。図11において,X軸・Y軸は図9と同様である。図より8本の遅延線からなる光遅延線バッファに電子バッファを組み合わせた融合型バッファの平均グッドプットは,混雑時(λ=8×104程度)では光遅延線バッファのみの場合に比べて20%近くグッドプットが向上している。更にこのとき,融合型バッファの平均グッドプットは,遅延線数64本の光遅延線バッファのグッドプットを上回る。このことから融合型バッファは遅延線数の拡張によらない収容能力の向上を達成していると言える。また,λ=105のときの出力回線スループットは約75Gbps程度に向上しており(図8),これはB=8の光遅延線バッファのみの場合と比べて約70%の性能向上である。一方,融合型バッファは,特に混雑時において,イーサネット(登録商標)スイッチに比べると性能が劣る。しかしこの点は電子バッファに収容するパケットの割合を上げることで解決できると考えられる。メモリ読み書きの頻度が上がると電子部品の消費電力が増すため,電子バッファの使用は極力抑えることが望ましい。光遅延線バッファと電子バッファの利用比は混雑状況に応じた調整が好ましい。図12は,2秒おきにフロー到着率,すなわちトラヒック需要が変動する状況下での光遅延線バッファと融合型バッファの出力回線スループットを比較したグラフである。X軸は時刻を表し,左のY軸は出力回線のスループットを,右のY軸はフロー到着率λを表す。時刻[2,4],および[6,8]でフロー到着率が上昇し,トラヒック負荷が高まっているが,融合型バッファは光遅延線バッファを上回るスループットを得られる。二種のバッファを組み合わせることで,棄却率の軽減と回線利用効率の向上が実現できる。

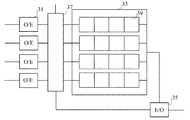

17・・遅延線 19・・電子バッファ 21・・出力端

23・・バッファ制御部 31・・O/E変換レシーバ

33・・メモリ 35・・E/O変換トランスミッタ

Claims (4)

- 光パケットを入力するN個(Nは2以上の整数)の入力端(11)と,

前記N個の入力端(11)と接続され,前記光パケットに関するパケット情報を得る光パケット情報取得部(13)と,

前記N個の入力端(11)と接続された,複数のスイッチ(15)と,

前記複数のスイッチ(15)のそれぞれと接続された複数の遅延線(17)と,

前記N個の入力端(11)と接続された,電子バッファ(19)と,

前記複数の遅延線(17)及び前記電子バッファ(19)と接続された出力端(21)と,

前記光パケット情報取得部(13)と接続され,前記N個の入力端(11)と前記複数のスイッチ(15)との接続関係,前記N個の入力端(11)と前記電子バッファ(19)との接続関係,及び,前記複数のスイッチ(15)と前記複数の遅延線(17)との接続関係を制御する光バッファ制御部(23)と,

を有し,

前記複数の遅延線(17)は,それぞれ遅延量が異なり,

前記バッファ制御部(23)は,前記パケット情報を受け取ってパケットのトラヒックを解析し,パケットのトラヒックがトラヒックに関する第1の閾値以下の場合であるか,又は前記遅延線の利用率が利用率に関する第1の閾値以下の場合は,前記電子バッファ(19)を利用しないように制御する,

光遅延線及び電子バッファ融合型光パケットバッファ制御装置。 - 請求項1に記載の装置であって,

前記電子バッファ(19)は,

前記N個の入力端(11)のそれぞれと対応したN個のO/E変換レシーバ(31)と,

前記N個のO/E変換レシーバ(31)のそれぞれと接続されたメモリ(33)と,

前記メモリ(33)から読み出された電気信号を光信号に変換する1個又は複数個のE/O変換トランスミッタ(35)とを有し,

前記バッファ制御部(23)は,

前記N個の入力端(11)のそれぞれにおけるパケット情報又は前記遅延線の利用率に基づいて,それぞれの入力端(11)の混雑状況を把握し,把握した混雑状況に基づいて,それぞれの入力端(11)と接続された電子バッファ(19)に含まれる記憶領域の状態を制御する,

装置。 - 請求項1に記載の装置であって,

前記バッファ制御部(23)は,

前記パケットのトラヒックが,トラヒックに関する第1の閾値以上トラヒックに関する第2の閾値以下の場合であるか,又は

前記遅延線の利用率が利用率に関する第1の閾値以上利用率に関する第2の閾値以下の場合は,前記電子バッファ(19)が動作準備状態となるように制御する,

装置。 - 請求項1に記載の装置であって,

前記バッファ制御部(23)は,前記N個の入力端(11)のうちいずれかから入力される光パケットを前記電子バッファ(19)へと入力する場合,前記複数の遅延線(17)のうち少なくとも1つを利用しないように制御する,

装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014036222A JP6249403B2 (ja) | 2014-02-27 | 2014-02-27 | 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 |

| US15/121,772 US9961420B2 (en) | 2014-02-27 | 2015-01-19 | Optical delay line and electronic buffer merged-type optical packet buffer control device |

| PCT/JP2015/051238 WO2015129330A1 (ja) | 2014-02-27 | 2015-01-19 | 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014036222A JP6249403B2 (ja) | 2014-02-27 | 2014-02-27 | 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015162772A JP2015162772A (ja) | 2015-09-07 |

| JP2015162772A5 JP2015162772A5 (ja) | 2017-11-16 |

| JP6249403B2 true JP6249403B2 (ja) | 2017-12-20 |

Family

ID=54008659

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014036222A Active JP6249403B2 (ja) | 2014-02-27 | 2014-02-27 | 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9961420B2 (ja) |

| JP (1) | JP6249403B2 (ja) |

| WO (1) | WO2015129330A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7030518B2 (ja) | 2015-08-25 | 2022-03-07 | 川崎重工業株式会社 | 産業用遠隔操作ロボットシステム |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9696920B2 (en) * | 2014-06-02 | 2017-07-04 | Micron Technology, Inc. | Systems and methods for improving efficiencies of a memory system |

| JP7044545B2 (ja) * | 2017-01-13 | 2022-03-30 | 住友化学株式会社 | 化合物、樹脂、レジスト組成物及びレジストパターンの製造方法 |

| CN108471399B (zh) * | 2018-02-07 | 2020-06-26 | 平安科技(深圳)有限公司 | 一种反洗钱作业中数据包的生成方法、存储介质和服务器 |

| KR102644304B1 (ko) * | 2021-11-23 | 2024-03-07 | 한국전자통신연구원 | 슬라이싱 기능을 지원하는 onu의 전원 관리 방법 및 장치 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020054732A1 (en) * | 1999-11-02 | 2002-05-09 | Zheng Si Q. | Optical burst scheduling using partitioned channel groups |

| CN1332546A (zh) * | 2000-06-08 | 2002-01-23 | 阿尔卡塔尔公司 | 光ip交换路由器结构 |

| US20020076142A1 (en) * | 2000-08-21 | 2002-06-20 | Song Qi Wang | Optical switch and switching network |

| FR2814305B1 (fr) * | 2000-09-18 | 2002-12-06 | Cit Alcatel | Dispositif de selection et de conversion de longueur d'onde, et matrice de commutation photonique l'incorporant |

| US8073327B2 (en) * | 2000-11-08 | 2011-12-06 | Yaron Mayer | System and method for improving the efficiency of routers on the internet and/or cellular networks and/or other networks and alleviating bottlenecks and overloads on the network |

| US7145704B1 (en) * | 2003-11-25 | 2006-12-05 | Cheetah Omni, Llc | Optical logic gate based optical router |

| US6731832B2 (en) * | 2001-02-28 | 2004-05-04 | Lambda Opticalsystems Corporation | Detection of module insertion/removal in a modular optical network, and methods and apparatus therefor |

| FR2834402B1 (fr) * | 2002-01-03 | 2005-03-11 | Cit Alcatel | Dispositif de commutation optique et procede de commande de ce dispositif |

| US6768827B2 (en) * | 2002-01-16 | 2004-07-27 | The Regents Of The University Of California | Integrated optical router |

| US7830442B2 (en) * | 2002-04-30 | 2010-11-09 | ARETé ASSOCIATES | Compact economical lidar system |

| GB0226249D0 (en) * | 2002-11-11 | 2002-12-18 | Clearspeed Technology Ltd | Traffic handling system |

| US7764882B2 (en) * | 2002-11-29 | 2010-07-27 | Alcatel-Lucent Usa Inc. | Optical packet tray router |

| US6940863B2 (en) * | 2003-01-13 | 2005-09-06 | The Regents Of The University Of California | Edge router for optical label switched network |

| US7272310B2 (en) * | 2003-06-24 | 2007-09-18 | Intel Corporation | Generic multi-protocol label switching (GMPLS)-based label space architecture for optical switched networks |

| JP3757286B2 (ja) * | 2003-07-09 | 2006-03-22 | 独立行政法人情報通信研究機構 | 光パケットのバッファリング装置とそのバッファリング方法 |

| US20050030951A1 (en) * | 2003-08-06 | 2005-02-10 | Christian Maciocco | Reservation protocol signaling extensions for optical switched networks |

| WO2005025112A2 (en) * | 2003-09-04 | 2005-03-17 | The Regents Of The University Of California | All optical variable buffer queue useful in optical packet networks |

| US20050063701A1 (en) * | 2003-09-23 | 2005-03-24 | Shlomo Ovadia | Method and system to recover resources in the event of data burst loss within WDM-based optical-switched networks |

| US7315693B2 (en) * | 2003-10-22 | 2008-01-01 | Intel Corporation | Dynamic route discovery for optical switched networks |

| JP4849627B2 (ja) | 2007-02-26 | 2012-01-11 | 独立行政法人情報通信研究機構 | 光パケットバッファ制御装置とその制御方法 |

| US8150264B2 (en) * | 2007-11-09 | 2012-04-03 | University Of Houston | Methods for non-wavelength-converting multi-lane optical switching |

| JP5507412B2 (ja) * | 2010-10-22 | 2014-05-28 | 日本電信電話株式会社 | 光伝送装置 |

| JP6357733B2 (ja) * | 2013-06-04 | 2018-07-18 | 富士通株式会社 | 光伝送装置、光伝送システム、及び光伝送方法 |

-

2014

- 2014-02-27 JP JP2014036222A patent/JP6249403B2/ja active Active

-

2015

- 2015-01-19 WO PCT/JP2015/051238 patent/WO2015129330A1/ja active Application Filing

- 2015-01-19 US US15/121,772 patent/US9961420B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7030518B2 (ja) | 2015-08-25 | 2022-03-07 | 川崎重工業株式会社 | 産業用遠隔操作ロボットシステム |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015162772A (ja) | 2015-09-07 |

| US20170013332A1 (en) | 2017-01-12 |

| US9961420B2 (en) | 2018-05-01 |

| WO2015129330A1 (ja) | 2015-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7180862B2 (en) | Apparatus and method for virtual output queue feedback | |

| JP6249403B2 (ja) | 光遅延線及び電子バッファ融合型光パケットバッファ制御装置 | |

| EP1565828B1 (en) | Apparatus and method for distributing buffer status information in a switching fabric | |

| US7573821B2 (en) | Data packet rate control | |

| US20040223452A1 (en) | Process for detecting network congestion | |

| US8576850B2 (en) | Band control apparatus, band control method, and storage medium | |

| US9614777B2 (en) | Flow control in a network | |

| JP6236945B2 (ja) | 伝送装置、伝送システム、及び伝送方法 | |

| US10461873B1 (en) | Disaggregated hybrid optical transport network, internet protocol, and Ethernet switching system | |

| JP4652314B2 (ja) | イーサoamスイッチ装置 | |

| US11271868B2 (en) | Programmatically configured switches and distributed buffering across fabric interconnect | |

| Fumagalli et al. | A low-latency and bandwidth-efficient distributed optical burst switching architecture for metro ring | |

| KR20170015000A (ko) | 온칩 네트워크 및 이의 통신방법 | |

| US8131854B2 (en) | Interfacing with streams of differing speeds | |

| US11563687B2 (en) | Controlling distributed buffers in a network to manage data packets | |

| CN111434079A (zh) | 一种数据通信方法及装置 | |

| EP1511231A1 (en) | A method for transmission of data packets through a network | |

| Molina et al. | Managing path diversity in layer 2 critical networks by using OpenFlow | |

| Hirayama et al. | Design of optical and electronic combined buffer architecture for optical packet switches | |

| US8780736B2 (en) | Communication apparatus and heat generation suppressing method | |

| JP4500589B2 (ja) | ネットワーク装置 | |

| Alparslan et al. | Rate-based pacing for small buffered optical packet-switched networks | |

| JP5417971B2 (ja) | ネットワークシステム、ネットワークシステムの通信方法、及びネットワークシステムのノード装置 | |

| Bianco et al. | A distributed scheduling algorithm for an optical switching fabric | |

| CN116055407A (zh) | 一种报文调度的方法及装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171002 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20171024 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171114 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6249403 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |