以下に、本願の開示する情報処理装置、情報処理装置の制御方法及び情報処理装置の制御プログラムの実施例を図面に基づいて詳細に説明する。なお、以下の実施例により本願の開示する情報処理装置、情報処理装置の制御方法及び情報処理装置の制御プログラムが限定されるものではない。

図1は、実施例1に係る情報処理システムの構成を示す構成図である。図1に示すように、本実施例に係る情報処理システムは情報処理装置であるサーバ1及びサーバ2を有している。

サーバ1は、CPUコア10及び11、メモリ12、I/O(Input/Output)13、I/O14、メモリコントローラ15、並びにI/Oブリッジ16を有している。そして、CPUコア10及び11とメモリコントローラ15とはバスで接続されており、メモリコントローラ15とメモリ12とはバスで接続されている。また、メモリコントローラ15とI/Oブリッジ16とはバスで接続されており、I/Oブリッジ16とI/O13及びI/O14とはバスで接続されている。ここで、I/O13は、ディスクなどである。

I/O14は、ホスト チャネル アダプタ(Host Channel Adapter:HCA)などのインフィニバンド用の通信路である。

サーバ2も同様に、CPUコア20及び21、メモリ22、I/O23、I/O24、メモリコントローラ25、並びにI/Oブリッジ26を有している。また、サーバ2における各部の接続もサーバ1と同様である。

サーバ1とサーバ2とは、例えば、インフィニバンド用のバス3で接続されている。ここで、説明の便宜上、図1ではサーバ1及びサーバ2はバス3により互いに接続されているが、実際には、サーバ1とサーバ2とはスイッチを経由して接続されている。また、本実施例では、説明の便宜上、サーバ1及びサーバ2という2台のサーバのみを記載しているが、複数であればサーバの台数に特に制限はなく、それぞれがインフィニバンド用のケーブルを用いたバス3で接続されていればよい。

そして、バス3には、ネットワークスイッチ4が接続されている。ネットワークスイッチ4は、バス3を介して送受信されるデータの伝送経路を制御する。

次に、サーバ1及びサーバ2の各部について詳細に説明する。サーバ1及びサーバ2は、同様の構成を有するため、ここでは、サーバ1を例に説明する。

CPUコア10及びCPUコア11は、上述したようにメモリコントローラ15に接続される演算処理部である。ここで、本実施例では、サーバ1は、CPUコア10及びCPUコア11という2つのCPUコアを有するように説明しているが、CPUコアの数には特に制限は無い。また、CPUコア10及び11は、内部に論理的なハードウェアの単位としてのスレッドを有している。本実施例では、CPUコア10及び11は、後述するように、2つのスレッドを有している。スレッドについては後で詳細に説明する。

メモリ12は、後述するCPUコア10の各スレッドに割り当てられたメモリ領域を有している。例えば、CPUコア10の2つのスレッドに、メモリ領域121及び領域122がそれぞれ割り当てられている。

メモリコントローラ15は、CPUコア10及び11からの指示を受けて、メモリ12に対するデータの書き込み及びメモリ12からのデータの読み出しを行う。

I/O13は、例えばハードディスクや入出力装置などを有している。入出力装置としては、例えば、キーボードやモニタなどがある。I/O13のキーボード及びモニタなどをユーザインタフェースとして、操作者は、データの入力などを行う。また、CPUコア10及び11は、メモリコントローラ15及びI/Oブリッジ16を介してI/O13のハードディスク等にデータを格納する。

また、CPUコア10及び11は、メモリコントローラ15、I/Oブリッジ16、I/O13及びバス3を介して、サーバ2のCPUコア20及び21などと通信を行い、データの送受信を行う。このように、CPU10及び11は、メモリコントローラ15やI/Oブリッジ16を経由してCPU20及び21とデータの送受信を行うが、以下では説明の都合上、メモリコントローラ15やI/Oブリッジ16を省いてデータの送受信を説明する場合がある。

図2は、スレッドを説明するための図である。本実施例では、CPUコア10は、アプリスレッド200及び通信制御スレッド201という2つのスレッドを有する。また、CPUコア20は、アプリスレッド202及び通信制御スレッド203という2つのスレッドを有する。スレッドとは、単一のCPUコアにおいて別個に処理を行う論理的な単位である。そして、CPU10及びCPU20は、自己が有する各スレッドのそれぞれに処理を同時に実行させる機能、すなわちSMTの機能を有している。CPUコア10及び11は、同様の構成を有し同様の機能を有するため、ここでは、CPUコア10を例に説明する。また、以下の説明では、説明の便宜上、各スレッドが処理を実行しているように説明する場合があるが、実際には各スレッドを実行する演算処理部がそれらの処理を実行している。この演算処理部とは、例えば、各スレッドを実行するCPUコア又はCPUコアの中の実行部がその一例にあたる。

アプリスレッド200は、アプリケーションにおける通信制御処理以外の処理を行うスレッドである。例えば、サーバ1で実行されるアプリケーションが証券取引のアプリケーションであれば、アプリスレッド200を実行するCPUコア10又は実行部は、証券の売買を成立させるための処理などを実施する。アプリスレッド200が実施する処理を、以下では「アプリケーション処理」と言う場合がある。図2におけるアプリケーション210が、アプリスレッド200を実行するCPUコア10又は実行部が実施しているアプリケーション処理を表している。また、アプリケーション214が、アプリスレッド202を実行するCPUコア10又は実行部が実施しているアプリケーション処理を表している。

アプリスレッド200を実行するCPUコア10又は実行部は、アプリケーション処理を実行しているモードと、アプリケーション処理を実行していないモードという2つの動作モードを有している。以下では、アプリケーション処理を実行していないモードを「Idle」という。以下では、アプリスレッド200を実行するCPUコア10又は実行部における動作モードを、単にアプリスレッド200の動作モードと言う場合がある。

また、アプリスレッド200は、メモリの中の領域が割り当てられている。本実施例では、アプリスレッド200は、例えば、図1に示すメモリ12のメモリ領域121が割り当てられている。そして、アプリスレッド200を実行するCPUコア10又は実行部は、メモリ領域121が更新されたか否かを監視している。

通信制御スレッド201を実行するCPUコア10又は実行部は、サーバ2のCPU20などからデータの受信処理などを行うスレッドである。例えば、通信制御スレッド201を実行するCPUコア10又は実行部は、通信制御スレッド203が送信したデータを受信する。通信制御スレッド201が実施するデータの受信処理などを含む処理を、以下では「通信制御処理」という場合がある。図2における通信制御211が、通信制御スレッド201が実施している通信制御処理を表している。また、通信制御213が、通信制御スレッド201が実施している通信制御処理を表している。さらに、通信制御処理の中の受信処理には、データが送信されてきたか否かを判定するポーリングの処理が含まれている。ポーリングを実行している状態では、通信制御スレッド201は、単にメモリ領域が更新されたか否かを判定するだけなので、他の通信制御処理とは異なりCPUコア10の資源の使用を制限することができる。

通信制御スレッド201を実行するCPUコア10又は実行部は、受信処理などのポーリング以外の通信制御処理を実行しているモードと、ポーリングを実行しており受信待ちのモードと、通信制御処理を実行していないモードという3つの動作モードを有している。以下では、ポーリングを実行しており受信待ちの動作モードを、「mpoll」と言い、通信制御処理を実行していないモードを、「Idle」という。以下では、通信制御スレッド201を実行するCPUコア10又は実行部における動作モードを、単に通信制御スレッド201の動作モードと言う場合がある。

また、通信制御スレッド201は、メモリの中の領域が割り当てられている。本実施例では、通信制御スレッド201は、例えば、図1に示すメモリ12のメモリ領域122が割り当てられている。そして、通信制御スレッド201を実行するCPUコア10又は実行部は、メモリ領域122が更新されたか否かを監視している。

例えば、インテル(登録商標)製のCPUの場合であれば、通信制御スレッド201は、mpollの状態では、mwait命令によるポーリング処理を行う。mwait命令は、指定したアドレスのメモリ領域が更新されるまでスレッドの動作を停止する命令である。指定したアドレスのメモリ領域とは、例えば、図1における通信制御スレッド201に割り当てられたメモリ領域122である。すなわち、通信制御スレッド201は、mpollの場合、メモリコントローラ15によりメモリ領域122が更新されると動作の停止を解除し通信制御処理を実行するモードに復帰する。また、メモリ領域122の更新の他、割り込み発生時にも、通信制御スレッド201は、通信制御処理を実行するモードに復帰する。

ここで、本実施例では、説明の都合上、CPU10及び20がそれぞれ2つのスレッドを有しているとして説明したが、複数であればスレッドの数に特に制限は無い。

図3は、スレッドが使用するCPUコアの資源を説明するための図である。図3に示すように、アプリスレッド200及び通信制御スレッド201のそれぞれが処理を行う場合に使用する資源である共通資源320が存在する。共通資源320には、演算器322を含む命令パイプライン321及びキャッシュ323などが含まれる。

アプリスレッド200は、CPUコア10の資源として、例えば、プログラムカウンタ301、命令フェッチ302、レジスタセット303、命令パイプライン321及びキャッシュ323を使用する。また、通信制御スレッド201は、CPUコア10の資源として、例えば、プログラムカウンタ311、命令フェッチ312、レジスタセット313、命令パイプライン321及びキャッシュ323を使用する。

共通資源320は、アプリスレッド200及び通信制御スレッド201のいずれのスレッドでも用いられ、一方のスレッドが使用している共通資源320は、他方のスレッドは使用できない。例えば、アプリスレッド200が演算器322を使用している場合には、通信制御スレッド201は演算器322を使用することはできない。

そして、アプリスレッド200及び通信制御スレッド201を実行するCPUコア10又は実行部は、CPUコア10の資源の使用状態を決定する消費資源モードとして、通常モードと省消費資源モードという2つの消費資源モードを有している。省消費資源モードとは、CPUコア10の資源の使用を抑制するモードである。通常モードは、CPUコア10の資源の使用を抑制しないモードである。特に、省消費資源モードの場合、アプリスレッド200及び通信制御スレッド201による共通資源320の使用も軽減される。そのため、一方のスレッドが省消費資源モードで動作している場合、その一方のスレッドによる共通資源320の利用が減るため、他方のスレッドは共通資源320をほぼいつでも利用可能であり、処理を迅速に行うことができる。以下では、アプリスレッド200及び通信制御スレッド201を実行するCPUコア10又は実行部における消費資源モードを、単に各スレッドの消費資源モードと言う場合がある。

消費資源モードは、例えば、インテル(登録商標)製のCPUの場合であれば、省電力モードを用いることで実現できる。具体的には、インテル製のCPUには、C0〜C6という消費電力に関するモードが設けられている。C0は、処理を実行しているときのモードである。C1〜C6は、消費電力を抑えるための省電力モードである。そして、C1〜C6は、数字が大きいほどより消費電力が抑えられるモードである。この省電力モードでは、消費電力を下げるためにCPUコア10の資源の使用が抑制される。そのため、インテルから提供されている省電力モードを、本実施例における「省消費資源モード」として用いることができる。特に、C2〜C6を本実施例における省消費資源モードとして用いた場合、処理を実行するためにC0のモードに移行する復帰時間が増大してしまう。そのため、C2〜C6では通信遅延時間が増大するので、通信遅延を短くするために「省消費資源モード」としてC1を利用することが好ましい。また、インテルから提供されているC0の省電力モードが、本実施例に係る通常モードの消費資源モードにあたる。

そして、通信制御スレッド201を実行するCPUコア10又は実行部は、動作モードがIdleの場合、消費資源モードに遷移できる。また、通信制御スレッド201は、動作モードがmpollの場合、waite命令による指示を受けることで、停止時に省消費資源モードか否かのいずれかの消費資源モードを選択することができる。

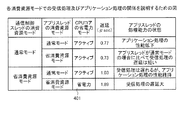

図4は、消費資源モードとCPUコアの省電力モードとの関係を示す図である。図4の欄400に示すように、アプリスレッド200及び通信制御スレッド201の両方が省消費資源モードで動作している場合、CPUコア10は省電力モードに移行してしまう。これに対して、欄400以外の欄で示されるように、アプリスレッド200又は通信制御スレッド201のいずれか一方が通常モードで動作していれば、CPUコア10は、アクティブになっており省電力モードには移行しない。CPUコア10が省電力モードに移行した場合、CPUコア10が有する演算器などの動作が抑制されてしまう。つまり、アプリスレッド200及び通信制御スレッド201が使用する共通資源の動作が抑制されてしまう場合がある。そのため、CPUコア10が省電力モードに移行した場合、通信制御スレッド201の起動までに時間が掛かってしまい、受信処理の遅延が大きくなってしまう。

図5は、各消費資源モードでの受信処理及びアプリケーション処理の関係を説明するための図である。

アプリスレッド200及び通信制御スレッド201のいずれも通常モードの場合、通信制御スレッド201による受信処理の遅延は0.77μsecとなる。この場合、通信制御スレッド201が共通資源などを用いて処理を行うため、アプリスレッド200によるアプリケーション処理の性能が低下する。

また、通信制御スレッド201が通常モードでアプリスレッド200が省消費資源モードの場合、通信制御スレッドによる受信処理の遅延は0.73μsecである。すなわち、両方のスレッドが通常モードである場合に比べて、アプリスレッド200を省消費資源モードにすると、受信処理の遅延が短くなる。このことから、アプリスレッド200が処理を実行中で無いのであれば、省消費資源モードに遷移させた方が、通信制御スレッド201による受信処理は速くなる。

通信制御スレッド201が省消費資源モードであり、アプリスレッド200が通常モードの場合、受信処理の遅延は1.03μsecとなる。この場合、通信制御スレッド201が通常モードに遷移した後に受信処理が行われるため、受信処理は遅延する。ただし、通信制御スレッド201による資源の消費が軽減されるため、アプリスレッド200によるアプリケーションの処理性能を維持できる。

通信制御スレッド201及びアプリスレッド200が共に省消費資源モードの場合、欄401に示すように、CPUコア10が省電力モードに入ってしまう。この場合、受信処理の遅延は、1.89μsecとなる。この場合、CPUコア10の省電力モードを解除した後、通信制御スレッド201が通常モードになって受信処理を開始するため、受信処理の遅延が大きくなってしまう。特に通信制御スレッド201が省消費資源モードでアプリスレッド200が通常モードの場合と比較しても、受信処理の遅延は非常に大きい。そこで、通信制御スレッド201による受信処理の遅延を軽減するために、通信制御スレッド201又はアプリスレッド200の少なくとも一方は省消費資源モードに遷移しないようにしておくことが望ましい。

そこで、図5に示す各省消費資源モードにおけるアプリケーション処理及び受信処理の関係から、例えば、アプリスレッド200及び通信制御スレッド201は、図6のテーブル500を満たすように、それぞれの動作モードに応じて消費資源モードを変更する。図6は、実施例1に係る各スレッドの消費資源モードの設定の一例を説明するための図である。

まず、テーブル500におけるグレーアウトされている欄501〜505は、対応するスレッドが処理を行っている状態であるため、そのスレッドの消費資源モードが通常モードに設定される場合を表している。例えば、アプリスレッド200がアプリケーション処理を実行している場合、欄501〜503で示されるように、アプリスレッド200は、通常モードに設定される。また、通信制御スレッド201が通信制御処理を行っている場合、欄504及び505で示されるように、通信制御スレッド201は、通常モードに設定される。

そして、アプリスレッド200又は通信制御スレッド201のいずれか一方が通常モードの場合、他方が省消費資源モードに遷移できるならば、他方を省消費資源モードに設定することが好ましい。まず、欄503及び504の場合、いずれのスレッドも省消費資源モードに遷移できないので、この場合は、両方のスレッドを通常モードで動作させる。一方、通信制御スレッド201は、通信制御処理を実行していない場合(以下では、「Idle」という。)及びポーリングをしている場合(以下では、「mpoll」という。)には、省消費資源モードへ遷移することができる。そこで、アプリスレッド200がアプリケーション処理を行っている場合で、通信制御スレッド201がmpoll又はIdelの場合には、通信制御スレッド201は、省消費資源モードに設定される。

また、アプリスレッド200がアプリケーション処理を実行していない場合(以下では、「Idle」という。)、アプリスレッド200は、省消費資源モードに遷移できる。そこで、通信制御スレッド201が通信制御処理を行っており、アプリスレッド200がIdleの場合、アプリスレッド200は省消費資源モードに設定される。

また、アプリスレッド200がIdleで、通信制御スレッド201がIdleの場合、アプリスレッド200は通常モードに設定され、通信制御スレッド201は省消費資源モードに設定される。この場合、通信制御スレッド201は、Idleであり、通信制御処理を行わないので、省消費資源モードであっても問題はない。一方、アプリスレッド200もIdleであるので、本来であれば、消費資源モードであってもよい。しかし、アプリスレッド200も省消費資源モードに遷移してしまうと、CPUコア10が省電力モードに入ってしまう。それを避けるために、アプリスレッド200は、通常モードに設定されている。このように、アプリスレッド200が通常モードであるので、CPUコア10は、アクティブの状態を維持できる。

次に、アプリスレッド200がIdleで、通信制御スレッド201がmpollの場合、アプリスレッド200は省消費資源モードに設定され、通信制御スレッド201は通常モードに設定される。この場合、アプリスレッド200は、Idleであり、アプリケーション処理を行わないので、省消費資源モードであっても問題はない。一方、通信制御スレッド201は、mpollの状態であるので、通常モード及び省消費資源モードのいずれでもよい。ただし、通信制御スレッド201が省消費資源モードに遷移してしまうと、CPUコア10が省電力モードに入ってしまう。それを避けるために、通信制御スレッド201は、通常モードに設定されている。このように、通信制御スレッド201が通常モードであるので、CPUコア10は、アクティブの状態を維持できる。

そして、図6で表される消費資源モードの状態を実現するため、アプリスレッド200及び通信制御スレッド201を実行するCPUコア10又は実行部は、以下のような処理を行う。すなわち、アプリスレッド200及び通信制御スレッド201を実行するCPUコア10又は実行部は、動作モードが通信制御処理を実行するモード又はmpollからIdleの状態に遷移した場合、OSを利用してIdleルーチンを走らせて、消費資源モードの切替えを行う。また、通信制御スレッド201を実行するCPUコア10又は実行部は、動作モードが通信制御処理を実行するモード又はIdleの状態からmpollの状態に遷移した場合、OSを利用してmpollルーチンを走らせて、消費資源モードの切替えを行う。

ここで、Idleルーチン実行時のアプリスレッド200を実行するCPUコア10又は実行部の動作を説明する。アプリスレッド200を実行するCPUコア10又は実行部は、Ready状態のアプリケーション処理のプロセスがあるか否かを判定する。これは、Idleに切り替わりIdleルーチンを走らせる間に、アプリケーション処理のプロセスがReady状態になることが考えられるからである。そして、Ready状態のプロセスがある場合、アプリスレッド200を実行するCPUコア10又は実行部は、通信制御スレッド201に割り当てられたメモリ領域122を更新する。これにより、アプリスレッド200を実行するCPUコア10又は実行部は、動作モードのIdleからアプリケーション処理を実行するモードへの切り替わりを、通信制御スレッド201を実行するCPUコア10又は実行部に対して通知する。その後、アプリスレッド200を実行するCPUコア10又は実行部は、スケジューラを呼び出し、アプリケーション処理のプロセスの実行を待つ。

一方、Ready状態のプロセスがない場合、アプリスレッド200を実行するCPUコア10又は実行部は、Idleルーチン以前に、自己の動作モードがIdleであったか否かを判定する。これは、後述するように、Idleの状態のアプリスレッド200が、割り込み又は通信制御スレッド201の動作モードの変化が発生することによりIdleルーチンを繰り返すためである。そして、以前の動作モードがIdleでなかった場合、アプリスレッド200を実行するCPUコア10又は実行部は、通信制御スレッド201に割り当てられたメモリ領域122を更新し、通信制御スレッド201を実行するCPUコア10又は実行部に対して、自己の動作モードが変化したことを通知する。その後、アプリスレッド200を実行するCPUコア10又は実行部は、通信制御スレッド201の動作モードがIdleか否かを判定する。通信制御スレッド201の動作モードがIdleの場合、アプリスレッド200を実行するCPUコア10又は実行部は、自己の消費資源モードを通常モードに設定する。これに対して、通信制御スレッド201の動作モードがIdleでない、アプリスレッド200を実行するCPUコア10又は実行部は、自己の消費資源モードを省消費資源モードに設定する。

その後、アプリスレッド200を実行するCPUコア10又は実行部は、通信制御スレッド201の動作モードの変化により自己に割り当てられたメモリ領域121が更新される又は割り込みが発生するまで待機する。メモリ領域121が更新される又は割り込みが発生すると、アプリスレッド200を実行するCPUコア10又は実行部は、Idleルーチンを繰り返す。

また、アプリスレッド200を実行するCPUコア10又は実行部は、アプリケーション処理を実行するモードに遷移した場合、消費資源モードを通常モードに設定する。

次に、Idleルーチン実行時の通信制御スレッド201を実行するCPUコア10又は実行部の動作を説明する。通信制御スレッド201を実行するCPUコア10又は実行部は、Ready状態の通信制御処理のプロセスがあるか否かを判定する。これは、Idleに切り替わりIdleルーチンを走らせる間に、通信制御処理のプロセスがReady状態になることが考えられるからである。そして、Ready状態のプロセスがある場合、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200に割り当てられたメモリ領域121を更新する。これにより、通信制御スレッド201を実行するCPUコア10又は実行部は、動作モードのIdleからアプリケーション処理を実行するモードへの切り替わりを、アプリスレッド200を実行するCPUコア10又は実行部へ通知する。その後、通信制御スレッド201を実行するCPUコア10又は実行部は、スケジューラを呼び出し、通信制御処理のプロセスの実行を待つ。

一方、Ready状態のプロセスがない場合、通信制御スレッド201を実行するCPUコア10又は実行部は、Idleルーチン以前に、自己の動作モードがIdleであったか否かを判定する。これは、Idleの状態の通信制御スレッド201が、割り込み又はアプリスレッド200の動作モードの変化が発生することによりIdleルーチンを繰り返すためである。そして、以前の動作モードがIdleでなかった場合、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200に割り当てられたメモリ領域121を更新し、アプリスレッド200を実行するCPUコア10又は実行部に対して、自己の動作モードが変化したことを通知する。その後、通信制御スレッド201を実行するCPUコア10又は実行部は、自己の消費資源モードを省消費資源モードに設定する。

その後、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200の動作モードの変化により自己に割り当てられたメモリ領域122が更新される又は割り込みが発生するまで待機する。メモリ領域122が更新される又は割り込みが発生すると、通信制御スレッド201を実行するCPUコア10又は実行部は、Idleルーチンを繰り返す。

次に、mpollルーチン実行時の通信制御スレッド201を実行するCPUコア10又は実行部の動作を説明する。通信制御スレッド201を実行するCPUコア10又は実行部は、CPUコア20又は21からデータが到着したか否かを判定する。これは、mpollに切り替わりmpollルーチンを走らせる間に、データを受信することが考えられるからである。そして、データが到着している場合、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200に割り当てられたメモリ領域121を更新して、動作モードがmpollから通信制御処理を実行するモードに切り替わったことを、アプリスレッド200を実行するCPUコア10又は実行部へ通知する。その後、通信制御スレッド201を実行するCPUコア10又は実行部は、データの受信処理を実施する。

一方、データが到着していない場合、通信制御スレッド201を実行するCPUコア10又は実行部は、mpollルーチン以前に、自己の動作モードがmpollであったか否かを判定する。これは、mpollの状態の通信制御スレッド201が、割り込み又はアプリスレッド200の動作モードの変化が発生することによりmpollルーチンを繰り返すためである。そして、以前の動作モードがmpollでなかった場合、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200に割り当てられたメモリ領域121を更新し、アプリスレッド200を実行するCPUコア10又は実行部に対して、自己の動作モードが変化したことを通知する。その後、通信制御スレッド201を実行するCPUコア10又は実行部は、自己の消費資源モードを省消費資源モードに設定する。

その後、通信制御スレッド201を実行するCPUコア10又は実行部は、アプリスレッド200の動作モードの変化により自己に割り当てられたメモリ領域121が更新される又は割り込みが発生するまで待機する。メモリ領域121が更新される又は割り込みが発生すると、通信制御スレッド201を実行するCPUコア10又は実行部は、Idleルーチンを繰り返す。

また、通信制御スレッド201を実行するCPUコア10又は実行部は、通信制御処理を実行するモードに遷移した場合、消費資源モードを通常モードに設定する。

メモリコントローラ15は、メモリ12に対するデータの書き込み及び読み出しを行う。例えば、CPUコア20からデータがCPU10に向けて送られてくると、メモリコントローラ15は、メモリ12の通信制御スレッド201に割り当てられたメモリ領域122を更新する。メモリコントローラ15によるメモリ領域122の更新により、ポーリング中の通信制御スレッド201は、データの受信を検知し、データの受信処理を開始する。さらに、メモリコントローラ15は、通信制御スレッド201からの指示を受けて、アプリスレッド200に割り当てられたメモリ領域121を更新する。また、メモリコントローラ15は、アプリスレッド200からの指示を受けて、通信制御スレッド201に割り当てられたメモリ領域122を更新する。

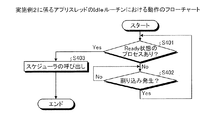

次に、図7を参照し、本実施例に係るアプリスレッド200のIdleルーチンにおける動作について説明する。図7は、実施例1に係るアプリスレッドのIdleルーチンにおける動作のフローチャートである。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

アプリスレッド200は、Ready状態のアプリケーション処理のプロセスがあるか否かを判定する(ステップS101)。

Ready状態のプロセスがない場合(ステップS101:否定)、アプリスレッド200は、今回のIdleルーチン以前に、自己の動作モードがIdleであったか否かを判定する(ステップS102)。そして、以前の動作モードがIdleでなかった場合(ステップS102:否定)、アプリスレッド200は、通信制御スレッド201に対して、自己の動作モードが変化したことを通知する(ステップS103)。具体的には、アプリスレッド200は、メモリ領域121を更新することで通信制御スレッド201への通知を行う。これに対して、以前の動作モードがIdleであった場合(ステップS102:肯定)、アプリスレッド200は、ステップS104へ進む。

アプリスレッド200は、通信制御スレッド201の動作モードがIdleか否かを判定する(ステップS104)。通信制御スレッド201の動作モードがIdleの場合(ステップS104:肯定)、アプリスレッド200は、自己の消費資源モードを通常モードに設定する(ステップS105)。これに対して、通信制御スレッド201の動作モードがIdleでない場合(ステップS104:否定)、アプリスレッド200は、自己の消費資源モードを省消費資源モードに設定する(ステップS106)。

その後、アプリスレッド200は、通信制御スレッド201の動作モードの変化により自己に割り当てられたメモリ領域121が更新されたか又は割り込みが発生したかを判定する(ステップS107)。メモリ領域121の更新及び割り込みのいずれも発生していない場合(ステップS107:否定)、アプリスレッド200は、メモリ領域121が更新される又は割り込みが発生するまで待機する。これに対して、メモリ領域121の更新又は割り込みが発生した場合(ステップS107:肯定)、アプリスレッド200は、ステップS101に戻る。

一方、Ready状態のプロセスがある場合(ステップS101:肯定)、アプリスレッド200は、動作モードがIdleからアプリケーション処理を実行するモードに切り替わったことを通信制御スレッド201へ通知する(ステップS108)。具体的には、アプリスレッド200は、メモリ領域122を更新することで通信制御スレッド201への通知を行う。その後、アプリスレッド200は、スケジューラを呼び出し(ステップS109)、アプリケーション処理のプロセスの実行を待つ。

次に、図8を参照し、本実施例に係る通信制御スレッド201のIdleルーチンにおける動作について説明する。図8は、実施例1に係る通信制御スレッドのIdleルーチンにおける動作のフローチャートである。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

通信制御スレッド201は、Ready状態の通信制御処理のプロセスがあるか否かを判定する(ステップS201)。

Ready状態のプロセスがない場合(ステップS201:否定)、通信制御スレッド201は、今回のIdleルーチン以前に、自己の動作モードがIdleであったか否かを判定する(ステップS202)。そして、以前の動作モードがIdleでなかった場合(ステップS202:否定)、通信制御スレッド201は、メモリ領域121を更新し、アプリスレッド200に対して自己の動作モードが変化したことを通知する(ステップS203)。これに対して、以前の動作モードがIdleであった場合(ステップS202:肯定)、通信制御スレッド201は、ステップS204へ進む。

通信制御スレッド201は、自己の消費資源モードを省消費資源モードに設定する(ステップS204)。

その後、通信制御スレッド201は、アプリスレッド200の動作モードの変化により自己に割り当てられたメモリ領域122が更新されたか又は割り込みが発生したかを判定する(ステップS205)。メモリ領域122の更新及び割り込みのいずれも発生していない場合(ステップS205:否定)、通信制御スレッド201は、メモリ領域122が更新される又は割り込みが発生するまで待機する。これに対して、メモリ領域122の更新又は割り込みが発生した場合(ステップS205:肯定)、通信制御スレッド201は、ステップS201に戻る。

一方、Ready状態のプロセスがある場合(ステップS201:肯定)、通信制御スレッド201は、動作モードがIdleから通信制御処理を実行するモードに切り替わったことをアプリスレッド200へ通知する(ステップS206)。具体的には、通信制御スレッド201は、メモリ領域121を更新することでアプリスレッド200への通知を行う。その後、通信制御スレッド201は、スケジューラを呼び出し(ステップS207)、通信制御処理のプロセスの実行を待つ。

次に、図9を参照し、本実施例に係る通信制御スレッド201のmpollルーチンにおける動作について説明する。図9は、実施例1に係る通信制御スレッドのmpollルーチンにおける動作のフローチャートである。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

通信制御スレッド201は、CPUコア20又は21からのデータが到着しているか否かを判定する(ステップS301)。

データが到着していない場合(ステップS301:否定)、通信制御スレッド201は、今回のmpollルーチン以前に、自己の動作モードがmpollであったか否かを判定する(ステップS302)。そして、以前の動作モードがmpollでなかった場合(ステップS302:否定)、通信制御スレッド201は、メモリ領域121を更新し、アプリスレッド200に対して自己の動作モードが変化したことを通知する(ステップS303)。これに対して、以前の動作モードがmpollであった場合(ステップS302:肯定)、通信制御スレッド201は、ステップS304へ進む。

通信制御スレッド201は、アプリスレッド200の動作モードがIdleか否かを判定する(ステップS304)。アプリスレッド200の動作モードがIdleの場合(ステップS304:肯定)、通信制御スレッド201は、自己の消費資源モードを通常モードに設定する(ステップS305)。これに対して、アプリスレッド200の動作モードがIdleでない場合(ステップS304:否定)、通信制御スレッド201は、自己の消費資源モードを省消費資源モードに設定する(ステップS306)。

その後、通信制御スレッド201は、アプリスレッド200の動作モードの変化により自己に割り当てられたメモリ領域122が更新されたか又は割り込みが発生したかを判定する(ステップS307)。メモリ領域122の更新及び割り込みのいずれも発生していない場合(ステップS307:否定)、通信制御スレッド201は、メモリ領域122が更新される又は割り込みが発生するまで待機する。これに対して、メモリ領域122の更新又は割り込みが発生した場合(ステップS307:肯定)、通信制御スレッド201は、ステップS301に戻る。

一方、Ready状態のプロセスがある場合(ステップS301:肯定)、通信制御スレッド201は、動作モードがIdleから通信制御処理を実行するモードに切り替わったことをアプリスレッド200へ通知する(ステップS308)。具体的には、通信制御スレッド201は、メモリ領域121を更新することでアプリスレッド200への通知を行う。その後、通信制御スレッド201は、受信処理を実施する(ステップS309)。

次に、図10を参照して、各スレッドの動作モード及び消費資源モードの遷移の一例について説明する。図10は、実施例1に係る各スレッドの動作モード及び消費資源モードの遷移の一例を示すタイムチャートである。図10の帯グラフ601はアプリスレッド200の動作モードの遷移を表している。また、図10の帯グラフ602は通信制御スレッド201の動作モードの遷移を表している。また、図10の帯グラフ603はCPUコア10の省電力モードの遷移を表している。さらに、図10の最下部の矢印は時間経過を表している。そして、帯グラフ601及び602におけるグレーアウトしている部分は、それぞれのスレッドの消費資源モードが通常モードであることを表している。また、帯グラフ603におけるグレーアウトしている部分は、CPUコア10が省電力モードに入っていない状態、すなわちアクティブな状態を表している。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

時刻t1までは、アプリスレッド200の動作モードは、アプリケーション処理を行っている状態である。この状態では、アプリスレッド200の省電力モードは、通常モードである。また、通信制御スレッド201の動作モードは、mpollの状態である。この状態では、通信制御スレッド201の省電力モードは、省消費資源モードである。この場合、アプリスレッド200が通常モードであるので、CPUコア10の省電力モードはアクティブである。

そして、時刻t1でアプリスレッド200におけるアプリケーション処理が終了する。これにより、アプリスレッド200の動作モードはIdleに遷移する。そして、アプリスレッド200は、通信制御スレッド201がmpollなので、自己の消費資源モードを省消費資源モードに設定する。通信制御スレッド201は、アプリスレッド200がIdleであり、自己がmpollなので、自己の消費資源モードを通常モードに設定する。この場合、通信制御スレッド201が通常モードであるので、CPUコア10の省電力モードはアクティブである。

次に、時刻t2でCPUコア20又は21からデータが到着する。これにより、通信制御スレッド201の動作モードは、受信処理などの通信制御処理を実行するモードへ遷移する。通信制御スレッド201の消費資源モードは既に通常モードであるので変化しない。また、アプリスレッド200の消費資源モードも、省消費資源モードから変化しない。この場合、通信制御スレッド201が通常モードであるので、CPUコア10の省電力モードはアクティブである。

次に、時刻t3で通信制御処理が終了する、データ到着を待つため通信制御スレッド201の動作モードはmpollに遷移する。ここで、アプリスレッド200の動作モードがIdleであるので、通信制御スレッド201は、省消費資源モードを通常モードのまま維持する。また、アプリスレッド200も、消費資源モードを省消費資源モードのまま維持する。この場合、通信制御スレッド201が通常モードであるので、CPUコア10の省電力モードはアクティブである。

次に、時刻t4でアプリスレッド200がアプリケーション処理を開始する。これにより、アプリスレッド200は、消費資源モードを通常モードに設定する。これを受けて、動作モードがmpollである通信制御スレッド201は、消費資源モードを省消費資源モードに設定する。この場合、アプリスレッド200が通常モードであるので、CPUコア10の省電力モードはアクティブである。

次に、時刻t5でCPUコア20又は21からデータが到着する。これにより、通信制御スレッド201の動作モードは、受信処理などの通信制御処理を実行するモードへ遷移する。そして、通信制御スレッド201は、消費資源モードを通常モードに設定する。この時、アプリスレッド200は、アプリケーション処理を実行しているので、消費資源モードを通常モードのまま維持する。この場合、アプリスレッド200及び通信制御スレッドともに通常モードであるので、CPUコア10の省電力モードはアクティブである。

次に、時刻t6でアプリケーション処理が終了し、アプリスレッド200の動作モードはIdleに遷移する。この時、通信制御スレッド201が通信制御処理を実行中であるので、アプリスレッド200は、消費資源モードを省消費資源モードに設定する。通信制御スレッド201は、消費資源モードを通常モードのまま維持する。この場合、通信制御スレッド201が通常モードであるので、CPUコア10の省電力モードはアクティブである。

そして、時刻t7で通信制御処理が終了し、通信制御スレッド201の動作モードはIdleに遷移する。通信制御スレッド201は、アプリスレッド200の動作モードがIdleであるので、消費資源モードを省消費資源モードに設定する。アプリスレッド200は、通信制御スレッド201の動作モードがIdleであるので、消費資源モードを通常モードに設定する。この場合、アプリスレッド200が通常モードであるので、CPUコア10の省電力モードはアクティブである。

このように、アプリスレッド200及び通信制御スレッド201のいずれか片方をなるべく省消費資源モードにすることで、通信制御処理又はアプリケーション処理における処理速度を向上させることができる。また、CPUコア10は、常にアクティブとなり、省電力モードに遷移しないため、通信制御スレッド201の受信処理の遅延を軽減することができる。

図11は、ポーリングによるアプリケーション処理への影響を説明するための図である。図11は縦軸で時間を表し、横軸でアプリケーション処理に対応するベンチマークの種類を表している。横軸の各ベンチマークにおける左端のグラフがポーリング処理を行わない場合の各ベンチマークの処理時間を表している。また、横軸の各ベンチマークにおける中央のグラフが単純なビジーポーリングを行った場合の、各ベンチマークの処理時間を表している。単純なビジーポーリングとは、アプリケーション処理が実行されている場合にポーリングを数クロック停止するポーズ命令を使用してポーリングを行った場合である。また、横軸の各ベンチマークにおける右端のグラフが省消費資源モードでポーリング処理を行った場合の、各ベンチマークの処理時間を表している。そして、縦軸の時間は、ポーリング処理を行わない場合の各ベンチマークの処理時間により各処理時間を正規化した値である。

図11に示すように、単純なビジーポーリングを行った場合には、アプリケーション処理の処理時間が非常に長くなり、アプリケーション処理の性能が低下している。これに対して、省消費資源モードでポーリングを行った場合には、単純なビジーポーリングを行った場合に比較していずれのベンチマークにおいても処理時間が短くなっている。すなわち、本実施例のように、アプリスレッド200がアプリケーション処理を実行している場合にポーリングを行うのであれば、通信制御スレッド201を省消費資源モードにすることで、アプリケーション処理の性能低下を軽減することができる。

以上に説明したように、本実施例に係る情報処理装置は、他のスレッドが処理を実行している場合、ポーリングを行うスレッドを実行するCPUコア又は実行部は省消費電力モードに遷移する。これにより、あるスレッドがポーリングを行っている場合に、他のスレッドが実行している処理の速度を向上させることができる。

また、常にいずれかのスレッドを実行するCPUコア又は実行部の消費資源モードを通常モードにしておくことで、CPUコアが省電力モードに遷移することを防止でき、受信処理における遅延を軽減することができる。

さらに、あるスレッドを実行するCPUコア又は実行部が処理を実行している場合、なるべく他のスレッドを実行するCPUコア又は実行部を省消費資源モードに遷移させることで、その処理の実行速度を向上させることができる。例えば、通信制御スレッドを実行するCPUコア又は実行部がポーリングを行っている場合に、アプリスレッドを実行するCPUコア又は実行部をなるべく省消費資源モードに遷移させることで、受信処理の遅延を軽減できる。

このように、本実施例に係る情報処理装置は、高い通信性能を維持しつつアプリケーションの処理性能の低下を抑制することができる。

次に、実施例2について説明する。本実施例に係る情報処理装置は、アプリスレッドを実行するCPUコア又は実行部の消費資源モードを常に通常モードにしておくことが実施例1と異なる。そこで、以下では、アプリスレッド及び通信制御スレッドを実行するCPUコア又は実行部の消費資源モードの遷移について主に説明する。ここでは、実施例1と同じ機能を有する各部については説明を省略する。

図12は、実施例2に係る各スレッドの消費資源モードの設定の一例を説明するための図である。アプリスレッド200及び通信制御スレッド201を実行するCPUコア又は実行部は、図12のテーブル510を満たすように、それぞれの動作モードに応じて消費資源モードを変更する。

まず、テーブル510におけるグレーアウトされている欄511〜515は、対応するスレッドが処理を行っている状態であるため、そのスレッドの消費資源モードが通常モードに設定される場合を表している。

さらに、本実施例の場合、欄516〜518に示すように、アプリスレッド200がIdleであっても、通信制御スレッド201の動作モードにかかわらず、アプリスレッド200を実行するCPUコア又は実行部は、消費資源モードを通常モードに設定する。このように、アプリスレッド200を実行するCPUコア又は実行部を常に通常動作モードにすることで、CPUコア10は、省電力モードに遷移することはなくなり、常にアクティブとなる。

そこで、通信制御スレッド201を実行するCPUコア又は実行部は、CPUコア10の省電力モードへの遷移を気にせずに、省消費資源モードに遷移できる場合には、消費資源モードを省消費資源モードに設定することができる。すなわち、通信制御スレッド201を実行するCPUコア又は実行部は、動作モードがIdle又はmpollの場合には、消費資源モードを省消費資源モードに設定する。

そして、アプリスレッド200及び通信制御スレッド201を実行するCPUコア又は実行部は、動作モードが通信制御処理を実行するモード又はmpollからIdleの状態に遷移した場合、OSを利用してIdleルーチンを走らせて、消費資源モードの切替えを行う。また、通信制御スレッド201を実行するCPUコア又は実行部は、動作モードが通信制御処理を実行するモード又はIdleの状態からmpollの状態に遷移した場合、OSを利用してmpollルーチンを走らせて、消費資源モードの切替えを行う。これにより、図12で表される消費資源モードの状態が実現される。

次に、図13を参照し、本実施例に係るアプリスレッド200のIdleルーチンにおける動作について説明する。図13は、実施例2に係るアプリスレッドのIdleルーチンにおける動作のフローチャートである。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

アプリスレッド200は、Ready状態のアプリケーション処理のプロセスがあるか否かを判定する(ステップS401)。

Ready状態のプロセスがない場合(ステップS401:否定)、アプリスレッド200は、割り込みが発生したか否かを判定する(ステップS402)。割り込みのいずれも発生していない場合(ステップS402:否定)、アプリスレッド200は、割り込みが発生するまで待機する。これに対して、割り込みが発生した場合(ステップS402:肯定)、アプリスレッド200は、ステップS401に戻る。

一方、Ready状態のプロセスがある場合(ステップS401:肯定)、アプリスレッド200は、スケジューラを呼び出し(ステップS403)、アプリケーション処理のプロセスの実行を待つ。

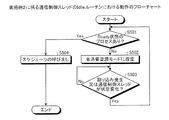

次に、図14を参照し、本実施例に係る通信制御スレッド201のIdleルーチンにおける動作について説明する。図14は、実施例2に係る通信制御スレッドのIdleルーチンにおける動作のフローチャートである。

通信制御スレッド201は、Ready状態の通信制御処理のプロセスがあるか否かを判定する(ステップS501)。

Ready状態のプロセスがない場合(ステップS501:否定)、通信制御スレッド201は、自己の消費資源モードを省消費資源モードに設定する(ステップS502)。

その後、通信制御スレッド201は、自己に割り当てられたメモリ領域122が更新されたか又は割り込みが発生したかを判定する(ステップS503)。メモリ領域122の更新及び割り込みのいずれも発生していない場合(ステップS503:否定)、通信制御スレッド201は、メモリ領域122が更新される又は割り込みが発生するまで待機する。これに対して、メモリ領域122の更新又は割り込みが発生した場合(ステップS503:肯定)、通信制御スレッド201は、ステップS501に戻る。

一方、Ready状態のプロセスがある場合(ステップS501:肯定)、通信制御スレッド201は、スケジューラを呼び出し(ステップS504)、通信制御処理のプロセスの実行を待つ。

次に、図15を参照し、本実施例に係る通信制御スレッド201のmpollルーチンにおける動作について説明する。図15は、実施例2に係る通信制御スレッドのmpollルーチンにおける動作のフローチャートである。

通信制御スレッド201は、CPUコア20又は21からのデータが到着しているか否かを判定する(ステップS601)。

データが到着していない場合(ステップS601:否定)、通信制御スレッド201は、消費資源モードを省消費資源モードに設定する(ステップS602)。

その後、通信制御スレッド201は、メモリ領域122が更新されたか又は割り込みが発生したかを判定する(ステップS603)。メモリ領域122の更新及び割り込みのいずれも発生していない場合(ステップS603:否定)、通信制御スレッド201は、メモリ領域122が更新される又は割り込みが発生するまで待機する。これに対して、メモリ領域122の更新又は割り込みが発生した場合(ステップS603:肯定)、通信制御スレッド201は、ステップS601に戻る。

一方、Ready状態のプロセスがある場合(ステップS601:肯定)、通信制御スレッド201は、受信処理を実施する(ステップS604)。

次に、図16を参照して、各スレッドの動作モード及び消費資源モードの遷移の一例について説明する。図16は、実施例2に係る各スレッドの動作モード及び消費資源モードの遷移の一例を示すタイムチャートである。図16の帯グラフ611はアプリスレッド200の動作モードの遷移を表している。また、図16の帯グラフ612は通信制御スレッド201の動作モードの遷移を表している。また、図16の帯グラフ613はCPUコア10の省電力モードの遷移を表している。さらに、図16の最下部の矢印は時間経過を表している。そして、帯グラフ611及び612におけるグレーアウトしている部分は、それぞれのスレッドの消費資源モードが通常モードであることを表している。また、帯グラフ613におけるグレーアウトしている部分は、CPUコア10が省電力モードに入っていない状態、すなわちアクティブな状態を表している。ここでは、説明を分かり易くするために、各スレッドが処理を行っているように説明する。

アプリスレッド200は、動作モードがどのモードに遷移しても、帯グラフ611に示すように消費資源モードを通常モードに維持する。そのため、CPUコア10は、帯グラフ613に示されるように常にアクティブの状態になっている。

一方、時刻T1までは、通信制御スレッド201の動作モードは、mpollの状態である。この状態では、通信制御スレッド201の省電力モードは、省消費資源モードである。

そして、時刻T1でアプリスレッド200におけるアプリケーション処理が終了する。これにより、アプリスレッド200の動作モードはIdleに遷移する。これに対して、通信制御スレッド201は、アプリスレッド200の動作モードに関らず、自己がmpollなので、自己の消費資源モードを省消費資源モードに維持する。

次に、時刻T2でCPUコア20又は21からデータが到着する。これにより、通信制御スレッド201の動作モードは、受信処理などの通信制御処理を実行するモードへ遷移する。これにより、通信制御スレッド201は、消費資源モードを通常モードに設定する。

次に、時刻T3で通信制御処理が終了し、データ到着を待つため通信制御スレッド201の動作モードはmpollに遷移する。これにより、通信制御スレッド201は、消費資源モードを省消費資源モードに設定する。

次に、時刻T4でアプリスレッド200がアプリケーション処理を開始する。このときも、動作モードがmpollである通信制御スレッド201は、消費資源モードを省消費資源モードのまま維持する。

次に、時刻T5でCPUコア20又は21からデータが到着する。これにより、通信制御スレッド201の動作モードは、受信処理などの通信制御処理を実行するモードへ遷移する。そして、通信制御スレッド201は、消費資源モードを通常モードに設定する。

次に、時刻T6でアプリケーション処理が終了し、アプリスレッド200の動作モードはIdleに遷移する。これに対して、通信制御スレッド201は、通信制御処理を実行中であるので、消費資源モードを通常モードのまま維持する。

そして、時刻T7で通信制御処理が終了し、通信制御スレッド201の動作モードはIdleに遷移する。通信制御スレッド201は、アプリスレッド200の動作モードに関らず、消費資源モードを省消費資源モードに設定する。

以上に説明したように、本実施例に係る情報処理装置においても、他のスレッドを実行するCPUコア又は実行部が処理を実行している場合、ポーリングを行うスレッドは省消費電力モードに遷移する。これにより、あるスレッドを実行するCPUコア又は実行部がポーリングを行っている場合に、他のスレッドが実行している処理の速度を向上させることができる。また、常にアプリスレッドを実行するCPUコア又は実行部の消費資源モードを通常モードにしておくことで、CPUコアが省電力モードに遷移することを防止でき、受信処理における遅延を軽減することができる。

また、アプリスレッドを常に通常モードにし、通信制御スレッドが省消費資源モードに遷移できる場合には、通信制御スレッドを省消費資源モードに設定するので、実施例1に比べて制御が容易になる。

さらに、以上の実施例では、受信処理の遅延をなるべく軽減するため、CPUコアを常にアクティブの状態にするように、いずれかのスレッドを実行するCPUコア又は実行部の消費資源モードが通常モードとなるように設定した。ただし、受信処理の遅延の許容できる程度によっては、全てのスレッドを実行するCPUコア又は実行部が省消費資源モードになることを許容して制御してもよい。その場合も、他のスレッドを実行するCPUコア又は実行部が処理を実行している場合、ポーリングを行うスレッドを実行するCPUコア又は実行部は省消費電力モードに遷移する。これにより、あるスレッドを実行するCPUコア又は実行部がポーリングを行っている場合に、他のスレッドを実行するCPUコア又は実行部が実行している処理の速度を向上させるという効果を得ることはできる。

また、以上では、図1に示すシステム構成を有する情報処理システムを例に説明したが、システム構成はこれ以外の構成を用いることもできる。図17は、情報処理システムの他の構成を示す構成図である。図17では、図1におけるメモリコントローラ15及びI/Oブリッジ16が、CPUコア10及び11に内蔵されている。また、メモリコントローラ25及びI/Oブリッジ26が、CPUコア20及び21に内蔵されている。

この場合、CPUコア10には、メモリ12aが接続されている。そして、CPUコア10に内蔵されたメモリコントローラによりメモリ12aに対するデータの読み書きが行われる。また、CPUコア11には、メモリ12bが接続されている。そして、CPUコア11に内蔵されたメモリコントローラによりメモリ12bに対するデータの読み書きが行われる。

また、CPUコア10及び11は、内蔵されているI/OバスによりI/O13及びI/O14と接続されており、CPUコア10及び11は、内蔵されているI/OバスによりI/O13及びI/O14との通信を行う。

このように、CPUコアにメモリコントローラやI/Oバスが内蔵されているシステム構成の場合でも、上述した各機能を有することができ、同様の効果を発揮することができる。