トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。トランジスタは、バイポーラトランジスタや電界効果トランジスタなど様々な形態が考案されている。電界効果トランジスタは、FET(Field Effect Transistor)、IGFET(Insulated Gate FET)、MISFET(Metal Insulator Semiconductor FET)などとも呼ばれ、特にゲート絶縁層に酸化絶縁層を用いた電界効果トランジスタはMOSFET(Metal Oxide Semiconductor FET)と呼ばれる。また、真空蒸着法、スパッタリング法、CVD法などの薄膜形成技術を用いて、ガラス、石英、プラスチックなどの基板上に、薄膜状に形成されたトランジスタは、薄膜トランジスタ(TFT:Thin Film Transistor)と呼ばれている。

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

また、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー(電気的な位置エネルギー)のことをいう。ただし、一般的に、ある一点における電位と基準となる電位(例えば接地電位)との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてもよいし、電圧を電位と読み替えてもよいこととする。

(実施の形態1)

本実施の形態では、非線形素子の一形態として、酸化物半導体を有するトランジスタを用いたダイオードについて、トランジスタがn型である場合について図1乃至図3を用いて説明する。本実施の形態にて説明するダイオードは、トランジスタのソース電極またはドレイン電極にゲート電極が接続されたものである。

一般に、ダイオードとは、アノードおよびカソードの2つの端子を有し、アノードの電位が、カソードの電位よりも高い場合に電流が流れる状態、すなわち導通状態となり、アノードの電位が、カソードの電位よりも低い場合にほとんど電流が流れない状態、すなわち非導通状態(絶縁状態)となる性質を有している。

ダイオードのこの性質は整流特性といわれ、ダイオードが導通状態となる方向を順方向、非導通状態となる方向を逆方向という。順方向の時の電圧を順方向電圧、または順方向バイアスといい、順方向の時の電流を順方向電流という。また、逆方向の時の電圧を逆方向電圧といい、逆方向の時の電流を逆方向電流という。

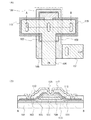

図1に示すダイオードでは、配線125が第3の電極113および第3の電極115と接続され、更には第2の電極109と接続され、第2の電極109は酸化物半導体層107を介して第1の電極105に接続されている。第1の電極105は配線131に接続されている。

図1(A)はダイオード接続されたトランジスタ133の上面図であり、図1(B)は図1(A)の一点鎖線A−Bの断面図に相当する。

図1(B)に示すように、基板101上に形成された絶縁層103上に、第1の電極105、酸化物半導体層107、及び第2の電極109が積層される。また、第1の電極105、酸化物半導体層107、及び第2の電極109を覆うように、ゲート絶縁層111が設けられている。ゲート絶縁層111上には、第3の電極113及び第3の電極115が設けられている。ゲート絶縁層111及び第3の電極113及び第3の電極115上には層間絶縁層として機能する絶縁層117が設けられている。絶縁層117には、開口部が形成されており、開口部において第1の電極105と接続する配線131(図1(A)参照)、第2の電極109および第3の電極113及び第3の電極115と接続する配線125が形成される。第1の電極105は、トランジスタのソース電極またはドレイン電極の一方として機能する。第2の電極109は、トランジスタのソース電極またはドレイン電極の他方として機能する。第3の電極113及び第3の電極115は、トランジスタのゲート電極として機能する。

本実施の形態のトランジスタは、縦型トランジスタであり、ゲート電極として機能する第3の電極113と、第3の電極115とは分離しており、且つ第1の電極105、酸化物半導体層107、及び第2の電極109を介して対向していることを特徴とする。

なお、トランジスタは、ゲート(ゲート電極)と、ドレイン(ドレイン電極またはドレイン領域)と、ソース(ソース電極またはソース領域)とを含む少なくとも三つの端子を有する素子であり、ドレインとソースの間にチャネル形成領域を有しており、ドレインとチャネル形成領域とソースとを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件などによって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインとよばない場合がある。その場合、一例としては、それぞれを第1の端子、第2の端子と表記する場合がある。あるいは、それぞれを第1の電極、第2の電極と表記する場合がある。あるいは、第1の領域、第2の領域と表記する場合がある。

基板101は、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。基板101としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素(B2O3)と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、B2O3よりBaOを多く含むガラス基板を用いることが好ましい。

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラスなどを用いることができる。

絶縁層103は、酸化シリコン、酸化窒化シリコンなど酸化物絶縁層、または窒化シリコン、窒化酸化シリコン、窒化アルミニウム、または窒化酸化アルミニウムなどの窒化物絶縁層で形成する。また、絶縁層103は積層構造でもよく、例えば、基板101側から上記した窒化物絶縁層のいずれか一つ以上と、上記した酸化物絶縁層のいずれか一つ以上との積層構造とすることができる。

第1の電極105及び第2の電極109は、アルミニウム(Al)、クロム(Cr)、鉄(Fe)、銅(Cu)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、イットリウム(Y)、銀(Ag)から選ばれた元素、または上述した元素を成分とする合金、上述した元素を組み合わせた合金などで形成する。また、マンガン(Mn)、マグネシウム(Mg)、ジルコニウム(Zr)、ベリリウム(Be)、トリウム(Th)から選択されたいずれか一または複数の材料を用いることができる。また、第1の電極105及び第2の電極109は、単層構造、または二層以上の積層構造とすることができる。例えば、シリコン(Si)を含むアルミニウムの単層構造、アルミニウム層上にチタン層を積層する二層構造、タングステン層上にチタン層を積層する二層構造、チタン層と、そのチタン層上に重ねてアルミニウム層を積層し、さらにその上にチタン層を形成する三層構造などが挙げられる。

また、アルミニウム(Al)に、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)などアルミニウム層に生ずるヒロックやウィスカーの発生を防止する元素が添加されているアルミニウム材料を用いることで耐熱性を向上させることが可能となる。

第1の電極105及び第2の電極109は、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

酸化物半導体層107としては、四元系金属酸化物であるIn−Sn−Ga−Zn−O系膜や、三元系金属酸化物であるIn−Ga−Zn−O系膜、In−Sn−Zn−O系膜、In−Al−Zn−O系膜、Sn−Ga−Zn−O系膜、Al−Ga−Zn−O系膜、Sn−Al−Zn−O系膜や、二元系金属酸化物であるIn−Zn−O系膜、Sn−Zn−O系膜、Al−Zn−O系膜、Zn−Mg−O系膜、Sn−Mg−O系膜、In−Mg−O系膜、In−Ga−O系膜や、In−O系膜、Sn−O系膜、Zn−O系膜などの酸化物半導体層を用いることができる。また、上記酸化物半導体層にSiO2を含んでもよい。

また、酸化物半導体層107は、InMO3(ZnO)m(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO3(ZnO)m(m>0)で表記される構造の酸化物半導体層のうち、MとしてGaを含む構造の酸化物半導体を、In−Ga−Zn−O系酸化物半導体とよび、その薄膜をIn−Ga−Zn−O系膜ともよぶこととする。

本実施の形態で用いる酸化物半導体層107は、酸化物半導体層に含まれる水素の濃度が5×1019/cm3以下、好ましくは5×1018/cm3以下、より好ましくは5×1017/cm3以下か、または1×1016/cm3未満であり、酸化物半導体層に含まれる水素が低減されている。即ち、酸化物半導体層の主成分以外の不純物が極力含まれないように高純度化されている。また、酸化物半導体層107のキャリア濃度は1×1012/cm3未満、好ましくは1×1011/cm3未満である。即ち、酸化物半導体層のキャリア濃度は、限りなくゼロに近い。また、エネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。なお、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectroscopy)で行えばよい。また、キャリア濃度は、ホール効果測定により測定することができる。

酸化物半導体層107の厚さは、30nm以上3000nm以下とするとよい。酸化物半導体層107の厚さを薄くすることで、トランジスタのチャネル長を小さくすることが可能であり、オン電流及び電界効果移動度の高いトランジスタを作製することができる。一方、酸化物半導体層107の厚さを厚くすることで、代表的には100nm以上3000nm以下とすることで、大電力用の半導体装置を作製することができる。

ゲート絶縁層111は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、または酸化アルミニウムを単層でまたは積層して形成することができる。ゲート絶縁層111は、酸化物半導体層107と接する部分が酸素を含むことが好ましく、特に好ましくは酸化シリコンにより形成する。酸化シリコンを用いることで、酸化物半導体層107に酸素を供給することができ、特性を良好にすることができる。ゲート絶縁層111の厚さは、50nm以上500nm以下とするとよい。ゲート絶縁層111の厚さを薄くすることで、電界効果移動度の高いトランジスタを作製することができ、駆動回路を同一基板に作製することができる。一方、ゲート絶縁層111の厚さを厚くすることで、ゲートリーク電流を低減することができる。

また、ゲート絶縁層111として、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたHfSixOy(x>0、y>0)、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))、酸化ハフニウム、酸化イットリウムなどのhigh−k材料を用いることでゲートリーク電流を低減できる。さらには、high−k材料と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、または酸化アルミニウムのいずれか一以上との積層構造とすることができる。

ゲート電極として機能する第3の電極113及び第3の電極115は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜などを用いて形成することができる。また、マンガン、マグネシウム、ジルコニウム、ベリリウムから選択されたのいずれか一または複数の材料を用いてもよい。また、第3の電極113及び第3の電極115は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウムの単層構造、アルミニウム層上にチタン層を積層する二層構造、チタン層と、そのチタン層上にアルミニウム層を積層し、さらにその上にチタン層を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素のいずれか一、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

本実施の形態に係る酸化物半導体層は、n型不純物である水素を酸化物半導体層から除去し、酸化物半導体層の主成分以外の不純物が極力含まれないように高純度化することにより真性(i型)とし、または真性型とせんとしたものである。すなわち、不純物を添加してi型化するのでなく、水素、水、水酸基または水素化物などの不純物を極力除去することにより、高純度化されたi型(真性半導体)またはそれに近づけることを特徴としている。そうすることにより、フェルミ準位(Ef)は真性フェルミ準位(Ei)と同じレベルにまですることができる。

上記したように、不純物を極力除去することにより、例えば、トランジスタのチャネル幅Wが1×104μmでチャネル長が3μmの素子であっても、オフ電流が10−13A以下ときわめて低く、さらに、サブスレッショルドスイング値(S値)を0.1V/dec.(ゲート絶縁層厚100nm)以下とすることができる。

このように、酸化物半導体層の主成分以外の不純物、代表的には水素、水、水酸基または水素化物などが極力含まれないように高純度化することにより、トランジスタの動作を良好なものとすることができる。特に、オフ電流を低減することができる。

ところで、チャネルが基板と概略平行に形成される横型トランジスタにおいては、チャネルのほかにソース及びドレインを設ける必要があり、基板におけるトランジスタの専有面積が大きくなってしまい、微細化の妨げとなる。しかしながら、縦型トランジスタにおいては、ソース、チャネル、及びドレインを積層するため、基板表面における占有面積を低減することができる。この結果、トランジスタの微細化が可能である。なお、微細化などの制約がなければ、本実施の形態を横型トランジスタに適用することも可能である。

また、縦型トランジスタのチャネル長は、酸化物半導体層の厚さで制御できるため、酸化物半導体層107の厚さを薄くすることでチャネル長の小さいトランジスタとすることが可能である。チャネル長を小さくすることで、ソース、チャネル、及びドレインの直列抵抗を低減できるため、トランジスタのオン電流および電界効果移動度を上昇させることができる。また、水素濃度が低減され高純度化された酸化物半導体を有するトランジスタは、オフ電流が極めて低く、オフ時には電流がほとんど流れない絶縁状態となる。このため、酸化物半導体層の厚さを薄くし、縦型トランジスタのチャネル長を小さくしても、非導通状態のオフ電流がほとんど無いトランジスタとすることができる。

このように、水素濃度が低減され高純度化された酸化物半導体を用いることで、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。本実施の形態では、水素濃度が低減され高純度化された酸化物半導体を有するトランジスタを用いてダイオードを形成する。

なお、本実施の形態のダイオードは、図1に示すものに限定されない。図1に示すダイオードでは、酸化物半導体層107中を第2の電極109から第1の電極105に電流が流れるが、図2に示すように、酸化物半導体層107中を第1の電極105から第2の電極109に電流が流れる構成としてもよい。

図2に示すダイオードでは、配線125が第3の電極113および第3の電極115と接続され、更には第1の電極105と接続されている。第1の電極105は酸化物半導体層107を介して第2の電極109と接続されている。第2の電極109は、配線129に接続されている。

なお、図2に示すダイオードでは、配線125が他の電極などとの重なりを避けて設けられているため、配線125と、これらの電極との間に生じる寄生容量を抑えつつ動作させることができる。

このような水素濃度が低減され高純度化された酸化物半導体を有するトランジスタのソースまたはドレインをゲートと電気的に接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、アバランシェ降伏現象が起きにくい(すなわち、耐圧が大きい)ダイオードを作製することができる。

また、第1の電極105の酸化物半導体層107と接する導電性材料の仕事関数をφmdとし、第2の電極109の酸化物半導体層107と接する導電性材料の仕事関数をφmsとし、酸化物半導体層107の電子親和力をχとし、これらを式1を充足するように構成することで、第1の電極105及び第2の電極109と、酸化物半導体層107との接合界面におけるエネルギー障壁を低減し、特に順方向電流特性に優れたダイオードとすることができる。

φms≦χ≧φmd・・・式1

図3に、図1及び図2で説明した、酸化物半導体(OS)を有するn型トランジスタを用いたダイオードを回路記号で示す。図3(A)は、図1で説明した酸化物半導体(OS)を有するn型トランジスタを用いたダイオードの回路記号であり、第2の電極109が配線125を介して、第3の電極113および第3の電極115に接続されている状態を示している。第2の電極109に第1の電極105よりも高い電圧(正の電圧)が印加されると、ゲート電極として機能する第3の電極113および第3の電極115にも正の電圧が印加されるため、トランジスタ133がオン状態となり、第1の電極105と第2の電極109の間に電流が流れる。

一方、第2の電極109に第1の電極105よりも低い電圧(負の電圧)が印加されると、トランジスタ133がオフ状態となるため、第1の電極105と第2の電極109の間に電流がほとんど流れない。このようにして、水素濃度が低減され高純度化された酸化物半導体を有するトランジスタ133を、第2の電極109をアノード、第1の電極105をカソードとするダイオードとして機能させることができる。

図3(B)は、図2で説明した酸化物半導体(OS)を有するn型トランジスタを用いたダイオードの回路記号であり、第1の電極105が配線125を介して、第3の電極113および第3の電極115に接続されている状態を示している。第1の電極105に第2の電極109よりも高い電圧(正の電圧)が印加されると、ゲート電極として機能する第3の電極113および第3の電極115にも正の電圧が印加されるため、トランジスタ133がオン状態となり、第1の電極105と第2の電極109の間に電流が流れる。

一方、第1の電極105に第2の電極109よりも低い電圧(負の電圧)が印加されると、トランジスタ133がオフ状態となるため、第1の電極105と第2の電極109の間に電流がほとんど流れない。このようにして、水素濃度が低減され高純度化された酸化物半導体を有するトランジスタ133を、第1の電極105をアノード、第2の電極109をカソードとするダイオードとして機能させることができる。

本実施の形態を用いることで、整流特性に優れ、アバランシェ降伏現象が起きにくい(すなわち、耐圧が大きい)ダイオードを作製することができる。特に順バイアス時の特性に優れたダイオードを得ることができる。

(実施の形態2)

本実施の形態では、実施の形態1で説明したダイオードの整流特性をより高める構成について図1乃至図5を用いて説明する。

実施の形態1では、順方向の特性に優れたダイオードの構成について説明したが、本実施の形態では、逆方向の特性に優れたダイオードの構成について説明する。本実施の形態を用いることにより、より逆方向電流が少ないダイオードとすることができる。

具体的には、トランジスタ133の第1の電極105に使用する導電性材料の仕事関数と、酸化物半導体層107の電子親和力と、第2の電極109に使用する導電性材料の仕事関数の関係を工夫することで、トランジスタ133を、逆方向電流がさらに少ないダイオードとして機能させることができる。

ここで、図4を用いて、仕事関数φMを有する金属と、電子親和力χを有する酸化物半導体の接合におけるエネルギー障壁について説明しておく。

図4(A)は、φMがχよりも大きい場合の熱平衡状態におけるバンド構造であり、接合界面800において、金属801と酸化物半導体802が接合している様子を示している。酸化物半導体802は真性半導体を示しており、酸化物半導体802のフェルミレベル823は、伝導帯822と価電子帯824のほぼ中央に位置している。金属801の仕事関数φMは、真空準位820と、金属801のフェルミレベル821のエネルギー差であり、図中では仕事関数803として示している。酸化物半導体802の電子親和力χは、真空準位820と、酸化物半導体802の伝導帯822のエネルギー差であり、図中では電子親和力804として示している。

接合界面800において、金属801のフェルミレベル821と酸化物半導体802のフェルミレベル823は一致する。また、伝導帯822及び価電子帯824は、φMとχのエネルギー差に応じて、接合界面800近傍で曲がった形状となる。

エネルギー障壁805は、仕事関数803(φM)と電子親和力804(χ)のエネルギー差(φM−χ)であり、図4(A)では、仕事関数803(φM)が酸化物半導体802の電子親和力804(χ)より大きいため、エネルギー障壁805は正の値となる。このため、金属801に存在する電子は、エネルギー障壁805に阻まれ、酸化物半導体802の伝導帯822にほとんど移動することができない。すなわち、電流が流れにくくなる。

図4(B)は、φMがχよりも小さい場合の熱平衡状態におけるバンド構造を示している。図4(B)では、仕事関数803(φM)が酸化物半導体802の電子親和力804(χ)より小さいため、エネルギー障壁805は負の値となる。このため、金属801に存在する電子は、酸化物半導体802の伝導帯822に容易に移動することができる。すなわち、電流が流れ易くなる。

なお、仕事関数803(φM)と電子親和力804(χ)が等しい場合は、エネルギー障壁805が存在しないため、金属801に存在する電子は、酸化物半導体802の伝導帯822に容易に移動することができる。すなわち、エネルギー障壁805が負の値の場合と同様に、電流が流れ易くなる。

続いて、図4(A)で説明したエネルギー障壁を、トランジスタ133に適用することにより、逆方向電流を効果的に低減し、整流特性に優れたダイオードを実現するトランジスタの構成について図1及び図2を用いて説明する。

図1で説明したトランジスタ133は、第2の電極109が、第3の電極113及び第3の電極115に接続している。このため、トランジスタ133は、第2の電極109をアノード、第1の電極105をカソードとするダイオードとして機能する。

また、図2で説明したトランジスタ133は、第1の電極105が、第3の電極113及び第3の電極115に接続している。このため、トランジスタ133は、第1の電極105をアノード、第2の電極109をカソードとするダイオードとして機能する。

第1の電極105または第2の電極109のうち、アノードとなる電極の酸化物半導体層107と接する導電性材料の仕事関数をφmdとし、第1の電極105または第2の電極109のうち、カソードとなる電極の酸化物半導体層107と接する導電性材料の仕事関数をφmsとし、酸化物半導体層107の電子親和力をχとし、これらを式2を充足するように構成する。

φms>χ≧φmd・・・式2

例えば、酸化物半導体の電子親和力χが4.3eVである場合、酸化物半導体の電子親和力よりも大きい仕事関数の導電性材料の例として、タングステン(W)、モリブデン(Mo)、クロム(Cr)、鉄(Fe)、金(Au)、プラチナ(Pt)、銅(Cu)、コバルト(Co)、ニッケル(Ni)、ベリリウム(Be)、酸化インジウム錫(ITO)などを用いることができる。

また、酸化物半導体の電子親和力χが4.3eVである場合、仕事関数が酸化物半導体の電子親和力以下である導電性材料の例として、チタン(Ti)、イットリウム(Y)、アルミニウム(Al)、ジルコニウム(Zr)、マグネシウム(Mg)、銀(Ag)、マンガン(Mn)、タンタル(Ta)、窒化タンタル、窒化チタンなどを用いることができる。

実施の形態1で示したように、第1の電極105または第2の電極109は、単層構造、または二層以上の積層構造とすることができる。この場合、酸化物半導体に接する層を、式2を満たす関係とすればよい。例えば、カソードとして機能する第1の電極105を、モリブデンとアルミニウムとチタンの三層構造とする場合は、酸化物半導体に接する層にタングステンを使用し、アルミニウムをモリブデンとチタンで挟む構造とする。アルミニウムは、モリブデン及びチタンよりも抵抗率が小さいため、配線抵抗を低減させる効果が実現できる。また、アルミニウムをモリブデンとチタンで挟む構造とすることで、アルミニウムのマイグレーションを防ぐ事ができる。

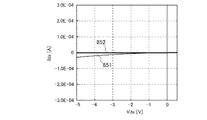

図5に、図1で説明したダイオードを、式1を満たすように構成した場合と、式2を満たすように構成した場合の逆方向電流のデバイスシミュレーション結果を示す。デバイスシミュレーションは、Silvaco社製ソフトウエア「Atlas」を用いて行った。前提条件として、アノードとカソード間の距離(酸化物半導体層の厚さ)を500nm、アノード及びカソードと酸化物半導体層の接触面積を1μm2(1μm×1μm)、酸化物半導体層の電子親和力(χ)を4.3eV、アノードとなる導電層の仕事関数(φmd)を4.3eVとした。また、カソードとなる導電層の仕事関数(φms)は、式1を満たす構成の場合は4.3eVとし、式2を満たす構成の場合は4.7eVとした。また、ダイオードとして用いるトランジスタのゲート絶縁層を、厚さ100nm、比誘電率4.0としてシミュレーションを行った。

図5の横軸は逆バイアス時のアノード−カソード間(ドレイン−ソース間)電圧(Vds)を示している。縦軸はアノード−カソード間(ドレイン−ソース間)の電流(Ids)を示している。また、曲線851は式1を満たす構成としたダイオードの逆方向電流電圧特性を示しており、曲線852は式2を満たす構成としたダイオードの逆方向電流電圧特性を示している。図5から、式1及び式2を満たす構成としたダイオードのどちらも逆方向電流が少ないことが確認できるが、式2を満たす構成としたダイオードの方がより逆方向電流が少なくなっていることが確認できる。

このように、酸化物半導体を有するトランジスタを用いて、酸化物半導体の電子親和力と電極材料の仕事関数の関係を、式2を満たす構成とすることで、より整流特性に優れ、アバランシェ降伏現象が起きにくい(すなわち、耐圧が大きい)ダイオードを作製することができる。特に逆方向電流(漏れ電流)の少ないダイオードを得ることができる。

(実施の形態3)

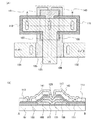

本実施の形態では、非線形素子の一態様であるダイオードの一例であって、実施の形態1及び実施の形態2とは異なる構造のものについて、図6を用いて説明する。本実施の形態にて説明するダイオードは、トランジスタのソース電極またはドレイン電極にゲート電極が電気的に接続されたものである。

図6に示すダイオードでは、配線131が第1の電極105および第3の電極113と接続され、配線132が第1の電極106および第3の電極115と接続されている。第1の電極105および第1の電極106は酸化物半導体層107を介して第2の電極109と接続されている。第2の電極109は、配線129に接続されている。

図6(A)はダイオード接続されたトランジスタ141、トランジスタ143の上面図であり、図6(B)は図6(A)の一点鎖線A−Bの断面図に相当する。

図6(B)に示すように、基板101上に形成された絶縁層103上に、第1の電極105、第1の電極106、酸化物半導体層107、及び第2の電極109が積層される。また、第1の電極105、第1の電極106、酸化物半導体層107、及び第2の電極109を覆うように、ゲート絶縁層111が設けられている。ゲート絶縁層111上には、第3の電極113及び第3の電極115が設けられている。ゲート絶縁層111及び第3の電極113及び第3の電極115上には層間絶縁層として機能する絶縁層117が設けられている。絶縁層117には、開口部が形成されており、開口部において第1の電極105及び第3の電極113と接続する配線131、第1の電極106及び第3の電極115と接続する配線132(図6(A)参照)、第2の電極109と接続する配線129が形成される。

第1の電極105は、トランジスタ141のソース電極またはドレイン電極の一方として機能する。第1の電極106は、トランジスタ143のソース電極またはドレイン電極の一方として機能する。第2の電極109は、トランジスタ141、143のソース電極またはドレイン電極の他方として機能する。第3の電極113は、トランジスタ141のゲート電極として機能する。第3の電極115は、トランジスタ143のゲート電極として機能する。

本実施の形態では、第1の電極105と、第1の電極106とが分離されていることを特徴とする。更には、トランジスタ141と、トランジスタ143とが、第2の電極109及び配線129で並列に接続していることを特徴とする。

または、トランジスタ141と第2のトランジスタ143を直列に接続してもよい。この場合、第1の電極105は、トランジスタ141のソース電極またはドレイン電極の一方(例えばソース)として機能する。第2の電極109は、トランジスタ141のソース電極またはドレイン電極の他方(例えばドレイン)として機能する。第3の電極113は、トランジスタ141のゲート電極として機能する。また、第2の電極109は、トランジスタ143のソース電極またはドレイン電極の一方(例えばソース)として機能する。第1の電極106は、トランジスタ143のソース電極またはドレイン電極の他方(例えばドレイン)として機能する。第3の電極115は、トランジスタ143のゲート電極として機能する。

即ち、トランジスタ141と第2のトランジスタ143が第2の電極109で直列に接続する。この場合、配線129を設けなくともよい。

本実施の形態のトランジスタ141、トランジスタ143は、実施の形態1及び実施の形態2と同様に、水素濃度が低減され高純度化された酸化物半導体層を用いている。このため、トランジスタの動作を良好なものとすることができる。特に、オフ電流を低減することができる。この結果、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。

なお、本実施の形態のダイオードは、図6に示すものに限定されない。図6に示すダイオードでは、酸化物半導体層107中を第1の電極105から第2の電極109に電流が流れるが、図7に示すように、酸化物半導体層107中を第2の電極109から第1の電極105に電流が流れる構成としてもよい。

図7に示すダイオードでは、配線125が第3の電極113および第3の電極115と接続され、更には第2の電極109と接続され、第2の電極109は酸化物半導体層107を介して第1の電極105に接続されている。第1の電極105は配線131および配線132に接続されている。

なお、図7に示すダイオードでは、配線125がトランジスタ141およびトランジスタ143と重畳して設けられているが、これに限定されず、図2と同様に、配線125がトランジスタ141およびトランジスタ143と重畳しないように設けてもよく、配線125がトランジスタ141およびトランジスタ143と重畳しない場合には、配線125と、これらの電極との間に生じる寄生容量を抑えつつ動作させることができる。

このようにトランジスタのソース電極またはドレイン電極をゲート電極と電気的に接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、降伏現象が起きにくい(すなわち、耐圧が高い)ダイオードを作製することができる。

(実施の形態4)

本実施の形態では、非線形素子の一態様であるダイオードの一例であって、実施の形態1及び実施の形態2とは異なる構造のものについて、図8を用いて説明する。本実施の形態にて説明するダイオードは、トランジスタのソース電極またはドレイン電極にゲートが接続されたものである。

図8に示すダイオードでは、配線131が第1の電極105および第3の電極113と接続されている。第1の電極105は酸化物半導体層107を介して第2の電極109と接続されている。第2の電極109は、配線129に接続されている。

図8(A)はダイオード接続されたトランジスタ145の上面図であり、図8(B)は図8(A)の一点鎖線A−Bの断面図に相当する。

図8(B)に示すように、基板101上に形成された絶縁層103上に、第1の電極105、酸化物半導体層107、及び第2の電極109が積層される。また、第1の電極105、酸化物半導体層107、及び第2の電極109を覆うように、ゲート絶縁層111が設けられている。ゲート絶縁層111上には、第3の電極113が設けられている。ゲート絶縁層111及び第3の電極113上には層間絶縁層として機能する絶縁層117が設けられている。

絶縁層117に、開口部が形成されており、開口部において第3の電極113と配線131が接続されている。また、絶縁層117及びゲート絶縁層111に開口部が形成されており、開口部において第1の電極105と配線131が接続されており、また、異なる開口部において、第2の電極109と配線129が接続されている。(図8(A)参照)。

第1の電極105は、トランジスタ145のソース電極またはドレイン電極の一方として機能する。第2の電極109は、トランジスタ145のソース電極またはドレイン電極の他方として機能する。第3の電極113は、トランジスタ145のゲート電極として機能する。

本実施の形態では、ゲート電極として機能する第3の電極113が環状であることを特徴とする。ゲート電極として機能する第3の電極113を環状とすることで、トランジスタのチャネル幅を大きくすることができる。このため、トランジスタのオン電流を高めることができる。

本実施の形態のトランジスタ141、トランジスタ143は、実施の形態1と同様に、水素濃度が低減され高純度化された酸化物半導体を用いている。このため、トランジスタの動作を良好なものとすることができる。特に、オフ電流を低減することができる。この結果、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。

なお、本実施の形態のダイオードは、図8に示すものに限定されない。図8に示すダイオードでは、酸化物半導体層107中を第1の電極105から第2の電極109に電流が流れるが、図9に示すように、酸化物半導体層107中を第2の電極109から第1の電極105に電流が流れる構成としてもよい。

図9に示すダイオードでは、配線129が第2の電極109および第3の電極113と接続されている。第2の電極109は酸化物半導体層107を介して第1の電極105と接続されている。第1の電極105は配線131と接続されている。

このようなトランジスタのソース電極またはドレイン電極をゲート電極と電気的に接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、降伏現象が起きにくい(すなわち、耐圧が高い)ダイオードを作製することができる。

(実施の形態5)

本実施の形態では、図1に示すダイオード接続されたトランジスタの作製工程について、図10を用いて説明する。

図10(A)に示すように、基板101上に絶縁層103を形成し、絶縁層103上に第1の電極105を形成する。第1の電極105は、トランジスタのソース電極またはドレイン電極の一方として機能する。

絶縁層103は、スパッタリング法、CVD法、塗布法などで形成することができる。

なお、スパッタリング法で絶縁層103を形成する場合、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ絶縁層103を形成することが好ましい。これは、絶縁層103に水素、水、水酸基または水素化物などが含まれないようにするためである。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。吸着型の真空ポンプとしては、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室では、水素、水、水酸基または水素化物などが排気されるため、当該処理室で絶縁層103を形成すると、絶縁層103に含まれる不純物の濃度を低減できる。

また、絶縁層103を形成する際に用いるスパッタガスは、水素、水、水酸基または水素化物などの不純物が濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

スパッタリング法にはスパッタ用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、また、パルス的にバイアスを与えるパルスDCスパッタリング法もある。RFスパッタリング法は主に絶縁層を形成する場合に用いられ、DCスパッタリング法は主に金属膜を形成する場合に用いられる。

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料の膜を積層形成することも、同一チャンバーで複数種類の材料を同時に放電させて形成することもできる。

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタ装置がある。

また、スパッタリング法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法を用いることもできる。

本明細書のスパッタリングにおいては、上記したスパッタリング装置及びスパッタリング方法を適宜用いることができる。

本実施の形態では、基板101を処理室へ搬送し、水素、水、水酸基または水素化物などが除去された高純度酸素を含むスパッタガスを導入し、シリコンターゲットを用いて、基板101に絶縁層103として、酸化シリコンを形成する。なお、絶縁層103を形成する際は、基板101は加熱されていてもよい。

例えば、石英(好ましくは合成石英)を用い、基板温度100℃、基板とターゲットの間との距離(T−S間距離)を60mm、圧力0.4Pa、高周波電源電力1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により酸化シリコンを形成する。膜厚は、例えば100nmとするとよい。なお、石英(好ましくは合成石英)に代えてシリコンターゲットを用いることができる。なお、スパッタガスとして、酸素、または酸素及びアルゴンの混合ガスを用いて行う。

また、絶縁層103を積層構造で形成する場合、例えば、酸化シリコンと基板との間に水素、水、水酸基または水素化物などが除去された高純度窒素を含むスパッタガス及びシリコンターゲットを用いて窒化シリコンを形成する。この場合においても、酸化シリコンと同様に、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ窒化シリコンを形成することが好ましい。なお、当該工程において、基板101は加熱されていてもよい。

絶縁層103として窒化シリコンと酸化シリコンとを積層する場合、窒化シリコンと酸化シリコンを同じ処理室において、共通のシリコンターゲットを用いて形成することができる。先に窒素を含むスパッタガスを導入して、処理室内に装着されたシリコンターゲットを用いて窒化シリコンを形成し、次に酸素を含むスパッタガスに切り替えて同じシリコンターゲットを用いて酸化シリコンを形成する。窒化シリコン及び酸化シリコンを大気に曝露せずに連続して形成することができるため、窒化シリコン表面に水素、水、水酸基または水素化物などの不純物が吸着することを防止することができる。

第1の電極105は、基板101上に導電層をスパッタリング法、CVD法、または真空蒸着法で形成し、当該導電層上にフォトリソグラフィ工程によりレジストマスクを形成し、当該レジストマスクを用いて導電層をエッチングして、形成することができる。または、フォトリソグラフィ工程を用いず、印刷法、インクジェット法で第1の電極105を形成することで、工程数を削減することができる。なお、第1の電極105の端部をテーパ形状とすると、後に形成されるゲート絶縁層の被覆性が向上するため好ましい。第1の電極105の端部と絶縁層103のなす角の角度を30°以上60°以下(好ましくは40°以上50°以下)とすることで、後に形成されるゲート絶縁層の被覆性を向上させることができる。

本実施の形態では、第1の電極105となる導電層として、スパッタリング法により膜厚50nmのチタン層を形成し、厚さ100nmのアルミニウム層を形成し、厚さ50nmのチタン層を形成する。次に、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、第1の電極105を形成する。なお、後に形成する酸化物半導体層と接する第1の電極105の材料は、実施の形態2で説明した電子親和力と仕事関数の関係を考慮して選定することもできる。

次に、図10(B)に示すように、第1の電極105上に酸化物半導体層107及び第2の電極109を形成する。酸化物半導体層107はトランジスタのチャネル形成領域として機能し、第2の電極109はトランジスタのソース電極またはドレイン電極の他方として機能する。

ここで、酸化物半導体層107及び第2の電極109の作製方法について、説明する。

基板101及び第1の電極105上にスパッタリング法により酸化物半導体層を形成する。次に、酸化物半導体層上に導電層を形成する。

酸化物半導体層107に水素がなるべく含まれないようにするために、前処理として、スパッタリング装置の予備加熱室で第1の電極105が形成された基板101を予備加熱し、基板101に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に形成するゲート絶縁層111の形成前の基板101に行ってもよいし、後に形成する第3の電極113及び第3の電極115形成前の基板101に行ってもよい。

なお、酸化物半導体層をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、第1の電極105の表面に付着しているゴミや酸化層を除去することで、第1の電極105及び酸化物半導体層の界面における抵抗を低減することができるため好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に高周波電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。

本実施の形態では、In−Ga−Zn−O系金属酸化物ターゲットを用いたスパッタリング法により酸化物半導体層を形成する。また、酸化物半導体層は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO2を2重量%以上10重量%以下含むターゲットを用いて形成してもよい。

酸化物半導体層を形成する際に用いるスパッタガスは水素、水、水酸基または水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

酸化物半導体層をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及びZnを含む金属酸化物ターゲット(組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比]、In2O3:Ga2O3:ZnO=1:1:2[mol数比])を用いることができる。また、In、Ga、及びZnを含む金属酸化物ターゲットとして、In2O3:Ga2O3:ZnO=2:2:1[mol数比]、またはIn2O3:Ga2O3:ZnO=1:1:4[mol数比]の組成比を有するターゲットを用いることもできる。金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いて形成した酸化物半導体は緻密な膜となる。

減圧状態に保持された処理室内に基板を保持し、処理室内に残留する水分を除去しつつ、水素、水、水酸基または水素化物などが除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板101上に酸化物半導体層を形成する。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素、水、水酸基または水素化物など(より好ましくは炭素原子を含む化合物も)などが排気されるため、酸化物半導体層に含まれる不純物の濃度を低減できる。また、基板を加熱しながら酸化物半導体層を形成してもよい。

本実施の形態では、酸化物半導体層の成膜条件の一例として、基板温度室温、基板とターゲットの間との距離を110mm、圧力0.4Pa、直流(DC)電源電力0.5kW、酸素及びアルゴン(酸素流量15sccm:アルゴン流量30sccm)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいうが軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体層は好ましくは30nm以上3000nm以下とする。なお、適用する酸化物半導体層材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

なお、酸化物半導体層を形成する際のスパッタリング法は、絶縁層103に示したスパッタリング法を適宜用いることができる。

第2の電極109となる導電層は、第1の電極105の材料及び手法を適宜用いることができる。また、実施の形態2で示したように、使用する材料の仕事関数と酸化物半導体層の電子親和力に応じて、第1の電極105と第2の電極109を異なる材料とすることもできる。ここでは、第2の電極109となる導電層として、厚さ50nmのチタン層、厚さ100nmのアルミニウム層、及び厚さ50nmのチタン層を順に積層する。

次に、フォトリソグラフィ工程により導電層上にレジストマスクを形成し、当該レジストマスクを用いて第2の電極109となる導電層及び酸化物半導体層107となる酸化物半導体層をエッチングして、第2の電極109及び酸化物半導体層107を形成する。なお、フォトリソグラフィ工程により形成したレジストマスクの代わりに、インクジェット法を用いてレジストマスクを作製することで、工程数を削減することができる。当該エッチングにより、第2の電極109及び酸化物半導体層107の端部と、第1の電極105のなす角の角度を30°以上60°以下(好ましくは40°以上50°以下)とすることで、後に形成されるゲート絶縁層の被覆性を向上させることができるため好ましい。

なお、ここでの導電層及び酸化物半導体層のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。所望の形状の酸化物半導体層107及び第2の電極109を形成するために、材料に合わせてエッチング条件(エッチング液、エッチング時間、温度など)を適宜調節する。

なお、第2の電極109となる導電層及び酸化物半導体層と、第1の電極105とのエッチングレートが異なる場合は、第1の電極105のエッチングレートが低く、第2の電極109となる導電層及び酸化物半導体層のエッチングレートの高い条件を選択する。または、酸化物半導体層のエッチングレートが低く、第2の電極109となる導電層のエッチングレートの高い条件を選択して、第2の電極109となる導電層をエッチングした後、第1の電極105のエッチングレートが低く、酸化物半導体層のエッチングレートの高い条件を選択する。

酸化物半導体層をウエットエッチングするエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液、アンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2容量比)などを用いることができる。また、ITO−07N(関東化学社製)を用いてもよい。

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体に含まれるインジウムなどの材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

また、ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化シリコン(SiCl4)、四塩化炭素(CCl4)など)が好ましい。

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度など)を適宜調節する。

本実施の形態では、エッチャントとしてアンモニア過水を用いて、第2の電極109となる導電層をエッチングした後、燐酸と酢酸と硝酸を混ぜた溶液で酸化物半導体層をエッチングして、酸化物半導体層107を形成する。

次に、本実施の形態では、第1の加熱処理を行う。第1の加熱処理の温度は、400℃以上750℃以下、好ましくは400℃以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素、希ガスなどの不活性ガス雰囲気下において450℃において1時間の加熱処理を行った後、大気に触れさせないことで、酸化物半導体層への水素、水、水酸基または水素化物などの侵入を防ぐことで、水素濃度が低減され高純度化され、i型化または実質的にi型化された酸化物半導体層を得ることができる。即ち、この第1の加熱処理によって酸化物半導体層107の脱水化及び脱水素化の少なくとも一方を行うことができる。

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴンなどの希ガスに、水素、水、水酸基または水素化物などなどが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、結晶化率が90%以上、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場合もある。また、非晶質の酸化物半導体層の中に微結晶部(粒径1nm以上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる場合もある。

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層を形成する前の酸化物半導体層に行ってもよい。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

なお、酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層を形成した後、酸化物半導体層上に第2の電極となる導電層を積層した後、第1の電極、酸化物半導体層及び第2の電極上にゲート絶縁層を形成した後、またはゲート電極を形成した後のいずれで行ってもよい。

次に、図10(C)に示すように、第1の電極105、酸化物半導体層107、第2の電極109上にゲート絶縁層111を形成する。

不純物を除去することによりi型化または実質的にi型化された酸化物半導体層(水素濃度が低減され高純度化された酸化物半導体層)は界面準位、界面電荷に対して極めて敏感となるため、ゲート絶縁層111との界面は重要である。そのため高純度化された酸化物半導体層に接するゲート絶縁層111は、高品質化が要求される。

例えば、μ波(2.45GHz)を用いた高密度プラズマCVDにより、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。水素濃度が低減され高純度化された酸化物半導体層と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、ゲート絶縁層の形成後の加熱処理によってゲート絶縁層の膜質、酸化物半導体層との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体層との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

さらに、85℃、2×106V/cm、12時間のゲートバイアス・熱ストレス試験(BT試験)においては、不純物が酸化物半導体層に添加されていると、不純物と酸化物半導体層の主成分との結合が、強電界(B:バイアス)と高温(T:温度)により切断され、生成された未結合手がしきい値電圧(Vth)のドリフトを誘発することとなる。

これに対して、酸化物半導体層の不純物、特に水素や水などを極力除去し、上記のようにゲート絶縁層との界面特性を良好にすることにより、BT試験に対しても安定なトランジスタを得ることを可能としている。

スパッタリング法でゲート絶縁層111を形成することでゲート絶縁層111中の水素濃度を低減することができる。スパッタリング法により酸化シリコンを形成する場合には、ターゲットとしてシリコンターゲットまたは石英ターゲットを用い、スパッタガスとして酸素または、酸素及びアルゴンの混合ガスを用いて行う。

ゲート絶縁層111は、第1の電極105、酸化物半導体層107、及び第2の電極109側から酸化シリコンと窒化シリコンを積層した構造とすることもできる。例えば、第1のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン(SiOx(x>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン(SiNy(y>0))を積層して、膜厚100nmのゲート絶縁層としてもよい。本実施の形態では、圧力0.4Pa、高周波電源電力1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により膜厚100nmの酸化シリコンを形成する。

次に、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を行ってもよい。なお、当該第2の加熱処理は、のちに形成される第3の電極113及び第3の電極115、絶縁層117、または配線125のいずれかを形成した後に行ってもよい。当該加熱処理により、第1の加熱処理により生じた酸化物半導体層中の酸素欠損を、ゲート絶縁層中の酸素や、加熱処理雰囲気中の酸素で補うことで、よりi型化された酸化物半導体層を得ることができる。

次に、ゲート絶縁層111上にゲート電極として機能する第3の電極113及び第3の電極115を形成する。

第3の電極113及び第3の電極115は、ゲート絶縁層111上に第3の電極113及び第3の電極115となる導電層をスパッタリング法、CVD法、または真空蒸着法で形成し、当該導電層上にフォトリソグラフィ工程によりレジストマスクを形成し、当該レジストマスクを用いて導電層をエッチングして、形成することができる。第3の電極113及び第3の電極115となる導電膜は、第1の電極105と同様の材料を用いることができる。

本実施の形態では、厚さ150nmのチタン層をスパッタリング法により形成した後、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、第3の電極113及び第3の電極115を形成する。

以上の工程で、水素濃度が低減され高純度化された酸化物半導体層107を有するトランジスタ133を形成することができる。

次に、図10(D)に示すように、ゲート絶縁層111及び第3の電極113及び第3の電極115上に絶縁層117を形成した後、コンタクトホール119、コンタクトホール121、及びコンタクトホール123を形成する。

絶縁層117は、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、または酸化窒化アルミニウムなどの酸化物絶縁層、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、または窒化酸化アルミニウムなどの窒化物絶縁層を用いる。または、酸化物絶縁層及び窒化物絶縁層の積層とすることもできる。

絶縁層117は、スパッタリング法、CVD法などで形成する。なお、スパッタリング法で絶縁層117を形成する場合、基板101を100℃以上400℃以下の温度に加熱し、水素、水、水酸基または水素化物などが除去された高純度窒素を含むスパッタガスを導入しシリコンターゲットを用いて絶縁層を形成してもよい。この場合においても、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ絶縁層を形成することが好ましい。

なお、絶縁層117の形成後、さらに、大気中、100℃以上200℃以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって半導体装置の信頼性を向上できる。

コンタクトホール119、コンタクトホール121、及びコンタクトホール123は、フォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁層111及び絶縁層117の一部を除去して、第2の電極109、及び第3の電極113及び第3の電極115に達するコンタクトホール119、コンタクトホール121、及びコンタクトホール123を形成する。なお、図10には図示していないが、ゲート絶縁層111及び絶縁層117の一部を除去して、第1の電極105に達するコンタクトホールも形成する(図1参照)。

次に、ゲート絶縁層111、絶縁層117、コンタクトホール119、コンタクトホール121、及びコンタクトホール123上に導電層を形成した後、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、配線125、配線131(図10中には図示せず。)を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを削減できる。

配線125、配線131は、第1の電極105と同様に形成することができる。

なお、第3の電極113及び第3の電極115と、配線125、及び配線131の間に平坦化のための平坦化絶縁層を設けてもよい。平坦化絶縁層の代表例としては、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂などの、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)などがある。なお、これらの材料で形成される絶縁層を複数積層させることで、平坦化絶縁層を形成してもよい。

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi−O−Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いてもよい。また、有機基はフルオロ基を有していてもよい。

平坦化絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷など)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーターなどを用いることができる。

上記のように酸化物半導体層中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、少数キャリアの数が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。

このようにトランジスタのソース電極またはドレイン電極をゲート電極と接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、降伏現象が起きにくい(すなわち、耐圧が大きい)ダイオードを作製することができる。

なお、酸化物半導体層に接して設けられる絶縁層にハロゲン元素(例えば、フッ素または塩素)を含ませ、または酸化物半導体層を露出させた状態でハロゲン元素を含むガス雰囲気中でのプラズマ処理によって酸化物半導体層にハロゲン元素を含ませ、酸化物半導体層、または該酸化物半導体層に接して設けられる絶縁層との界面に存在しうる、水素、水分、水酸基または水素化物(水素化合物ともいう)などの不純物を排除してもよい。絶縁層にハロゲン元素を含ませる場合には、該絶縁層中におけるハロゲン元素濃度は、5×1018atoms/cm3以上1×1020atoms/cm3以下程度とすればよい。

なお、上記したように酸化物半導体層中または酸化物半導体層とこれに接する絶縁層との界面にハロゲン元素を含ませ、酸化物半導体層と接して設けられた絶縁層が酸化物絶縁層である場合には、酸化物半導体層と接しない側の酸化物絶縁層を、窒化物絶縁層で覆うことが好ましい。すなわち、酸化物半導体層に接する酸化物絶縁層の上に接して窒化シリコンなどを設ければよい。このような構造とすることで、水素、水分、水酸基または水素化物などの不純物が酸化物絶縁層に侵入することを防止することができる。

なお、図2及び図6乃至図9に示すダイオードも同様に形成することができる。

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

(実施の形態6)

本実施の形態では、実施の形態5とは異なる形態の酸化物半導体層を有するダイオード接続されたトランジスタとその作製方法について、図10及び図11を用いて説明する。

実施の形態5と同様に、図10(A)に示すように、基板101上に絶縁層103及び第1の電極105を形成する。次に、図10(B)に示すように、第1の電極105上に酸化物半導体層107及び第2の電極109を形成する。

次に、第1の加熱処理を行う。本実施の形態における第1の加熱処理は、上記実施の形態における第1の加熱処理とは異なるものであり、当該加熱処理によって、図11(A)に示すように、表面に結晶粒が形成される酸化物半導体層151を形成することができる。本実施の形態では、抵抗発熱体などの発熱体からの熱伝導及び熱輻射の少なくとも一方によって被処理物を加熱する装置を用いて第1の加熱処理を行う。ここで、加熱処理の温度は500℃以上700℃以下、好ましくは650℃以上700℃以下とすることが好適である。なお、加熱処理温度の上限は基板101の耐熱性の範囲内とする必要がある。また、加熱処理の時間は、1分以上10分以下とすることが好適である。RTA処理を適用することで、短時間に加熱処理を行うことができるため、基板101に対する熱の影響を小さくすることができる。つまり、加熱処理を長時間行う場合と比較して、加熱処理温度の上限を引き上げることが可能である。また、酸化物半導体層の表面近傍に、所定の構造の結晶粒を選択的に形成することが可能である。

本実施の形態で用いることができる加熱装置としては、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置などのRTA(Rapid Thermal Anneal)装置などがある。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

例えば、第1の加熱処理として、650℃以上700℃以下の高温に加熱した窒素または希ガスなどの不活性ガス雰囲気に基板を移動し、数分間加熱した後、高温に加熱した不活性ガス中から基板を出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴンなどの希ガスに、水素、水、水酸基または水素化物などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

なお、上記の加熱処理は、酸化物半導体層107を形成した後であればいずれのタイミングで行ってもよいが、脱水化または脱水素化を促進させるためには、酸化物半導体層107の表面に他の構成要素を設ける前に行うのが好適である。また、上記の加熱処理は、一回に限らず、複数回行っても良い。

ここで、図11(A)の鎖線部153の拡大図を図11(B)に示す。

酸化物半導体層151は、非晶質を主たる構成とする非晶質領域155と、酸化物半導体層151の表面に形成される結晶粒157とを有する。また、結晶粒157は、表面からの距離(深さ)が20nmまでの領域(表面近傍)に形成される。ただし、酸化物半導体層151の厚さが大きくなる場合にはこの限りではない。例えば、酸化物半導体層151の厚さが200nm以上となる場合には、「表面の近傍(表面近傍)」とは、表面からの距離(深さ)が酸化物半導体層の厚さの10%以下である領域をいう。

ここで、非晶質領域155は、非晶質酸化物半導体層を主たる構成としている。なお、「主たる」とは、例えば、50%以上を占める状態をいい、この場合には、非晶質酸化物半導体層が体積%(または重量%)で50%以上を占める状態をいうものとする。つまり、非晶質酸化物半導体層以外にも、酸化物半導体層の結晶などを含むことがあるが、その含有率は体積%(または重量%)で50%未満であることが望ましいがこれらの範囲に限定される必要はない。

酸化物半導体層の材料としてIn−Ga−Zn−O系酸化物半導体を用いる場合には、上記の非晶質領域155の組成は、Znの含有量(原子%)が、InまたはGaの含有量(原子%)未満となるようにするのが好適である。このような組成とすることにより、所定の組成の結晶粒157を形成することが容易になるためである。

この後、実施の形態5と同様に、ゲート絶縁層と、ゲート電極として機能する第3の電極を形成してトランジスタを作製する。

酸化物半導体層151の表面はゲート絶縁層と接するため、チャネルとなる。チャネルとなる領域に結晶粒を有することで、ソース、チャネル、及びドレイン間の抵抗が低減すると共に、キャリア移動度が上昇する。このため、当該酸化物半導体層151を有するトランジスタの電界効果移動度が上昇し、良好な電気特性を実現できる。

また、結晶粒157は、非晶質領域155と比較して安定であるため、これを酸化物半導体層151の表面近傍に有することで、非晶質領域155に不純物(例えば水素、水、水酸基または水素化物など)が取り込まれることを低減することが可能である。このため、酸化物半導体層151の信頼性を向上させることができる。

以上の工程により酸化物半導体層中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、少数キャリアの数が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。

このようにトランジスタのソース電極またはドレイン電極の一方をゲート電極と電気的に接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、本実施の形態によって、降伏現象が起きにくい(すなわち、耐圧が高い)ダイオードを作製することができる。

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

(実施の形態7)

本実施の形態では、図1に示すダイオード接続されたトランジスタの作製工程であって、実施の形態5とは異なるものについて、図10を用いて説明する。

実施の形態5と同様に、図10(A)に示すように、基板101上に第1の電極105を形成する。

次に、図10(B)に示すように、第1の電極105上に酸化物半導体層107及び第2の電極109を形成する。

なお、酸化物半導体層をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、第1の電極105の表面に付着しているゴミや酸化層を除去することで、第1の電極105及び酸化物半導体層の界面における抵抗を低減することができるため好ましい。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。

基板101及び第1の電極105上にスパッタリング法により酸化物半導体層を形成する。次に、酸化物半導体層上に導電層を形成する。

本実施の形態では、酸化物半導体層をIn−Ga−Zn−O系金属酸化物ターゲットを用いたスパッタリング法により形成する。本実施の形態では、減圧状態に保持された処理室内に基板を保持し、基板を室温または400℃未満の温度に加熱する。そして、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ、水素、水、水酸基または水素化物などが除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板101及び第1の電極105上に酸化物半導体層を形成する。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素、水、水酸基または水素化物(より好ましくは炭素原子を含む化合物も)などが排気されるため、当該処理室で形成した酸化物半導体層に含まれる不純物の濃度を低減できる。また、クライオポンプにより処理室内に残留する水素、水、水酸基または水素化物などを除去しながらスパッタ形成を行うことで、基板温度が室温から400℃未満でも水素原子、水などの不純物を低減した酸化物半導体層を形成することができる。

本実施の形態では、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源電力0.5kW、酸素(酸素流量比率100%)雰囲気下での成膜条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体層は、好ましくは30nm以上3000nm以下とする。なお、適用する酸化物半導体層材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

なお、酸化物半導体層を形成する際のスパッタリング法は、絶縁層103に示したスパッタリング法を適宜用いることができる。

次に、第2の電極109となる導電層を、第1の電極105の材料及び手法を用いて形成する。また、実施の形態2で示したように、使用する材料の仕事関数に応じて、第1の電極105と第2の電極109を異なる材料とすることもできる。

次に、実施の形態5と同様に、第2の電極109となる導電層及び酸化物半導体層107となる酸化物半導体層をエッチングして、第2の電極109及び酸化物半導体層107を形成する。所望の形状の酸化物半導体層107及び第2の電極109を形成するために、材料に合わせてエッチング条件(エッチング液、エッチング時間、温度など)を適宜調節する。

次に、図10(C)に示すように、実施の形態5と同様に、第1の電極105、酸化物半導体層107、第2の電極109上にゲート絶縁層111を形成する。ゲート絶縁層111は、酸化物半導体層107との界面特性が良好なものとすることが好ましく、μ波(2.45GHz)を用いた高密度プラズマCVDでゲート絶縁層111を形成することで、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。また、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の形成方法を適用することができる。

なお、ゲート絶縁層111を形成する前に逆スパッタを行い、少なくとも酸化物半導体層107の表面に付着しているレジスト残渣などを除去してもよい。

また、ゲート絶縁層111を形成する前にN2O、N2、またはArなどのガスを用いたプラズマ処理によって露出している酸化物半導体層の表面に付着した水素、水、水酸基または水素化物などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接するゲート絶縁層111を形成することが好ましい。

また、ゲート絶縁層111に、水素、水、水酸基または水素化物などがなるべく含まれないようにするために、前処理として、スパッタリング装置の予備加熱室で第1の電極105から第2の電極109まで形成された基板101を予備加熱し、基板101に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。または、ゲート絶縁層111を形成した後、基板101を、スパッタリング装置の予備加熱室で予備加熱して、基板101に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100℃以上400℃以下好ましくは150℃以上300℃以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

ゲート絶縁層111は、第1の電極105、酸化物半導体層107、及び第2の電極109側から酸化シリコンと窒化シリコンとを積層した構造とすることもできる。例えば、第1のゲート絶縁層としてスパッタリング法により膜厚5nm以上300nm以下の酸化シリコン(SiOx(x>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚50nm以上200nm以下の窒化シリコン(SiNy(y>0))を積層して、ゲート絶縁層とする。

次に、不活性ガス雰囲気下、または酸素ガス雰囲気下で加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を行ってもよい。なお、当該第2の加熱処理は、のちに形成される第3の電極113及び第3の電極115、絶縁層117、または配線125、配線131のいずれかを形成した後に行ってもよい。当該加熱処理により、酸化物半導体層中の酸素欠損を、ゲート絶縁層中の酸素や、加熱処理雰囲気中の酸素で補うことで、よりi型化された酸化物半導体層を得ることができる。

次に、図10(C)に示すように、実施の形態5と同様に、ゲート絶縁層111上にゲート電極として機能する第3の電極113及び第3の電極115を形成する。

以上の工程で、水素濃度が低減された酸化物半導体層107を有するトランジスタ133を形成することができる。

上記のように酸化物半導体層を形成する際に、反応雰囲気中に残留する水素、水、水酸基または水素化物などを除去することで、該酸化物半導体層中の水素濃度を低減することができる。それにより酸化物半導体層の安定化を図ることができる。

次に、図10(D)に示すように、実施の形態5と同様に、ゲート絶縁層111及び第3の電極113及び第3の電極115上に絶縁層117を形成した後、コンタクトホール119、コンタクトホール121、及びコンタクトホール123を形成する。

次に、図10(E)に示すように、実施の形態5と同様に、配線125、配線131を形成する。

次に、実施の形態5と同様に、絶縁層117を形成する。なお、絶縁層117の形成後、さらに、実施の形態5と同様に、大気中、100℃以上200℃以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって半導体装置の信頼性を向上できる。

なお、第3の電極113及び第3の電極115と、配線125及び配線131の間に平坦化のための平坦化絶縁層を設けてもよい。

上記のように酸化物半導体層を形成するに際し、反応雰囲気中に残留する水素、水、水酸基または水素化物などを除去することで、該酸化物半導体層中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、少数キャリアの数が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、高精細化に適し、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さないトランジスタを作製することができる。

このようにトランジスタのソース電極またはドレイン電極をゲート電極と電気的に接続させることで、逆方向電流が非常に少ないダイオードを得ることができる。従って、降伏現象が起きにくい(すなわち、耐圧が高い)ダイオードを作製することができる。

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

(実施の形態8)

上記実施の形態にて説明したダイオードなどの非線形素子は、半導体装置に適用することができる。半導体装置として、例えば表示装置を挙げることができる。

本発明の一態様である表示装置の構成について、図12を参照して説明する。図12は、表示装置が形成された基板200の上面図を示す。基板200上には、画素部201が形成されている。また、入力端子202及び入力端子203は、基板200上に形成された画素回路に対して画像を表示するための信号及び電源電力を供給する。

なお、本発明の一態様である表示装置は、図12に示す形態に限定されない。すなわち、基板200上には、走査線駆動回路及び信号線駆動回路の一方または双方が形成されていてもよい。

そして、基板200上に形成された走査線側の入力端子202及び信号線側の入力端子203と、画素部201とは、縦横に延びた配線によって接続されており、該配線は保護回路204乃至保護回路207に接続されている。

画素部201と、入力端子202とは、配線209によって接続されている。保護回路204は、画素部201と、入力端子202との間に配設され、配線209に接続されている。保護回路204を設けることによって、画素部201が有するトランジスタ等の各種半導体素子を保護することができ、これらが劣化し、または破壊することを防止できる。なお、配線209は、図中では一の配線を指し示しているが、配線209と平行に設けられている複数の配線のすべてが配線209と同様の接続関係を有する。なお、配線209は、走査線として機能するものである。

なお、走査線側には、入力端子202と画素部201との間に設けられている保護回路204のみならず、画素部201を挟んで入力端子202の反対側にも保護回路が設けられていても良い(図12の保護回路205を参照)。

一方で、画素部201と、入力端子203とは配線208によって接続されている。保護回路206は、画素部201と、入力端子203との間に配設され、配線208に接続されている。保護回路206を設けることによって、画素部201が有するトランジスタ等の各種半導体素子を保護することができ、これらが劣化し、または破壊されることを防止できる。なお、配線208は、図中では一の配線を指し示しているが、配線208と平行に設けられている複数の配線のすべてが配線208と同様の接続関係を有する。なお、配線208は、信号線として機能するものである。

なお、信号線側には、入力端子203と画素部201との間に設けられている保護回路206のみならず、画素部201を挟んで入力端子203の反対側にも設けられていても良い(図12の保護回路207を参照)。

なお、保護回路204乃至保護回路207は全て設ける必要はない。しかし、少なくとも保護回路204は設ける必要がある。走査線に過大な電流が生じることで、画素部201が有するトランジスタのゲート絶縁層が破壊され、多数の点欠陥を生じうるからである。

また、保護回路204のみならず保護回路206を設けることで信号線に過大な電流が生じることを防止できる。そのため、保護回路204のみを設ける場合と比較して信頼性が向上し、歩留まりが向上する。保護回路206を有することで、トランジスタ形成後のラビング工程等にて生じうる、静電気による破壊を防止することもできる。

更には、保護回路205及び保護回路207を有することで、信頼性を更に向上させることができる。また、歩留まりを高くすることができる。保護回路205及び保護回路207は、入力端子202及び入力端子203とは反対側に設けられている。そのため、これらは表示装置の作製工程(例えば、液晶表示装置の作製工程におけるラビング工程)中において生じる、各種半導体素子の劣化及び破壊を防止することに寄与する。

なお、図12では、基板200とは別に形成した信号線駆動回路及び走査線駆動回路をCOG方式やTAB方式等の公知の方式により基板200に実装する。しかし、これに限定されず、走査線駆動回路と画素部とを基板200上に形成し、信号線駆動回路は別に形成したものを実装してもよい。または、走査線駆動回路の一部或いは信号線駆動回路の一部を、画素部201と共に基板200上に形成し、走査線駆動回路の他の部分或いは信号線駆動回路の他の部分を実装するようにしても良い。走査線駆動回路の一部が画素部201と走査線側の入力端子202との間に設けられている場合には、走査線側の入力端子202と基板200上の走査線駆動回路の一部との間に保護回路を設けても良いし、走査線駆動回路の一部と画素部201との間に保護回路を設けても良いし、これらの双方に保護回路を設けても良い。また、信号線駆動回路の一部が画素部201と信号線側の入力端子203との間に設けられている場合には、信号線側の入力端子203と基板200上の信号線駆動回路の一部との間に保護回路を設けても良いし、信号線駆動回路の一部と画素部201との間に保護回路を設けても良いし、これらの双方に保護回路を設けても良い。つまり、駆動回路の形態は様々であるため、保護回路はその形態に合わせて設ける数と場所を定める。

次に、図12における保護回路204乃至保護回路207に用いられる保護回路の具体的な回路構成の例について、図13を参照して説明する。以下の説明ではn型トランジスタを設ける場合についてのみ説明する。

図13(A)に示す保護回路は、複数のトランジスタを用いた保護ダイオード211乃至保護ダイオード214を有する。保護ダイオード211は、酸化物半導体(OS)を有するn型トランジスタ211a及びn型トランジスタ211bが直列に接続されている。そして、n型トランジスタ211aのソース電極及びドレイン電極の一方は、n型トランジスタ211a及びn型トランジスタ211bのゲート電極と接続され、且つ電位Vssに保たれている。n型トランジスタ211aのソース電極及びドレイン電極の他方は、n型トランジスタ211bのソース電極及びドレイン電極の一方に接続されている。n型トランジスタ211bのソース電極及びドレイン電極の他方は保護ダイオード212に接続されている。そして、他の保護ダイオード212乃至保護ダイオード214も保護ダイオード211と同様に、それぞれ直列に接続された複数のトランジスタを有し、且つ直列に接続された複数のトランジスタの一端は、複数のトランジスタのゲート電極と接続されている。

なお、保護ダイオード211乃至保護ダイオード214のそれぞれが有するトランジスタの数及び極性は、図13(A)に示す構成に限定されない。例えば、保護ダイオード211は、直列に接続された三つのトランジスタにより構成されていてもよい。

そして、保護ダイオード211乃至保護ダイオード214は順に直列に接続されており、且つ保護ダイオード212と保護ダイオード213の間は、配線215に接続されている。なお、配線215は、保護対象となる半導体素子に電気的に接続されているものである。なお、配線215と接続する配線は、保護ダイオード212と保護ダイオード213との間の配線に限定されない。即ち、配線215は、保護ダイオード211と保護ダイオード212との間に接続されていても良いし、保護ダイオード213と保護ダイオード214との間に接続されていても良い。

そして、保護ダイオード214の一端は電源電位Vddに保たれている。また、保護ダイオード211乃至保護ダイオード214のそれぞれは、逆方向バイアスの電圧がかかるように接続されている。

図13(B)に示す保護回路は、保護ダイオード220、保護ダイオード221、容量素子222、容量素子223及び抵抗素子224を有する。抵抗素子224は2端子の抵抗であり、その一端には配線225から電位Vinが供給され、他端には電位Vssが供給される。抵抗素子224は、電位Vinが供給されなくなったときに配線225の電位をVssにするために設けられており、その抵抗値は配線225の配線抵抗よりも十分に大きくなるように設定する。保護ダイオード220及び保護ダイオード221は、ダイオード接続されたn型トランジスタを用いている。

なお、図13に示す保護ダイオードは、更に複数のトランジスタを直列に接続したものであっても良い。

ここで、図13に示す保護回路が動作する場合について考える。このとき、保護ダイオード211、212、221、230、231、234、235のソース電極及びドレイン電極において、電位Vssに保持される側がドレイン電極である。また他方はソース電極となる。保護ダイオード213、214、220、232、233、236、237のソース電極及びドレイン電極において、電位Vddに保持される側をソース電極とし、他方がドレイン電極となる。また、保護ダイオードを構成するトランジスタのしきい値電圧をVthと示す。

また、保護ダイオード211、212、221、230、231、234、235は電位Vinが電位Vssより高いときに逆バイアスの電圧がかかり、電流が流れにくい。一方、保護ダイオード213、214、220、232、233、236、237は、電位Vinが電位Vddより低いときに逆方向バイアスの電圧がかかり、電流が流れにくい。

ここでは、電位Voutが概ね電位Vssと電位Vddの間となるように設けられた保護回路の動作について説明する。

まず、電位Vinが電位Vddよりも高い場合を考える。電位Vinが電位Vddよりも高い場合、保護ダイオード213、214、220、232、233、236、237のゲート電極とソース電極間の電位差Vgs=Vin−Vdd>Vthのときに、当該n型トランジスタはオン状態となる。ここでは、Vinが異常に高い場合を想定しているため、当該n型トランジスタはオン状態となる。このとき、保護ダイオード211、212、221、230、231、234、235が有するn型トランジスタは、オフ状態となる。そうすると、保護ダイオード213、214、220、232、233、236、237を介して、配線215、225、239A、239Bの電位がVddとなる。従って、ノイズ等により電位Vinが電位Vddよりも異常に高くなったとしても、配線215、224、225、239A、239Bの電位は、電位Vddよりも高くなることはない。

一方で、電位Vinが電位Vssよりも低い場合には、保護ダイオード211、212、221、230、231、234、235のゲート電極とソース電極間の電位差Vgs=Vss−Vin>Vthのときに、当該n型トランジスタはオン状態となる。ここでは、Vinが異常に低い場合を想定しているため、n型トランジスタはオンする。このとき、保護ダイオード213、214、220、232、233、236、237が有するn型トランジスタはオフ状態となる。そうすると、保護ダイオード211、212、221、230、231、234、235を介して、配線215、225、239A、239Bの電位がVssとなる。従って、ノイズ等により、電位Vinが電位Vssより異常に低くなったとしても、配線215、225、239A、239Bの電位は、電位Vssよりも低くなることはない。さらに、容量素子222、223は、入力電位Vinが有するパルス状のノイズを鈍らせ、ノイズによる電位の急峻な変化を緩和する働きをする。

なお、電位Vinが、Vss−VthからVdd+Vthの間の場合には、すべての保護ダイオードが有するn型トランジスタがオフ状態となり、電位Vinが電位Voutへ入力される。

以上説明したように保護回路を配置することで、配線215、225、239A、239Bの電位は、概ね電位Vssと電位Vddの間に保たれることになる。従って、配線215、225、239A、239Bがこの範囲から大きく外れる電位となることを防止することができる。つまり、配線215、225、239A、239Bが異常に高い電位または異常に低い電位となることを防止し、当該保護回路の後段の回路が破壊されまたは劣化することを防止し、後段の回路を保護することができる。

さらに、図13(B)に示すように、入力端子に抵抗素子224を有する保護回路を設けることで、信号が入力されていないときに、信号が与えられる全ての配線の電位を、一定(ここでは電位Vss)とすることができる。つまり信号が入力されていないときは、配線同士をショートさせることができるショートリングとしての機能も有する。そのため、配線間に生じる電位差に起因する静電破壊を防止することができる。また、抵抗素子224の抵抗値が配線抵抗に対して十分に大きいので、信号の入力時に、配線に与えられる信号が電位Vssまで降下することを防止することができる。

ここで、一例として、図13(B)の保護ダイオード220及び保護ダイオード221に閾値電圧Vth=0のn型トランジスタを用いた場合について説明する。

まず、Vin>Vddの場合には、保護ダイオード220はVgs=Vin−Vdd>0となり、オンする。保護ダイオード221が有するn型薄膜トランジスタはオフ状態となる。従って、配線225の電位はVddとなり、Vout=Vddとなる。

一方で、Vin<Vssの場合には、保護ダイオード220が有するn型薄膜トランジスタはオフ状態となる。保護ダイオード221が有するn型薄膜トランジスタはVgs=Vss−Vin>0となり、オン状態となる。従って、配線225の電位はVssとなり、Vout=Vssとなる。

このように、Vin<VssまたはVdd<Vinとなる場合であっても、Vss<Vout<Vddの範囲で動作させることができる。従って、Vinが過大な場合または過小な場合であっても、Voutが過大になりまたは過小となることを防止することができる。従って、例えばノイズ等により、電位Vinが電位Vssより低くなる場合であっても、配線225の電位は、電位Vssよりも遙かに低くなることはない。さらに、容量素子222及び容量素子223は、入力電位Vinが有するパルス状のノイズを鈍らせ、電位の急峻な変化を緩和する働きをする。

以上説明したように保護回路を配置することで、配線225の電位は、電位Vssと電位Vddの間に概ね保たれることになる。従って、配線225がこの範囲から大きくはずれた電位となることを防止することができ、当該保護回路の後段の回路(入力部がVoutに電気的に接続された回路)を破壊または劣化から保護することができる。さらに、入力端子に保護回路を設けることで、信号が入力されていないときに、信号が与えられる全ての配線の電位を、一定(ここでは電位Vss)に保つことができる。つまり、信号が入力されていないときは、配線同士をショートさせることができるショートリングとしての機能も有する。そのため、配線間に生じる電位差に起因する静電破壊を防止することができる。また、抵抗素子224の抵抗値が十分に大きいので、信号の入力時には、配線225に与えられる信号の電位の低下を防止できる。

図13(C)に示す保護回路は、保護ダイオード220及び保護ダイオード221を、それぞれ2つのn型トランジスタで代用したものである。

なお、図13(B)及び図13(C)に示す保護回路は、保護ダイオードとしてダイオード接続されたn型トランジスタを用いているが、これに限定されない。

また、図13(D)に示す保護回路は、保護ダイオード230乃至保護ダイオード237と、抵抗素子238と、を有する。抵抗素子238は配線239Aと配線239Bの間に直列に接続されている。保護ダイオード230乃至保護ダイオード233のそれぞれは、ダイオード接続されたn型トランジスタを用いており、保護ダイオード234乃至保護ダイオード237のそれぞれは、ダイオード接続されたn型トランジスタを用いている。

保護ダイオード230と保護ダイオード231は直列に接続されており、一端は電位Vssに保持され、他端は電位Vinの配線239Aに接続されている。保護ダイオード232と保護ダイオード233は直列に接続されており、一端は電位Vddに保持され、他端は電位Vinの配線239Aに接続されている。保護ダイオード234と保護ダイオード235は直列に接続されており、一端は電位Vssに保持され、他端は電位Voutの配線239Bに接続されている。保護ダイオード236と保護ダイオード237は直列に接続されており、一端は電位Vddに保持され、他端は電位Voutの配線239Bに接続されている。

また、図13(E)に示す保護回路は、抵抗素子240と、抵抗素子241と、保護ダイオード242と、を有する。図13(E)では、保護ダイオード242としてダイオード接続されたn型トランジスタを用いているが、これに限定されない。ダイオード接続された複数のトランジスタを用いても良い。抵抗素子240と、抵抗素子241と、保護ダイオード242は、配線243に直列に接続されている。

抵抗素子240及び抵抗素子241によって、配線243の電位の急激な変動を緩和し、半導体素子の劣化または破壊を防止することができる。また、保護ダイオード242によって、電位の変動により配線243に逆方向バイアスの電流が流れることを防止することができる。

なお、図13(A)に示す保護回路は、図13(F)に示す構成に置き換えることも可能である。図15(F)は、図15(A)に示した保護ダイオード211及び保護ダイオード212を保護ダイオード216に、保護ダイオード213及び保護ダイオード214を保護ダイオード217に置き換えた構成を示している。特に、上記実施の形態で説明したダイオードは、耐圧が高いため、図13(F)のような構成を用いることができる。

なお、抵抗素子のみを配線に直列に接続する場合には、配線の電位の急激な変動を緩和し、半導体素子の劣化または破壊を防止することができる。また、保護ダイオードのみを配線に直列に接続する場合、電位の変動により配線に逆方向の電流が流れるのを防ぐことができる。

なお、本発明の一態様である表示装置に設けられる保護回路は図13に示す構成に限定されるものではなく、同様の働きをする回路構成であれば、適宜設計変更が可能である。

(実施の形態9)

本実施の形態では、上記実施の形態にて説明したダイオードを用いて、安定した電源供給を可能とする半導体装置の構成例について図14で説明する。電源線に想定以上の電圧が印加されると、その電源線に接続している回路が損傷される恐れがある。実施の形態8では、主に信号線に対して想定以上の過大な電圧から保護するための構成例について示したが、図14では、電源線に想定以上の電圧が印加されることを防ぐための構成例を示す。

図14(A)は、電位Vssを供給する電源線270と、電位Vddを供給する電源線271の間に、酸化物半導体(OS)を有するn型トランジスタを用いた保護ダイオード251乃至保護ダイオード255、及び保護ダイオード261が接続されている状態を示す回路図である。また、図14(B)は、図14(A)のトランジスタを用いた保護ダイオードの構成を、ダイオードの回路記号で置き換えた図である。

一例として、電位Vssを0Vとし、電位Vddを10Vとし、電源線270と電源線271の電位差が10Vを超える事がないようにする場合について説明する。ここでは、保護ダイオードとして、閾値電圧(Vth)が2Vのn型トランジスタを用いることとする。

図14(A)及び図14(B)において、電位Vddを供給する電源線271に保護ダイオード251のアノード側が接続されている。保護ダイオード251は酸化物半導体(OS)を有するn型トランジスタで構成されており、該n型トランジスタのソース電極及びドレイン電極の一方が、電源線271及び該n型トランジスタのゲート電極と接続され、アノードとして機能する。また、ソース電極及びドレイン電極の他方はカソードとして機能し、保護ダイオード252のアノードに接続されている。

保護ダイオード252は酸化物半導体(OS)を有するn型トランジスタで構成されており、該n型トランジスタのソース電極及びドレイン電極の一方が、保護ダイオード251のカソード及び該n型トランジスタのゲート電極と接続され、アノードとして機能する。また、ソース電極及びドレイン電極の他方はカソードとして機能し、保護ダイオード253のアノードに接続されている。

このようにして、保護ダイオード251乃至保護ダイオード255が直列に接続し、保護ダイオード255のカソードが電位Vssを供給する電源線270に接続される。つまり、電源線270と電源線271の間に、順バイアス方向に保護ダイオードが5個直列に接続されている。

通常、順方向バイアス方向に電圧が印加されるとダイオードに順方向電流が流れ、アノードとカソード間が導通状態となる。本実施の形態では、閾値電圧(Vth)が2Vのn型トランジスタで構成されたダイオードを5個直列に接続しているため、順方向バイアスが2Vの5倍である10Vを超えないと、電源線270と電源線271間が導通状態とならない。しかし、ノイズなどの原因により、電源線270と電源線271間の電位差が10Vを超えると、保護ダイオード251乃至保護ダイオード255が導通状態となり、電位差が10V以下になるまで電源線270と電源線271が短絡状態となる。このようにして、想定以上の電圧が電源線を通して回路に印加され、回路が損傷される事を防ぐことができる。

また、保護ダイオード261を、電源線270と電源線271の間に逆方向バイアスとなるように接続することで、ノイズなどの原因により、電源線270の電位が電源線271より大きくなったときに、電源線270と電源線271を短絡させて電荷を逃がし、電源線に接続されている回路が損傷することを防ぐことができる。

保護ダイオード261は、酸化物半導体(OS)を有するトランジスタであり、大きな逆方向バイアスが印加されても、降伏現象が起きにくい高耐圧ダイオードである。本実施の形態では、電源線270と電源線271の間に保護ダイオード261を一つ配置した例を示しているが、保護ダイオード261を複数直列に配置してもよい。保護ダイオード261をn個直列に配置することで、保護ダイオード一つ当たりに印加される電圧をn分の1とすることができるため、複数直列に配置したダイオード全体を、さらに耐圧特性に優れた一つのダイオードとして機能させることができる。

また、直列接続した保護ダイオード251乃至保護ダイオード255、及び保護ダイオード261は、電源線270と電源線271の間に複数並列に設けてもよい。複数並列に設けることにより、より多くの電流を流すことができるため、電源線270と電源線271の間の電位をより迅速に安定させる事ができる。

なお、端子281を保護ダイオード254と保護ダイオード255の間に設けることで、保護ダイオード255の閾値電圧(Vth)を取り出すことができる。本実施の形態では、保護ダイオード255の閾値電圧(Vth)を2Vとしているため、端子281を2Vの電源線として用いる事ができる。また、端子281を保護ダイオード253と保護ダイオード252の間に設けることで、端子281を6Vの電源線として用いる事ができる。保護ダイオード255の閾値電圧(Vth)と直列接続数を調整することにより、任意の電位を取り出すことができる。

(実施の形態10)

実施の形態8で説明した保護回路を有する表示装置は、電子機器に適用することができる。

実施の形態8の表示装置を表示部に用いた電子機器として、例えば、ビデオカメラ、デジタルカメラなどのカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポなど)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍など)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)などの記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。

図15(A)に示すディスプレイは、筐体300、支持台301および表示部302を含み、入力された様々な情報(静止画、動画、テキスト画像など)を表示部302に表示する機能を有する。なお、図15(A)に示すディスプレイが有する機能はこれに限定されず、例えばスピーカーを具備していてもよいし、情報の表示のみならず入力も可能なタッチパネルであってもよい。

図15(B)に示すテレビジョン装置は、筐体311に表示部312が組み込まれている。表示部312により、映像を表示することが可能である。また、ここでは、壁310に固定して筐体の裏側を支持した構成を示している。

図15(B)に示すテレビジョン装置の操作は、筐体311が備える操作スイッチや、リモコン操作機315により行うことができる。リモコン操作機315が備える操作キー314により、チャンネルや音量の操作を行うことができ、表示部312に表示される映像を操作することができる。また、リモコン操作機315に、当該リモコン操作機315から出力する情報を表示する表示部313を設ける構成としてもよい。

なお、図15(B)に示すテレビジョン装置は、受信機やモデムなどを備えた構成とするとよい。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

図15(C)に示すコンピュータは、本体320、筐体321、表示部322、キーボード323、外部接続ポート324およびポインティングデバイス325を含み、様々な情報(静止画、動画、テキスト画像など)を表示部322に表示する機能を有する。なお、図15(C)に示すコンピュータが有する機能はこれに限定されず、例えば、情報の表示のみならず入力も可能なタッチパネルであってもよい。

本実施の形態で説明したように、本発明の一態様であるダイオードなどの非線形素子を電子機器に用いることができる。