JP5593373B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP5593373B2 JP5593373B2 JP2012287062A JP2012287062A JP5593373B2 JP 5593373 B2 JP5593373 B2 JP 5593373B2 JP 2012287062 A JP2012287062 A JP 2012287062A JP 2012287062 A JP2012287062 A JP 2012287062A JP 5593373 B2 JP5593373 B2 JP 5593373B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel electrode

- electrode

- strip

- liquid crystal

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 122

- 239000000758 substrate Substances 0.000 claims description 47

- 210000002858 crystal cell Anatomy 0.000 claims description 16

- 210000004027 cell Anatomy 0.000 claims description 12

- 239000010410 layer Substances 0.000 description 24

- 238000005516 engineering process Methods 0.000 description 11

- 239000010409 thin film Substances 0.000 description 7

- 230000001154 acute effect Effects 0.000 description 5

- 230000005684 electric field Effects 0.000 description 5

- 239000011241 protective layer Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 238000000034 method Methods 0.000 description 3

- 239000004988 Nematic liquid crystal Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1337—Surface-induced orientation of the liquid crystal molecules, e.g. by alignment layers

- G02F1/133707—Structures for producing distorted electric fields, e.g. bumps, protrusions, recesses, slits in pixel electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134318—Electrodes characterised by their geometrical arrangement having a patterned common electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

Landscapes

- Liquid Crystal (AREA)

Description

置されることにより、その間にセルギャップが定義される。液晶層は、第1の基板と第2の基板との間におけるセルギャップに配置され、且つこの液晶層は、複数の液晶セルが定

義されている。画素アレイは、複数の画素を有する。これらの画素は、第1の基板に形成されている。各画素は、対応する液晶セルに接続され、且つ第1の画素電極と、第2の画

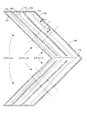

素電極とを含む。第1の画素電極は、複数の第1の画素電極ストリップを有する。第2の画素電極は、複数の第2の画素電極ストリップを有する。これらの第1の画素電極ストリップと第2の画素電極ストリップとは、交互に並ぶように配置されることにより、その間に複数の電極間隔が定義され、各電極間隔は、隣り合った第1の画素電極ストリップと第2の画素電極ストリップとによって定義されており、且つ所定の幅を有する。基準線が2つの隣り合った第1の画素電極ストリップと第2の画素電極ストリップとの間に位置され、隣り合った第1の画素電極ストリップと第2の画素電極ストリップとは、基準線に対して対称となり、各電極間隔の所定の幅は、隣り合った第1の画素電極ストリップと第2の画素電極ストリップとの間おける基準線の延設方向に沿って変化する。一実施形態では、各画素は、対向電極を含んでもよい。この対向電極は、第2の基板上に形成されるとともに、第2の画素電極と電気的に接続される。もう1つの実施形態では、対向電極は、第1の画素電極と電気的に接続されてもよい。別の実施形態では、交流電圧又は直流電圧を対向電極に印加してもよい。

の間にセルギャップが定義される。液晶層は、第1の基板と第2の基板との間におけるセルギャップに配置され、且つこの液晶層は、複数の液晶セルが定義されている。画素アレ

イは、複数の画素を有する。これらの画素は、第1の基板に形成されている。各画素は、対応する液晶セルに接続され、且つ第1の画素電極と、第2の画素電極とを含む。第1の画素電極は、複数の第1の画素電極ストリップを有する。第2の画素電極は、複数の第2

の画素電極ストリップを有する。第1の画素電極ストリップと第2の画素電極ストリップとは、交互に並ぶように配置されることにより、その間に複数の電極間隔が定義されている。各電極間隔は、隣り合った第1の画素電極ストリップと第2の画素電極ストリップとによって定義されており、且つ所定の幅を有し、各電極間隔のうち少なくとも1つの幅は、その他の電極間隔の幅と異なっている。一実施形態では、各画素は、対向電極を含んでもよい。この対向電極は、第2の基板上に形成されている。一実施形態では、対向電極は、第2の画素電極と電気的に接続されている。もう1つの実施形態では、対向電極は、第1の画素電極と電気的に接続されてもよい。別の実施形態では、交流電圧又は直流電圧を対向電極に印加してもよい。

110 第1の基板

120 第2の基板

130 液晶層

132 液晶

140 絶縁層

150 保護層

162,163,164 第2の画素電極ストリップ

172,173 第1の画素電極ストリップ

260 第2の画素電極

261,262,263,264,265,261,262a,263a,264a,265a 第2の画素電極ストリップ

266 頂部

266a 底部

270 第1の画素電極

271,272,273,274,271a,272a,273a,274a 第1の画素電極ストリップ

275 リッジ部

301 第1の方向

302 第2の方向

360 第2の画素電極

361,362,363,364,365 第2の画素電極ストリップ

370 第1の画素電極

371,372,373,374 第1の画素電極ストリップ

401 第1の方向

402 第2の方向

460 第2の画素電極

461,462,463,464 第2の画素電極ストリップ

470 第1の画素電極

471,472,473 第1の画素電極ストリップ

560 第2の画素電極

561,562,563,564,565 第2の画素電極ストリップ

570 第1の画素電極

571,572,573,574 第1の画素電極ストリップ

660 第2の画素電極

661,662,663,664,665,666,667,668 第2の画素電極ストリップ

670 第1の画素電極

671,672,673,675,676,677 第1の画素電極ストリップ

760 第2の画素電極

761,762,763,764,765,766,767,768 第2の画素電極ストリップ

770 第1の画素電極

771,772,773,775,776,777 第1の画素電極ストリップ

860 第2の画素電極

861,862,863,864,865,866,867,868,861a、862a、863a、864a、865a、866a、867a、868a 第2の画素電極ストリップ

869b 側部

869a 底部

869 頂部

870 第1の画素電極

871,872,873,874,875,876,877,878,871a,872a,873a,874a,875a,876a,877a,878a 第1の画素電極ストリップ

879 リッジ部

879b 側部

970 第1の画素電極

971,972,973 第1の画素電極ストリップ

960 第2の画素電極

961,962 第2の画素電極ストリップ

1000 液晶表示装置

1010 第1の基板

1020 第2の基板

1030 液晶層

1032 液晶

1040 絶縁層

1050 保護層

1062,1063,1064 第2の画素電極ストリップ

1072,1073 第1の画素電極ストリップ

1080 対向電極

1110 垂直画素構造

1120 ゲート線

1130 信号線

1140 薄膜トランジスタ

1161 第2の画素電極ストリップ

1171 第1の画素電極ストリップ

1210 垂直画素構造

1220 ゲート線

1230 信号線

1240 薄膜トランジスタ

1261 第2の画素電極ストリップ

1271 第1の画素電極ストリップ

A,B,C,D セグメント

d 距離

P,P1,P2,P3,P4,P5,P6,P7,P8 電極間隔

R 基準線

S 傾斜部

a1 第1の角度

a2 第2の角度

θ,θ1,θ2 鋭角

Claims (3)

- 液晶表示装置であって、

互いに対向して配置されて間にセルギャップを定義する第1の基板及び第2の基板と、

前記セルギャップ内に配置され、複数の液晶セルが定義されている液晶層と、

前記第1の基板に形成され且つ各々が対応する前記液晶セルと接続している複数の画素を有する画素アレイと、

を含み、

各画素は、複数の第1の画素電極ストリップを有する第1の画素電極と、複数の第2の画素電極ストリップを有する第2の画素電極とを含み、

前記複数の第1の画素電極ストリップと前記複数の第2の画素電極ストリップとが交互に並ぶように配置されて間に複数の電極間隔を定義し、

各電極間隔は、隣り合った前記第1の画素電極ストリップと前記第2の画素電極ストリップとによって定義されて所定の幅を有しており、

隣り合った前記第1の画素電極ストリップと前記第2の画素電極ストリップとの間に基準線が位置され、隣り合った前記第1の画素電極ストリップと前記第2の画素電極ストリップとは前記基準線に対して対称となり、

前記第1の画素電極ストリップ及び前記第2の画素電極ストリップは、鋸歯状のストリップであり、

前記所定の幅は、隣り合った前記第1の画素電極ストリップと前記第2の画素電極ストリップとの間における前記基準線の延伸方向に沿って変化することを特徴とする液晶表示装置。 - 前記各画素が対向電極を更に含み、前記対向電極は、前記第2の基板上に形成され、前記第1の画素電極と、前記第2の画素電極と、交流電圧又は直流電圧と電気的に接続されることを特徴とする請求項1に記載の液晶表示装置。

- 複数のゲート線と、複数の信号線とを更に含み、前記複数のゲート線と前記複数の信号線は、前記複数の画素に対応して電気的に接続されることを特徴とする請求項1に記載の液晶表示装置。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/346,899 | 2012-01-10 | ||

| US13/346,899 US20130176523A1 (en) | 2012-01-10 | 2012-01-10 | Pixel structure for liquid crystal display device |

| TW101128791A TWI484269B (zh) | 2012-01-10 | 2012-08-09 | 液晶顯示裝置 |

| TW101128791 | 2012-08-09 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013142900A JP2013142900A (ja) | 2013-07-22 |

| JP5593373B2 true JP5593373B2 (ja) | 2014-09-24 |

Family

ID=49039467

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012287062A Active JP5593373B2 (ja) | 2012-01-10 | 2012-12-28 | 液晶表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5593373B2 (ja) |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102449545A (zh) * | 2009-05-28 | 2012-05-09 | 夏普株式会社 | 液晶显示装置 |

| WO2011040080A1 (ja) * | 2009-09-30 | 2011-04-07 | シャープ株式会社 | 液晶表示装置 |

-

2012

- 2012-12-28 JP JP2012287062A patent/JP5593373B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013142900A (ja) | 2013-07-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI484269B (zh) | 液晶顯示裝置 | |

| US9885926B2 (en) | Slit electrode, array substrate and display device | |

| US9116568B2 (en) | Liquid crystal display device | |

| CN104834142A (zh) | 像素结构、阵列基板及显示装置 | |

| US20140210868A1 (en) | Liquid crystal display device and method of driving the same | |

| US8854587B2 (en) | Liquid crystal display device | |

| WO2019041801A1 (zh) | 一种显示基板、显示面板及显示装置 | |

| US9176347B2 (en) | Lateral electric field type liquid crystal display device having non-uniform spacings between two electrodes | |

| TW201341913A (zh) | 液晶顯示面板 | |

| JP2014206639A (ja) | 液晶表示装置 | |

| US9966027B2 (en) | Array substrate combining plane electric field and fringe electric field, driving method thereof and display device | |

| US9772529B2 (en) | Liquid crystal display | |

| JP7118722B2 (ja) | 液晶表示装置 | |

| CN109416490B (zh) | 液晶显示面板、液晶显示装置及操作液晶显示面板的方法 | |

| US9812079B2 (en) | Array substrate, driving method thereof and display apparatus | |

| US9097952B2 (en) | Array substrate and liquid crystal display device | |

| JP5593373B2 (ja) | 液晶表示装置 | |

| JP2015102566A (ja) | 表示素子 | |

| US9541802B2 (en) | TFT array substrate used in a dual domain liquid crystal display panel and a dual-domain liquid crystal display panel | |

| US20160327839A1 (en) | Pixel unit array and liquid crystal display device | |

| US10437111B2 (en) | Pixel electrode and array substrate | |

| TW201405223A (zh) | 液晶顯示面板 | |

| JP2010139776A (ja) | 液晶表示装置 | |

| US20130176524A1 (en) | Pixel structure for liquid crystal display device | |

| US9766513B2 (en) | Pixel array structure and liquid crystal display panel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131210 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140307 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140320 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140410 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140708 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140804 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5593373 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |