JP5561801B2 - 集積回路デバイス及びその形成方法 - Google Patents

集積回路デバイス及びその形成方法 Download PDFInfo

- Publication number

- JP5561801B2 JP5561801B2 JP2012513085A JP2012513085A JP5561801B2 JP 5561801 B2 JP5561801 B2 JP 5561801B2 JP 2012513085 A JP2012513085 A JP 2012513085A JP 2012513085 A JP2012513085 A JP 2012513085A JP 5561801 B2 JP5561801 B2 JP 5561801B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- well

- conductivity type

- semiconductor layer

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 51

- 239000004065 semiconductor Substances 0.000 claims description 97

- 238000009792 diffusion process Methods 0.000 claims description 96

- 239000000758 substrate Substances 0.000 claims description 83

- 238000002955 isolation Methods 0.000 claims description 78

- 239000004020 conductor Substances 0.000 claims description 56

- 230000005669 field effect Effects 0.000 claims description 43

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 23

- 229910052710 silicon Inorganic materials 0.000 claims description 23

- 239000010703 silicon Substances 0.000 claims description 23

- 230000003068 static effect Effects 0.000 claims description 17

- 229910021332 silicide Inorganic materials 0.000 claims description 15

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 15

- 239000010410 layer Substances 0.000 description 144

- 239000000463 material Substances 0.000 description 16

- 238000002513 implantation Methods 0.000 description 14

- 235000012431 wafers Nutrition 0.000 description 14

- 230000008569 process Effects 0.000 description 13

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000002019 doping agent Substances 0.000 description 6

- 230000003466 anti-cipated effect Effects 0.000 description 4

- 238000003491 array Methods 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 239000011231 conductive filler Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823481—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type isolation region manufacturing related aspects, e.g. to avoid interaction of isolation region with adjacent structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823493—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the wells or tubs, e.g. twin tubs, high energy well implants, buried implanted layers for lateral isolation [BILLI]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

- H01L27/092—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate complementary MIS field-effect transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- General Engineering & Computer Science (AREA)

- Semiconductor Memories (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

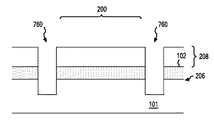

101:基板

102、103:ウェル

104、105:デバイス

110:SRAMセル

110a−110d:メモリセル

111、111a、111b、112:ノード

121a:第1のデバイス(第1のプルアップ電界効果トランジスタ)

121b:第2のデバイス(第2のプルアップ電界効果トランジスタ)

122:プルダウン電界効果トランジスタ(FET)

123:パスゲート電界効果トランジスタ(FET)

150、160:深いトレンチ分離(DTI)領域

200:デバイス領域

205:浮動ウェル部分

206:ウェル102の最大深さ

208:半導体層

221:第1の拡散領域(第1のソース領域)

222:第2の拡散領域(第2のソース領域)

223:第3の拡散領域(ドープ領域)

250:接合部

260:導体層

280:共用コンタクト

760:トレンチ

901、902:ゲート構造体

Claims (11)

- 第1の導電型を有する基板と、

前記第1の導電型とは異なる第2の導電型を有する、前記基板内のウェルと、

前記ウェル上の半導体層であって、

各々が前記第1の導電型を有する、第1のデバイスの第1の拡散領域と、第2のデバイスの第2の拡散領域とを含むデバイス領域と、

前記第1の拡散領域と前記第2の拡散領域との間にそれらに接触するように横方向に配置された、前記第2の導電型を有し、前記ウェルに至るまで垂直方向にさらに延びる第3の拡散領域と、を含む半導体層と、

前記第1の拡散領域、前記第3の拡散領域、及び前記第2の拡散領域の上に横方向に延びてそれらに接触する、前記半導体層の上の導体層と、

前記半導体層を貫通して前記基板内に前記ウェルの最大深さより下まで延びる深いトレンチ分離領域であって、前記デバイス領域を画定する、トレンチ分離領域と、

電源電圧に接続する前記導体層上のコンタクトと、

を含む集積回路デバイス構造体。 - 前記第1の導電型はP型導電率を含み、前記第2の導電率はN型導電率を含む、請求項1に記載の集積回路デバイス構造体。

- 前記導体層はシリサイド層またはエピタキシャル・シリコン層を含む、請求項1に記載の集積回路デバイス構造体。

- 第1の導電型を有する基板と、

前記第1の導電型とは異なる第2の導電型を有する、前記基板内のウェルと、

前記ウェル上の半導体層であって、

各々が前記第1の導電型を有する、第1のメモリセルの第1のプルアップ電界効果トランジスタの第1のソース領域と、第2のメモリセルの第2のプルアップ電界効果トランジスタの第2のソース領域とを含むデバイス領域と、

前記第1のソース領域と前記第2のソース領域との間にそれらに接触するように横方向に配置された、前記第2の導電型を有し、前記ウェルに至るまで垂直方向にさらに延びるドープ領域と、を含む半導体層と、

前記第1のソース領域、前記ドープ領域及び前記第2のソース領域の上に横方向に延びてそれらに接触する、前記半導体層の上の導体層と、

前記半導体層を貫通して前記基板内の前記ウェルの最大深さより下まで延びる深いトレンチ分離領域であって、前記デバイス領域を画定する、トレンチ分離領域と、

電源電圧に接続する前記導体層上のコンタクトと、

を含むスタティック・ランダム・アクセス・メモリ(SRAM)アレイ構造体。 - 前記第1の導電型はP型導電率を含み、前記第2の導電率はN型導電率を含む、請求項4に記載のスタティック・ランダム・アクセス・メモリ(SRAM)アレイ構造体。

- 前記導体層はシリサイド層またはエピタキシャル・シリコン層を含む、請求項4に記載のスタティック・ランダム・アクセス・メモリ(SRAM)アレイ構造体。

- P−基板と、

前記基板内のN+ウェルと、

前記基板上の半導体層と、

前記半導体層を貫通して前記基板内に前記N+ウェルの最大深さより下まで延びて、前記アレイ内のメモリセルのデバイス領域を画定する深いトレンチ分離領域であって、

前記デバイス領域の1つは、前記N+ウェルの領域の上の半導体層の部分を含み、

前記半導体層の前記部分は、

第1のメモリセルの第1のP型プルアップ電界効果トランジスタの第1のP型ソース領域と、

前記第1のメモリセルに隣接する第2のメモリセルの第2のP型プルアップ電界効果トランジスタの第2のP型ソース領域と、

前記第1のP型ソース領域と前記第2のP型ソース領域との間に横方向にそれらに接するように配置された、前記N+ウェルの前記部分に至るまで垂直方向にさらに延びるN型ドープ領域と、を含む、深いトレンチ分離領域と、

前記第1のP型ソース領域、前記N型ドープ領域及び前記第2のP型ソース領域の上を横方向に延びてそれらに接触する、前記半導体層上の導体層と、

正の電源電圧(Vdd)に接続される、前記導体層上のコンタクトと、

を含む、スタティック・ランダム・アクセス・メモリ(SRAM)アレイ構造体。 - 集積回路デバイス構造体を形成する方法であって、

第1の導電型を有する基板を準備することと、

前記基板内に、前記第1の導電型とは異なる第2の導電型を有するウェルを形成することと、

前記ウェルを形成することの後で、前記基板上に半導体層を形成することと、

前記ウェル、第1のデバイスの第1の拡散領域及び第2のデバイスの第2の拡散領域の間に接合部を形成することと、を含み、

前記接合部を形成することは、

前記半導体層内に、前記第1の拡散領域及び前記第2の拡散領域を、前記第1の拡散領域及び前記第2の拡散領域が前記第1の導電型を有するように形成することと、

前記半導体層内に、前記第1の拡散領域と前記第2の拡散領域との間にそれらに接するように横方向に配置された第3の拡散領域を、前記第3の拡散領域が前記第2の導電型を有し、前記ウェルに至るまで垂直方向に延びるように形成することと、

前記半導体層上に、前記第1の拡散領域、前記第3の拡散領域及び前記第2の拡散領域の上に横方向に延びてそれらに接触するように導体層を形成することとを含み、さらに、前記方法は、

前記接合部を形成することの前に、前記基板内で前記ウェルの最大深さより下まで延びて前記半導体層内にデバイス領域を画定する深いトレンチ分離領域を形成することと、

前記導体層に対するコンタクトを形成して前記コンタクトを電源電圧に電気的に接続することと、を含み、

前記デバイス領域の1つは、前記ウェルの上に前記第1のデバイス及び前記第2のデバイスのための指定領域を含む、方法。 - 前記第1の導電型はP型導電率を含み、前記第2の導電率はN型導電率を含む、請求項8に記載の方法。

- 前記導体層を形成することは、シリサイド層またはエピタキシャル・シリコン層を形成することを含む、請求項8に記載の方法。

- スタティック・ランダム・アクセス・メモリ(SRAM)アレイ構造体を形成する方法であって、

第1の導電型を有する基板を準備することと、

前記基板内に、前記第1の導電型とは異なる第2の導電型を有するウェルを形成することと、

前記ウェルを形成することの後で、前記基板上に半導体層を形成することと、

前記ウェル、第1のメモリセルの第1のプルアップ電界効果トランジスタの第1のソース領域及び第2のメモリセルの第2のプルアップ電界効果トランジスタの第2のソース領域の間に接合部を形成することと、を含み、

前記接合部を形成することは、

前記半導体層内に、前記第1のプルアップ電界効果トランジスタの前記第1のソース領域及び前記第2のプルアップ電界効果トランジスタの前記第2のソース領域を、前記第1のソース領域及び前記第2のソース領域が前記第1の導電型を有するように形成することと、

前記半導体層内に、前記第1のソース領域と前記第2のソース領域との間に横方向にそれらに接するように配置されたドープ領域を、前記ドープ領域が前記第2の導電型を有し、前記ウェルに至るまで垂直方向に延びるように形成することと、

前記半導体層上に、前記第1のソース領域、前記ドープ領域及び前記第2のソース領域の上に横方向に延びてそれらに接触するように、導体層を形成することとを含み、さらに、前記方法は、

前記接合部を形成することの前に、前記基板内で前記ウェルの最大深さより下まで延びて前記半導体層内にデバイス領域を画定する深いトレンチ分離領域を形成することと、

前記導体層に対するコンタクトを形成して前記コンタクトを電源電圧に電気的に接続することと、を含み、

前記デバイス領域の1つは、前記ウェルの上に、前記第1及び前記第2のプルアップ電界効果トランジスタのための指定領域を含む、方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/473,324 US7902608B2 (en) | 2009-05-28 | 2009-05-28 | Integrated circuit device with deep trench isolation regions for all inter-well and intra-well isolation and with a shared contact to a junction between adjacent device diffusion regions and an underlying floating well section |

| US12/473,324 | 2009-05-28 | ||

| PCT/US2010/033469 WO2010138278A2 (en) | 2009-05-28 | 2010-05-04 | Integrated circuit device with deep trench isolation regions for all inter-well and intra-well isolation and with a shared contact to a junction between adjacent device diffusion regions and an underlying floating well section |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012528484A JP2012528484A (ja) | 2012-11-12 |

| JP2012528484A5 JP2012528484A5 (ja) | 2013-10-10 |

| JP5561801B2 true JP5561801B2 (ja) | 2014-07-30 |

Family

ID=43219260

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012513085A Expired - Fee Related JP5561801B2 (ja) | 2009-05-28 | 2010-05-04 | 集積回路デバイス及びその形成方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7902608B2 (ja) |

| EP (1) | EP2401761A4 (ja) |

| JP (1) | JP5561801B2 (ja) |

| CN (1) | CN102428556B (ja) |

| CA (1) | CA2757776A1 (ja) |

| TW (1) | TW201104840A (ja) |

| WO (1) | WO2010138278A2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8183639B2 (en) * | 2010-10-07 | 2012-05-22 | Freescale Semiconductor, Inc. | Dual port static random access memory cell layout |

| KR20130126948A (ko) * | 2010-12-15 | 2013-11-21 | 이피션트 파워 컨버젼 코퍼레이션 | 후면 격리를 갖는 반도체 소자 |

| JP5891678B2 (ja) * | 2011-09-22 | 2016-03-23 | ソニー株式会社 | 電気光学装置および表示装置 |

| US10529866B2 (en) | 2012-05-30 | 2020-01-07 | X-Fab Semiconductor Foundries Gmbh | Semiconductor device |

| US9214378B2 (en) | 2012-06-29 | 2015-12-15 | International Business Machines Corporation | Undercut insulating regions for silicon-on-insulator device |

| US9478736B2 (en) * | 2013-03-15 | 2016-10-25 | International Business Machines Corporation | Structure and fabrication of memory array with epitaxially grown memory elements and line-space patterns |

| US9105691B2 (en) * | 2013-04-09 | 2015-08-11 | International Business Machines Corporation | Contact isolation scheme for thin buried oxide substrate devices |

| US11037937B2 (en) * | 2019-11-20 | 2021-06-15 | Globalfoundries U.S. Inc. | SRAM bit cells formed with dummy structures |

Family Cites Families (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE1764241C3 (de) * | 1968-04-30 | 1978-09-07 | Ibm Deutschland Gmbh, 7000 Stuttgart | Monolithisch integrierte Halbleiterschaltung |

| JPS553691A (en) * | 1978-06-13 | 1980-01-11 | Ibm | Integrated circuit having junction field effect transistor |

| US4395812A (en) * | 1980-02-04 | 1983-08-02 | Ibm Corporation | Forming an integrated circuit |

| IT1213260B (it) * | 1984-12-18 | 1989-12-14 | Sgs Thomson Microelectronics | Circuito a ponte di transistori mos di potenza a canale n integrato eprocedimento per la sua fabbricazione. |

| US5156989A (en) * | 1988-11-08 | 1992-10-20 | Siliconix, Incorporated | Complementary, isolated DMOS IC technology |

| US4994406A (en) | 1989-11-03 | 1991-02-19 | Motorola Inc. | Method of fabricating semiconductor devices having deep and shallow isolation structures |

| JPH03192763A (ja) * | 1989-12-21 | 1991-08-22 | Nec Corp | 半導体記憶装置 |

| JPH0831954A (ja) * | 1994-07-20 | 1996-02-02 | Hitachi Ltd | 半導体集積回路装置 |

| JP3329640B2 (ja) * | 1995-10-10 | 2002-09-30 | 株式会社東芝 | 半導体装置の製造方法 |

| US5692281A (en) | 1995-10-19 | 1997-12-02 | International Business Machines Corporation | Method for making a dual trench capacitor structure |

| US5937288A (en) * | 1997-06-30 | 1999-08-10 | Siemens Aktiengesellschaft | CMOS integrated circuits with reduced substrate defects |

| US5930633A (en) | 1997-07-23 | 1999-07-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated butt-contact process in shallow trench isolation |

| US5843816A (en) | 1997-07-28 | 1998-12-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated self-aligned butt contact process flow and structure for six transistor full complementary metal oxide semiconductor static random access memory cell |

| US6057186A (en) | 1998-07-31 | 2000-05-02 | Taiwan Semiconductor Manufacturing Company | Method for improving the butted contact resistance of an SRAM by double Vcc implantation |

| TW400614B (en) | 1998-11-06 | 2000-08-01 | United Microelectronics Corp | The manufacture method of Shallow Trench Isolation(STI) |

| US6624459B1 (en) * | 2000-04-12 | 2003-09-23 | International Business Machines Corp. | Silicon on insulator field effect transistors having shared body contact |

| US6303413B1 (en) | 2000-05-03 | 2001-10-16 | Maxim Integrated Products, Inc. | Method of forming a shallow and deep trench isolation (SDTI) suitable for silicon on insulator (SOI) substrates |

| US6297127B1 (en) | 2000-06-22 | 2001-10-02 | International Business Machines Corporation | Self-aligned deep trench isolation to shallow trench isolation |

| US6667226B2 (en) | 2000-12-22 | 2003-12-23 | Texas Instruments Incorporated | Method and system for integrating shallow trench and deep trench isolation structures in a semiconductor device |

| US6661049B2 (en) | 2001-09-06 | 2003-12-09 | Taiwan Semiconductor Manufacturing Co., Ltd | Microelectronic capacitor structure embedded within microelectronic isolation region |

| US6885080B2 (en) | 2002-02-22 | 2005-04-26 | International Business Machines Corporation | Deep trench isolation of embedded DRAM for improved latch-up immunity |

| US8089129B2 (en) * | 2002-08-14 | 2012-01-03 | Advanced Analogic Technologies, Inc. | Isolated CMOS transistors |

| US6900091B2 (en) * | 2002-08-14 | 2005-05-31 | Advanced Analogic Technologies, Inc. | Isolated complementary MOS devices in epi-less substrate |

| US6833602B1 (en) | 2002-09-06 | 2004-12-21 | Lattice Semiconductor Corporation | Device having electrically isolated low voltage and high voltage regions and process for fabricating the device |

| US6864151B2 (en) | 2003-07-09 | 2005-03-08 | Infineon Technologies Ag | Method of forming shallow trench isolation using deep trench isolation |

| KR100539243B1 (ko) * | 2003-10-04 | 2005-12-27 | 삼성전자주식회사 | 부분 에스오아이 기판에 구현된 에스램 소자 |

| US7042044B2 (en) | 2004-02-18 | 2006-05-09 | Koucheng Wu | Nor-type channel-program channel-erase contactless flash memory on SOI |

| US7019348B2 (en) | 2004-02-26 | 2006-03-28 | Taiwan Semiconductor Manufacturing Co., Ltd. | Embedded semiconductor product with dual depth isolation regions |

| CN1329994C (zh) * | 2004-03-23 | 2007-08-01 | 联华电子股份有限公司 | 深沟渠式电容以及单晶体管静态随机存取内存单元的结构 |

| US7009237B2 (en) | 2004-05-06 | 2006-03-07 | International Business Machines Corporation | Out of the box vertical transistor for eDRAM on SOI |

| US7282771B2 (en) | 2005-01-25 | 2007-10-16 | International Business Machines Corporation | Structure and method for latchup suppression |

| EP1722421A3 (fr) * | 2005-05-13 | 2007-04-18 | Stmicroelectronics Sa | Photodiode intégrée de type à substrat flottant |

| US7663237B2 (en) | 2005-12-27 | 2010-02-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Butted contact structure |

| US7494850B2 (en) | 2006-02-15 | 2009-02-24 | International Business Machines Corporation | Ultra-thin logic and backgated ultra-thin SRAM |

| DE102006013203B3 (de) * | 2006-03-22 | 2008-01-10 | Infineon Technologies Ag | Integrierte Halbleiteranordnung mit Rückstromkomplex zur Verringerung eines Substratstroms und Verfahren zu deren Herstellung |

| US7586147B2 (en) | 2006-04-17 | 2009-09-08 | Taiwan Semiconductor Manufacturing Co. Ltd. | Butted source contact and well strap |

| US7737526B2 (en) * | 2007-03-28 | 2010-06-15 | Advanced Analogic Technologies, Inc. | Isolated trench MOSFET in epi-less semiconductor sustrate |

| US11126608B2 (en) | 2018-01-31 | 2021-09-21 | Salesforce.Com, Inc. | Techniques and architectures for partition mapping in a multi-node computing environment |

-

2009

- 2009-05-28 US US12/473,324 patent/US7902608B2/en active Active

-

2010

- 2010-05-04 WO PCT/US2010/033469 patent/WO2010138278A2/en active Application Filing

- 2010-05-04 JP JP2012513085A patent/JP5561801B2/ja not_active Expired - Fee Related

- 2010-05-04 CN CN201080021329.6A patent/CN102428556B/zh active Active

- 2010-05-04 EP EP10780978A patent/EP2401761A4/en not_active Withdrawn

- 2010-05-04 CA CA2757776A patent/CA2757776A1/en not_active Abandoned

- 2010-05-10 TW TW099114867A patent/TW201104840A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| EP2401761A2 (en) | 2012-01-04 |

| US7902608B2 (en) | 2011-03-08 |

| CN102428556B (zh) | 2014-03-12 |

| US20100301419A1 (en) | 2010-12-02 |

| JP2012528484A (ja) | 2012-11-12 |

| CA2757776A1 (en) | 2010-12-02 |

| WO2010138278A3 (en) | 2011-02-03 |

| CN102428556A (zh) | 2012-04-25 |

| EP2401761A4 (en) | 2012-04-25 |

| TW201104840A (en) | 2011-02-01 |

| WO2010138278A2 (en) | 2010-12-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5561801B2 (ja) | 集積回路デバイス及びその形成方法 | |

| US11152393B2 (en) | Semiconductor device and method of manufacturing the same | |

| US9780097B2 (en) | Dual-port SRAM devices and methods of manufacturing the same | |

| US8624295B2 (en) | SRAM devices utilizing strained-channel transistors and methods of manufacture | |

| US7435634B2 (en) | Methods of forming semiconductor devices having stacked transistors | |

| CN111758164B (zh) | 三维存储器件和用于形成其的方法 | |

| EP0809302B1 (en) | CMOS structure in isolated wells with merged depletion regions and method of making same | |

| JP3965064B2 (ja) | ボディ・コンタクトを有する集積回路の形成方法 | |

| US9570465B2 (en) | Dual STI integrated circuit including FDSOI transistors and method for manufacturing the same | |

| CN103715236A (zh) | 鳍结构上的保护环 | |

| KR100593739B1 (ko) | 바디-소스 접속을 갖는 모스 전계효과 트랜지스터 및 그제조방법 | |

| CN105723501A (zh) | 异质层器件 | |

| US6633067B2 (en) | Compact SOI body contact link | |

| US7338867B2 (en) | Semiconductor device having contact pads and method for manufacturing the same | |

| CN109524355B (zh) | 一种半导体器件的结构和形成方法 | |

| JP2009004800A (ja) | 半導体集積回路装置 | |

| US20090269897A1 (en) | Methods of fabricating dual-depth trench isolation regions for a memory cell | |

| US10062702B2 (en) | Mask read-only memory device | |

| JP2006140539A (ja) | 半導体集積回路装置の製造方法 | |

| US20090267156A1 (en) | Device structures including dual-depth trench isolation regions and design structures for a static random access memory | |

| CN109545802B (zh) | 一种绝缘体上半导体器件结构和形成方法 | |

| KR100663349B1 (ko) | 선택적 에피택시얼 성장 기술 및 부분 평탄화 기술을사용하여 박막 트랜지스터들을 갖는 반도체 집적회로를제조하는 방법들 및 그에 의해 제조된 반도체 집적회로들 | |

| JP2010232361A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130116 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20130801 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130805 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20130805 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130801 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20130820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130917 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140416 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140520 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20140523 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140605 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5561801 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |