JP5444698B2 - Data processing apparatus and program - Google Patents

Data processing apparatus and program Download PDFInfo

- Publication number

- JP5444698B2 JP5444698B2 JP2008299322A JP2008299322A JP5444698B2 JP 5444698 B2 JP5444698 B2 JP 5444698B2 JP 2008299322 A JP2008299322 A JP 2008299322A JP 2008299322 A JP2008299322 A JP 2008299322A JP 5444698 B2 JP5444698 B2 JP 5444698B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- power supply

- hibernation

- storage means

- area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Cash Registers Or Receiving Machines (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

本発明は、データ処理装置及びプログラムに関する。 The present invention relates to a data processing apparatus and a program.

従来、ECR(電子レジスタ)等の売上データ処理装置では、主電源遮断時のシステムの動作状態を示すデータを電池でバックアップされた揮発性メモリに保存しておくことで、停電時や誤操作による主電源の遮断時でもすぐに電源遮断前の動作状態で起動できるようにしている。しかし、近年、売上データ処理装置の高機能化が進み、それに伴いメモリも大容量となっている。そのため、店舗の夏季休業等により主電源の遮断状態が長時間続いた場合に備えて大容量のバックアップ電池が必要となっている。 Conventionally, in sales data processing devices such as ECR (electronic registers), data indicating the operating state of the system when the main power supply is shut down is stored in a volatile memory backed up by a battery, which can be used mainly when a power failure occurs. Even when the power is cut off, it can be started immediately in the operating state before the power is cut off. In recent years, however, sales data processing devices have become more sophisticated, and the memory has also increased in capacity. Therefore, a large-capacity backup battery is required in case the main power supply is shut off for a long time due to a summer holiday of the store.

例えば、特許文献1には、商用電源の瞬断あるいは停電時において中央処理装置と揮発性メモリのみをバッテリでバックアップし、消費電力の大きい周辺装置はバックアップしないようにした商品情報ターミナルが記載されている。

しかしながら、特許文献1の技術においては、主電源である商用電源の瞬断あるいは停電時のバッテリの容量は低減できるが、店舗の夏季休業等により主電源の遮断状態が長時間続く場合には、大容量のバッテリが必要となる。

However, in the technology of

一方、主電源が遮断された際に、補助電源の給電により揮発性メモリのデータを不揮発性記憶手段に退避させることも考えられるが、この場合、前回の主電源の遮断時に不揮発性記憶手段に退避されたデータが残っているため、まず不揮発性記憶手段に記憶されたデータの消去をしてから揮発性メモリのデータの退避を行わなければならない。そのため、主電源を遮断してから動作が完全に停止するまでに時間がかかり、補助電源の消耗が大きい。 On the other hand, when the main power is shut off, it is conceivable to save the data in the volatile memory to the nonvolatile storage means by supplying power from the auxiliary power supply. Since the saved data remains, the data stored in the nonvolatile storage means must first be erased before the data in the volatile memory is saved. For this reason, it takes time until the operation is completely stopped after the main power supply is shut off, and the auxiliary power supply is greatly consumed.

本発明の課題は、主電源遮断時のデータのバックアップに使用される補助電源の消耗を低減させることである。 An object of the present invention is to reduce consumption of an auxiliary power source used for data backup when a main power source is shut off.

上記課題を解決するため、請求項1に記載の発明のデータ処理装置は、

主電源からの給電によりデータを記憶する揮発性記憶手段と、

前記主電源の遮断時に前記揮発性記憶手段に記憶されているデータを退避するための不揮発性記憶手段と、

入力手段に対する入力処理が行われているか否かを判別し、入力処理が行われていない場合は、予め決められたデータ単位で前記不揮発性記憶手段に記憶されているデータの消去処理を実行し、前記主電源が遮断された際に、前記不揮発性記憶手段の最終領域まで前記データの消去処理が完了しているか否かを判別し、前記データの消去処理が完了していない場合は、補助電源からの給電により前記不揮発性記憶手段に記憶されている未消去の残存データの消去処理を実行し前記揮発性記憶手段に記憶されているデータを前記不揮発性記憶手段に退避させる制御手段と、

を備える。

In order to solve the above problem, a data processing device according to

Volatile storage means for storing data by power supply from the main power supply;

Nonvolatile storage means for saving data stored in the volatile storage means when the main power supply is shut off;

It is determined whether or not the input process is being performed on the input means. If the input process is not being performed, the data stored in the non-volatile storage means is erased in a predetermined data unit. When the main power is cut off, it is determined whether or not the data erasing process has been completed up to the final area of the nonvolatile storage means. If the data erasing process has not been completed, Control means for executing an erasing process of unerased residual data stored in the nonvolatile storage means by power supply from a power source and saving the data stored in the volatile storage means to the nonvolatile storage means;

Is provided.

請求項2に記載の発明は、請求項1に記載の発明において、

前記不揮発性記憶手段を複数備え、

前記制御手段は、前記揮発性記憶手段に記憶されているデータを前記複数の不揮発性記憶手段に分散して退避させる。

The invention according to claim 2 is the invention according to

A plurality of the nonvolatile storage means;

The control unit distributes and stores data stored in the volatile storage unit to the plurality of nonvolatile storage units.

請求項3に記載の発明は、請求項1又は2に記載の発明において、

前記補助電源からの電源の供給と遮断とを切り替える切り替え手段を備え、

前記制御手段は、前記主電源が遮断された際に前記切り替え手段により前記補助電源に給電を行わせ、前記不揮発性記憶手段へのデータ退避の終了後、前記切り替え手段により前記補助電源を遮断させる。

The invention according to claim 3 is the invention according to

Comprising a switching means for switching between supply and interruption of power from the auxiliary power supply,

The control means causes the switching means to supply power to the auxiliary power supply when the main power is cut off, and causes the switching means to cut off the auxiliary power supply after data saving to the nonvolatile storage means is completed. .

請求項4に記載の発明のプログラムは、

主電源からの給電によりデータを記憶する揮発性記憶手段と、前記主電源の遮断時に前記揮発性記憶手段に記憶されているデータを退避するための不揮発性記憶手段と、を備えるデータ処理装置に用いられるコンピュータを、

入力手段に対する入力処理が行われているか否かを判別し、入力処理が行われていない場合は、予め決められたデータ単位で前記不揮発性記憶手段に記憶されているデータの消去処理を実行し、前記主電源が遮断された際に、前記不揮発性記憶手段の最終領域まで前記データの消去処理が完了しているか否かを判別し、前記データの消去処理が完了していない場合は、補助電源からの給電により前記不揮発性記憶手段に記憶されている未消去の残存データの消去処理を実行し前記揮発性記憶手段に記憶されているデータを前記不揮発性記憶手段に退避させる制御手段、

として機能させる。

The program of the invention according to claim 4 is:

A data processing apparatus comprising: volatile storage means for storing data by power supply from a main power supply; and nonvolatile storage means for saving data stored in the volatile storage means when the main power supply is shut off The computer used,

It is determined whether or not the input process is being performed on the input means. If the input process is not being performed, the data stored in the non-volatile storage means is erased in a predetermined data unit. When the main power is cut off, it is determined whether or not the data erasing process has been completed up to the final area of the nonvolatile storage means. If the data erasing process has not been completed, Control means for executing erasure processing of unerased residual data stored in the nonvolatile storage means by power supply from a power source and saving the data stored in the volatile storage means to the nonvolatile storage means;

To function as.

本発明によれば、主電源遮断時のデータのバックアップに使用される補助電源の消耗を低減させることが可能となる。 According to the present invention, it is possible to reduce the consumption of the auxiliary power source used for data backup when the main power source is shut off.

(実施形態1)

まず、本発明の実施形態1について説明する。

図1に、実施形態1におけるECR1の機能構成例を示す。

ECR1は、店舗に設けられ、オペレータの操作に基づいて商品登録処理(取引された日時、商品名、商品の売上個数、売上金額等の売上データ、担当者等の登録処理)、点検処理、精算処理、店舗内の売上集計等を行う売上データ処理装置である。ECR1としては、例えば、電子レジスタ等が適用可能である。

(Embodiment 1)

First,

FIG. 1 shows a functional configuration example of the ECR 1 in the first embodiment.

ECR1 is provided in the store, and product registration processing (transaction date and time, product name, number of products sold, sales data such as sales amount, registration processing of person in charge, etc.), inspection processing, and settlement based on operator operations This is a sales data processing device that performs processing, total sales in a store, and the like. As ECR1, for example, an electronic register or the like is applicable.

図1に示すように、ECR1は、CPU10と、RTC11と、プログラム格納メモリ12と、メインメモリ13と、ハイバネーション用メモリ14と、メイン表示装置151と、サブ表示装置152と、LED16と、印字装置17と、入力装置18と、ストレージI/F19と、通信部20と、を備えて構成され、各部はバス21を介して接続されて構成されている。

As shown in FIG. 1, the ECR 1 includes a

CPU(Central Processing Unit)10は、ECR1の各部を集中制御する制御手段

である。CPU10は、プログラム格納メモリ12に記憶されている各種プログラムをメインメモリ13に展開し、メインメモリ13に展開されたプログラムとの協働により、ECR1全体の制御及び各種処理を実行する。

A CPU (Central Processing Unit) 10 is control means for centrally controlling each part of the

例えば、CPU10は、AC電源状態監視回路34(図3参照)からAC電源供給を通知する信号が入力されると、プログラム格納メモリ12に記憶されている起動処理プログラム及び終了処理プログラムをメインメモリ13の起動処理・終了処理用ワークエリア131(図2参照)に読み出して、読み出した起動処理プログラムとの協働により後述する起動処理を実行する。

For example, when a signal for notifying AC power supply is input from the AC power supply state monitoring circuit 34 (see FIG. 3), the

起動処理によりECR1が起動されると、CPU10は、メインメモリ13に記憶されているECR制御プログラムとの協働により後述するECR制御処理を実行し、ECR1の各部を制御する。具体的には、入力装置18からの入力があると、CPU10は、入力に応じた処理プログラムを起動させ、商品登録処理、点検処理、精算処理、店舗内の売上集計処理等を行う。入力装置18からの入力がない、即ち他に実行すべき処理のない空き時間には、後述する書込みエリア事前消去処理を実行する。なお、「他に実行すべき処理」には、実行すべき処理があるか否かを判断して実行する「ECR制御処理」は含まない。

When the ECR 1 is activated by the activation process, the

また、CPU10は、動作中にAC電源状態監視回路34からAC電源遮断を通知する信号が入力されると、メインメモリ13に記憶されている終了処理プログラムとの協働により、サスペンド処理(第1の退避処理)、ハイバネーション処理(第2の退避処理)を含む終了処理を実行する。

Further, when a signal for notifying AC power supply interruption is input from the AC power supply

ここで、本実施形態において、サスペンド処理とは、AC電源31の遮断時にCPU10のシステム動作状態を示すデータ(プログラムカウンタ(PC)、スタックポインタ(SP)、レジスタ、システムデータ等)を揮発性のメインメモリ13に退避する処理をいう。ハイバネーション処理とは、メインメモリ13に記憶されているシステム動作状態を示すデータ等を不揮発性のハイバネーション用メモリ14に退避する処理をいう。

Here, in the present embodiment, the suspend process refers to volatile data (program counter (PC), stack pointer (SP), register, system data, etc.) indicating the system operation state of the

ハイバネーション処理中にAC電源状態監視回路34からAC電源供給を通知する信号が入力されると、CPU10は、ハイバネーション処理を中断させて起動処理を実行し、メインメモリ13に退避されているシステム動作状態を示すデータに基づいてAC電源遮断前の状態にシステムを復帰させる。

When a signal for notifying the AC power supply is input from the AC power

RTC(Real Time Clock)11は、計時回路を内蔵し、現在時刻及び現在日付を計時

してCPU10に出力する。RTC11は、RTC用バックアップ電源111が備えられており(図3参照)、AC電源31及びバックアップ用電源32の何れからも電源が供給されない状態でも動作可能となっている。

An RTC (Real Time Clock) 11 has a built-in clock circuit, clocks the current time and the current date, and outputs them to the

プログラム格納メモリ12は、不揮発性のROM(Read Only Memory)等により構成され、図2に示すように、ECR1で実行可能な各種プログラムやECR1の固有データ(例えば、ECR1のMACアドレス、タッチパネルキャリブレーションデータ等)を記憶する。

The

メインメモリ13は、CPU10によって実行される各種プログラム及びこれらプログラムに係る各種データ等を記憶する揮発性記憶手段である。

メインメモリ13は、図2に示すように、起動処理・終了処理用ワークエリア131、サスペンド用エリア132、コピー領域133、システムデータ領域134、設定データ領域135、ユーザデータ領域136を有している。

The

As shown in FIG. 2, the

起動処理・終了処理用ワークエリア131は、AC電源投入時にCPU10によりプログラム格納メモリ12から読み出された起動処理プログラム、終了処理プログラム(サブルーチンの処理を含む)を記憶するとともに、これらのプログラムが動作するためのワークエリアである。起動処理・終了処理用ワークエリア131は、消去ブロック番号領域131aを有している。消去ブロック番号領域131aは、ハイバネーション用メモリ14において最終に消去されたブロックのブロック番号(1〜n)を記憶するための領域である。ブロックとは、ハイバネーション用メモリ14において一度にデータ書込み及び消去可能なデータ単位を示す。なお、「0」は、ハイバネーション用メモリ14が未消去状態であることを示す。 サスペンド用エリア132は、サスペンド処理において、CPU10のシステム動作状態を示すデータ(プログラムカウンタ(PC)、スタックポインタ(SP)、レジスタ、システムデータ等)を退避するための領域である。

コピー領域133は、プログラム格納メモリ12に記憶されているプログラムのコピーを書込むための領域である。

システムデータ領域134は、スタック、変数やオペレーティングシステム(OS)のシステムデータを記憶する領域である。

設定データ領域135は、入力装置18を介して設定された周辺機器(メイン表示装置151、サブ表示装置152、印字装置17、入力装置18等)に関する各種設定データを記憶する領域である。

ユーザデータ領域136は、入力装置18を介して入力された売上データ、メイン表示装置151で表示中の表示データ、印字装置17に印字させる印字データ等のユーザデータを記憶する領域である。

The start process / end

The

The

The setting

The

ハイバネーション用メモリ14は、フラッシュメモリ等の不揮発性メモリにより構成され、AC電源31の遮断時にメインメモリ13に記憶されているデータを退避するための不揮発性記憶手段である。ハイバネーション用メモリ14は、n個のブロックのデータ書込みが可能である。

また、本実施の形態において、ハイバネーション用メモリ14は、CPU10から書込み指示されたデータの上位Bitを格納するためのハイバネーション用メモリ14a、CPU10から書込み指示されたデータの下位Bitを格納するためのハイバネーション用メモリ14bを備えて構成されている。ハイバネーション処理におけるデータの書込み速度及び消去速度を向上させるためである。

The

In the present embodiment, the

ハイバネーション用メモリ14は、図2に示すように、ヘッダ領域141、バックアップ領域142、チェックサム格納領域143を有している。ヘッダ領域141は、ハイバネーション処理が完了したことを示すハイバネーション完了フラグを設定するためのハイバネーション完了フラグ領域141aを有する領域である。バックアップ領域142は、ハイバネーション処理において、メインメモリ13の起動処理・終了処理用ワークエリア131以外の領域のデータを退避するための領域である。チェックサム格納領域143は、ハイバネーション処理において算出されたチェックサムを書込むための領域である。

As shown in FIG. 2, the

メイン表示装置151、サブ表示装置152は、LCD(Liquid Crystal Display)や有機EL(Electro-Luminescence)ディスプレイ等により構成され、CPU10から入力される表示信号の指示に従って、各種画面を表示する。メイン表示装置151は、オペレータ側に向けて設けられた表示装置であり、サブ表示装置152は、顧客側に向けて設けられた表示装置である。

The

LED(Light Emitting Diode)16は、CPU10から入力される指示信号に応じて駆動され、点灯、点滅する。

An LED (Light Emitting Diode) 16 is driven in response to an instruction signal input from the

印字装置17は、例えば、サーマルプリンタ(感熱式プリンタ)であり、レシート用、ジャーナル用のロール紙(感熱紙)を有し、CPU10から入力される指示信号に従って、各ロール紙に対して金額等のデータをプリントアウトする。

The

入力装置18は、電源キー、カーソルキー、文字、数字入力キーや、INITキー、FCキー等の各種機能キー等を備えたレジ用のキーボードを含む構成とし、オペレータによる各キーの操作信号をCPU10に出力する。また、入力装置18は、メイン表示装置151の画面上に設けられたタッチパネルを含む。タッチパネルは、メイン表示装置151の上面を覆うように設置されており、オペレータの指などを用いた操作によって押圧入力された所望の入力位置を検出し、その検出信号をCPU10に出力する。また、入力装置18は、商品に設けられたバーコードを読み取るバーコードリーダやバーコードスキャナ等を備える。

The

ストレージI/F19は、CF(Compact Flash)カード、SDカード(Secure Digital Card)等の外部ストレージ19aを接続可能であり、外部ストレージ19aとのデータの入出力を行う。

The storage I /

通信部20は、LAN(Local Area Network)アダプタやルータ等により構成され、LANやインターネット等の通信ネットワークを介してサーバ100等の外部機器とデータ送受信を行う。

The

図3に、ECR1における電源系の要部構成例を示す。

図3に示す電源生成回路33は、AC電源(主電源)31、及び、スイッチ35を介して補助電源としてのバックアップ用電源(充電池)32に接続されている。電源生成回路33は、AC電源31から入力されたAC(交流)電源電力をDC(直流)電源電力に変換し、図1に示す各部にそれぞれ供給する。また、電源生成回路33は、スイッチ35を介してバックアップ用電源32から入力された電源電力をCPU10、RTC11、プログラム格納メモリ12、メインメモリ13及びハイバネーション用メモリ14a、14b、LED16に供給する。

AC電源状態監視回路34は、AC電源31の電源状態を監視する電源監視手段であり、AC電源31から電源が供給されている間は、AC電源供給を通知する信号(HIGH信号)をCPU10に出力し、AC電源31からの電源が遮断されている間は、AC電源遮断を通知する信号(LOW信号)をCPU10に出力する。

スイッチ35は、CPU10からのバックアップ用電源ON/OFFスイッチ切替制御信号に基づいて、バックアップ電源32のON/OFF(電源の供給/遮断)を切り替える切り替え手段である。

FIG. 3 shows a configuration example of a main part of the power supply system in ECR1.

3 is connected to an AC power source (main power source) 31 and a backup power source (rechargeable battery) 32 as an auxiliary power source via a

The AC power supply

The

このように、AC電源31からの電源が供給状態である場合、電源生成回路33によりECR1の各部にAC電源31からの電源が供給される。AC電源31が遮断されると、CPU10からの制御に基づいて、CPU10、RTC11、プログラム格納メモリ12、メインメモリ13及びハイバネーション用メモリ14a、14b、LED16のみにバックアップ用電源32からの電源が供給される。このように構成することで、バックアップ用電源32の消耗を必要最低限に抑えることができる。なお、AC電源31遮断後一定時間T内は回路的に電源が保持されている。この一定時間内にCPU10はバックアップ用電源32をONに切り替え、CPU動作電源、メモリ動作電源を維持する。

As described above, when the power supply from the

次に、実施形態1におけるECR1の主要な動作についてフローチャートを参照して詳細に説明する。なお、実施形態1においては、シングルタスクで各種処理が実行される場合の一例について説明する。

Next, main operations of the

まず、ECR1の起動後にCPU10により実行されるECR制御処理について説明する。図4に、ECR制御処理のフローチャートを示す。ECR制御処理は、CPU10とECR制御プログラムとの協働によるソフトウエア処理により実現される。

First, an ECR control process executed by the

まず、起動処理・終了処理用ワークエリア131の消去ブロック番号領域131aに0が設定される(ステップS1)。

First, 0 is set in the erase

次いで、入力装置18から入力がされたか否かが判断され(ステップS2)、入力装置18から入力がされてないと判断されると(ステップS2;NO)、書込みエリア事前消去処理が実行される(ステップS3)。 Next, it is determined whether or not an input has been made from the input device 18 (step S2). If it is determined that no input has been made from the input device 18 (step S2; NO), a write area pre-erasing process is executed. (Step S3).

図5に、ステップS3においてCPU10により実行される書込みエリア事前消去処理を示す。書込みエリア事前消去処理は、CPU10と書込みエリア事前消去処理プログラムとの協働により実行される。

FIG. 5 shows the write area pre-erasing process executed by the

ここで、書込みエリア事前消去処理は、ハイバネーション用メモリ14a、14bに記憶されているデータを消去する処理である。ハイバネーション用メモリ14a、14bには、上述したように、AC電源31の遮断時にメインメモリ13に記憶されているデータが退避される(書込まれる)。このデータ退避は、後述する終了処理において、バックアップ用電源32の給電により行われる。しかし、ハイバネーション用メモリ14a、14bにデータを書込む前に、まず前回のAC遮断時に書込まれたデータをハイバネーション用メモリ14a、14bから消去する必要がある。この処理を全て終了処理において行うと、AC電源31が遮断されてから動作が完全に停止するまでに時間がかかり、バックアップ用電源32が消耗する。そこで、CPU10において他に実行すべき処理のない、即ち、商品登録処理や他の処理が要求又は実行されていない「処理の空き時間」に書込みエリア事前消去処理を実行することで、AC電源31の遮断時におけるハイバネーション用メモリ14a、14bからのデータ消去にかかる時間を短縮し、バックアップ用電源32の消耗を低減する。即ち、本実施形態において、「処理の空き時間」とは、CPU10が商品登録処理や他の処理を要求又は実行していない時間をいう。

Here, the write area pre-erasing process is a process of erasing data stored in the

書込みエリア事前消去処理においては、まず、メインメモリ13の消去ブロック番号領域131aに記憶されている番号が取得される(ステップS101)。次いで、取得された番号がハイバネーション用メモリ14a、14bの最終ブロック番号nであるか否かが判断される(ステップS102)。

In the write area pre-erasure process, first, the number stored in the erase

取得された番号が最終ブロック番号nではないと判断されると(ステップS102;NO)、取得された番号の次の番号のブロックのデータ消去がハイバネーション用メモリ14a、14bに指示される(ステップS103)。そして、処理は、ハイバネーション用メモリ14a、14bからのブロック消去完了の通知待ち状態となる。ハイバネーション用メモリ14a、14bにおいては、1ブロック分のデータ消去が終了すると、CPU10にブロック消去完了が通知される。

If it is determined that the acquired number is not the final block number n (step S102; NO), the

1ブロック分のデータ消去が完了した旨がハイバネーション用メモリ14a、14bから通知されると(ステップS104;YES)、データ消去されたブロックのブロック番号が消去ブロック番号領域131aに書込まれ(ステップS105)、処理は図4のステップS2に戻る。

When it is notified from the

一方、ステップS102において、取得された番号が最終ブロック番号nであると判断されると(ステップS102;YES)、書込みエリア事前消去処理は終了し、図4のステップS2に戻る。 On the other hand, if it is determined in step S102 that the acquired number is the final block number n (step S102; YES), the write area pre-erasing process is terminated, and the process returns to step S2 in FIG.

図4のステップS2において、入力装置18から入力がされたと判断されると(ステップS2;YES)、当該入力が商品登録の指示であるか否か判断される(ステップS4)。当該入力が商品登録の指示であると判断されると(ステップS4;YES)、商品登録処理が実行される(ステップS5)。商品登録処理は、商品が取引された日時、商品名、商品の売上個数、売上金額等の売上データ、担当者等をユーザデータ領域136に登録する処理である。そして、商品名、売上(購入)個数、売上(購入)金額、お預かり金額、返金額等が印字装置17によりレシートに印字され(ステップS6)、処理はステップS8に移行する。

If it is determined in step S2 of FIG. 4 that input has been made from the input device 18 (step S2; YES), it is determined whether or not the input is an instruction to register a product (step S4). If it is determined that the input is a product registration instruction (step S4; YES), a product registration process is executed (step S5). The product registration process is a process for registering the date and time when the product was traded, the product name, the sales volume of the product, the sales data such as the sales amount, the person in charge, etc. in the

入力装置18からの入力が商品登録の指示ではないと判断されると(ステップS4;NO)、入力に応じた他の処理が実行され(ステップS7)、処理はステップS8に移行する。

If it is determined that the input from the

ステップS8においては、AC電源監視回路34から入力される通知信号に基づいてAC電源31の電源状態が判断される。AC電源31が供給状態であると判断されると(ステップS8;NO)、処理はステップS2に戻る。AC電源31が遮断状態であると判断されると(ステップS8;YES)、終了処理が実行され(ステップS9)、ECR制御処理は終了する。

In step S <b> 8, the power state of the

図6に、図4のステップS9においてCPU10により実行される終了処理のフローチャートを示す。当該処理は、CPU10と終了処理プログラムとの協働により実行される。

FIG. 6 shows a flowchart of the end process executed by the

まず、サスペンド処理(第1の退避処理)が実行され、CPU10に記憶されているスタックポインタ、プログラムカウンタ、レジスタ、システムデータ等がメインメモリ13のサスペンド用エリア132に退避される(ステップS201)。

First, a suspend process (first save process) is executed, and the stack pointer, program counter, register, system data, etc. stored in the

次いで、バックアップ用電源ON/OFFスイッチ切替制御信号によりスイッチ35がONに切り替えられることにより、バックアップ用電源32がONに切り替えられる(ステップS202)。

Next, the

次いで、ハイバネーション処理(第2の退避処理)が実行され、メインメモリ13における起動処理・終了処理用ワークエリア131以外の領域のデータがハイバネーション用メモリ14に退避(バックアップ)される(ステップS203)。なお、ハイバネーション処理実行中にAC電源監視回路34によりAC電源供給を通知する信号が入力されると、CPU10により本処理は中断され、図11a〜図11bに示す起動処理が実行される。

Next, hibernation processing (second saving processing) is executed, and data in an area other than the activation / termination

図7に、図6のステップS203においてCPU10により実行されるハイバネーション処理のフローチャートを示す。当該処理は、CPU10とハイバネーション処理プログラムとの協働によるソフトウエア処理により実現される。

FIG. 7 shows a flowchart of the hibernation process executed by the

ハイバネーション処理においては、まず、LED16の点滅が開始される(ステップS301)。次いで、書込みエリア消去処理が実行される(ステップS302)。

図8に、書込みエリア消去処理のフローチャートを示す。

図8に示すように、書込みエリア消去処理においては、まず、消去ブロック番号領域131aに記憶されている番号が取得される(ステップS1000)。次いで、取得された番号がハイバネーション用メモリ14a、14bの最終ブロック番号nであるか否かが判断される(ステップS1001)。取得された番号が最終ブロック番号nであると判断されると(ステップS1001;YES)、書込みエリア消去処理は終了し、処理は図7のステップS303に移行する。

In the hibernation process, first, the

FIG. 8 shows a flowchart of the write area erasing process.

As shown in FIG. 8, in the write area erase process, first, the number stored in the erase

取得された番号が最終ブロック番号nではないと判断されると(ステップS1001;NO)、次の番号のブロックのデータ消去がハイバネーション用メモリ14a、14bに指示される(ステップS1002)。

If it is determined that the acquired number is not the final block number n (step S1001; NO), data deletion of the next numbered block is instructed to the

次いで、AC電源状態監視回路34から入力される信号が監視され、AC電源31の電源状態が判断される(ステップS1003)。AC電源31が遮断状態であると判断されると(ステップS1003;AC電源遮断状態)、 ハイバネーション用メモリ14a、14bにおいて、1ブロックの消去が完了したか否かが判断される。ここで、ハイバネーション用メモリ14a、14bにおいては、1ブロック分のデータ消去が終了すると、CPU10にブロック消去完了が通知される。1ブロックの消去が完了していないと判断されると(ステップS1004;NO)、処理はステップS1003に戻る。

Next, the signal input from the AC power supply

1ブロックの消去が完了したと判断されると(ステップS1004;YES)、ハイバネーション用メモリ14a、14bの全領域の消去が完了したか否かが判断され、完了していないと判断されると(ステップS1005;NO)、処理はステップS1002に戻り、次の番号の1ブロックについての消去が実行される。ハイバネーション用メモリ14a、14bの全領域の消去が完了したと判断されると(ステップS1005;YES)、書込みエリア消去処理は終了し、処理は図7のステップS303に移行する。

If it is determined that the erasure of one block has been completed (step S1004; YES), it is determined whether or not the erasure of all areas of the

一方、ステップS1003において、AC電源31が供給状態であると判断されると(ステップS1003;AC電源供給状態)、スイッチ35によりバックアップ用電源32がOFFに切り替えられ(ステップS1006)、本処理は中断され、図11a〜図11bに示す起動処理(ハイバネーション中断リスタート)に移行する。

On the other hand, when it is determined in step S1003 that the

図7のステップS303においては、書込み処理が実行される。

図9に、書込み処理のフローチャートを示す。

図9に示すように、書込み処理においては、まず、退避対象のデータ、即ち、メインメモリ13の起動処理・終了処理用ワークエリア131以外の領域に記憶されているデータがハイバネーション用メモリ14a、14bに1ブロック分ずつ転送され、1ブロック分のデータ書込みが指示される(ステップS2001)。ハイバネーション用メモリ14aには、データの上位Bit(例えば、8Bitデータであれば上位4Bit)が1ブロック分転送され、ハイバネーション用メモリ14bには、データの下位Bit(例えば、8Bitデータであれば下位4Bit)が1ブロック分転送される。

In step S303 in FIG. 7, a writing process is executed.

FIG. 9 shows a flowchart of the writing process.

As shown in FIG. 9, in the writing process, first, data to be saved, that is, data stored in an area other than the start / end

次いで、AC電源状態監視回路34から入力される信号が監視され、AC電源31の電源状態が判断される(ステップS2002)。AC電源31が遮断状態であると判断されると(ステップS2002;AC電源遮断状態)、 ハイバネーション用メモリ14a、14bにおいて、1ブロックの書込みが完了したか否かが判断される(ステップS2003)。ここで、ハイバネーション用メモリ14a、14bにおいては、1ブロック分のデータ書込みが終了すると、CPU10にブロック書込み完了が通知される。1ブロックの書込みが完了していないと判断されると(ステップS2003;NO)、処理はステップS2002に戻る。

Next, the signal input from the AC power supply

1ブロックの書込みが完了したと判断されると(ステップS2003;YES)、メインメモリ13の起動処理・終了処理用ワークエリア131以外の全領域のデータの書込みが完了したか否かが判断され、完了していないと判断されると(ステップS2004;NO)、処理はステップS2001に戻り、次のブロックについての書込みが実行される。メインメモリ13の起動処理・終了処理用ワークエリア131以外の全領域のデータの書込みが完了したと判断されると(ステップS2004;YES)、処理は図7のステップS304に移行する。上記書込み処理によりハイバネーション用メモリ14a、14bに書込まれたデータをバックアップデータとよぶ。

If it is determined that writing of one block is completed (step S2003; YES), it is determined whether writing of data in all areas other than the activation / end

一方、ステップS2002において、AC電源31が供給状態であると判断されると(ステップS2002;AC電源供給状態)、スイッチ35によりバックアップ用電源32がOFFに切り替えられ(ステップS2005)、本処理は中断され、図11a〜図11bに示す起動処理(ハイバネーション中断リスタート)に移行する。

On the other hand, when it is determined in step S2002 that the

図7のステップS304においては、書込み内容保証処理が実行される。

書込み内容保証処理は、メインメモリ13における退避対象となったデータとハイバネーション用メモリ14に退避されたデータの整合性を確認するための処理である。

In step S304 of FIG. 7, a write content guarantee process is executed.

The written content guarantee process is a process for confirming the consistency between the data to be saved in the

図10に、書込み内容保証処理のフローチャートを示す。

図10に示すように、書込み内容保証処理においては、まず、メインメモリ13に記憶されているハイバネーション用メモリ14a、14bへの退避対象となったデータ、具体的には、起動処理・終了処理用ワークエリア131以外の領域に書込まれたデータと、ハイバネーション用メモリ14a、14bに退避されたデータのベリファイ処理(誤り検査)が実行される(ステップS3001)。なお、ベリファイ処理により誤りがあった場合は、ハイバネーション処理を再実行することが好ましい。

FIG. 10 shows a flowchart of the write content guarantee process.

As shown in FIG. 10, in the written content guarantee processing, first, the data to be saved in the

次いで、メインメモリ13上における退避対象となったデータのチェックサム(合計値)が算出され(ステップS3002)、算出されたチェックサムがハイバネーション用メモリ14a、14bのチェックサム格納領域143に書込まれる(ステップS3003)。そして、ハイバネーション用メモリ14a、14bのハイバネーション完了フラグ領域141aにハイバネーション完了フラグONが設定され(ステップS3004)、処理は図7のステップS305に移行する。

Next, a checksum (total value) of data to be saved on the

図7のステップS305においては、LED16の点滅が停止され(ステップS305)、ハイバネーション処理は終了し、処理は図6のステップS204に移行する。

In step S305 in FIG. 7, the blinking of the

図6のステップS204においては、スイッチ35によりバックアップ用電源32がOFFに切り替えられ、終了処理は終了する。

In step S204 of FIG. 6, the

バックアップ用電源32がOFFに切り替えられた後、AC電源31が遮断状態から供給状態となると、CPU10により、プログラム格納メモリ12の起動処理プログラム及び終了処理プログラムがメインメモリ13の起動処理・終了処理用ワークエリア131に読み出される。そして、図11a〜図11bに示す起動処理が実行される。

After the

図11a〜図11bに、起動処理のフローチャートを示す。当該処理は、CPU10と起動処理プログラムとの協働によるソフトウエア処理により実現される。ここで、起動処理は図11a〜図11bに示す「リセットスタート」の位置から開始されるが、ハイバネーション処理中断時においては、ハイバネーション処理プログラムによって図11aに示す「ハイバネーション中断リスタート」の位置への移行が指示されているため、「ハイバネーション中断リスタート」の位置から処理が開始される。

11a to 11b show a flowchart of the activation process. This processing is realized by software processing through cooperation between the

「リセットスタート」から処理が開始された場合、まず、システム初期化処理が実行される(ステップS10)。システム初期化処理とは、CPU10がこれから使用するシステム環境を認識し、システムを確立させるための処理である。例えば、どのようなメモリが接続されているかをCPU10が認識する処理等が挙げられる。

次いで、リセットスタートであることを示すスタート情報がメインメモリ13の起動処理・終了処理用ワークエリア131に設定され(ステップS11)、処理はステップS14に移行する。

When the process is started from “reset start”, first, a system initialization process is executed (step S10). The system initialization process is a process for the

Next, start information indicating a reset start is set in the

「ハイバネーション中断リスタート」から処理が開始された場合、まず、ハイバネーション用システム初期化処理が実行される(ステップS12)。ハイバネーション処理を中断して起動処理が開始された場合にはCPU10は動作中であるので、システム初期化処理の全てを行う必要はない。そこで、ステップS12においては、例えば、CPU10内のキャッシュ情報の初期化等、一部の初期化処理が行われる。

次いで、ハイバネーション中断リスタートであることを示すスタート情報がメインメモリ13の起動処理・終了処理用ワークエリア131に設定され(ステップS13)、処理はステップS14に移行する。

When the process is started from “hibernation interruption restart”, a hibernation system initialization process is first executed (step S12). When the hibernation process is interrupted and the startup process is started, the

Next, start information indicating that the hibernation interruption restart is set in the

ステップS14においては、メイン表示装置151、サブ表示装置152、印字装置17、入力装置18等の周辺機器のドライバが初期化される(ステップS14)。

In step S14, drivers for peripheral devices such as the

次いで、入力装置18のINITキーが押下されたか否かが判断される(ステップS15)。ここで、INITキー(イニシャルキー)は、ECR1の設置の際にディーラーが使用するキーであり、メインメモリ13上の起動処理・終了処理用ワークエリア131以外の領域のデータ、即ち、設定データやユーザデータを含む全てのデータを初期化することを指示するためのキーである。入力装置18の電源キーがOFFされた後、INITキーを押しながら電源キーがONに切り替えられると、INITキーが有効となる。即ち、INITキーが押下されるタイミングでは、ほとんどの場合、ハイバネーション処理中断後のリスタートとなる。

Next, it is determined whether or not the INIT key of the

INITキーが押下された場合(ステップS15;YES)、処理は図11bのステップS35に移行し、プログラム格納メモリ12のプログラムに誤りがないかチェックが行われる。チェック結果がOKである場合(ステップS35;OK)、プログラム格納メモリ12のプログラムがメインメモリ13のコピー領域133にコピーされ(ステップS36)、ECR1がINIT状態にて起動され(ステップS37)、本処理は終了する。INIT状態にて起動とは、メインメモリ13から起動処理・終了処理用ワークエリア131以外の領域のデータ、即ち、サスペンド用エリア132、システムデータ領域134、設定データ領域135、ユーザデータ領域136のデータが消去された後に起動されることを意味する。起動後は、図4に示すECR制御処理が実行される。チェック結果がNGである場合(ステップS35;NG)、システムエラーが発生したことを示すシステムエラーメッセージ、例えば「システムエラー」という文字列がメイン表示装置151に表示され(ステップS38)、本処理は終了する。

If the INIT key has been pressed (step S15; YES), the process proceeds to step S35 in FIG. 11b, and a check is made to see if there is an error in the

INITキーが押下されていない場合(ステップS15;NO)、FCキーが押下されたか否かが判断される(ステップS16)。ここで、FCキー(フラグクリアキー)は、メインメモリ13上の起動処理・終了処理用ワークエリア131以外のデータのうち設定データを残して初期化することを指示するためのキーである。入力装置18の電源キーがOFFされた後、FCキーを押しながら電源キーがONに切り替えられると、FCキーが有効となる。即ち、FCキーが押下されるタイミングでは、ほとんどの場合、ハイバネーション処理中断後のリスタートとなる。FCキーが押下されていない場合(ステップS16;NO)、処理はステップS18に移行する。FCキーが押下されている場合(ステップS16;YES)、FCキー検知済みを示すフラグがメインメモリ13上の起動処理・終了処理用ワークエリア131に設定され(ステップS17)、処理はステップS18に移行する。

If the INIT key has not been pressed (step S15; NO), it is determined whether or not the FC key has been pressed (step S16). Here, the FC key (flag clear key) is a key for instructing to leave the setting data among the data other than the

ステップS18においては、ハイバネーション処理中断後のリスタートであるか否かが判断される。具体的に、起動処理・終了処理用ワークエリア131に設定されているスタート情報が参照され、設定されているスタート情報がハイバネーション中断リスタートであることを示す情報である場合は、ハイバネーション中断リスタートであると判断される。設定されているスタート情報がリセットスタートであることを示す情報である場合は、ハイバネーション中断リスタートではないと判断される。ハイバネーション処理中断後のリスタートであると判断されると(ステップS18;YES)、処理は図11bのステップS23に移行する。即ち、ステップS19〜S22の処理がスキップされる。ハイバネーション処理中断後のリスタートである場合、メインメモリ13にAC電源31遮断前のメインメモリ13上のデータがそのまま残されているので、ハイバネーション用メモリ14からデータを復帰させる必要はない。

In step S18, it is determined whether or not the restart is after the hibernation process is interrupted. Specifically, when the start information set in the

ハイバネーション処理中断後のリスタートではないと判断されると(ステップS18;NO)、ハイバネーション用メモリ14のハイバネーション完了フラグ領域141aが参照される。ハイバネーション完了フラグがONに設定されている場合(ステップS19;YES)、チェックサムの検証が行われる(ステップS20)。即ち、チェックサム格納領域143に記憶されているチェックサムとバックアップ領域142に記憶されているデータの合計値とが一致するか否かの検証が行われる。チェックサムの検証結果がOKである場合(ステップS20;OK)、ハイバネーション用メモリ14のバックアップ領域142に記憶されているバックアップデータがメインメモリ13に書き戻される(ステップS21)。

If it is determined that the restart is not after the hibernation process is interrupted (step S18; NO), the hibernation

次いで、メインメモリ13に書き戻されたプログラムに誤りがないかチェックが行われる(ステップS22)。チェック結果がOKである場合(ステップS22;OK)、FCキーが検知済みであるか否かが判断される(図11bのステップS23)。FCキーが検知済みではないと判断されると(ステップS23;NO)、サスペンド用エリア132上のプログラムカウンタ、スタックポインタ、レジスタ、システムデータ等がCPU10に書き戻される(ステップS24)。また、周辺機器がAC電源遮断前の状態へ復帰される(ステップS25)。例えば、メイン表示装置151にメインメモリ13のユーザデータに含まれる表示データが送信され、AC電源遮断前の表示状態に戻される。そして、AC電源遮断前の状態でシステムが復帰され(ステップS26)、本処理は終了する。

Next, it is checked whether or not there is an error in the program written back to the main memory 13 (step S22). If the check result is OK (step S22; OK), it is determined whether or not the FC key has been detected (step S23 in FIG. 11b). If it is determined that the FC key has not been detected (step S23; NO), the program counter, stack pointer, register, system data, etc. on the suspend

一方、FCキーが検知済みであると判断されると(ステップS23;YES)、処理は図11bのステップS27に移行し、プログラム格納メモリ12のプログラムに誤りがないかチェックが行われる。チェック結果がOKである場合(ステップS27;OK)、プログラム格納メモリ12のプログラムがメインメモリ13のコピー領域133にコピーされ(ステップS28)、ECR1がFC状態にて起動され(ステップS29)、本処理は終了する。FC状態にて起動とは、メインメモリ13のサスペンド用エリア132、システムデータ領域134、ユーザデータ領域136のデータが消去された後に起動されることを意味する。起動後は、図4に示すECR制御処理が実行される。チェック結果がNGである場合(ステップS27;NG)、システムエラーが発生したことを示すシステムエラーメッセージ、例えば「システムエラー」という文字列がメイン表示装置151に表示され(ステップS30)、本処理は終了する。

On the other hand, if it is determined that the FC key has been detected (step S23; YES), the process proceeds to step S27 in FIG. 11b, and a check is made as to whether there is an error in the program in the

一方、ステップS19でハイバネーション完了フラグがONでないと判断された場合(ステップS19;NO)、ステップS20でチェックサムの検証がNGであると判断された場合(ステップS20;NG)、又は、ステップS22でメインメモリ13のプログラムチェック結果がNGである場合(ステップS22;NG)、処理は図11bのステップS31に移行し、プログラム格納メモリ12のプログラムに誤りがないかチェックが行われる。チェック結果がOKである場合(ステップS31;OK)、プログラム格納メモリ12のプログラムがメインメモリ13のコピー領域133にコピーされ(ステップS32)、ECR1がバックアップエラー状態にて起動され(ステップS33)、本処理は終了する。バックアップエラー状態にて起動とは、メイン表示装置151に「バックアップエラーが発生しました」等のメッセージが表示され、メインメモリ13から起動処理・終了処理用ワークエリア131以外の領域のデータ、即ち、サスペンド用エリア132、システムデータ領域134、設定データ領域135、ユーザデータ領域136のデータが消去された後、起動されることを意味する。起動後は、図4に示すECR制御処理が実行される。プログラムのチェック結果がNGである場合(ステップS31;NG)、システムエラーが発生したことを示すシステムエラーメッセージ、例えば「システムエラー」という文字列がメイン表示装置151に表示され(ステップS34)、本処理は終了する。

On the other hand, if it is determined in step S19 that the hibernation completion flag is not ON (step S19; NO), if it is determined in step S20 that checksum verification is NG (step S20; NG), or step S22. If the result of the program check in the

図12に、AC電源31の電源遮断前のメイン表示装置151及びAC電源31の電源供給後のメイン表示装置151の画面表示例を示す。図12では、商品登録処理中に停電等によりAC電源31が遮断された場合を示している。上述のように、終了処理では、CPU10のプログラムカウンタ、スタックポインタ、レジスタ、システムデータ等のシステムの動作状態を示すデータがメインメモリ13に退避され、バックアップ電源32のOFF前に更に不揮発性メモリであるハイバネーション用メモリ14に退避される。再度AC電源31が供給状態になった場合には、メインメモリ13上(又はハイバネーション用メモリ14)からプログラムカウンタ、スタックポインタ、レジスタ、システムデータ等がCPU10に読み出される。そのため、中断された商品登録処理プログラムの処理の実行位置をAC電源遮断前の状態に戻すことができ、図12に示すように、AC電源遮断前と同じ画面がメイン表示装置151に表示される。ユーザは、AC電源遮断前に行った登録をやり直すことなく、商品登録処理を継続して実行することが可能となる。

FIG. 12 shows screen display examples of the

また、バックアップ用電源32のOFF前にメインメモリ13上のデータが不揮発メモリであるハイバネーション用メモリ14に退避されるので、大容量のバックアップ用電源を搭載することなく、長期のAC電源遮断後に電源遮断前の状態にシステムを復帰させることが可能となる。

In addition, since the data on the

ハイバネーション用メモリ14に退避されたデータは、CPU10において他に実行すべき処理のない空き時間に書込みエリア事前消去処理により事前に消去されるので、AC電源31の遮断時にバックアップ用電源32からの給電をうけて実行されるハイバネーション処理におけるハイバネーション用メモリ14a、14bからのデータ消去にかかる時間を短縮することが可能となる。その結果、バックアップ電源32の消耗を低減することが可能となる。

Since the data saved in the

また、ハイバネーション処理の実行時以外はバックアップ用電源32がOFFに切り替えられるので、バックアップ電源32の消耗を必要最低限に抑えることが可能となる。

Further, since the

また、ハイバネーション用メモリ14が複数備えられ、データの書込み及び消去を複数のハイバネーション用メモリ14において並行して行うので、ハイバネーション用メモリ14へのデータ書込み速度及び消去速度を向上させることができる。その結果、バックアップ電源32の消耗を低減することが可能となる。

Further, since a plurality of

また、ハイバネーション処理が終了するまではAC電源遮断時におけるメインメモリ13の状態が保持され、ハイバネーション処理中には、CPU10によりAC電源31の電源状態が監視され、AC電源31が供給状態となった場合には、ハイバネーション処理を中断して起動処理に移行し、メインメモリ13に記憶されているシステム動作状態を示すデータをCPU10に書き戻してAC電源遮断前の状態で動作を復帰させる制御が行われる。具体的に、ハイバネーション処理は、書込みエリアの消去処理、書込み処理、書込み内容保証処理を含んで構成されるが、CPU10により、ハイバネーション用メモリ14における1ブロック毎のデータ消去中、書込み中にAC電源状態が監視されており、AC電源31が供給状態となった場合は、ハイバネーション処理を中断して起動処理のハイバネーション中断リスタート位置に移行する制御が行われる。従って、ハイバネーション処理中にAC電源31が供給状態となった場合、ハイバネーション処理の完了を待つことなく直ちにAC電源遮断前のシステム状態に復帰することが可能となる。

Further, the state of the

また、書込み内容保証処理では、メインメモリ13の退避対象データとハイバネーション用メモリ14に退避されたデータとの整合性をチェックするデータベリファイ処理の実施、書込んだバックアップデータのチェックサムの書込み、ハイバネーション完了フラグONの設定が行われるので、ハイバネーション用メモリ14に退避されたデータとハイバネーション用メモリ14からメインメモリ13に書き戻されるデータの整合性を保証することが可能となる。

In the write content guarantee process, a data verify process for checking the consistency between the save target data in the

(実施形態2)

次に、本発明の実施形態2について説明する。

実施形態2においては、マルチタスクで各種処理が実行される場合の一例について説明する。

(Embodiment 2)

Next, Embodiment 2 of the present invention will be described.

In the second embodiment, an example in which various processes are executed by multitasking will be described.

なお、実施形態2において、プログラム格納メモリ12には、オペレーティングシステムが記憶されている。オペレーティングシステムには、後述するECR制御処理(実施形態1と区別するためECR制御処理Bとする)、外部入力イベント割込み処理、タイマ割込み処理、終了処理、を実行するためのプログラムが含まれる。また、プログラム格納メモリ12には、商品登録処理タスク、書込みエリア事前消去処理タスクを実行するための各種プログラムが記憶されている。なお、各タスクのプログラムは、処理関数により構成される。

In the second embodiment, the

その他のECR1の構成については図1〜3を用いて実施形態1で説明したものと同様であるので説明を援用し、以下実施形態2の動作について説明する。

Since the configuration of the

図13〜図16に、CPU10とオペレーティングシステムとの協働により実行される処理のフローチャートを示す。

FIGS. 13 to 16 show flowcharts of processing executed in cooperation with the

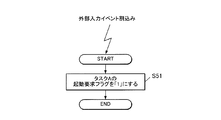

図13〜図16に示す処理は、CPU10とオペレーティングシステムの協働により以下のように切り替えながら実行される。

ECR1の起動後は、まず、図13に示すECR制御処理Bが実行される。入力装置18による入力(外部入力イベント割込み)が発生すると、ECR制御処理Bは中断され、図14に示す外部入力イベント割込み処理が実行される。外部入力イベント割込み処理が終了すると、ECR制御処理Bの中断した実行位置から処理が再開される。CPU10の内部クロックによるタイマ割込みが発生すると、ECR制御処理Bは中断され、図15に示すタイマ割込み処理が実行される。タイマ割込み処理が終了すると、ECR制御処理Bの中断した位置の処理に戻る。AC電源状態監視回路34によりAC電源遮断を通知する信号が入力され、電源遮断割込みが発生すると、図16に示す終了処理が実行され、ECR1の動作が停止される。

The processing shown in FIGS. 13 to 16 is executed while switching as follows by the cooperation of the

After the activation of ECR1, first, ECR control processing B shown in FIG. 13 is executed. When an input (external input event interrupt) by the

図13を参照してECR制御処理Bについて説明する。

まず、タスク登録処理が実行される(ステップS41)。タスク登録処理は、例えば、メインメモリ13のシステムデータ領域134に、OSのシステムデータとしてタスクとなる処理(処理関数)へのポインタ及びタスクの実行優先度(以下、単に優先度という)を登録する処理、タスクのスタックエリアを確保する処理等が含まれる。

The ECR control process B will be described with reference to FIG.

First, a task registration process is executed (step S41). In the task registration process, for example, a pointer to a process (processing function) serving as a task (system function) and a task execution priority (hereinafter simply referred to as priority) are registered in the

図17に、メインメモリ13のシステムデータ領域134に、オペレーティングシステムのシステムデータとして登録される情報の一例を示す。

タスク登録処理では、図17に示す優先度1の登録タスク情報134a、優先度2の登録タスク情報134b、優先度3の登録タスク情報134cが登録される。ここでは、優先度1が最も高く、優先度3が最も低い優先度を示している。各登録タスク情報には、タスクとなる処理(処理関数)へのポインタ等が含まれる。実施形態2においては、優先度1の登録タスク情報134aとして、商品登録処理タスク(タスクAとする)が書込まれており、優先度3の登録タスク情報134cとして、書込みエリア事前消去処理タスク(タスクCとする)が書込まれている。なお、図17においては、タスクの優先度が3段階の場合を例として示しているが、これに限定されない。

その他、オペレーティングシステムのシステムデータには、図17に示すように、その他情報134dが書込まれる。その他情報134dには、登録された各タスクの起動要求フラグ等が書込まれる。本実施形態2においては、タスクAの起動要求フラグ、タスクCの起動要求フラグ、タスクCの次の起動までの指定時間及びタスクCの次の実行位置等が書込まれる。タスクAの起動要求フラグ及びタスクCの起動要求フラグが「1」の場合は起動要求があることを示し、「0」の場合は起動要求がないことを示す。なお、タスク登録処理においては、タスクAの起動要求フラグの初期値として「0」が、タスクCの起動要求フラグの初期値として「1」が書込まれる。

FIG. 17 shows an example of information registered as system data of the operating system in the

In the task registration process, registered

In addition, as shown in FIG. 17,

次いで、システムデータ領域134のタスクAの起動要求フラグが参照され、タスクAの起動要求フラグが「1」であるか否かが判断される(ステップS42)。

Next, the activation request flag for task A in the

タスクAの起動要求フラグは、初期値は「0」であるが、入力装置18から商品登録処理の要求が入力され、入力装置18による外部入力イベント割込みが発生すると、図14に示すように、外部入力イベント割込み処理が実行され、「1」に書き替えられる(図14のステップS51)。

Although the initial value of the task A activation request flag is “0”, when a request for product registration processing is input from the

タスクAの起動要求フラグが「1」であると判断されると(ステップS42;YES)、タスクAの起動要求フラグが「0」に書き替えられ(ステップS43)、商品登録処理タスク(タスクA)が実行される(ステップS44)。 If it is determined that the task A activation request flag is “1” (step S42; YES), the task A activation request flag is rewritten to “0” (step S43), and the product registration processing task (task A) ) Is executed (step S44).

商品登録処理タスクは、入力装置18からの入力に従って、商品が取引された日時、商品名、商品の売上個数、売上金額等の売上データ、担当者等をユーザデータ領域136に登録し、商品名、売上(購入)個数、売上(購入)金額、お預かり金額、返金額等が印字装置17によりレシートに印字する処理である。

商品登録処理タスクの実行中に外部入力イベント割込み又はタイマ割込みが発生すると、商品登録処理タスクは中断され、外部入力イベント割込み処理又はタイマ割込み処理が実行される。このとき、中断されたタスクの実行位置はCPU10のレジスタに書込まれ、割り込みによる処理の終了後、中断された実行位置から商品登録処理タスクが再開される。

In accordance with the input from the

If an external input event interrupt or timer interrupt occurs during the execution of the product registration processing task, the product registration processing task is interrupted, and the external input event interrupt processing or timer interrupt processing is executed. At this time, the execution position of the interrupted task is written into the register of the

ステップS44の処理が終了すると、処理はステップS42に戻る。

ステップS42において、タスクAの起動要求フラグが「0」であると判断されると(ステップS42;NO)、システムデータ領域134のタスクCの起動要求フラグが参照され、タスクCの起動要求フラグが「1」であるか否かが判断される(ステップS45)。 タスクCの起動要求フラグが「1」であると判断されると(ステップS45;YES)、タスクCの起動要求フラグが「0」に書き替えられ(ステップS46)、書込みエリア事前消去処理タスク(タスクC)が実行される(ステップS47)。

When the process of step S44 ends, the process returns to step S42.

If it is determined in step S42 that the task A activation request flag is “0” (step S42; NO), the task C activation request flag in the

図18に、書込みエリア事前消去処理タスクのフローチャートを示す。

ここで、書込みエリア事前消去処理タスクは、ハイバネーション用メモリ14a、14bに記憶されているデータを消去する処理である。ハイバネーション用メモリ14a、14bには、上述したように、AC電源31の遮断時にメインメモリ13に記憶されているデータが退避される(書込まれる)。このデータ退避は、後述する電源遮断割込みによって実行される終了処理において、バックアップ用電源32の給電により行われる。しかし、ハイバネーション用メモリ14a、14bにデータを書込む前に、まず前回のAC遮断時に書込まれたデータをハイバネーション用メモリ14a、14bから消去する必要がある。この処理を全て終了処理において行うと、AC電源31が遮断されてから動作が完全に停止するまでに時間がかかり、バックアップ用電源32が消耗する。そこで、CPU10において他に実行すべき処理のない、即ち、商品登録処理タスク等が実行されていない空き時間に書込みエリア事前消去処理タスクを実行することで、AC電源31の遮断時におけるハイバネーション用メモリ14a、14bからのデータ消去にかかる時間を短縮し、バックアップ用電源32の消耗を低減する。

FIG. 18 shows a flowchart of the write area pre-erasing process task.

Here, the write area pre-erasing process task is a process of erasing data stored in the

まず、消去ブロック番号領域131aに記憶されている番号が取得される(ステップS401)。次いで、取得された番号がハイバネーション用メモリ14a、14bの最終ブロック番号nであるか否かが判断される(ステップS402)。

First, the number stored in the erase

取得された番号が最終ブロック番号nではないと判断されると(ステップS402;NO)、取得された番号の次の番号のブロックのデータ消去がハイバネーション用メモリ14a、14bに指示される(ステップS403)。そして、システムデータ領域134に、書込みエリア事前消去処理タスク(タスクC)の次の起動までの指定時間及びタスクCの次の実行位置の情報(書込みエリア事前消去処理が再開されたときに実行を開始する位置、具体的には、ステップS405)が書込まれ、書込みエリア事前消去処理タスクは待ち状態となる(ステップS404)。

If it is determined that the acquired number is not the final block number n (step S402; NO), the

図13に戻り、書込みエリア事前消去処理タスクが待ち状態となると、ECR制御処理Bに戻り、ステップS42から処理が実行される。

ECR制御処理Bが予め定められた一定時間実行されると、タイマ割込みが発生し、図15に示すタイマ割込み処理が実行される。タイマ割込みの発生は、CPU10の内部クロックにより管理される。

Returning to FIG. 13, when the write area pre-erasing process task is in a waiting state, the process returns to the ECR control process B, and the process is executed from step S42.

When the ECR control process B is executed for a predetermined time, a timer interrupt is generated and the timer interrupt process shown in FIG. 15 is executed. Generation of the timer interrupt is managed by the internal clock of the

ここで、図15を参照してタイマ割込み処理について説明する。

まず、システムデータ領域134に書込まれている、タスクCの次の起動までの指定時間が経過したか否かが判断される(ステップS61)。タスクCの次の起動までの指定時間が経過したか否かは、CPU10の内部クロックにより管理される。

Here, the timer interrupt process will be described with reference to FIG.

First, it is determined whether or not the specified time written in the

タスクCの次の起動までの指定時間が経過していないと判断されると(ステップS61;NO)、タイマ割込み処理は終了する。

タスクCの次の起動までの指定時間が経過したと判断されると(ステップS61;YES)、タスクCの起動要求フラグが「1」に書き替えられ、タイマ割込み処理は終了する。

When it is determined that the designated time until the next activation of the task C has not elapsed (step S61; NO), the timer interrupt process ends.

When it is determined that the designated time until the next activation of task C has elapsed (step S61; YES), the activation request flag of task C is rewritten to “1”, and the timer interrupt process ends.

タイマ割込み処理が終了すると、処理は図13に示すECR制御処理BのステップS42に移行する。ステップS42において、タスクAの起動要求フラグが「1」であると判断されると(ステップS42;YES)、上述のステップS43、S44の処理が実行される。ステップS42において、タスクAの起動要求フラグが「0」であると判断されると(ステップS42;NO)、システムデータ領域134のタスクCの起動要求フラグが参照され、タスクCの起動要求フラグが「1」であるか否かが判断される(ステップS45)。

When the timer interrupt process ends, the process proceeds to step S42 of the ECR control process B shown in FIG. If it is determined in step S42 that the activation request flag for task A is “1” (step S42; YES), the processes of steps S43 and S44 described above are executed. If it is determined in step S42 that the task A activation request flag is “0” (step S42; NO), the task C activation request flag in the

タスクCの起動要求フラグが「1」ではないと判断されると(ステップS45;NO)、処理はステップS42に戻る。タスクCの起動要求フラグが「1」であると判断されると(ステップS45;YES)、処理はステップS46に進み、タスクCの起動要求フラグが「0」に書き替えられ、書込みエリア事前消去処理が再開される(ステップS47)。 When it is determined that the task C activation request flag is not “1” (step S45; NO), the process returns to step S42. If it is determined that the task C activation request flag is “1” (step S45; YES), the process proceeds to step S46, the task C activation request flag is rewritten to “0”, and the write area pre-erase is performed. Processing is resumed (step S47).

ここで、システムデータ領域134には、書込みエリア事前消去処理が再開されたときの実行位置として、図18のステップS405の位置が書込まれているので、書込みエリア事前消去処理は図18のステップS405から再開される。

Here, since the position of step S405 in FIG. 18 is written in the

図18のステップS405においては、ステップS403において指示したブロックのデータ消去が終了したか否かの問い合わせがハイバネーション用メモリ14a、14bに送信され、指示されたブロックのデータ消去が終了していない旨がハイバネーション用メモリ14a、14bから応答されると(ステップS405;NO)、処理はステップS404に戻る。指示されたブロックのデータ消去が終了した旨がハイバネーション用メモリ14a、14bから応答されると(ステップS405;YES)、データ消去されたブロックのブロック番号が消去ブロック番号領域131aに書込まれ(ステップS406)、処理は図4のステップS401に戻る。

In step S405 in FIG. 18, an inquiry as to whether or not the data erasure of the block designated in step S403 has been completed is transmitted to the

一方、ステップS402において、取得された番号が最終ブロック番号nであると判断されると(ステップS402;YES)、書込みエリア事前消去処理タスクは終了し、処理は図13のステップS42に移行する。 On the other hand, if it is determined in step S402 that the acquired number is the final block number n (step S402; YES), the write area pre-erasing process task is terminated, and the process proceeds to step S42 in FIG.

AC電源状態監視回路34からAC電源遮断を通知する信号が入力されると、電源遮断割込みが発生し、図16に示す終了処理が実行される。終了処理は、実施形態1において図6を用いて説明したものと同様であるので詳細説明を援用する。即ち、サスペンド処理(ステップS71)、スイッチ35の切り替えによるバックアップ用電源32のONへの切り替え(ステップS72)、ハイバネーション処理(ステップS73)、スイッチ35の切り替えによるバックアップ用電源32のOFFへの切り替え(ステップS74)が行われ、動作が停止される。ハイバネーション処理の書込みエリア消去処理(図8参照)においては、書込みエリア事前消去処理タスクによって消去しきれなかった未処理の残存データのみを消去すればよいので、AC電源31の遮断時におけるハイバネーション用メモリ14a、14bからのデータ消去にかかる時間を短縮し、バックアップ電源32の消耗を低減することが可能となる。

When a signal for notifying AC power supply interruption is input from the AC power supply

AC電源状態監視回路34からAC電源投入を通知する信号が入力されると、図11a〜図11bに示す起動処理が実行される。起動処理は、実施形態1において説明したものと同様であるので説明を援用する。

When a signal for notifying that the AC power is turned on is input from the AC power supply

以上説明したように、実施形態2におけるECR1によれば、AC電源31の遮断時にメインメモリ13上のデータが不揮発メモリであるハイバネーション用メモリ14に退避されるので、大容量のバックアップ用電源を搭載することなく、長期のAC電源遮断後に電源遮断前の状態にシステムを復帰させることが可能となる。

As described above, according to the

ハイバネーション用メモリ14に退避されたデータは、CPU10において他に実行すべきタスクのない空き時間に書込みエリア事前消去処理タスクにより事前に消去されるので、AC電源31の遮断時にバックアップ用電源32からの給電をうけて実行されるハイバネーション処理におけるハイバネーション用メモリ14a、14bからのデータ消去にかかる時間を短縮することが可能となる。その結果、バックアップ電源32の消耗を低減することが可能となる。

Since the data saved in the

また、ハイバネーション処理の実行時以外はバックアップ用電源32がOFFに切り替えられるので、バックアップ電源32の消耗を必要最低限に抑えることが可能となる。

Further, since the

また、ハイバネーション用メモリ14が複数備えられ、データの書込み及び消去を複数のハイバネーション用メモリ14において並行して行うので、ハイバネーション用メモリ14へのデータ書込み速度及び消去速度を向上させることができる。その結果、バックアップ電源32の消耗を低減することが可能となる。

Further, since a plurality of

また、ハイバネーション処理が終了するまではAC電源遮断時におけるメインメモリ13の状態が保持され、ハイバネーション処理中には、CPU10によりAC電源31の電源状態が監視され、AC電源31が供給状態となった場合には、ハイバネーション処理を中断して起動処理に移行し、メインメモリ13に記憶されているシステム動作状態を示すデータをCPU10に書き戻してAC電源遮断前の状態で動作を復帰させる制御が行われる。具体的に、ハイバネーション処理は、書込みエリアの消去処理、書込み処理、書込み内容保証処理を含んで構成されるが、CPU10により、ハイバネーション用メモリ14における1ブロック毎のデータ消去中、書込み中にAC電源状態が監視されており、AC電源31が供給状態となった場合は、ハイバネーション処理を中断して起動処理のハイバネーション中断リスタート位置に移行する制御が行われる。従って、ハイバネーション処理中にAC電源31が供給状態となった場合、ハイバネーション処理の完了を待つことなく直ちにAC電源遮断前のシステム状態に復帰することが可能となる。

Further, the state of the

また、書込み内容保証処理では、メインメモリ13の退避対象データとハイバネーション用メモリ14に退避されたデータとの整合性をチェックするデータベリファイ処理の実施、書込んだバックアップデータのチェックサムの書込み、ハイバネーション完了フラグONの設定が行われるので、ハイバネーション用メモリ14に退避されたデータとハイバネーション用メモリ14からメインメモリ13に書き戻されるデータの整合性を保証することが可能となる。

In the write content guarantee process, a data verify process for checking the consistency between the save target data in the

なお、上記実施形態1〜2における記述内容は、本発明に係るECR1の好適な一例であり、これに限定されるものではない。

例えば、メインメモリ13に記憶されるデータは一例であり、これに限定されない。

その他、ECR1を構成する各装置の細部構成及び細部動作に関しても、発明の趣旨を逸脱することのない範囲で適宜変更可能である。

In addition, the description content in the said Embodiment 1-2 is a suitable example of ECR1 which concerns on this invention, and is not limited to this.

For example, the data stored in the

In addition, the detailed configuration and detailed operation of each device constituting the

1 ECR

10 CPU

11 RTC

12 プログラム格納メモリ

13 メインメモリ

131 起動処理・終了処理用ワークエリア

131a 消去ブロック番号領域

132 サスペンド用エリア

133 コピー領域

134 システムデータ領域

135 設定データ領域

136 ユーザデータ領域

14 ハイバネーション用メモリ

141 ヘッダ領域

142 バックアップ領域

143 チェックサム格納領域

151 メイン表示装置

152 サブ表示装置

16 LED

17 印字装置

18 入力装置

19 ストレージI/F

19a 外部ストレージ

20 通信部

1 ECR

10 CPU

11 RTC

12

17

Claims (4)

前記主電源の遮断時に前記揮発性記憶手段に記憶されているデータを退避するための不揮発性記憶手段と、

入力手段に対する入力処理が行われているか否かを判別し、入力処理が行われていない場合は、予め決められたデータ単位で前記不揮発性記憶手段に記憶されているデータの消去処理を実行し、前記主電源が遮断された際に、前記不揮発性記憶手段の最終領域まで前記データの消去処理が完了しているか否かを判別し、前記データの消去処理が完了していない場合は、補助電源からの給電により前記不揮発性記憶手段に記憶されている未消去の残存データの消去処理を実行し前記揮発性記憶手段に記憶されているデータを前記不揮発性記憶手段に退避させる制御手段と、

を備えるデータ処理装置。 Volatile storage means for storing data by power supply from the main power supply;

Nonvolatile storage means for saving data stored in the volatile storage means when the main power supply is shut off;

It is determined whether or not the input process is being performed on the input means. If the input process is not being performed, the data stored in the non-volatile storage means is erased in a predetermined data unit. When the main power is cut off, it is determined whether or not the data erasing process has been completed up to the final area of the nonvolatile storage means. If the data erasing process has not been completed, Control means for executing an erasing process of unerased residual data stored in the nonvolatile storage means by power supply from a power source and saving the data stored in the volatile storage means to the nonvolatile storage means;

A data processing apparatus comprising:

前記制御手段は、前記揮発性記憶手段に記憶されているデータを前記複数の不揮発性記憶手段に分散して退避させる請求項1に記載のデータ処理装置。 A plurality of the nonvolatile storage means;

The data processing apparatus according to claim 1, wherein the control unit distributes and saves data stored in the volatile storage unit to the plurality of nonvolatile storage units.

前記制御手段は、前記主電源が遮断された際に前記切り替え手段により前記補助電源に給電を行わせ、前記不揮発性記憶手段へのデータ退避の終了後、前記切り替え手段により前記補助電源を遮断させる請求項1又は2に記載のデータ処理装置。 Comprising a switching means for switching between supply and interruption of power from the auxiliary power supply,

The control means causes the switching means to supply power to the auxiliary power supply when the main power is cut off, and causes the switching means to cut off the auxiliary power supply after data saving to the nonvolatile storage means is completed. The data processing device according to claim 1 or 2.

入力手段に対する入力処理が行われているか否かを判別し、入力処理が行われていない場合は、予め決められたデータ単位で前記不揮発性記憶手段に記憶されているデータの消去処理を実行し、前記主電源が遮断された際に、前記不揮発性記憶手段の最終領域まで前記データの消去処理が完了しているか否かを判別し、前記データの消去処理が完了していない場合は、補助電源からの給電により前記不揮発性記憶手段に記憶されている未消去の残存データの消去処理を実行し前記揮発性記憶手段に記憶されているデータを前記不揮発性記憶手段に退避させる制御手段、

として機能させるためのプログラム。 A data processing apparatus comprising: volatile storage means for storing data by power supply from a main power supply; and nonvolatile storage means for saving data stored in the volatile storage means when the main power supply is shut off The computer used,

It is determined whether or not the input process is being performed on the input means. If the input process is not being performed, the data stored in the non-volatile storage means is erased in a predetermined data unit. When the main power is cut off, it is determined whether or not the data erasing process has been completed up to the final area of the nonvolatile storage means. If the data erasing process has not been completed, Control means for executing erasure processing of unerased residual data stored in the nonvolatile storage means by power supply from a power source and saving the data stored in the volatile storage means to the nonvolatile storage means;

Program to function as.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008299322A JP5444698B2 (en) | 2008-11-25 | 2008-11-25 | Data processing apparatus and program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008299322A JP5444698B2 (en) | 2008-11-25 | 2008-11-25 | Data processing apparatus and program |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010128537A JP2010128537A (en) | 2010-06-10 |

| JP2010128537A5 JP2010128537A5 (en) | 2011-11-04 |

| JP5444698B2 true JP5444698B2 (en) | 2014-03-19 |

Family

ID=42328920

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008299322A Active JP5444698B2 (en) | 2008-11-25 | 2008-11-25 | Data processing apparatus and program |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5444698B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6000655B2 (en) * | 2012-05-30 | 2016-10-05 | キヤノン株式会社 | Information processing apparatus, information processing apparatus control method, and program |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62140154A (en) * | 1985-12-16 | 1987-06-23 | Hitachi Ltd | Data holding system for memory device |

| JP4131116B2 (en) * | 2002-03-06 | 2008-08-13 | 松下電工株式会社 | Storage device and storage device backup method |

| JP3979308B2 (en) * | 2003-02-27 | 2007-09-19 | カシオ計算機株式会社 | Data processing apparatus and data processing program |

| JP4767597B2 (en) * | 2005-06-21 | 2011-09-07 | リンナイ株式会社 | Data backup device |

| JP4536785B2 (en) * | 2008-02-01 | 2010-09-01 | 富士通株式会社 | Information processing apparatus, control unit for controlling data storage performed in information processing apparatus, and data storage control method |

| JP2010026791A (en) * | 2008-07-18 | 2010-02-04 | Casio Comput Co Ltd | Sales data processor and program |

| JP2010026789A (en) * | 2008-07-18 | 2010-02-04 | Casio Comput Co Ltd | Sales data processor and program |

-

2008

- 2008-11-25 JP JP2008299322A patent/JP5444698B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010128537A (en) | 2010-06-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4768237B2 (en) | Portable electronic device and method for controlling portable electronic device | |

| JPH04362717A (en) | System restarting device | |

| CN102667716A (en) | Methods and devices for updating firmware of a component using a firmware update application | |

| JP2009146061A (en) | Information processing device and start-up method of the device | |

| JP2008200943A (en) | Image forming apparatus | |

| JP4820271B2 (en) | Image processing apparatus and image processing method | |

| CN100456313C (en) | Information display device | |

| JP2010026791A (en) | Sales data processor and program | |

| JP2012216014A (en) | Information processor and data protection method | |

| JP5444698B2 (en) | Data processing apparatus and program | |

| CN112035171B (en) | Factory setting restoration method and system based on UEFI firmware | |

| JP2003216511A (en) | Non-volatile memory device, data updating method, data updating program and computer readable recording medium with recorded program | |

| JP5349104B2 (en) | Electronic device and program update method | |

| JP2002099390A (en) | Disk controller | |

| JP2010026789A (en) | Sales data processor and program | |

| JP2008009799A (en) | Image forming device | |

| JP6737013B2 (en) | Image forming apparatus, starting method, and computer program | |

| JP2008009494A (en) | Image forming device | |

| JP4744983B2 (en) | Information processing device | |

| JP6000655B2 (en) | Information processing apparatus, information processing apparatus control method, and program | |

| JP3427010B2 (en) | Computer system | |

| JP2001306345A (en) | Information processor and pos terminal | |

| JP2001344156A (en) | Device with flash memory and data rewriting method | |

| JP3812281B2 (en) | Printing device | |

| JP5161600B2 (en) | Information processing apparatus and data recovery method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110914 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110914 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130305 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131209 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5444698 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |