JP5441216B2 - 半導体装置及びデータ処理システム - Google Patents

半導体装置及びデータ処理システム Download PDFInfo

- Publication number

- JP5441216B2 JP5441216B2 JP2010038857A JP2010038857A JP5441216B2 JP 5441216 B2 JP5441216 B2 JP 5441216B2 JP 2010038857 A JP2010038857 A JP 2010038857A JP 2010038857 A JP2010038857 A JP 2010038857A JP 5441216 B2 JP5441216 B2 JP 5441216B2

- Authority

- JP

- Japan

- Prior art keywords

- address

- input

- information

- terminal

- external

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

本発明の代表的な実施の形態に係る半導体装置(2)はデータ処理ユニット(100)と、前記半導体装置の外部から前記データ処理ユニットのアドレス空間へのアクセスを制御する外部インタフェース回路(10)を有する。前記外部インタフェース回路は、前記アドレス空間をアクセスするために用いられるアドレス信号の一部を前記半導体装置の外部から入力するための複数の外部端子(303,304)と、前記外部端子から入力されたアドレス情報の上位側を補完するための補完情報が前記半導体装置の外部から書込まれる補完レジスタ(401)と、前記半導体装置の外部からモード情報が書込まれるモードレジスタ(400)と、前記アドレス空間をアクセスするためのアドレス信号を前記外部端子からの入力情報、必要な補完情報及び前記モードレジスタのモード情報に基づく形態で生成するアドレス制御回路(202)と、を有する。

項1の半導体装置において、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報を前記補完レジスタの補完情報で補完する第1生成形態を含む(図5)。

項1乃至3の何れかの半導体装置において、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビット(A25)が第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、上位側を特定リソースのアドレスに割当てられた既定値とする第2生成形態(図6、図7)と、前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からのアドレス情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列(AD13〜AD11)の値に対応するリソースのアドレスに割り当てられている既定値とする第3生成形態(図6、図8)と、を含む。

項1乃至6の何れかの半導体装置において、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビット(A16)が第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、その上位側を前記補完レジスタが持つ補完情報とし、更にその上位側を特定リソースのアドレスに割当てられた既定値とする第4生成形態(図9、図10)と、前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からの情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列(AD13〜AD11)の値に対応するリソースのアドレスに割り当てられている既定値とする第5生成形態(図9、図8)と、を含む。

項9の半導体装置において、前記補完レジスタの補完情報をインクリメントするインクリメンタ(403)と、前記第4生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路(510)と、を更に有する。

項10の半導体装置において、前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する。

項11の半導体装置において、前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタ(402)を更に有する。前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える。

項2乃至12の何れかの半導体装置において、前記アドレス制御回路による前記アドレス信号の生成形態は、前記第1生成形態で用いられる場合よりも少ないビット数で前記外部端子の一部から入力されるアドレス情報を、前記第1生成形態で用いられる場合よりも多いビット数の前記補完レジスタの補完情報で補完する第6生成形態(図11)を含む。

項13の半導体装置において、前記第6生成形態において前記アドレス情報が入力される前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子である。

項14の半導体装置において、前記補完レジスタの補完情報をインクリメントするインクリメンタと、前記第6生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する。

項15の半導体装置において前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する。

項16の半導体装置において、前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有する。前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える。

本発明の別の実施の形態に係るデータ処理システム(1)は、第1のデータプロセッサ(2)と、前記第1のデータプロセッサのアドレス空間の一部に配置され前記第1のデータプロセッサの外部に接続された記憶装置(9)と、前記第1のデータプロセッサの外部に接続された第2のデータプロセッサ(3)と、を有する。前記第1のデータプロセッサは、前記第2のデータプロセッサから前記第1のデータプロセッサのアドレス空間へのアクセスを制御する第1の外部インタフェース回路(10)と、前記記憶装置へのアクセスを制御する第2の外部インタフェース回路(11)とを有する。前記第1の外部インタフェース回路は、前記アドレス空間をアクセスするために用いられるアドレス信号の一部を前記第2データプロセッサから入力するための外部端子(303,304)と、前記外部端子から入力されたアドレス情報の上位側を補完するための補完情報が前記第2のデータプロセッサによって書込まれる補完レジスタ(401)と、前記第2のデータプロセッサによってモード情報が書込まれるモードレジスタ(400)と、前記第1のデータプロセッサのアドレス空間をアクセスするためのアドレス信号を前記外部端子からの入力情報、必要な補完情報及び前記モードレジスタのモード情報に基づく形態で生成するアドレス制御回路(202)と、を有する。

項18のデータプロセッサにおいて前記第2のデータプロセッサは、前記モードレジスタ及び補完レジスタを設定した後に、前記外部端子にアドレス情報を出力してリードアクセス又はライトアクセスを発行する。

項18又は19のデータプロセッサにおいて、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報を前記補完レジスタの補完情報で補完する第1生成形態を含む。

項18乃至21の何れかのデータ処理システムにおいて、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、上位側を特定リソースのアドレスに割当てられた既定値とする第2生成形態と、前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からのアドレス情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第3生成形態と、を含む。

項22のデータ処理システムにおいて、前記特定リソースは前記記憶装置であり、前記特定ビット配列の値に対応するリソースは前記第1のデータプロセッサに内蔵されたレジスタ群である。

項22又は23のデータ処理システムにおいて、前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、前記第2生成形態及び第3生成形態において前記アドレス入力端子及びマルチプレクス端子の双方の全ビットが情報の入力に用いられ、前記特定ビットは前記アドレス入力端子の1ビットの入力であり、前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である。

項18乃至24の何れかのデータ処理システムにおいて、前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、その上位側を前記補完レジスタが持つ補完情報とし、更にその上位側を特定リソースのアドレスに割当てられた既定値とする第4生成形態と、前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からの情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第5生成形態と、を含む。

項25のデータ処理システムにおいて、前記特定リソースは前記記憶装置であり、前記特定ビット配列の値に対応するリソースは前記第1のデータプロセッサに内蔵されるレジスタ群である。

項25又は265のデータ処理システムにおいて、前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、前記第4生成形態及び第5生成形態において前記アドレス入力端子の1ビット及びマルチプレクス端子の全ビットが情報の入力に用いられ、前記特定ビットは前記1ビットのアドレス入力端子からの入力であり、前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である。

項27のデータ処理システムにおいて、前記補完レジスタの補完情報をインクリメントするインクリメンタと、前記第4生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する。

項28のデータ処理システムにおいて、前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する。

項29のデータ処理システムにおいて、前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える。

項20乃至30の何れかのデータ処理システムにおいて、前記アドレス制御回路による前記アドレス信号の生成形態は、前記第1生成形態で用いられる場合よりも少ないビット数で前記外部端子の一部から入力されるアドレス情報を、前記第1生成形態で用いられる場合よりも多いビット数の前記補完レジスタの補完情報で補完する第6生成形態を含む。

項31のデータ処理システムにおいて、前記第6生成形態において前記アドレス情報が入力される前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子である。

項32のデータ処理システムにおいて、前記補完レジスタの値をインクリメントするインクリメンタと、前記第6生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する。

項33のデータ処理システムにおいて、前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する。

項34のデータ処理システムにおいて、前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える。

実施の形態について更に詳述する。

図2には本発明に係るデータ処理システムの一例として携帯電話器が示される。携帯電話器は高周波トランシーバ(RFIC)4を有し、ベースバンドプロセッサ(BBP)3のプロトコル制御によって符号化された送信データを高周波トランシーバ4がアンテナを駆動して送信し、また、アンテナを介して高周波トランシーバ4が受信した信号をベースバンドプロセッサ3が所定のプロトコル制御によって受信データに復号する。ベースバンドプロセッサ3は命令を実行して送受信のプロトコル制御及び電話通信の認証などを行う中央処理装置やメモリなどを備えたひとつのデータプロセッサ若しくはマイクロコンピュータを構成する。

図3にはアプリケーションプロセッサ2の具体的な構成が例示される。

図4にはマスタインタフェース回路10の具体例が示される。マスタインタフェース回路10のアドレス変換回路140は内部バス150とのインタフェースを行うバス制御回路205と内部バス151とのインタフェースを行うバス制御回路206とを備え、チップの外部には外部同期インタフェース制御回路200と外部非同期インタフェース制御回路201を介して接続される。

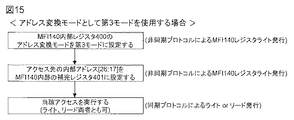

図1にはアドレス制御回路202及びレジスタ制御回路203によるアドレス変換機構の詳細が示される。レジスタ回路203は例えば補完レジスタ401及びモードレジスタ400を有する。補完レジスタ401は、前記アドレス端子304及びマルチプレクス端子303から入力されるアドレス情報の上位側を補完するための補完情報(例えば最大15ビット)CMPLがインタフェース回路201などを介してアプリケーションプロセッサ2の外部から書込まれるレジスタである。モードレジスタ400はインタフェース回路201などを介してアプリケーションプロセッサ2の外部などから例えば2ビットのモードデータMODEが書込まれるレジスタである。

上記第2のアドレス生成形態に対して第4のアドレス生成形態は外部端子を用いた連続アクセス空間が128KByteと小さく、同様に第1のアドレス生成形態に対して第6のアドレス生成形態は外部端子を用いた連続アクセス空間が128KByteと小さい。これよりも大きなアドレスアドレス範囲で連続アクセスを行う場合には、外部端子からのアドレス入力が一巡する度に補完レジスタ401に対するレジスタアクセスを介在されてその値を書き換える操作を行わなければならない。この書き換え操作を不要にするために補完レジスタ401に対するアドレスインクリメント機能を採用することができる。

図13にはアプリケーションプロセッサ2への第1モードを使用したアクセス例が示される。例えばアプリケーションプロセッサ2のアドレス空間におけるアドレス0x_41231234(※1)にアクセスする場合を一例とする。0x_4*******はSDRAMのアドレス空間とする。

図17には外部同期インタフェース制御回路200に対する書き込み動作のタイミングチャートが示される。クロック信号CK、ライトイネーブル信号WE及びリードイネーブル信号REはアドレスバリッド信号VLDadrと共にバスコントロール信号CTLに含まれる信号である。図17は8バイトのライト動作を例示する。アドレス入力はアドレス端子304からのアドレス信号ADRとマルチプレクス端子303からのアドレス信号ADRmuxとが並列入力される場合を例示する。ここではバーストライトのために連続的にライトデータが入力される場合を示す。例えばSDRAM9に対するバーストライトの場合にはそのためのバスコントローラ11がターゲットアドレス(Target Address)に続いてバーストライトアドレスを順次生成する。

3 ベースバンドプロセッサ(BBP)

2 アプリケーションプロセッサ(APP)

11 外部インタフェース回路(IF2nd)、SDRAMコントローラ(SBSC)

12 外部インタフェース回路(IF2nd)、バスステートコントローラ(BSC)

10 外部インタフェース回路(IF1st)

9 SDRAM

8 フラッシュメモリ

100 中央処理装置(CPU)

13 CPG

14 SYSC

10 マスタインタフェース回路

140 アドレス変換回路(MFI)

141 共有メモリ(MFRAM)

205 バス制御回路

206 バス制御回路

200 外部同期インタフェース制御回路

201 外部非同期インタフェース制御回路

202 アドレス制御回路

207 内部バッファ制御回路

203 内部レジスタ回路

205 バス制御回路

206 バス制御回路

300 同期インタフェース用チップ選択信号(CSsy)の入力端子

303 アドレス系信号(ADRmux)とデータ(DAT)のマルチプレクス端子

301 アドレスバリッド信号(VL Dadr)などのバスコントロール信号(CLT)の入力端子

302 ウェート信号(WAIT)の出力端子

304 アドレス信号(ADR)の入力端子

300 非同期インタフェース用チップ選択信号(CSasy)の入力端子

401 補完レジスタ

400 モードレジスタ

CMPL 補完情報

MODE モードデータ

500 アドレス生成ロジック回路

501 アドレスラッチ

502 ロジック回路

503 セレクタ

ACCADR 内部アドレス信号

403 インクリメンタ

402 アドレスインクリメントモードレジスタ

510 アドレスインクリメント制御ロジック

512 バッファ制御ロジック

511 アドレスバッファ

Claims (35)

- データ処理ユニットを有する半導体装置であって、

前記半導体装置の外部のデータプロセッサから前記データ処理ユニットのアドレス空間へのアクセスを制御する第1外部インタフェース回路と、

前記半導体装置の特定リソースとされ前記アドレス空間に保有される、記憶装置が接続される第2外部インタフェース回路とを有し、

前記第1外部インタフェース回路は、前記アドレス空間をアクセスするために用いられるアドレス信号の一部を前記データプロセッサから入力するための外部端子と、前記外部端子から入力されたアドレス情報の上位側を補完するための補完情報が前記データプロセッサから書込まれる補完レジスタと、前記データプロセッサからモード情報が書込まれるモードレジスタと、前記アドレス空間をアクセスするためのアドレス信号を前記外部端子からの入力情報、必要な補完情報及び前記モードレジスタのモード情報に基づく形態で生成するアドレス制御回路と、を有する半導体装置。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報を前記補完レジスタの補完情報で補完する第1生成形態を含む、請求項1記載の半導体装置。

- 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第1生成形態において前記アドレス入力端子及びマルチプレクス端子の双方を用いてアドレス情報を入力する、請求項2記載の半導体装置。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、上位側を特定リソースのアドレスに割当てられた既定値とする第2生成形態と、

前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からのアドレス情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第3生成形態と、を含む請求項1乃至3の何れか1項記載の半導体装置。 - 前記特定リソースはシンクロナスDRAMであり、

前記特定ビット配列の値に対応するリソースはレジスタ群である、請求項4記載の半導体装置。 - 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第2生成形態及び第3生成形態において前記アドレス入力端子及びマルチプレクス端子の双方の全ビットが情報の入力に用いられ、

前記特定ビットは前記アドレス入力端子の1ビットの入力であり、

前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である、請求項4記載の半導体装置。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、その上位側を前記補完レジスタが持つ補完情報とし、更にその上位側を特定リソースのアドレスに割当てられた既定値とする第4生成形態と、

前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からの情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第5生成形態と、を含む請求項1乃至4の何れか1項記載の半導体装置。 - 前記特定リソースはシンクロナスDRAMであり、

前記特定ビット配列の値に対応するリソースはレジスタ群である、請求項7記載の半導体装置。 - 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第4生成形態及び第5生成形態において前記アドレス入力端子の1ビット及びマルチプレクス端子の全ビットが情報の入力に用いられ、

前記特定ビットは前記1ビットのアドレス入力端子からの入力であり、

前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である、請求項7記載の半導体装置。 - 前記補完レジスタの補完情報をインクリメントするインクリメンタと、前記第4生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する、請求項9記載の半導体装置。

- 前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する、請求項10記載の半導体装置。

- 前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、

前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える、請求項11記載の半導体装置。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記第1生成形態で用いられる場合よりも少ないビット数で前記外部端子の一部から入力されるアドレス情報を、前記第1生成形態で用いられる場合よりも多いビット数の前記補完レジスタの補完情報で補完する第6生成形態を含む、請求項2記載の半導体装置。

- 前記第6生成形態において前記アドレス情報が入力される前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子である、請求項13記載の半導体装置。

- 前記補完レジスタの補完情報をインクリメントするインクリメンタと、前記第6生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する請求項14記載の半導体装置。

- 前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する、請求項15記載の半導体装置。

- 前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、

前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える、請求項16記載の半導体装置。 - 第1のデータプロセッサと、

前記第1のデータプロセッサのアドレス空間の一部に配置され前記第1のデータプロセッサの外部に接続された記憶装置と、

前記第1のデータプロセッサの外部に接続された第2のデータプロセッサと、を有するデータ処理システムであって、

前記第1のデータプロセッサは、前記第2のデータプロセッサから前記第1のデータプロセッサのアドレス空間へのアクセスを制御する第1の外部インタフェース回路と、前記記憶装置へのアクセスを制御する第2の外部インタフェース回路とを有し、

前記第1の外部インタフェース回路は、前記アドレス空間をアクセスするために用いられるアドレス信号の一部を前記第2データプロセッサから入力するための外部端子と、前記外部端子から入力されたアドレス情報の上位側を補完するための補完情報が前記第2のデータプロセッサによって書込まれる補完レジスタと、前記第2のデータプロセッサによってモード情報が書込まれるモードレジスタと、前記第1のデータプロセッサのアドレス空間をアクセスするためのアドレス信号を前記外部端子からの入力情報、必要な補完情報及び前記モードレジスタのモード情報に基づく形態で生成するアドレス制御回路と、を有するデータ処理システム。 - 前記第2のデータプロセッサは、前記モードレジスタ及び補完レジスタを設定した後に、前記外部端子にアドレス情報を出力してリードアクセス又はライトアクセスを発行する、請求項18記載のデータ処理システム。

- 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報を前記補完レジスタの補完情報で補完する第1生成形態を含む、請求項18記載のデータ処理システム。

- 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第1生成形態において前記アドレス入力端子及びマルチプレクス端子の双方を用いてアドレス情報を入力する、請求項20記載のデータ処理システム。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、上位側を特定リソースのアドレスに割当てられた既定値とする第2生成形態と、

前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からのアドレス情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第3生成形態と、を含む請求項18記載のデータ処理システム。 - 前記特定リソースは前記記憶装置であり、

前記特定ビット配列の値に対応するリソースは前記第1のデータプロセッサに内蔵されたレジスタ群である、請求項22記載のデータ処理システム。 - 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第2生成形態及び第3生成形態において前記アドレス入力端子及びマルチプレクス端子の双方の全ビットが情報の入力に用いられ、

前記特定ビットは前記アドレス入力端子の1ビットの入力であり、

前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である、請求項22記載のデータ処理システム。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記外部端子から入力されるアドレス情報の特定ビットが第1の値であるとき、当該特定ビットを除く前記外部端子からのアドレス情報を下位側とし、その上位側を前記補完レジスタが持つ補完情報とし、更にその上位側を特定リソースのアドレスに割当てられた既定値とする第4生成形態と、

前記外部端子から入力されるアドレス情報の特定ビットが第2の値であるとき、前記外部端子からの情報の所定のビット列を下位側とし、上位側を前記外部端子から入力される情報の別の特定ビット配列の値に対応するリソースのアドレスに割り当てられている既定値とする第5生成形態と、を含む請求項18記載のデータ処理システム。 - 前記特定リソースは前記記憶装置であり、

前記特定ビット配列の値に対応するリソースは前記第1のデータプロセッサに内蔵されるレジスタ群である、請求項25記載のデータ処理システム。 - 前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子とアドレス入力端子であり、

前記第4生成形態及び第5生成形態において前記アドレス入力端子の1ビット及びマルチプレクス端子の全ビットが情報の入力に用いられ、

前記特定ビットは前記1ビットのアドレス入力端子からの入力であり、

前記所定のビット列及び別の特定ビット配列は外部マルチプレクス端子からの入力である、請求項25記載のデータ処理システム。 - 前記補完レジスタの補完情報をインクリメントするインクリメンタと、前記第4生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する請求項27記載のデータ処理システム。

- 前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する、請求項28記載のデータ処理システム。

- 前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、

前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える、請求項29記載のデータ処理システム。 - 前記アドレス制御回路による前記アドレス信号の生成形態は、前記第1生成形態で用いられる場合よりも少ないビット数で前記外部端子の一部から入力されるアドレス情報を、前記第1生成形態で用いられる場合よりも多いビット数の前記補完レジスタの補完情報で補完する第6生成形態を含む、請求項20記載のデータ処理システム。

- 前記第6生成形態において前記アドレス情報が入力される前記外部端子はアドレス入力又はデータ入出力に切換えて用いられる外部マルチプレクス端子である、請求項31記載のデータ処理システム。

- 前記補完レジスタの値をインクリメントするインクリメンタと、前記第6生成形態において補完レジスタによる補完対象にされる前記マルチプレクス端子からのアドレス情報のビット数で表現される値が一巡される一つ前の値に達する毎に前記インクリメンタにインクリメント動作の指示を与えるアドレスインクリメント制御回路と、を更に有する請求項32記載のデータ処理システム。

- 前記アドレスインクリメント制御回路は、前記外部端子からのアドレス情報が複数バイトアドレス単位で変化される複数バイトアドレスインクリメントモードによる外部端子からのアドレス情報の値が、前記アドレス情報のビット数で表現される最終値の一つ前の値にされることに応答して前記インクリメント動作の指示を発行する、請求項33記載のデータ処理システム。

- 前記アドレスインクリメントモードの種別を指定するアドレスインクリメントモードレジスタを更に有し、

前記アドレスインクリメント制御回路は、アドレスインクリメントモードレジスタで指定された種別に応じて、アドレスインクリメント動作を指示するときの前記最終値を切換える、請求項34記載のデータ処理システム。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010038857A JP5441216B2 (ja) | 2010-02-24 | 2010-02-24 | 半導体装置及びデータ処理システム |

| US13/033,641 US8291124B2 (en) | 2010-02-24 | 2011-02-24 | Semiconductor device and data processing system having a reduced number of terminals allocated for externally accessed address |

| US13/618,369 US8543735B2 (en) | 2010-02-24 | 2012-09-14 | Semiconductor device and data processing system having reduced number of terminals allocated for externally accessed address |

| US14/011,336 US9298657B2 (en) | 2010-02-24 | 2013-08-27 | Semiconductor device and data processing system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010038857A JP5441216B2 (ja) | 2010-02-24 | 2010-02-24 | 半導体装置及びデータ処理システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011175445A JP2011175445A (ja) | 2011-09-08 |

| JP2011175445A5 JP2011175445A5 (ja) | 2012-09-20 |

| JP5441216B2 true JP5441216B2 (ja) | 2014-03-12 |

Family

ID=44477430

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010038857A Expired - Fee Related JP5441216B2 (ja) | 2010-02-24 | 2010-02-24 | 半導体装置及びデータ処理システム |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US8291124B2 (ja) |

| JP (1) | JP5441216B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6294732B2 (ja) * | 2014-03-31 | 2018-03-14 | 株式会社メガチップス | データ転送制御装置及びメモリ内蔵装置 |

| JP6517549B2 (ja) * | 2015-03-13 | 2019-05-22 | 東芝メモリ株式会社 | メモリコントローラ、記憶装置、データ転送システム、データ転送方法、及びデータ転送プログラム |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55108052A (en) * | 1979-02-09 | 1980-08-19 | Usac Electronics Ind Co Ltd | Data processing system |

| US4754435A (en) | 1985-02-14 | 1988-06-28 | Nec Corporation | Semiconductor device having a memory circuit |

| JPH06251168A (ja) * | 1993-03-01 | 1994-09-09 | Oki Lsi Tekunoroji Kansai:Kk | Eprom内蔵マイコンのアドレス生成回路 |

| US20020116595A1 (en) * | 1996-01-11 | 2002-08-22 | Morton Steven G. | Digital signal processor integrated circuit |

| EP1122688A1 (en) * | 2000-02-04 | 2001-08-08 | Texas Instruments Incorporated | Data processing apparatus and method |

| US6785781B2 (en) * | 2000-04-20 | 2004-08-31 | International Business Machines Corporation | Read/write alignment scheme for port reduction of multi-port SRAM cells |

| EP1679590B1 (en) * | 2001-01-31 | 2011-03-23 | Renesas Electronics Corporation | Data processing system |

| US20040193835A1 (en) * | 2003-03-31 | 2004-09-30 | Patrick Devaney | Table lookup instruction for processors using tables in local memory |

| DE10355583A1 (de) * | 2003-11-28 | 2005-07-07 | Advanced Micro Devices, Inc., Sunnyvale | Gemeinsame Nutzung eines Speichers in einer Zentralsteuerung |

| US7230876B2 (en) | 2005-02-14 | 2007-06-12 | Qualcomm Incorporated | Register read for volatile memory |

| US7613060B2 (en) * | 2007-05-21 | 2009-11-03 | Micron Technology, Inc. | Methods, circuits, and systems to select memory regions |

| US8850103B2 (en) * | 2009-08-28 | 2014-09-30 | Microsoft Corporation | Interruptible NAND flash memory |

-

2010

- 2010-02-24 JP JP2010038857A patent/JP5441216B2/ja not_active Expired - Fee Related

-

2011

- 2011-02-24 US US13/033,641 patent/US8291124B2/en not_active Expired - Fee Related

-

2012

- 2012-09-14 US US13/618,369 patent/US8543735B2/en active Active

-

2013

- 2013-08-27 US US14/011,336 patent/US9298657B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011175445A (ja) | 2011-09-08 |

| US20130346634A1 (en) | 2013-12-26 |

| US20130073831A1 (en) | 2013-03-21 |

| US20110208878A1 (en) | 2011-08-25 |

| US8291124B2 (en) | 2012-10-16 |

| US9298657B2 (en) | 2016-03-29 |

| US8543735B2 (en) | 2013-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI679539B (zh) | 主從式系統、指令執行方法與資料存取方法 | |

| JP3234734B2 (ja) | 複数のオンチップメモリバスを備えたデータ処理装置 | |

| US9501964B2 (en) | Semiconductor device and data processing system selectively operating as one of a big endian or little endian system | |

| JP3904244B2 (ja) | シングル・チップ・データ処理装置 | |

| JP6998991B2 (ja) | 情報処理用方法及び装置 | |

| JPS5925254B2 (ja) | デイジタル・デ−タ処理装置 | |

| JP5441216B2 (ja) | 半導体装置及びデータ処理システム | |

| JP2013092852A (ja) | バス接続回路、半導体装置及びバス接続回路の動作方法 | |

| US11907120B2 (en) | Computing device for transceiving information via plurality of buses, and operating method of the computing device | |

| JP2002366425A (ja) | アドレス変換回路を有するデータ処理装置 | |

| JP2004199187A (ja) | Cpu内蔵lsi | |

| JPH11259417A (ja) | バスアクセス方式およびバスアクセス制御装置 | |

| KR20060130033A (ko) | 비메모리 맵핑된 디바이스 메모리에 대한 액세스를관리하는 방법 및 시스템 | |

| JP2007087416A (ja) | シングルチップデータ処理装置 | |

| JP3562215B2 (ja) | マイクロコンピュータ及び電子機器 | |

| JP4227789B2 (ja) | 集積回路装置およびデータ処理システム | |

| US20050289320A1 (en) | Semiconductor device, microcomputer, and electronic equipment | |

| JP2004013289A (ja) | マイクロコントローラのオンチップデバッグ方法 | |

| JP2003208399A (ja) | データ処理装置 | |

| JP2001306493A (ja) | データ転送制御装置及びマイクロコンピュータ | |

| CN113961487A (zh) | 加速存储器存取的电子装置及方法 | |

| JP4070141B2 (ja) | シングル・チップ・データ処理装置及びデータ処理装置 | |

| KR100791176B1 (ko) | 디지털 데이터 폭 정합을 통한 인터페이스 장치 | |

| JP2011175444A (ja) | データプロセッサ、半導体装置及びデータ処理システム | |

| JP4448917B2 (ja) | 半導体集積回路装置、データ処理装置及びマイクロコンピュータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120806 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120806 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130927 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131003 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131119 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131213 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5441216 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |